Sequential Logic Implementation z Models for representing sequential

![Moore Verilog FSM (cont’d) always @(in or state) case (state) zero [0] zero: begin Moore Verilog FSM (cont’d) always @(in or state) case (state) zero [0] zero: begin](https://slidetodoc.com/presentation_image_h/aa85564ec84c9043468cd46e525ceeed/image-10.jpg)

- Slides: 32

Sequential Logic Implementation z Models for representing sequential circuits y Abstraction of sequential elements y Finite state machines and their state diagrams y Inputs/outputs y Mealy, Moore, and synchronous Mealy machines z Finite state machine design procedure y Verilog specification y Deriving state diagram y Deriving state transition table y Determining next state and output functions y Implementing combinational logic CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 1

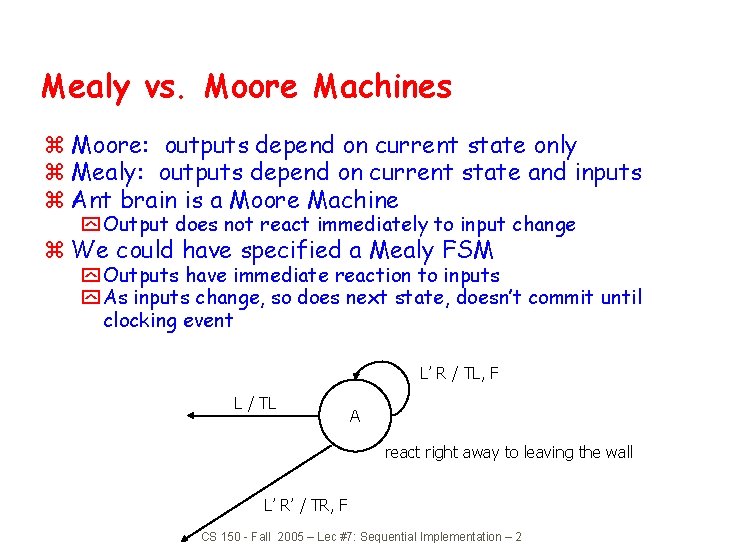

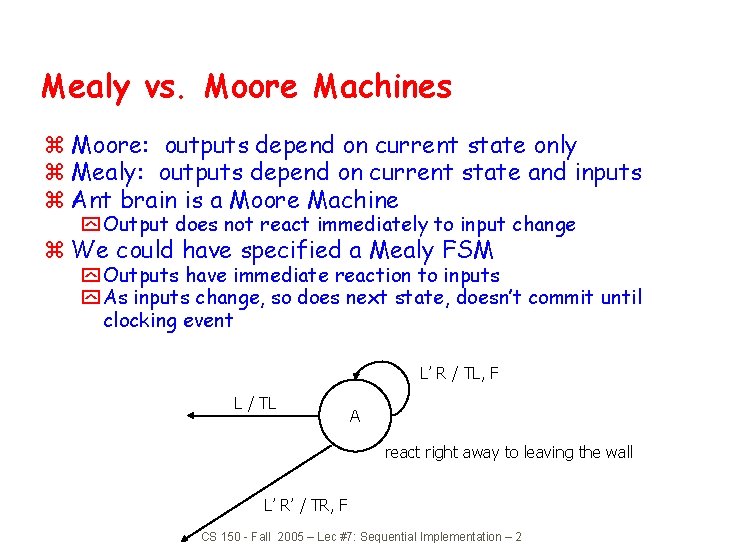

Mealy vs. Moore Machines z Moore: outputs depend on current state only z Mealy: outputs depend on current state and inputs z Ant brain is a Moore Machine y Output does not react immediately to input change z We could have specified a Mealy FSM y Outputs have immediate reaction to inputs y As inputs change, so does next state, doesn’t commit until clocking event L’ R / TL, F L / TL A react right away to leaving the wall L’ R’ / TR, F CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 2

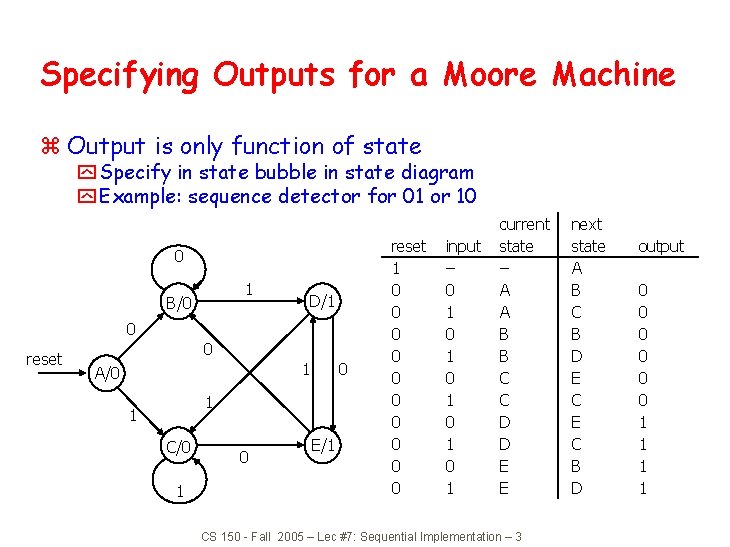

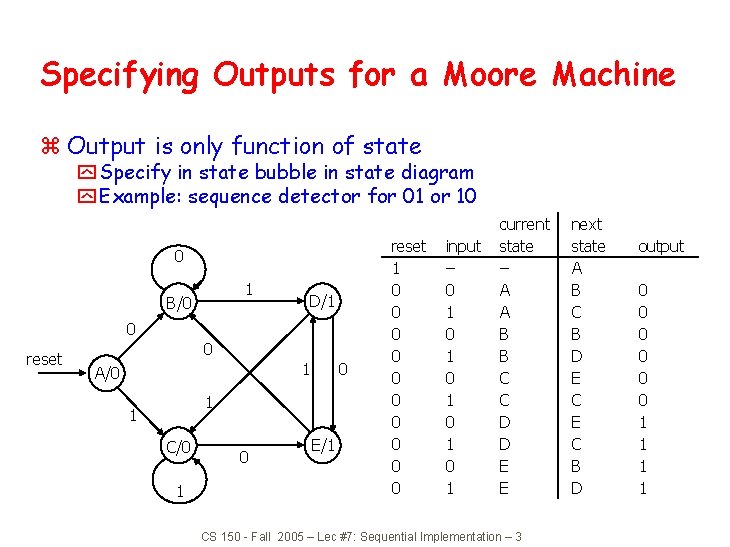

Specifying Outputs for a Moore Machine z Output is only function of state y Specify in state bubble in state diagram y Example: sequence detector for 01 or 10 0 1 B/0 D/1 0 reset 0 1 A/0 0 1 1 C/0 1 0 E/1 reset 1 0 0 0 0 0 input – 0 1 0 1 0 1 current state – A A B B C C D D E E CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 3 next state A B C B D E C B D output 0 0 0 1 1

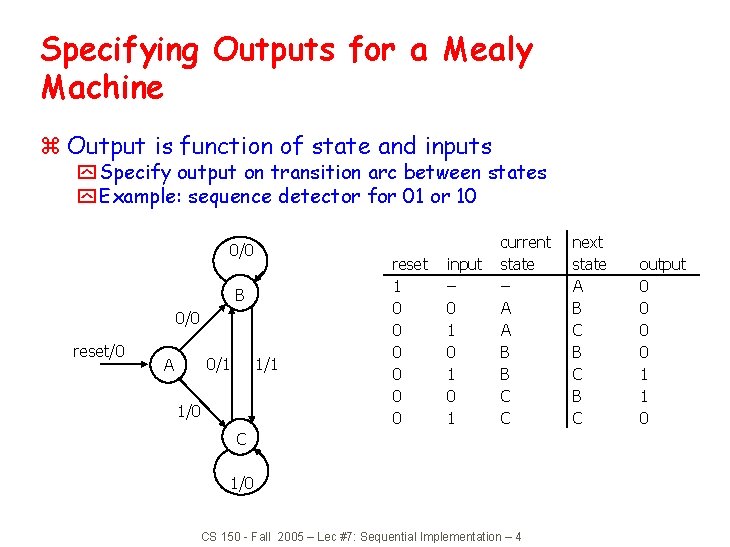

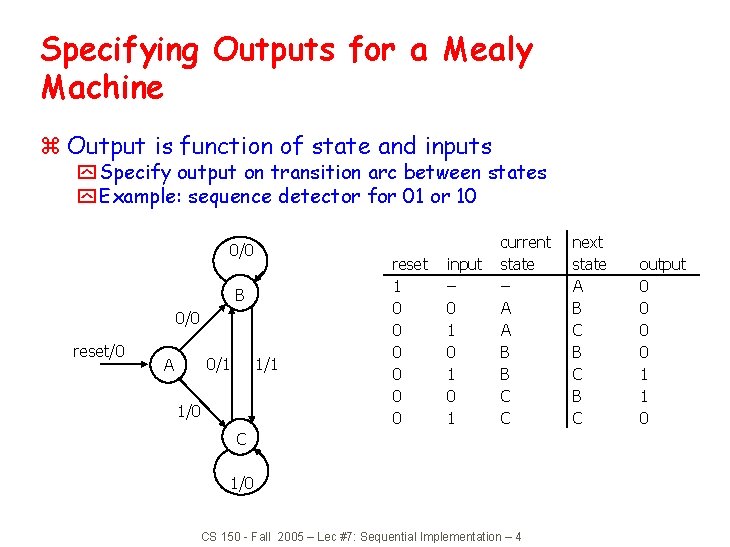

Specifying Outputs for a Mealy Machine z Output is function of state and inputs y Specify output on transition arc between states y Example: sequence detector for 01 or 10 0/0 B 0/0 reset/0 0/1 A 1/1 1/0 reset 1 0 0 0 input – 0 1 0 1 current state – A A B B C C C 1/0 CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 4 next state A B C B C output 0 0 1 1 0

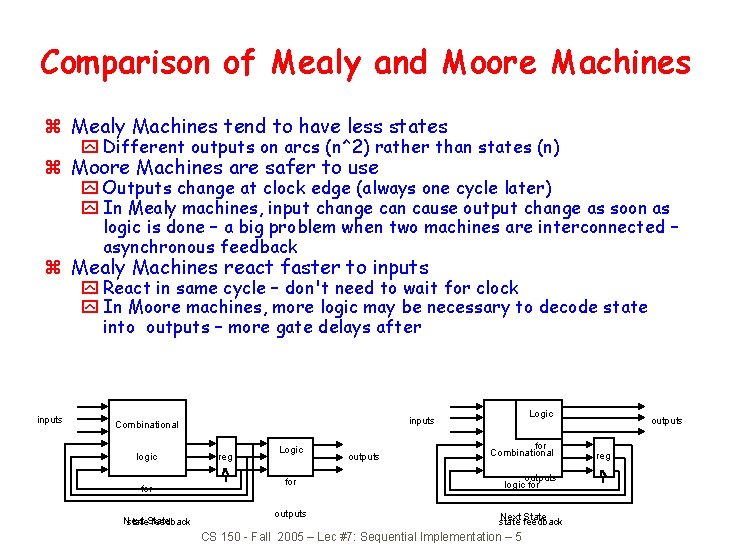

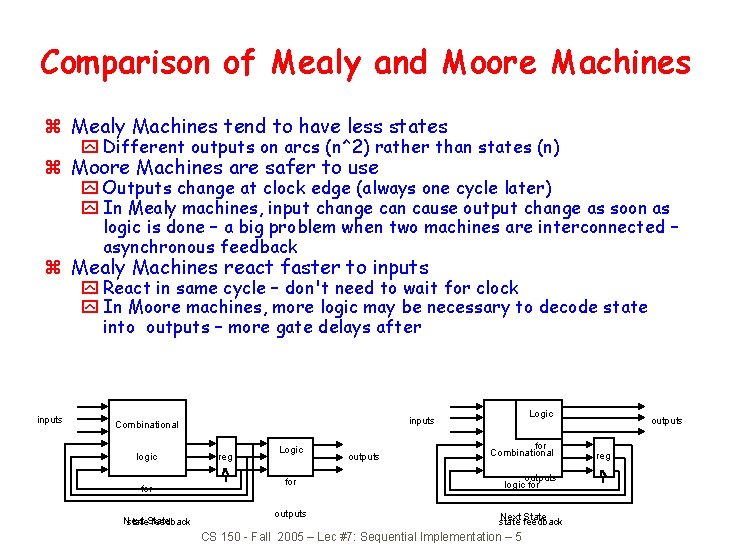

Comparison of Mealy and Moore Machines z Mealy Machines tend to have less states y Different outputs on arcs (n^2) rather than states (n) z Moore Machines are safer to use y Outputs change at clock edge (always one cycle later) y In Mealy machines, input change can cause output change as soon as logic is done – a big problem when two machines are interconnected – asynchronous feedback z Mealy Machines react faster to inputs y React in same cycle – don't need to wait for clock y In Moore machines, more logic may be necessary to decode state into outputs – more gate delays after inputs logic for Next state. State feedback Logic inputs Combinational reg Logic outputs for Combinational for outputs logic for outputs Next State state feedback CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 5 outputs reg

Mealy and Moore Examples z Recognize A, B = 0, 1 y Mealy or Moore? CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 6

Mealy and Moore Examples (cont’d) z Recognize A, B = 1, 0 then 0, 1 y Mealy or Moore? CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 7

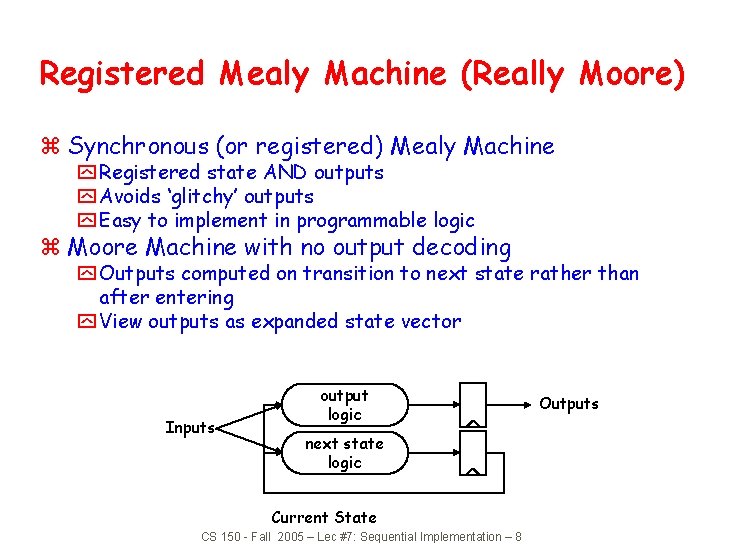

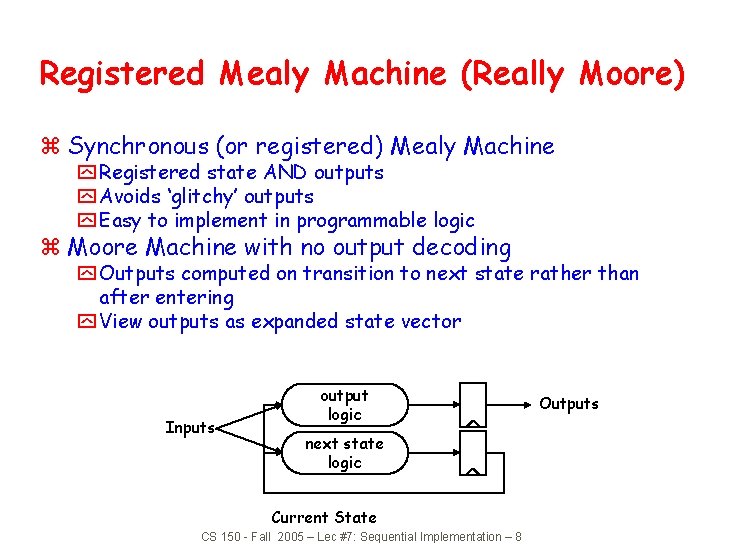

Registered Mealy Machine (Really Moore) z Synchronous (or registered) Mealy Machine y Registered state AND outputs y Avoids ‘glitchy’ outputs y Easy to implement in programmable logic z Moore Machine with no output decoding y Outputs computed on transition to next state rather than after entering y View outputs as expanded state vector Inputs output logic next state logic Current State CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 8 Outputs

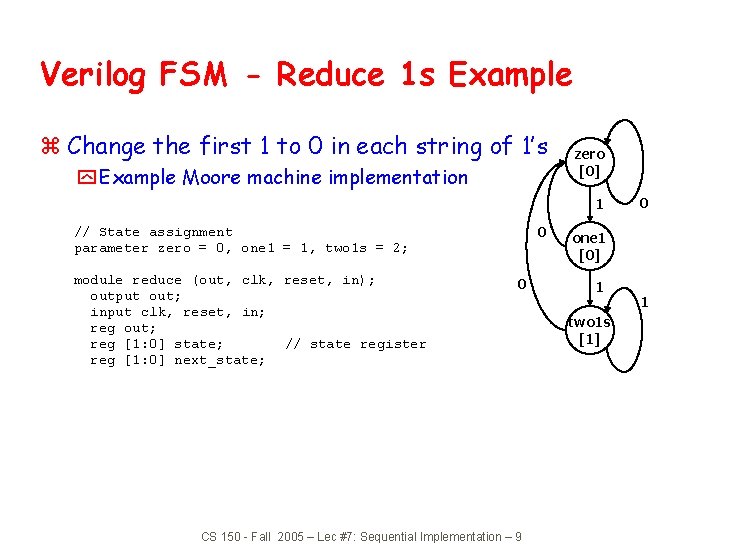

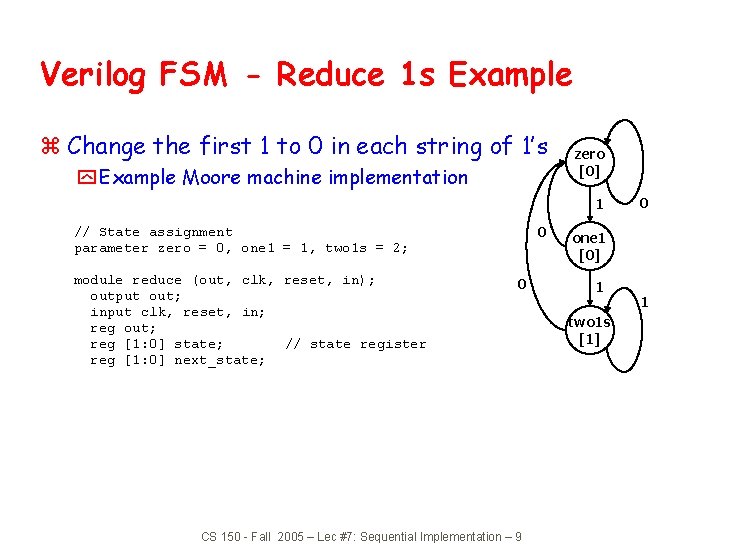

Verilog FSM - Reduce 1 s Example z Change the first 1 to 0 in each string of 1’s y Example Moore machine implementation zero [0] 1 0 // State assignment parameter zero = 0, one 1 = 1, two 1 s = 2; module reduce (out, clk, reset, in); output out; input clk, reset, in; reg out; reg [1: 0] state; // state register reg [1: 0] next_state; 0 CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 9 0 one 1 [0] 1 two 1 s [1] 1

![Moore Verilog FSM contd always in or state case state zero 0 zero begin Moore Verilog FSM (cont’d) always @(in or state) case (state) zero [0] zero: begin](https://slidetodoc.com/presentation_image_h/aa85564ec84c9043468cd46e525ceeed/image-10.jpg)

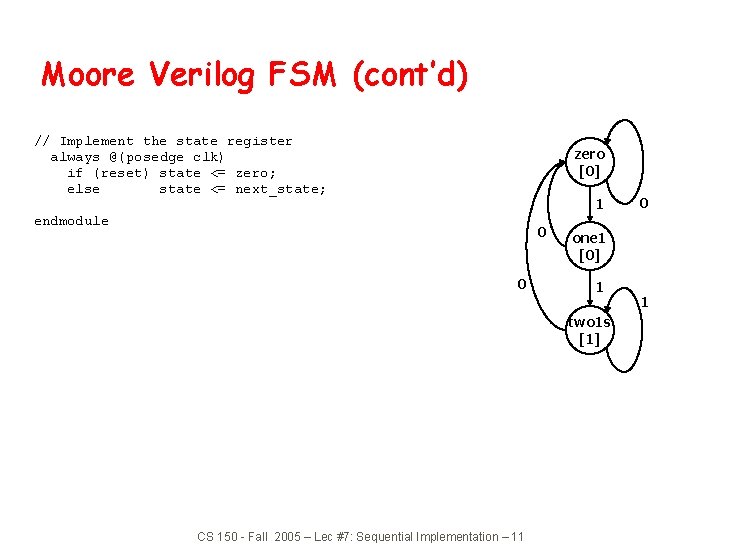

Moore Verilog FSM (cont’d) always @(in or state) case (state) zero [0] zero: begin // last input was a zero out = 0; if (in) next_state = one 1; else next_state = zero; end one 1: begin // we've seen one 1 out = 0; if (in) next_state = two 1 s; else next_state = zero; end two 1 s: begin // we've seen at least 2 ones out = 1; if (in) next_state = two 1 s; else next_state = zero; end default: begin // in case we reach a bad state out = 0; next_state = zero; endcase 1 0 0 0 one 1 [0] 1 1 two 1 s [1] include all signals that are input to state and output equations CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 10

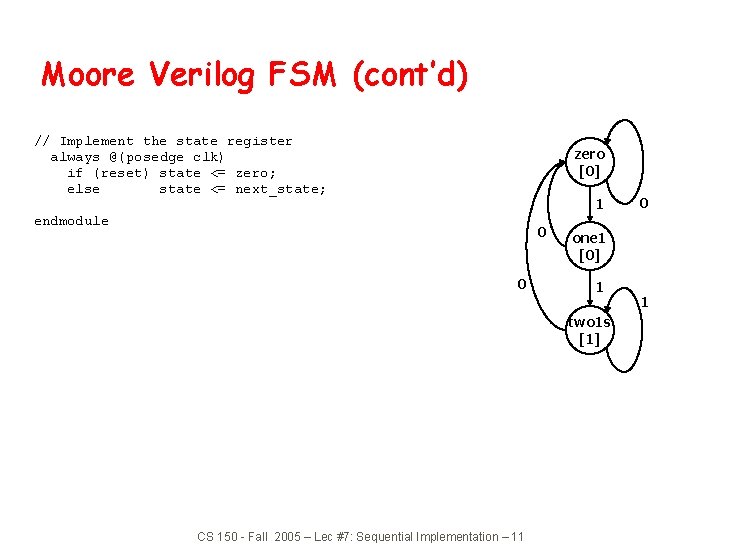

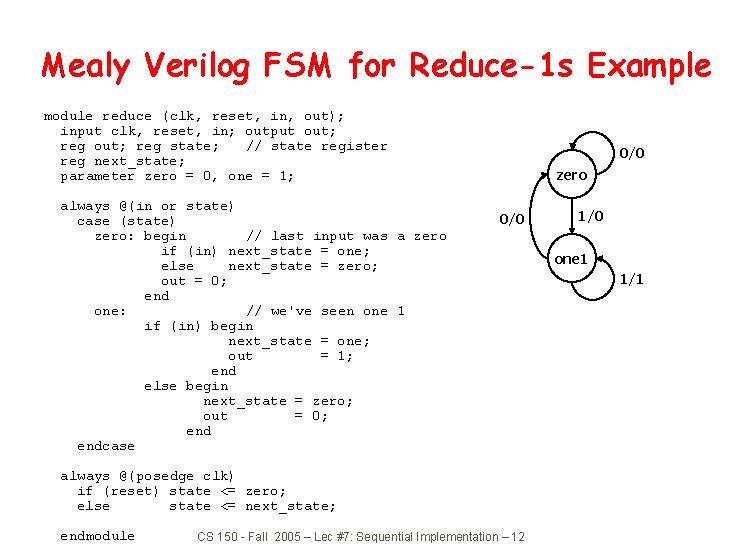

Moore Verilog FSM (cont’d) // Implement the state register always @(posedge clk) if (reset) state <= zero; else state <= next_state; zero [0] 1 endmodule 0 0 one 1 [0] 1 two 1 s [1] CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 11 0 1

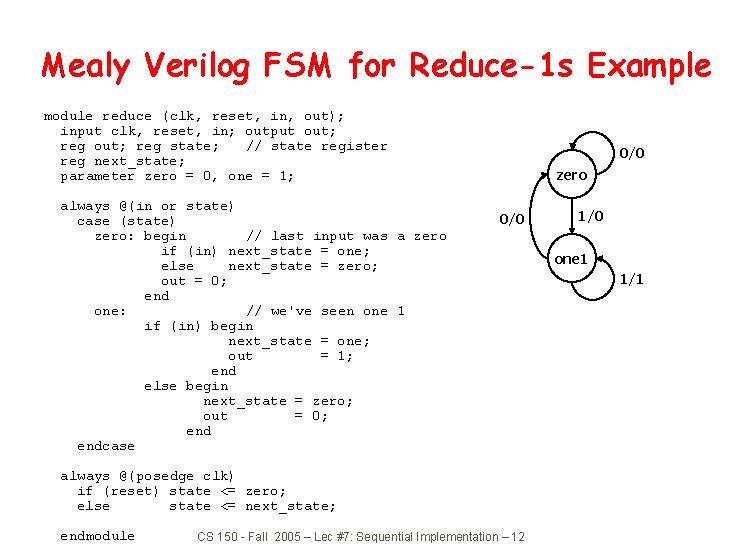

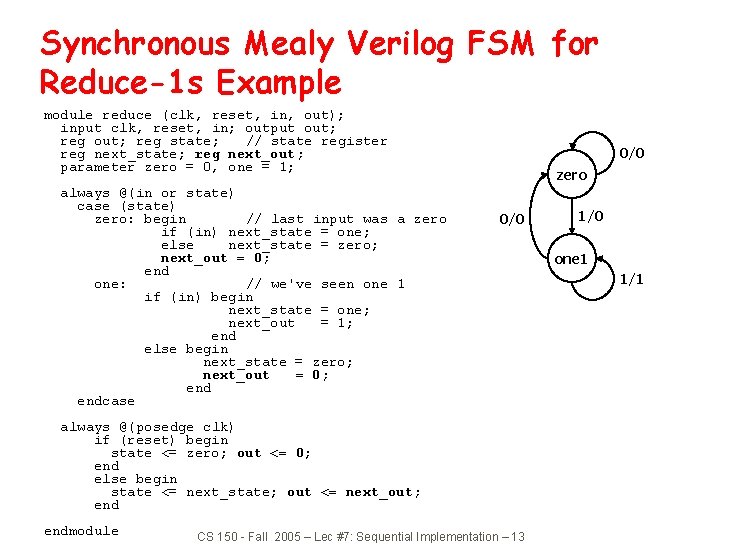

Mealy Verilog FSM for Reduce-1 s Example module reduce (clk, reset, in, out); input clk, reset, in; output out; reg state; // state register reg next_state; parameter zero = 0, one = 1; always @(in or state) case (state) zero: begin // last input was a zero if (in) next_state = one; else next_state = zero; out = 0; end one: // we've seen one 1 if (in) begin next_state = one; out = 1; end else begin next_state = zero; out = 0; endcase 0/0 zero 0/0 always @(posedge clk) if (reset) state <= zero; else state <= next_state; endmodule CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 12 1/0 one 1 1/1

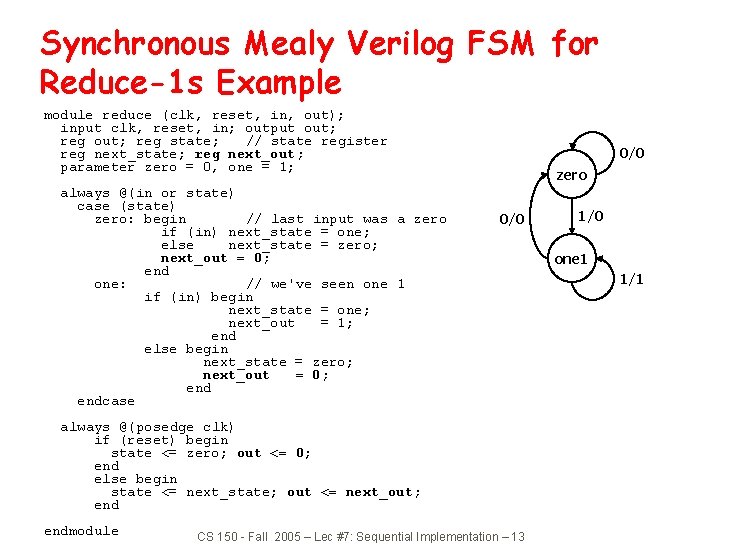

Synchronous Mealy Verilog FSM for Reduce-1 s Example module reduce (clk, reset, in, out); input clk, reset, in; output out; reg state; // state register reg next_state; reg next_out; parameter zero = 0, one = 1; always @(in or state) case (state) zero: begin // last input was a zero if (in) next_state = one; else next_state = zero; next_out = 0; end one: // we've seen one 1 if (in) begin next_state = one; next_out = 1; end else begin next_state = zero; next_out = 0; endcase 0/0 zero 0/0 always @(posedge clk) if (reset) begin state <= zero; out <= 0; end else begin state <= next_state; out <= next_out; endmodule CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 13 1/0 one 1 1/1

Announcements z Review Session, Today, 5 -6 PM, 125 Cory Hall z Examination, Wednesday, 1 -2: 30 PM, 125 Cory Hall y Five Quiz-like Questions -- Please Read Them Carefully! They are not intended to be tricky; they should contain all the information you need to answer the question correctly y No calculators or other gadgets are necessary! Don’t bring them! No blue books! All work on the sheets handed out! y Do bring pencil and eraser please! If you like to unstaple the exam pages, then bring a stapler with you! Write your name and student ID on EVERY page in case they get separated -it has happened! y Don’t forget your two-sided 8. 5” x 11” crib sheet! CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 14

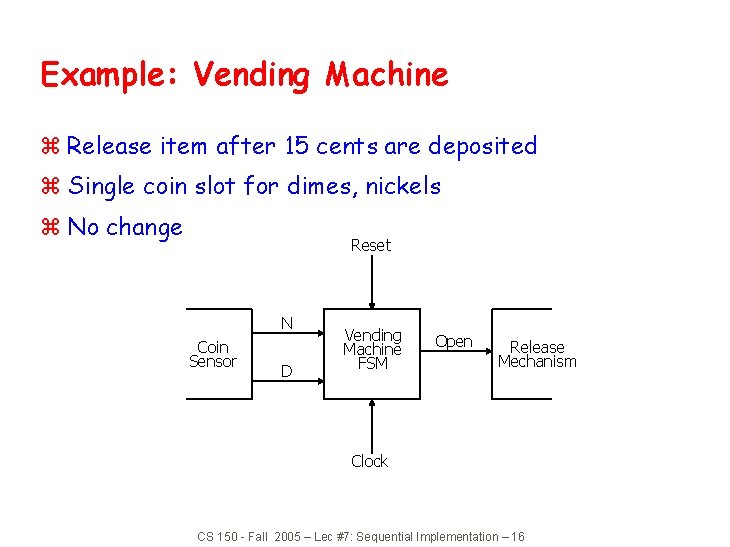

Announcements z Examination, Wednesday, 1 -2: 30 PM, 125 Cory Hall y Topics covered through last Wednesday x Combinational logic: design and optimization (K-maps up to and including 6 variables) x Implementation: Simple gates (minimum wires and gates), PLA structures (minimum unique terms), Muxes, Decoders, ROMs, (Simplified) Xilinx CLB x Sequential logic: R-S latches, flip-flops, transparent vs. edge-triggered behavior, master/slave concept x Basic Finite State Machines: Representations (state diagrams, transition tables), Moore vs. Mealy Machines, Shifters, Registers, Counters x Structural and Behavioral Verilog for combinational and sequential logic x Labs 1, 2, 3 x K&B: Chapters 1, 2 (2. 1 -2. 5), 3 (3. 1, 3. 6), 4 (4. 1, 4. 2, 4. 3), 6 (6. 1, 6. 2. 1, 6. 3), 7 (7. 1, 7. 2, 7. 3) CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 15

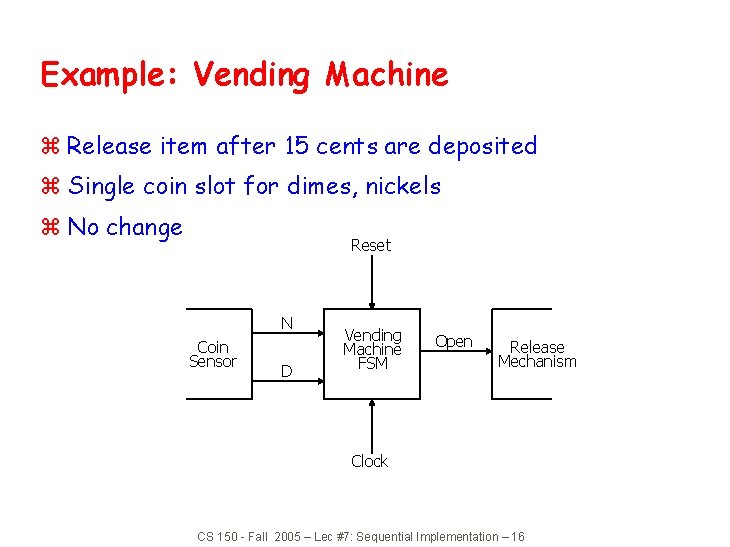

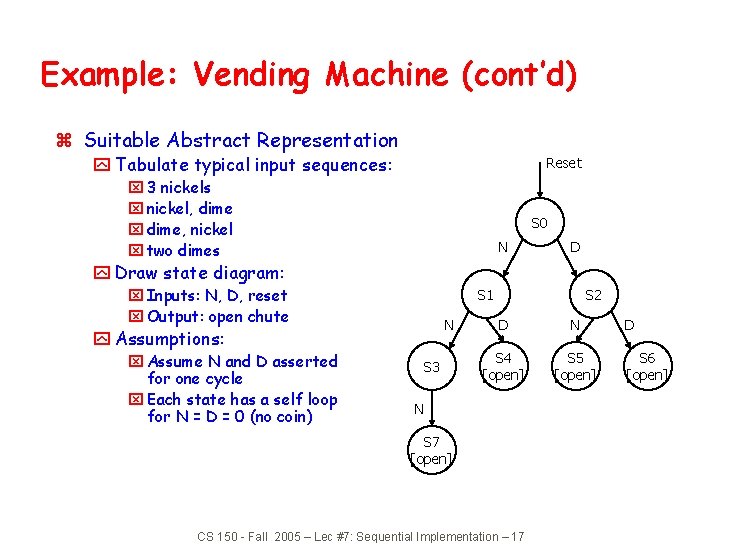

Example: Vending Machine z Release item after 15 cents are deposited z Single coin slot for dimes, nickels z No change Reset N Coin Sensor D Vending Machine FSM Open Release Mechanism Clock CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 16

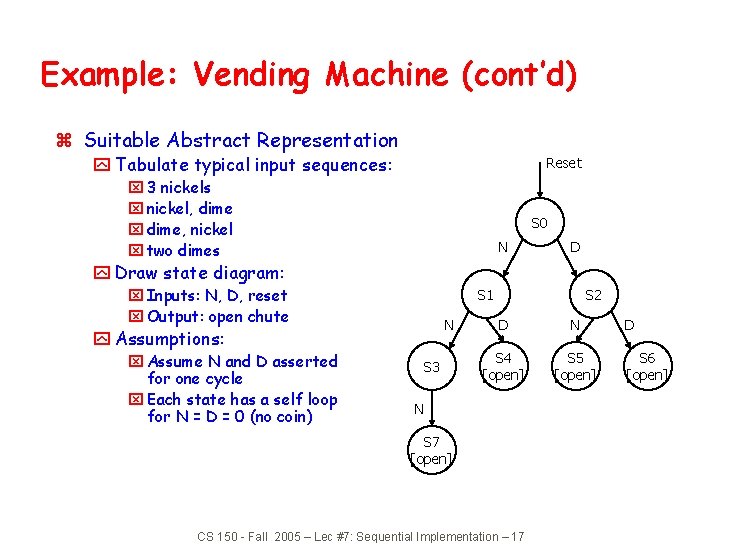

Example: Vending Machine (cont’d) z Suitable Abstract Representation y Tabulate typical input sequences: Reset x 3 nickels x nickel, dime x dime, nickel x two dimes S 0 N D y Draw state diagram: x Inputs: N, D, reset x Output: open chute S 1 N y Assumptions: x Assume N and D asserted for one cycle x Each state has a self loop for N = D = 0 (no coin) S 3 S 2 D N S 4 [open] S 5 [open] N S 7 [open] CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 17 D S 6 [open]

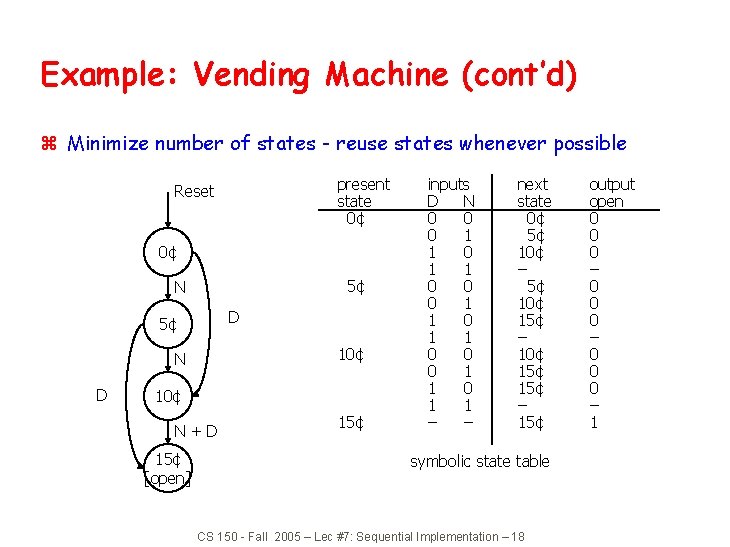

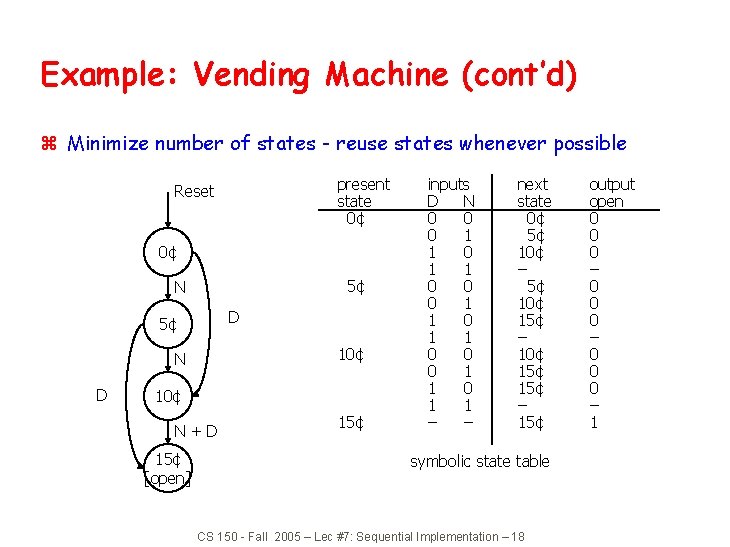

Example: Vending Machine (cont’d) z Minimize number of states - reuse states whenever possible present state 0¢ Reset 0¢ 5¢ N D 5¢ 10¢ N D 10¢ N+D 15¢ [open] 15¢ inputs D N 0 0 0 1 1 0 0 0 1 1 – – next state 0¢ 5¢ 10¢ – 5¢ 10¢ 15¢ – 15¢ symbolic state table CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 18 output open 0 0 0 – 1

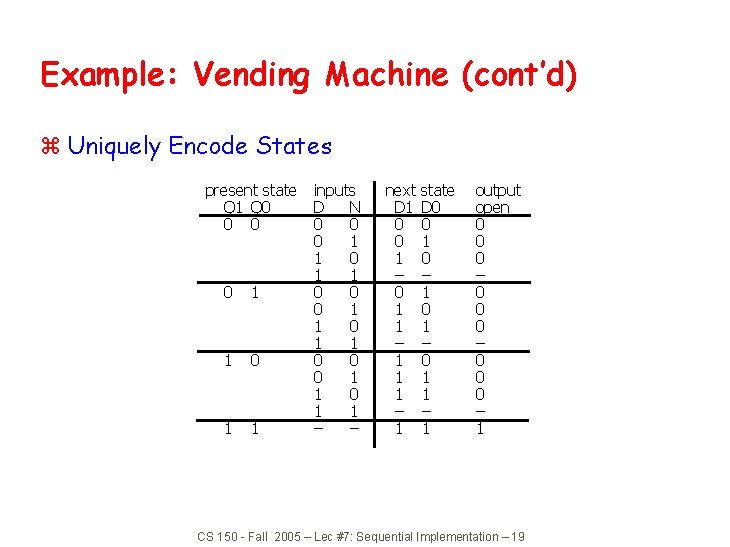

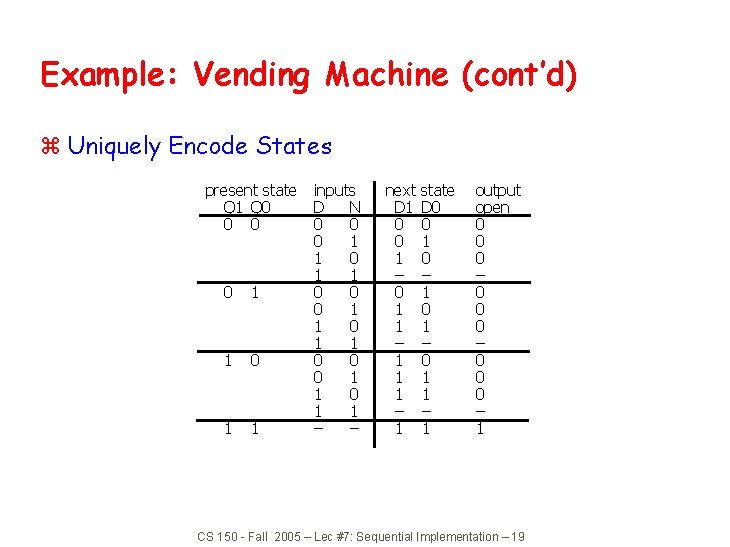

Example: Vending Machine (cont’d) z Uniquely Encode States present state inputs Q 1 Q 0 D N 0 0 0 1 1 0 1 0 0 0 1 1 1 0 0 1 1 – – next D 1 0 0 1 – 0 1 1 – 1 state D 0 0 1 0 – 1 0 1 – 0 1 1 – 1 output open 0 0 0 – 1 CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 19

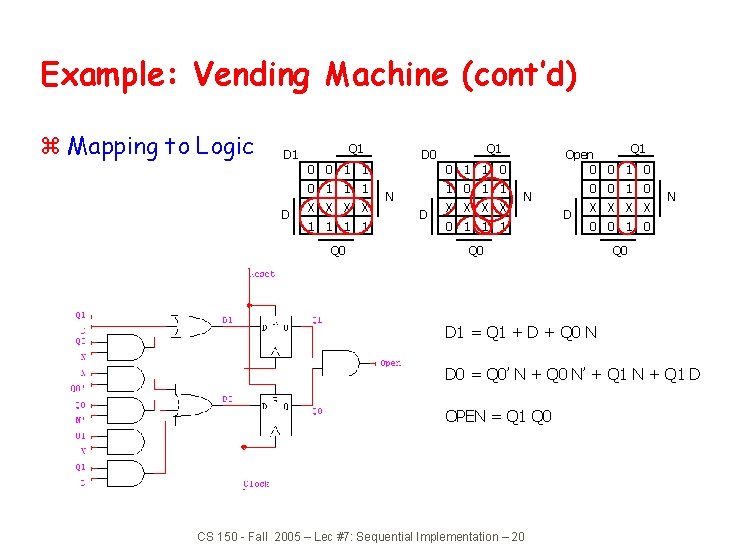

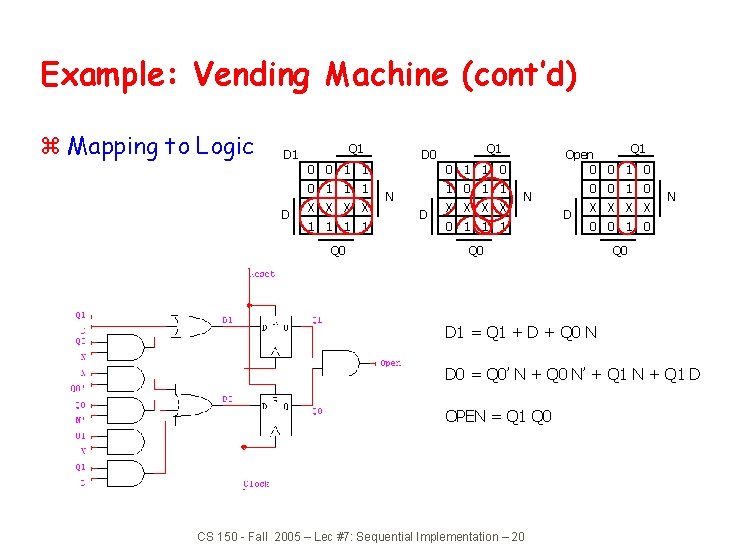

Example: Vending Machine (cont’d) z Mapping to Logic Q 1 D 1 0 0 1 1 1 D X X 1 1 Q 0 Q 1 D 0 Q 1 Open 0 0 1 1 N D X X 0 0 1 0 N 0 1 1 1 D X X N 0 0 1 0 Q 0 D 1 = Q 1 + D + Q 0 N D 0 = Q 0’ N + Q 0 N’ + Q 1 N + Q 1 D OPEN = Q 1 Q 0 CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 20

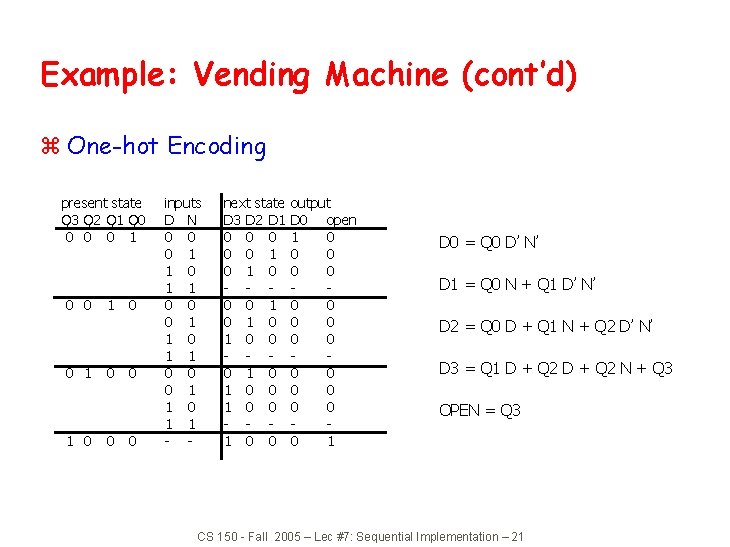

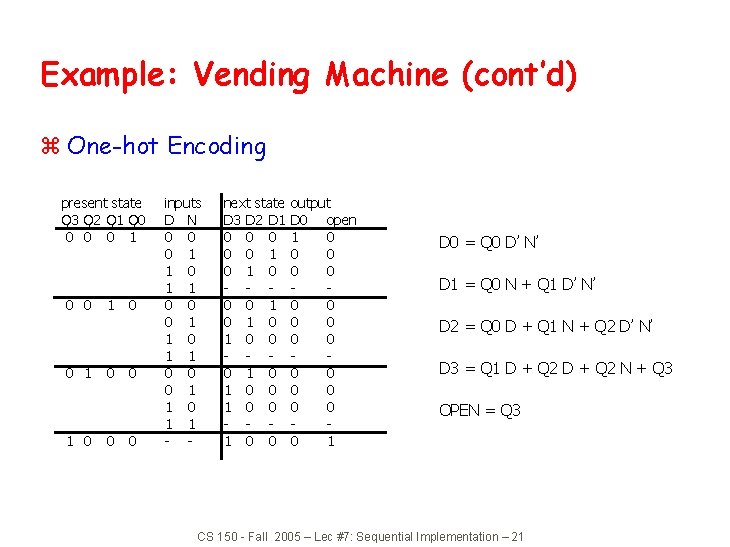

Example: Vending Machine (cont’d) z One-hot Encoding present state Q 3 Q 2 Q 1 Q 0 0 1 0 0 0 1 1 0 0 0 inputs D N 0 0 0 1 1 0 0 0 1 1 - - next state D 3 D 2 D 1 0 0 0 1 0 - - 0 0 1 0 1 0 0 - - 0 1 0 0 - - 1 0 0 output D 0 open 1 0 0 0 0 0 1 D 0 = Q 0 D’ N’ D 1 = Q 0 N + Q 1 D’ N’ D 2 = Q 0 D + Q 1 N + Q 2 D’ N’ D 3 = Q 1 D + Q 2 N + Q 3 OPEN = Q 3 CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 21

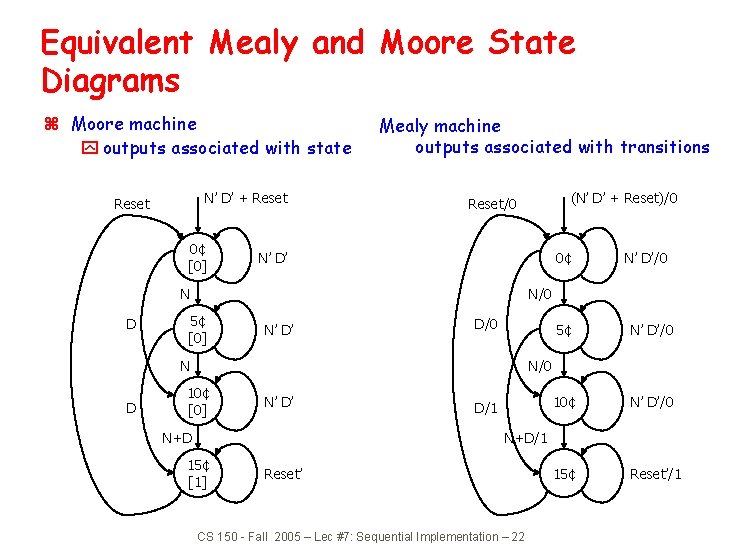

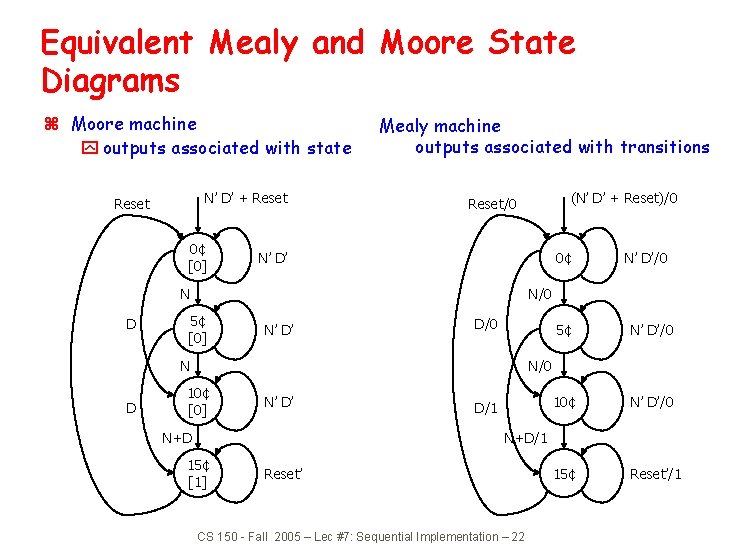

Equivalent Mealy and Moore State Diagrams z Moore machine y outputs associated with state N’ D’ + Reset 0¢ [0] Mealy machine outputs associated with transitions 0¢ N’ D’ N D N’ D’/0 N/0 5¢ [0] N’ D’ D/0 N D (N’ D’ + Reset)/0 Reset/0 5¢ N’ D’/0 10¢ N’ D’/0 15¢ Reset’/1 N/0 10¢ [0] N’ D’ N+D D/1 N+D/1 15¢ [1] Reset’ CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 22

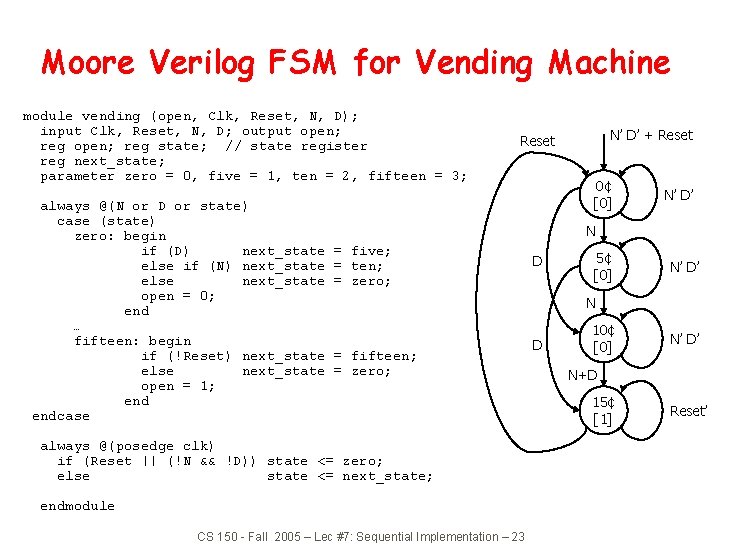

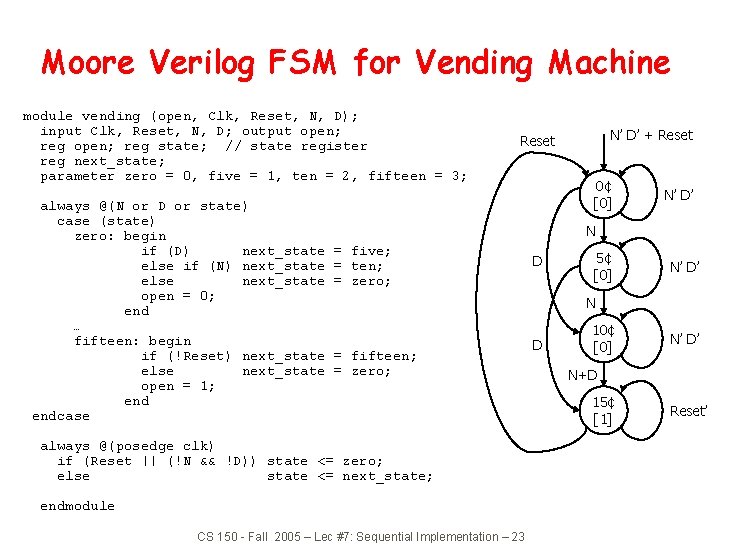

Moore Verilog FSM for Vending Machine module vending (open, Clk, Reset, N, D); input Clk, Reset, N, D; output open; reg state; // state register reg next_state; parameter zero = 0, five = 1, ten = 2, fifteen = 3; always @(N or D or state) case (state) zero: begin if (D) next_state else if (N) next_state else next_state open = 0; end … fifteen: begin if (!Reset) next_state else next_state open = 1; endcase N’ D’ + Reset 0¢ [0] N’ D’ N = five; = ten; = zero; D 5¢ [0] N’ D’ N = fifteen; = zero; always @(posedge clk) if (Reset || (!N && !D)) state <= zero; else state <= next_state; endmodule CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 23 D 10¢ [0] N’ D’ N+D 15¢ [1] Reset’

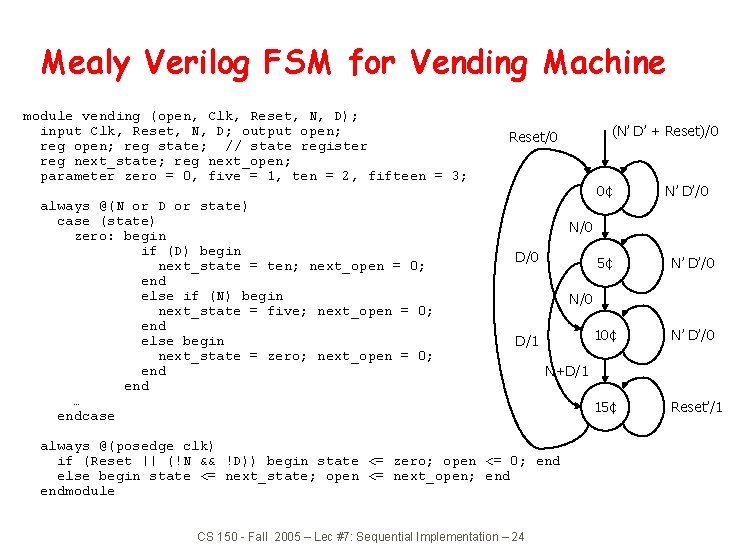

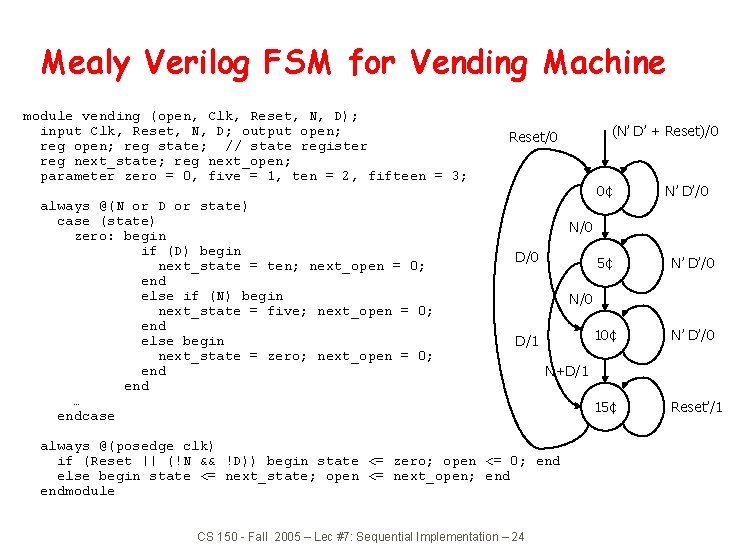

Mealy Verilog FSM for Vending Machine module vending (open, Clk, Reset, N, D); input Clk, Reset, N, D; output open; reg state; // state register reg next_state; reg next_open; parameter zero = 0, five = 1, ten = 2, fifteen = 3; always @(N or D or state) case (state) zero: begin if (D) begin next_state = ten; next_open = 0; end else if (N) begin next_state = five; next_open = 0; end else begin next_state = zero; next_open = 0; end … endcase (N’ D’ + Reset)/0 Reset/0 0¢ N’ D’/0 N/0 D/0 5¢ N’ D’/0 10¢ N’ D’/0 15¢ Reset’/1 N/0 D/1 N+D/1 always @(posedge clk) if (Reset || (!N && !D)) begin state <= zero; open <= 0; end else begin state <= next_state; open <= next_open; endmodule CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 24

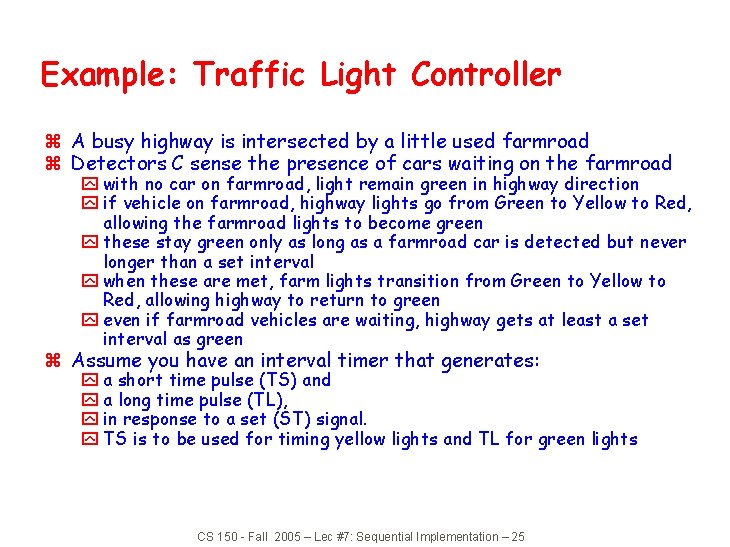

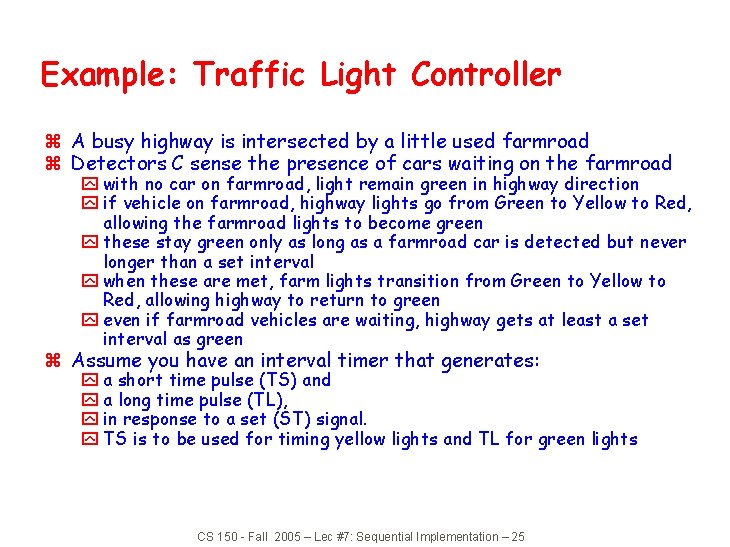

Example: Traffic Light Controller z A busy highway is intersected by a little used farmroad z Detectors C sense the presence of cars waiting on the farmroad y with no car on farmroad, light remain green in highway direction y if vehicle on farmroad, highway lights go from Green to Yellow to Red, allowing the farmroad lights to become green y these stay green only as long as a farmroad car is detected but never longer than a set interval y when these are met, farm lights transition from Green to Yellow to Red, allowing highway to return to green y even if farmroad vehicles are waiting, highway gets at least a set interval as green z Assume you have an interval timer that generates: y a short time pulse (TS) and y a long time pulse (TL), y in response to a set (ST) signal. y TS is to be used for timing yellow lights and TL for green lights CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 25

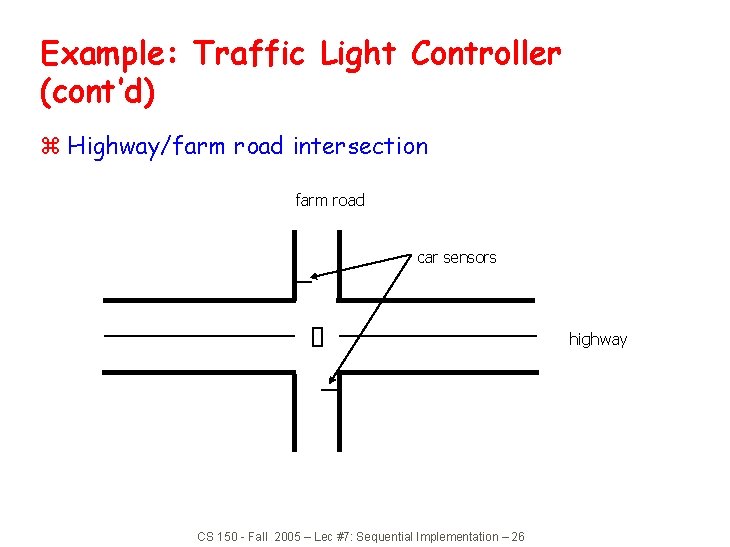

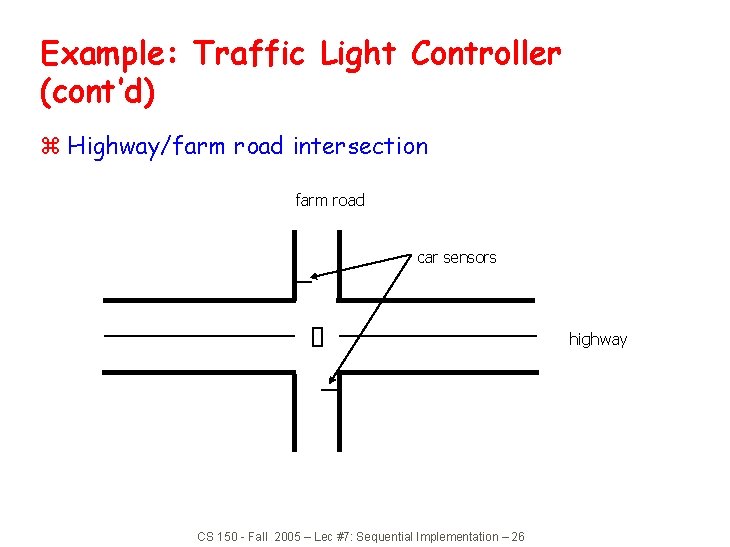

Example: Traffic Light Controller (cont’d) z Highway/farm road intersection farm road car sensors highway CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 26

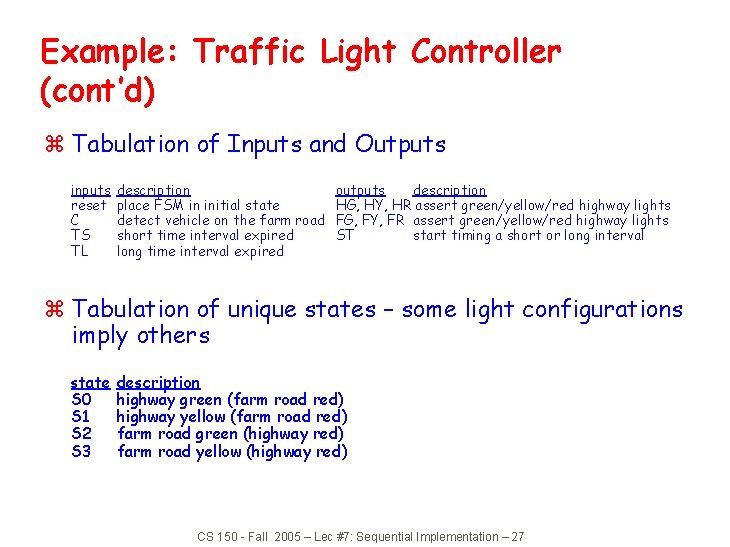

Example: Traffic Light Controller (cont’d) z Tabulation of Inputs and Outputs inputs reset C TS TL description place FSM in initial state detect vehicle on the farm road short time interval expired long time interval expired outputs description HG, HY, HR assert green/yellow/red highway lights FG, FY, FR assert green/yellow/red highway lights ST start timing a short or long interval z Tabulation of unique states – some light configurations imply others state S 0 S 1 S 2 S 3 description highway green (farm road red) highway yellow (farm road red) farm road green (highway red) farm road yellow (highway red) CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 27

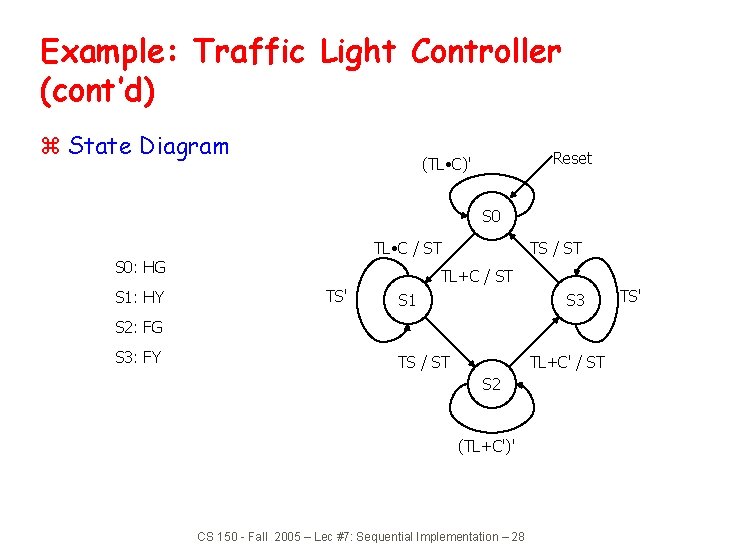

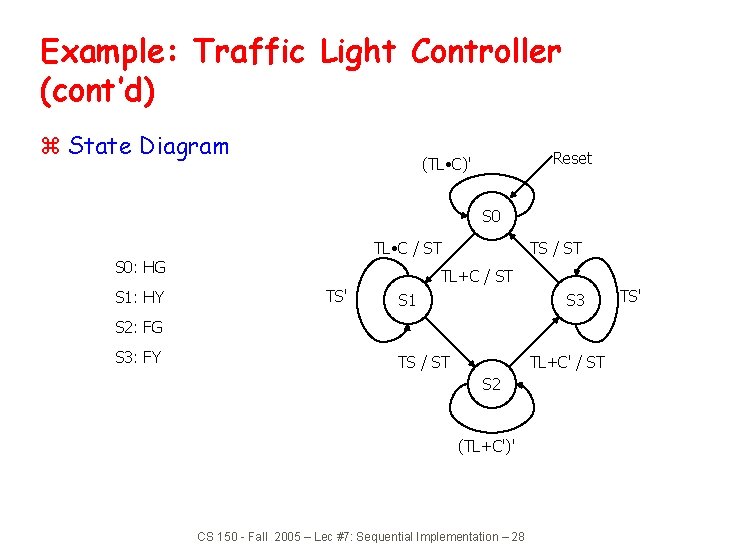

Example: Traffic Light Controller (cont’d) z State Diagram Reset (TL • C)' S 0 TL • C / ST S 0: HG S 1: HY TS / ST TL+C / ST TS' S 1 S 3 S 2: FG S 3: FY TS / ST TL+C' / ST S 2 (TL+C')' CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 28 TS'

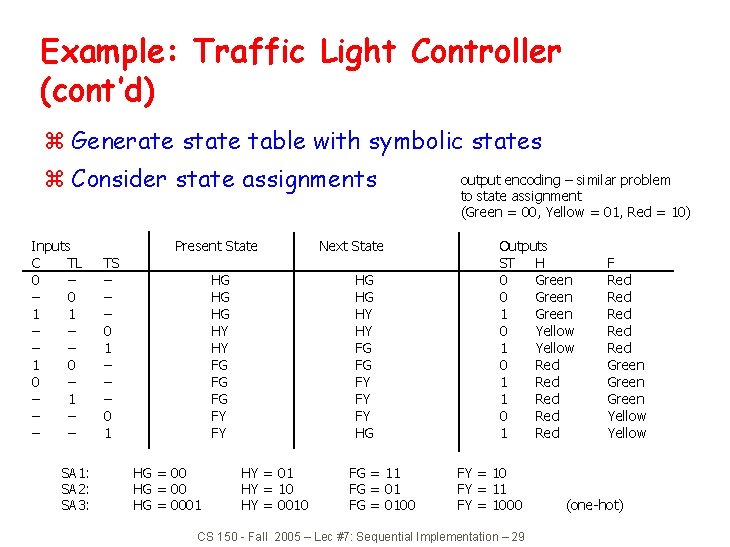

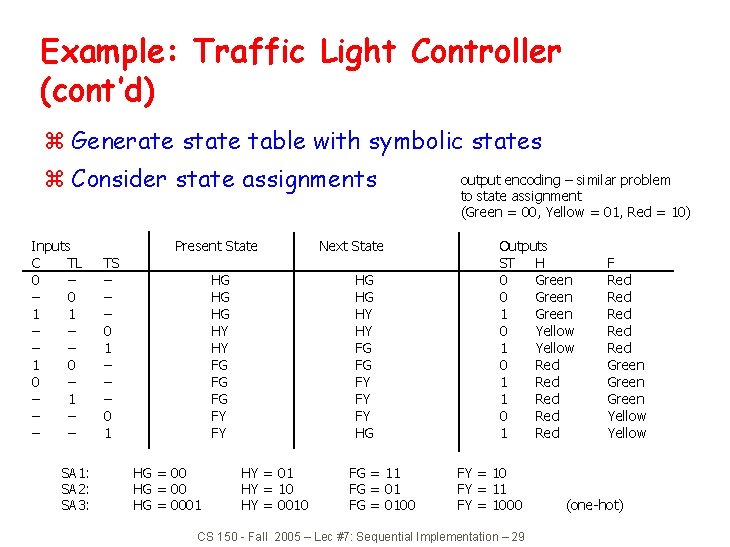

Example: Traffic Light Controller (cont’d) z Generate state table with symbolic states z Consider state assignments Inputs C TL 0 – – 0 1 1 – – 1 0 0 – – 1 – – SA 1: SA 2: SA 3: Present State TS – – – 0 1 HG HG HG HY HY FG FG FG FY FY HG = 0001 Next State HG HG HY HY FG FG FY FY FY HG HY = 01 HY = 10 HY = 0010 FG = 11 FG = 0100 output encoding – similar problem to state assignment (Green = 00, Yellow = 01, Red = 10) Outputs ST H 0 Green 1 Green 0 Yellow 1 Yellow 0 Red 1 Red FY = 10 FY = 11 FY = 1000 CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 29 F Red Red Red Green Yellow (one-hot)

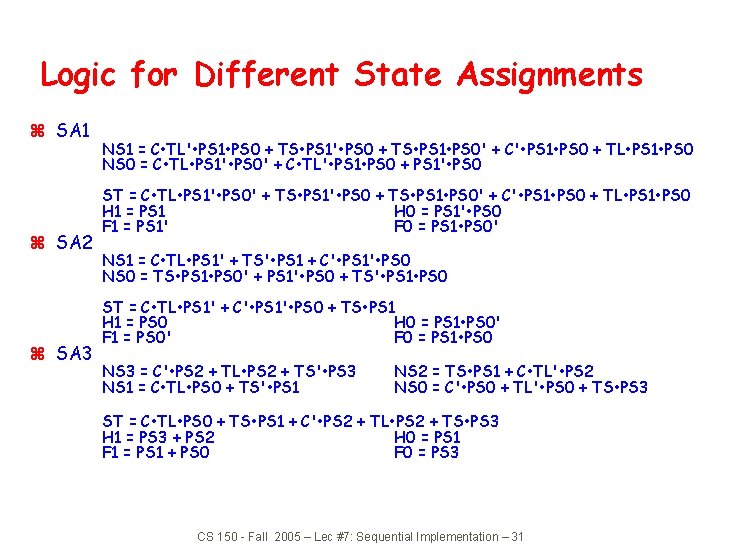

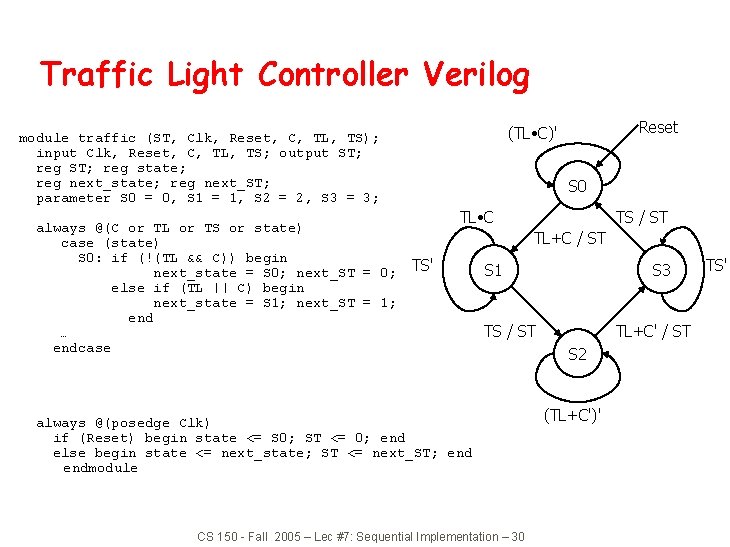

Traffic Light Controller Verilog always @(C or TL or TS or state) case (state) S 0: if (!(TL && C)) begin next_state = S 0; next_ST = 0; else if (TL || C) begin next_state = S 1; next_ST = 1; end … endcase Reset (TL • C)' module traffic (ST, Clk, Reset, C, TL, TS); input Clk, Reset, C, TL, TS; output ST; reg state; reg next_ST; parameter S 0 = 0, S 1 = 1, S 2 = 2, S 3 = 3; S 0 TL • C TS / ST TL+C / ST TS' S 1 S 3 TS / ST always @(posedge Clk) if (Reset) begin state <= S 0; ST <= 0; end else begin state <= next_state; ST <= next_ST; endmodule CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 30 TL+C' / ST S 2 (TL+C')' TS'

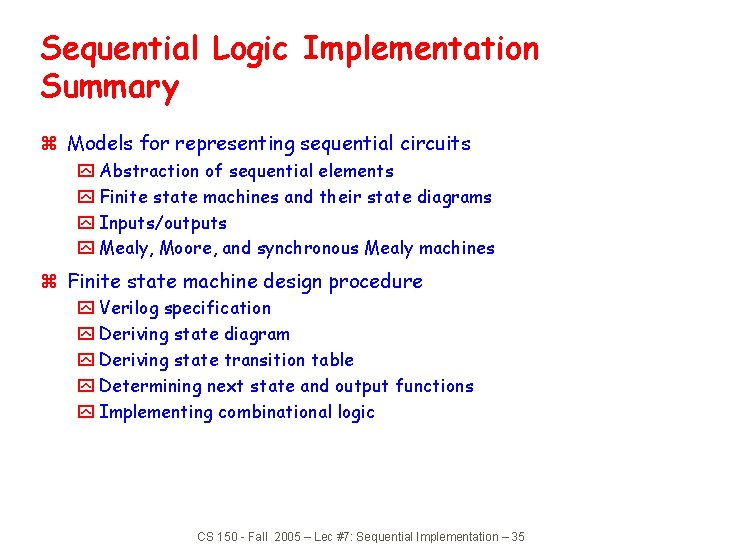

Logic for Different State Assignments z SA 1 z SA 2 z SA 3 NS 1 = C • TL' • PS 1 • PS 0 + TS • PS 1' • PS 0 + TS • PS 1 • PS 0' + C' • PS 1 • PS 0 + TL • PS 1 • PS 0 NS 0 = C • TL • PS 1' • PS 0' + C • TL' • PS 1 • PS 0 + PS 1' • PS 0 ST = C • TL • PS 1' • PS 0' + TS • PS 1' • PS 0 + TS • PS 1 • PS 0' + C' • PS 1 • PS 0 + TL • PS 1 • PS 0 H 1 = PS 1 H 0 = PS 1' • PS 0 F 1 = PS 1' F 0 = PS 1 • PS 0' NS 1 = C • TL • PS 1' + TS' • PS 1 + C' • PS 1' • PS 0 NS 0 = TS • PS 1 • PS 0' + PS 1' • PS 0 + TS' • PS 1 • PS 0 ST = C • TL • PS 1' + C' • PS 1' • PS 0 + TS • PS 1 H 1 = PS 0 H 0 = PS 1 • PS 0' F 1 = PS 0' F 0 = PS 1 • PS 0 NS 3 = C' • PS 2 + TL • PS 2 + TS' • PS 3 NS 1 = C • TL • PS 0 + TS' • PS 1 NS 2 = TS • PS 1 + C • TL' • PS 2 NS 0 = C' • PS 0 + TL' • PS 0 + TS • PS 3 ST = C • TL • PS 0 + TS • PS 1 + C' • PS 2 + TL • PS 2 + TS • PS 3 H 1 = PS 3 + PS 2 H 0 = PS 1 F 1 = PS 1 + PS 0 F 0 = PS 3 CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 31

Sequential Logic Implementation Summary z Models for representing sequential circuits y Abstraction of sequential elements y Finite state machines and their state diagrams y Inputs/outputs y Mealy, Moore, and synchronous Mealy machines z Finite state machine design procedure y Verilog specification y Deriving state diagram y Deriving state transition table y Determining next state and output functions y Implementing combinational logic CS 150 - Fall 2005 – Lec #7: Sequential Implementation – 35