SEQUENTIAL LOGIC Digital Integrated Circuits Sequential Logic Prentice

- Slides: 29

SEQUENTIAL LOGIC Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

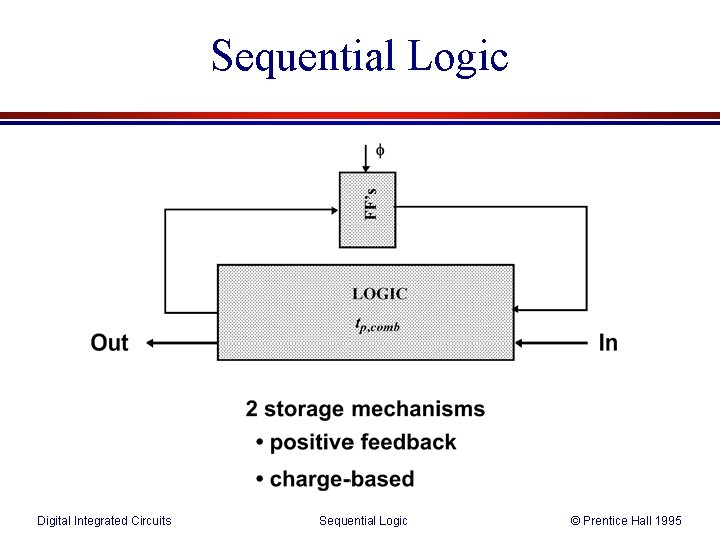

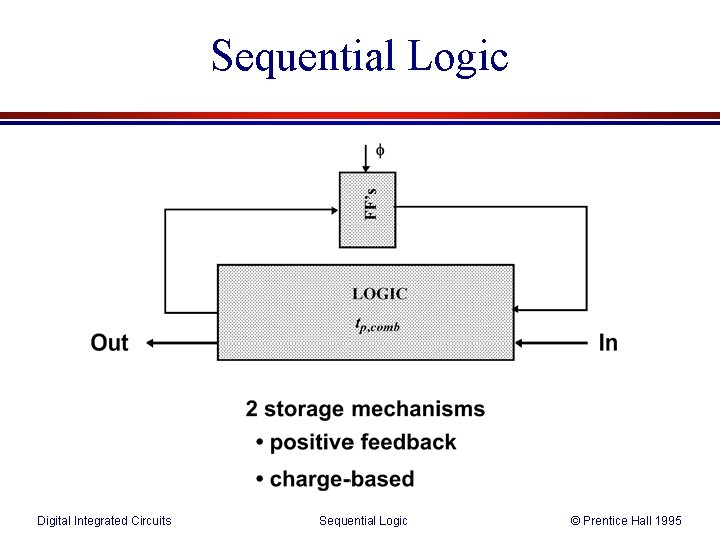

Sequential Logic Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

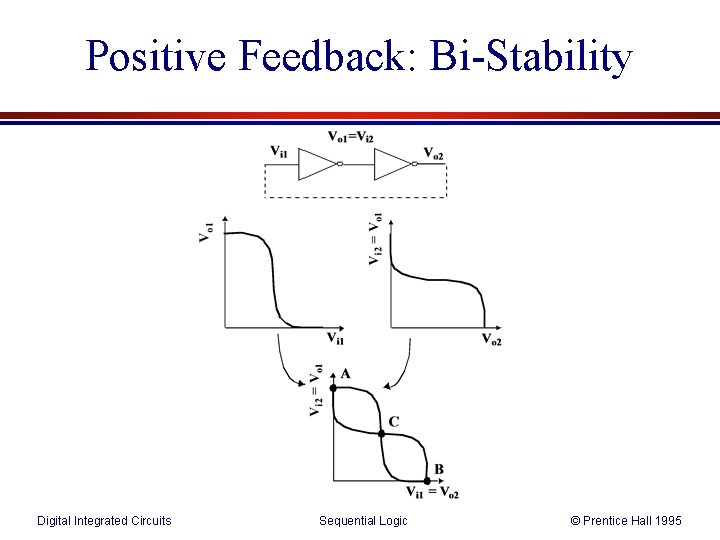

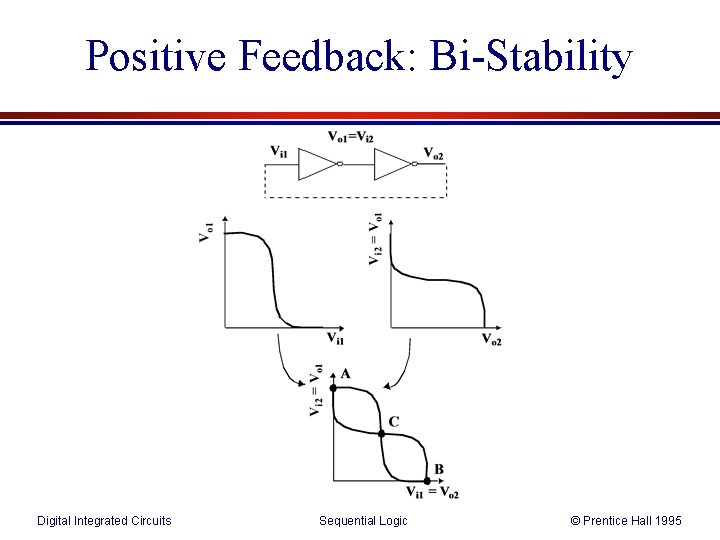

Positive Feedback: Bi-Stability Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

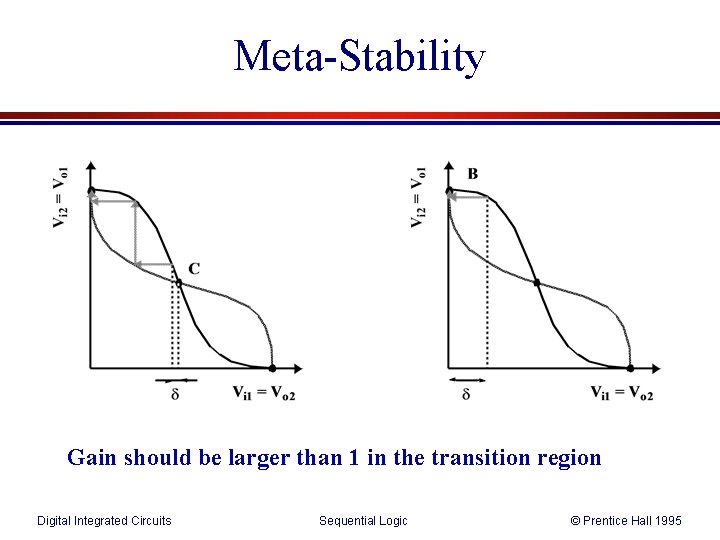

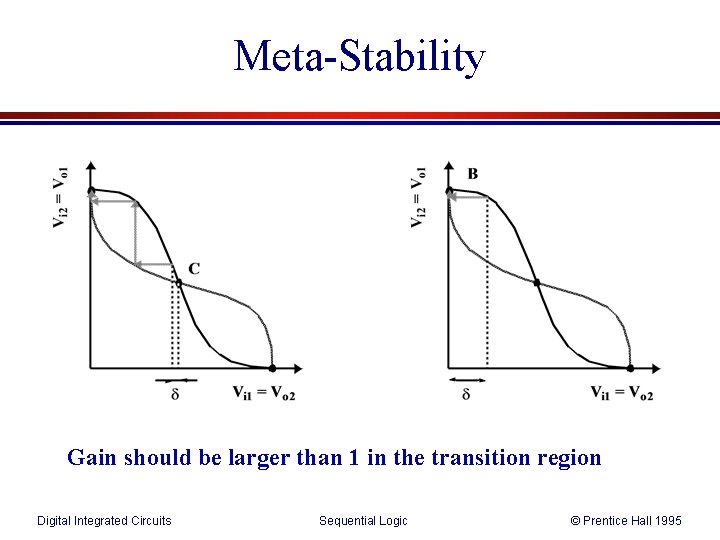

Meta-Stability Gain should be larger than 1 in the transition region Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

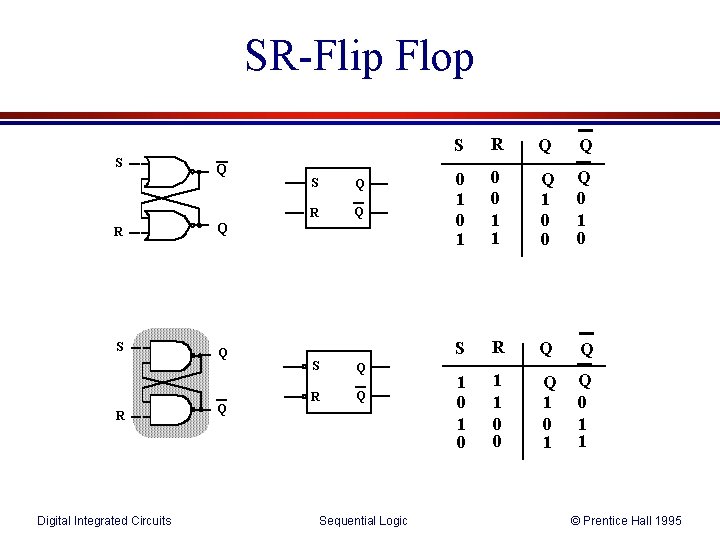

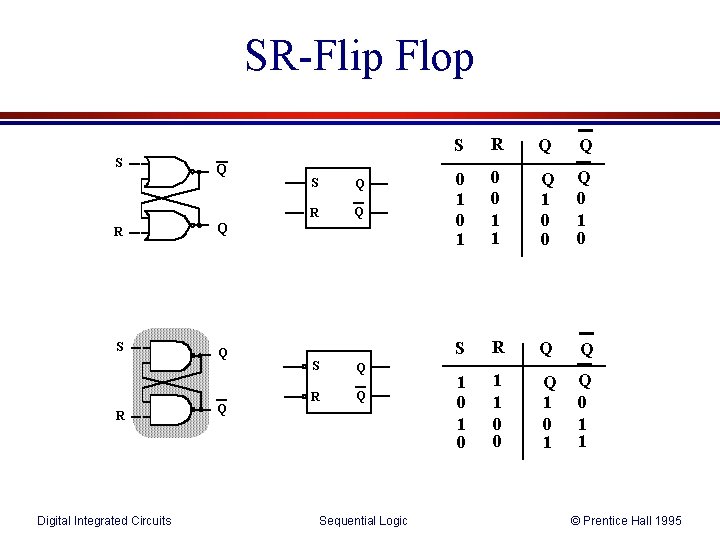

SR-Flip Flop S Q R Q S Q R Digital Integrated Circuits Q S Q R Q Sequential Logic S R Q Q 0 1 0 0 1 1 Q 1 0 0 Q 0 1 0 S R Q Q 1 0 1 1 0 0 Q 1 0 1 Q 0 1 1 © Prentice Hall 1995

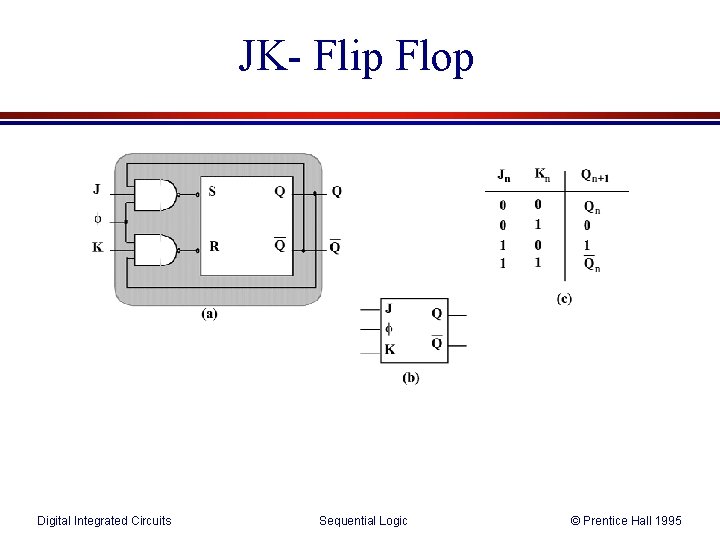

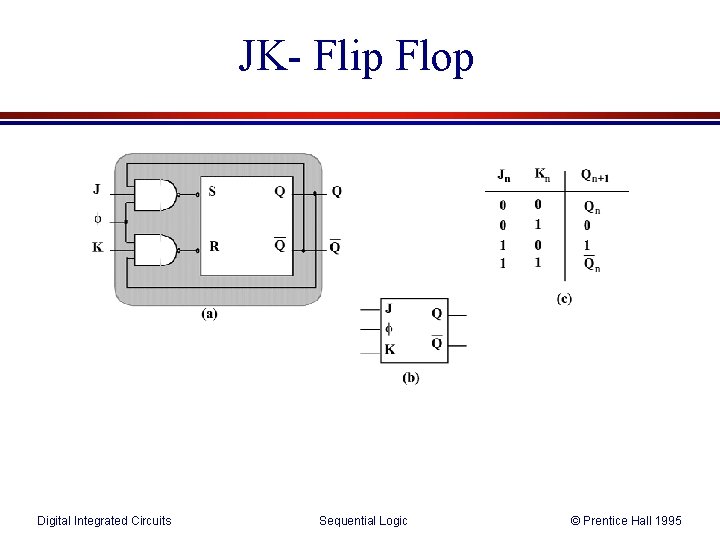

JK- Flip Flop Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

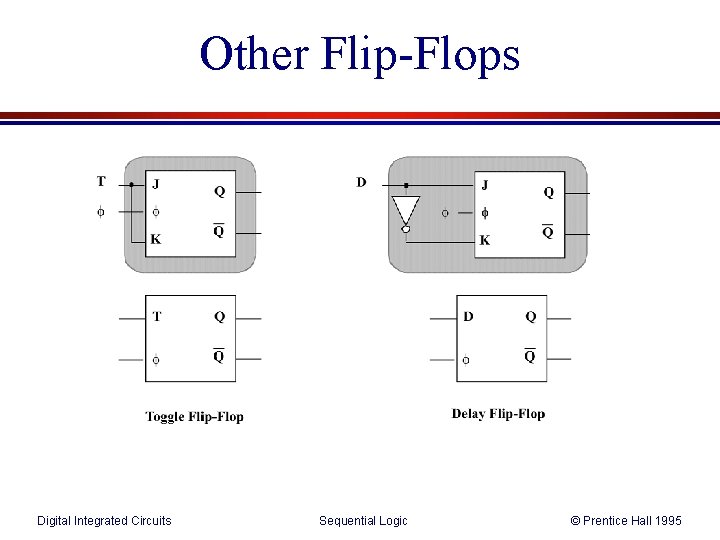

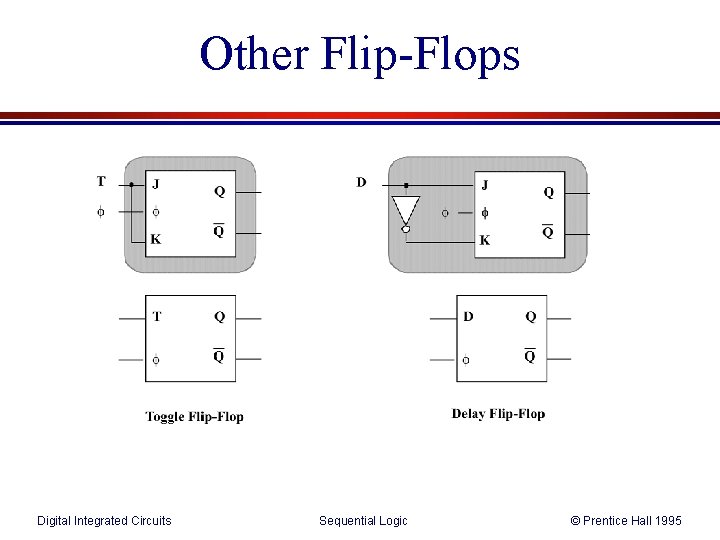

Other Flip-Flops Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

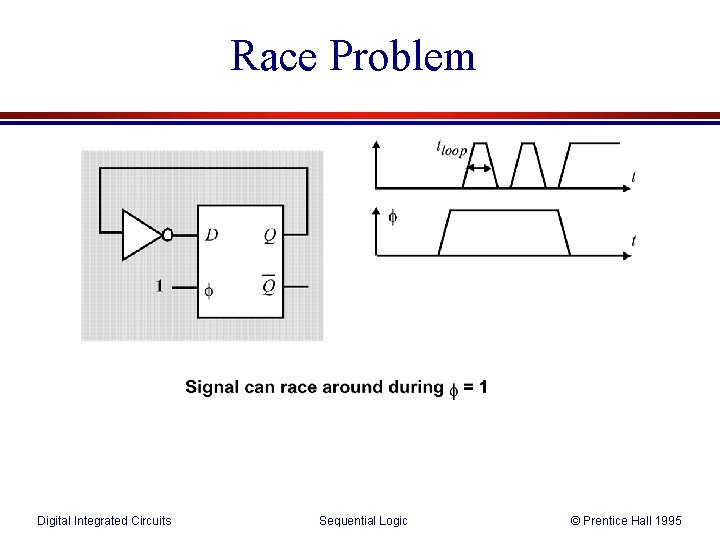

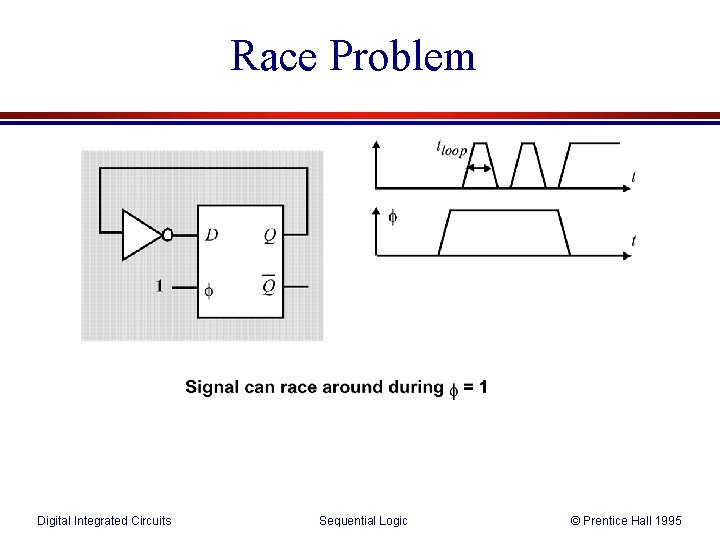

Race Problem Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

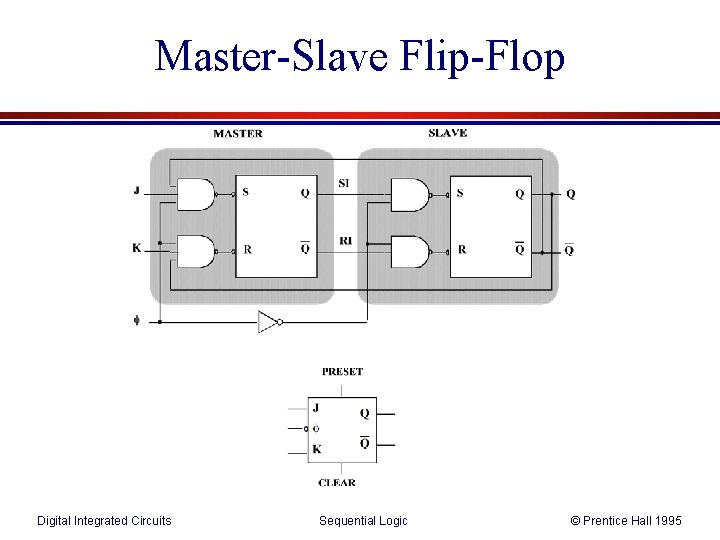

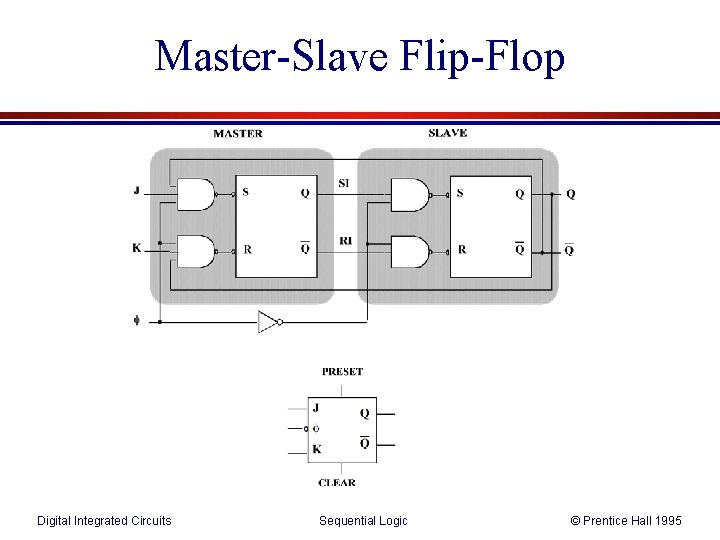

Master-Slave Flip-Flop Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

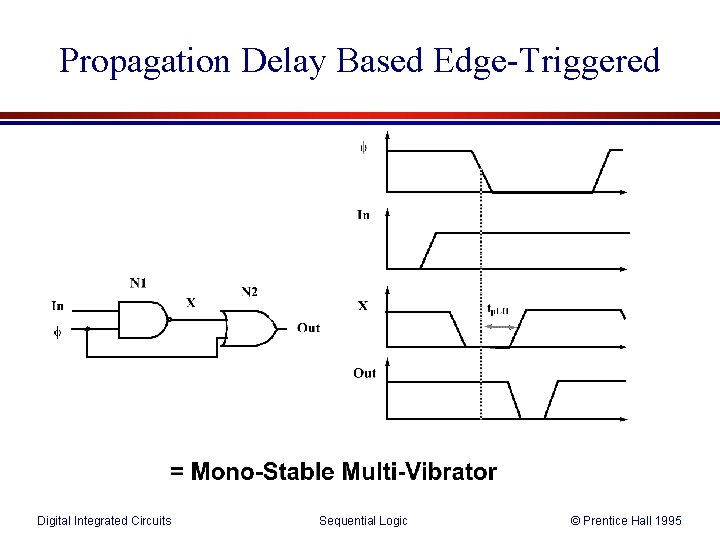

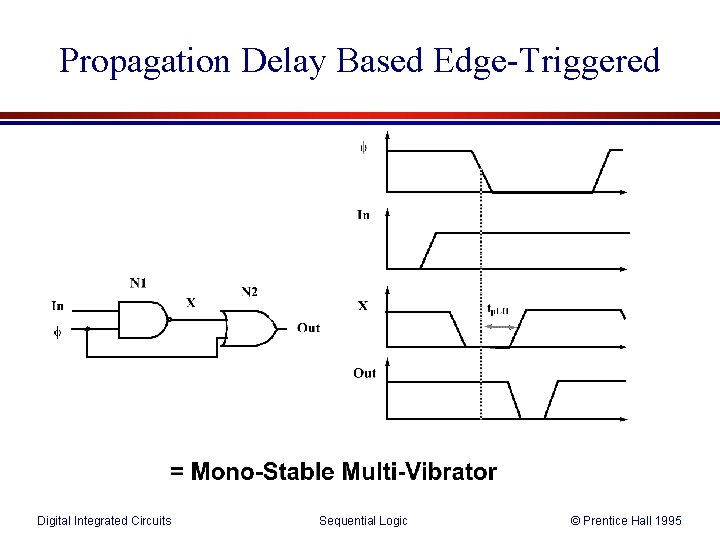

Propagation Delay Based Edge-Triggered Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

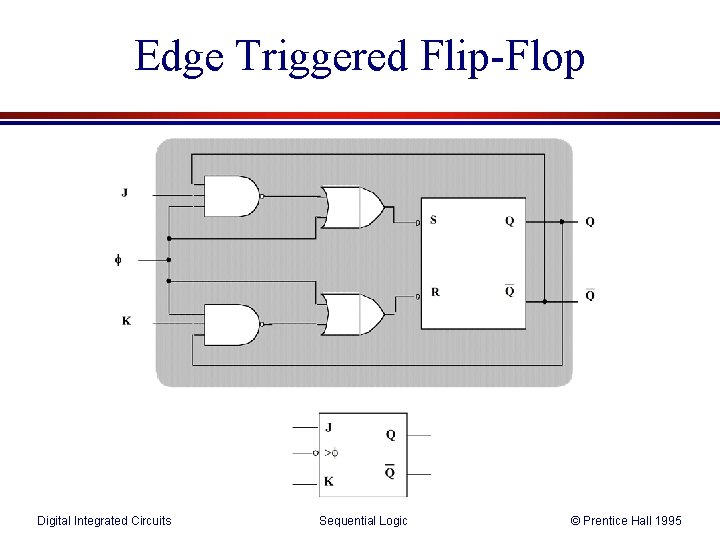

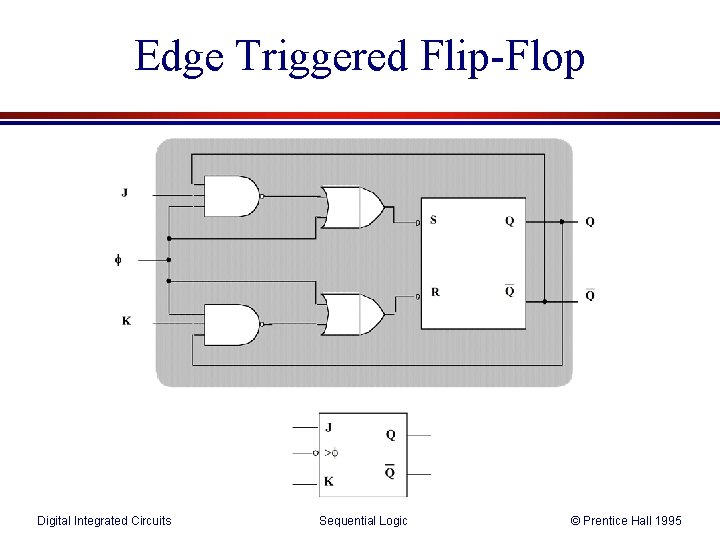

Edge Triggered Flip-Flop Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

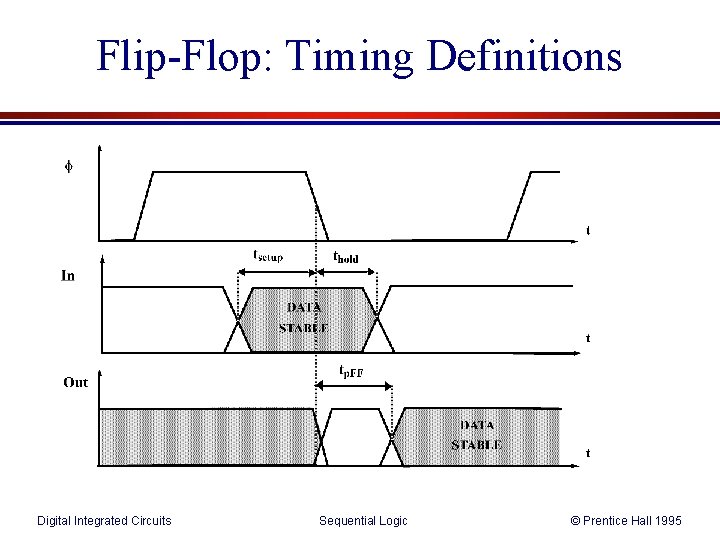

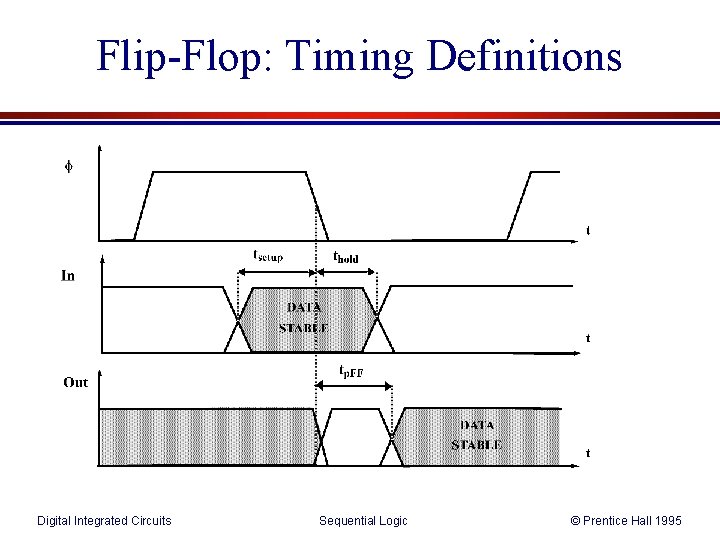

Flip-Flop: Timing Definitions Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

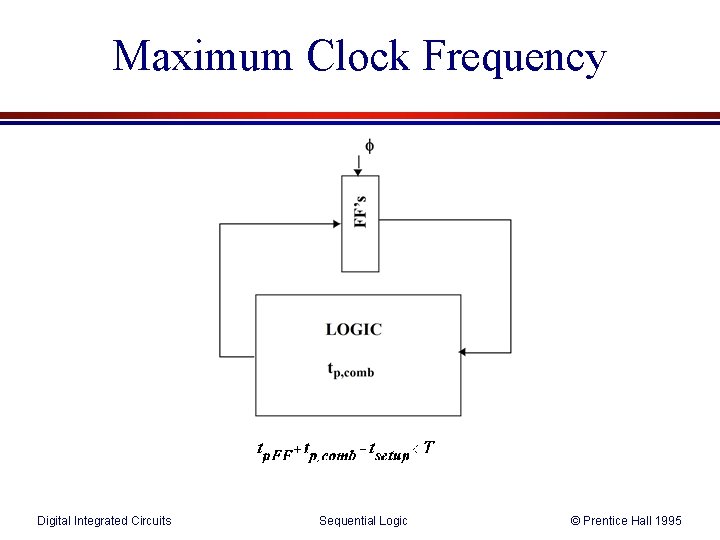

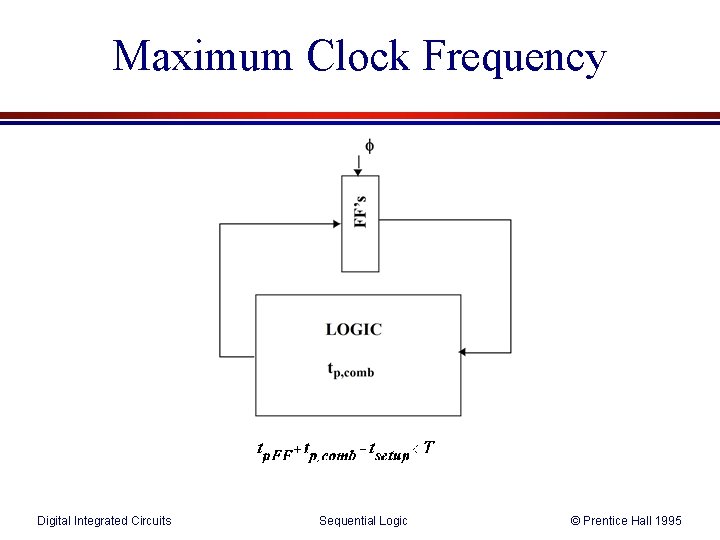

Maximum Clock Frequency Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

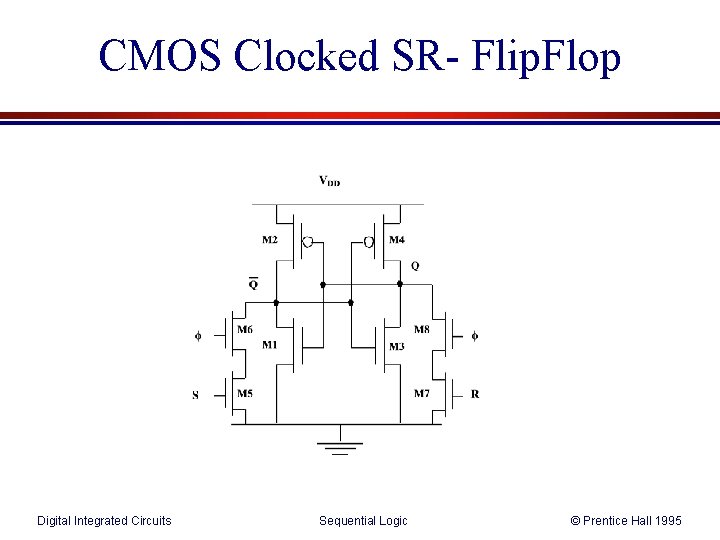

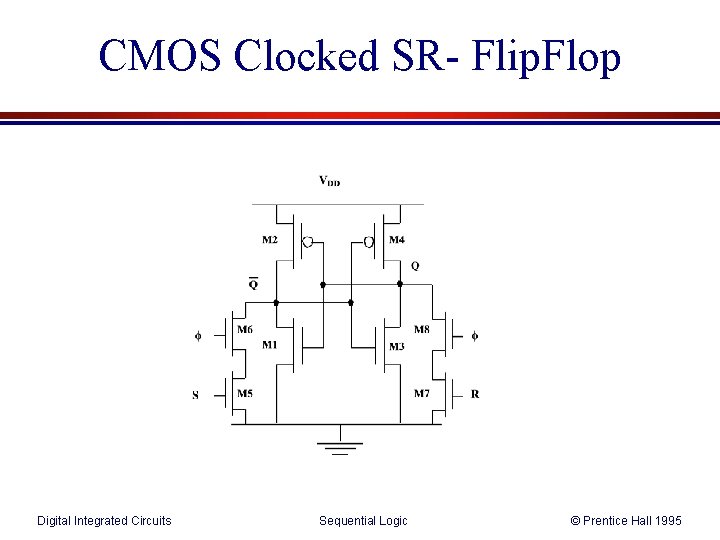

CMOS Clocked SR- Flip. Flop Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

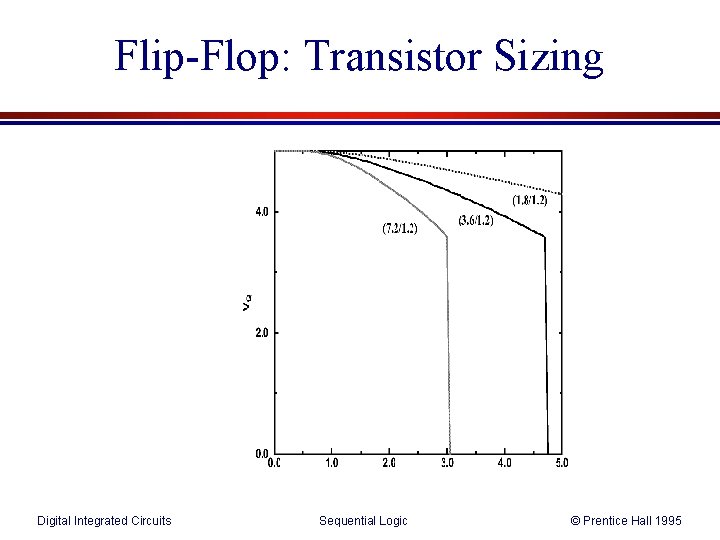

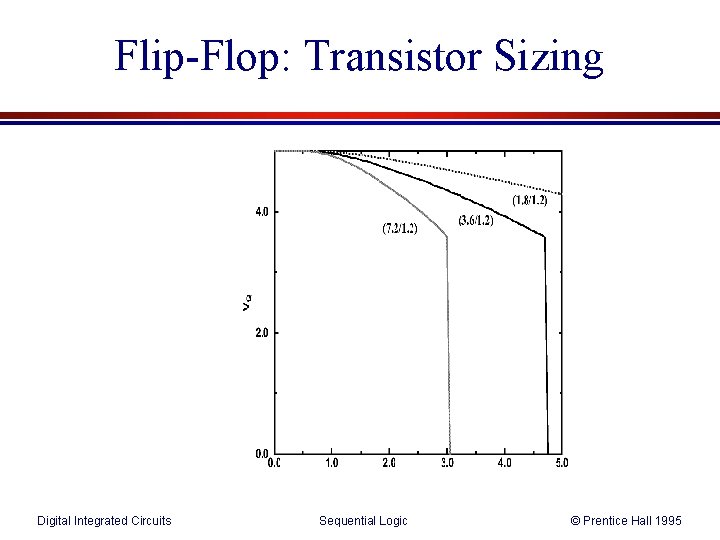

Flip-Flop: Transistor Sizing Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

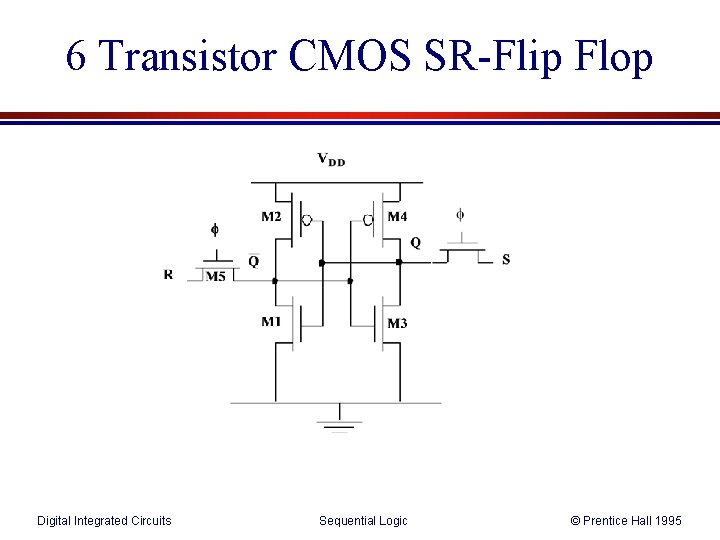

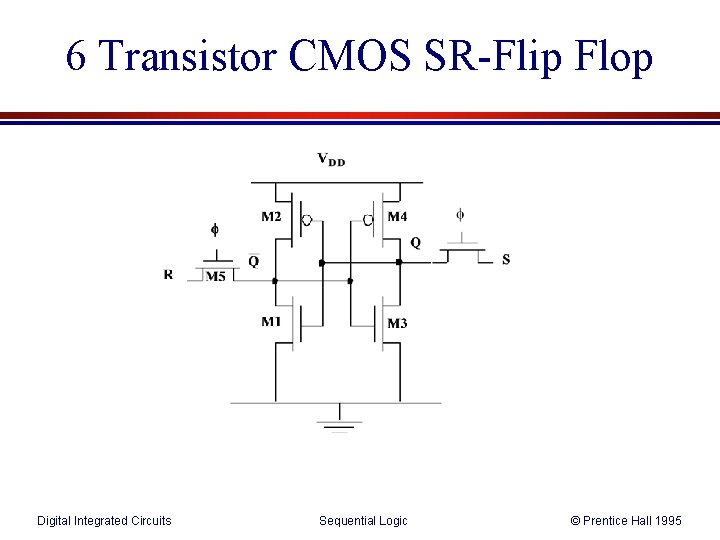

6 Transistor CMOS SR-Flip Flop Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

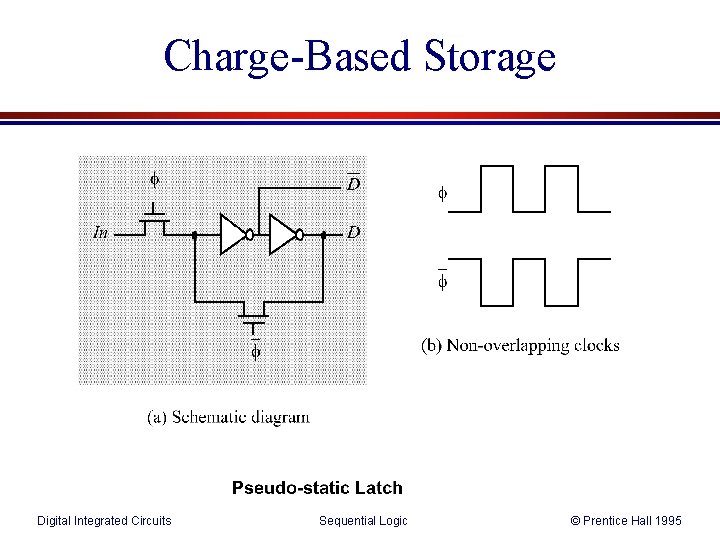

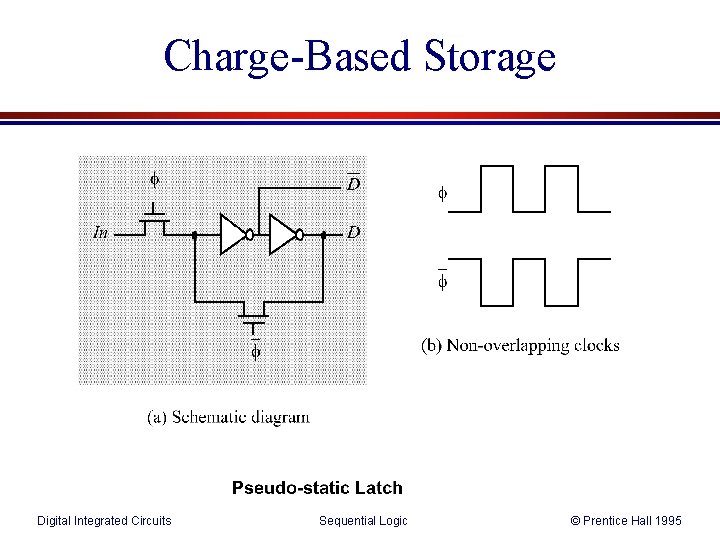

Charge-Based Storage Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

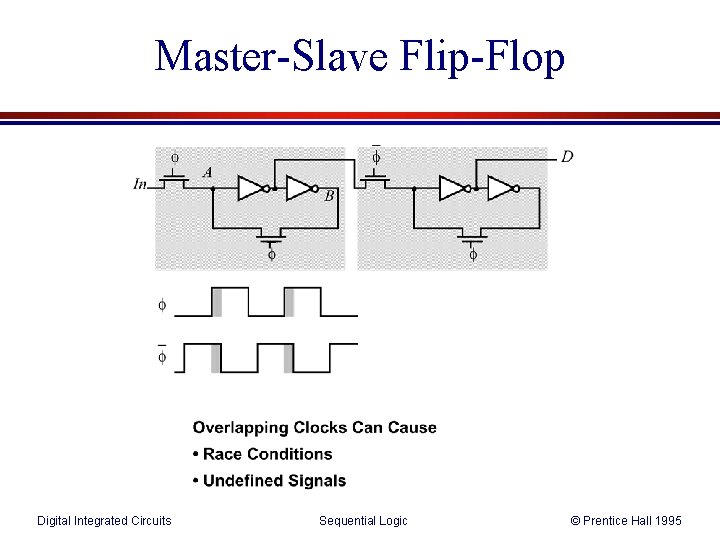

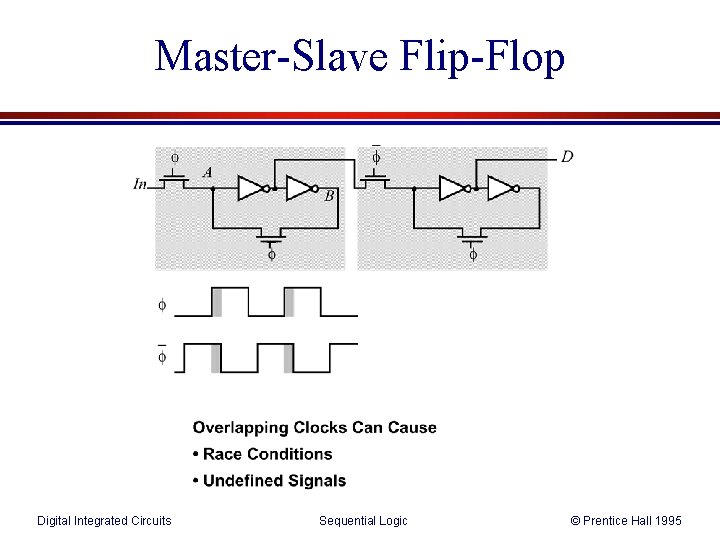

Master-Slave Flip-Flop Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

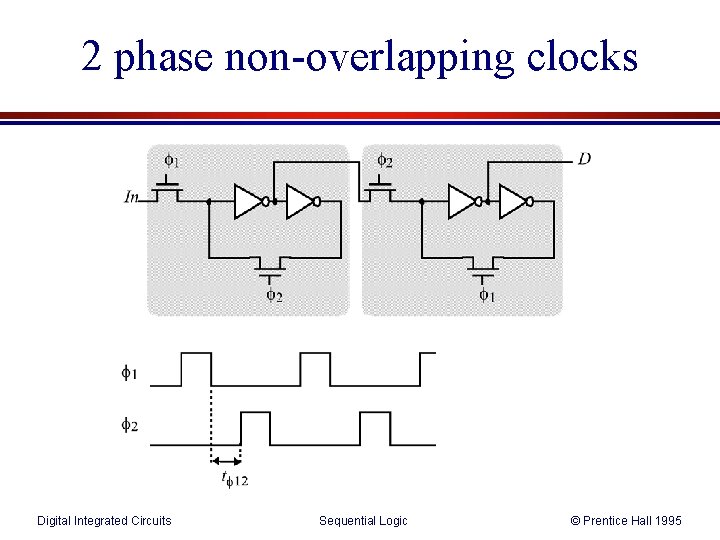

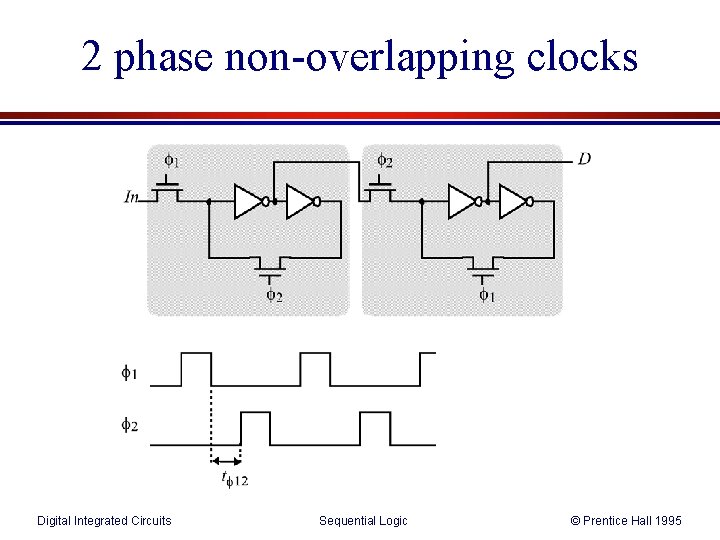

2 phase non-overlapping clocks Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

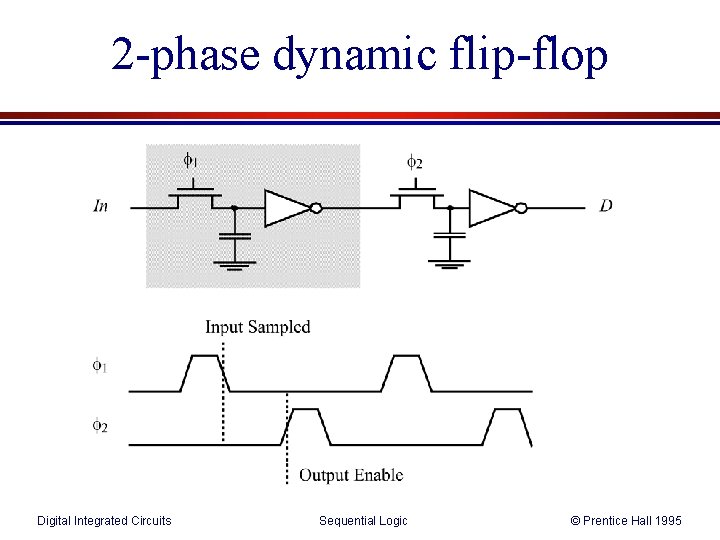

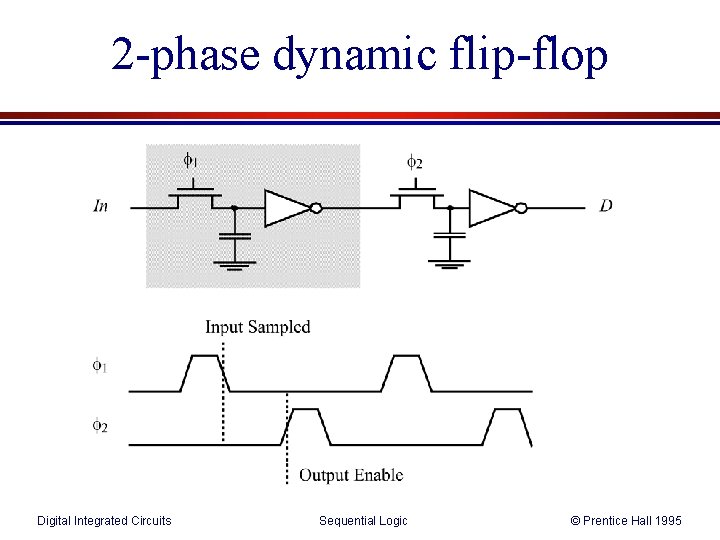

2 -phase dynamic flip-flop Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

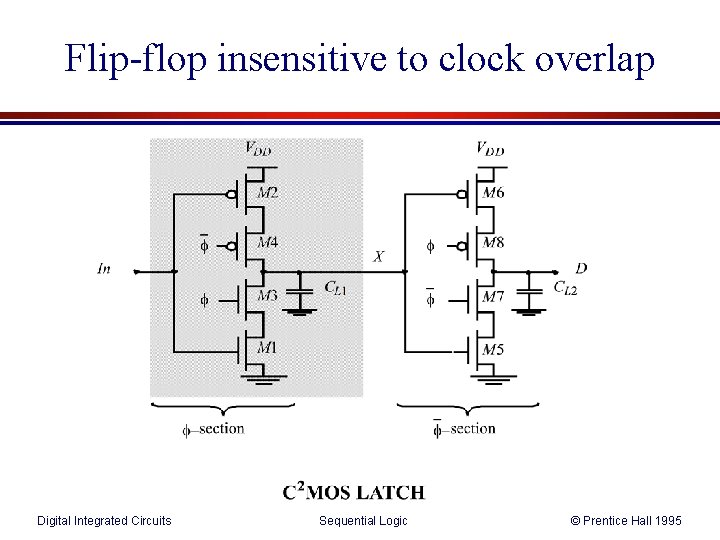

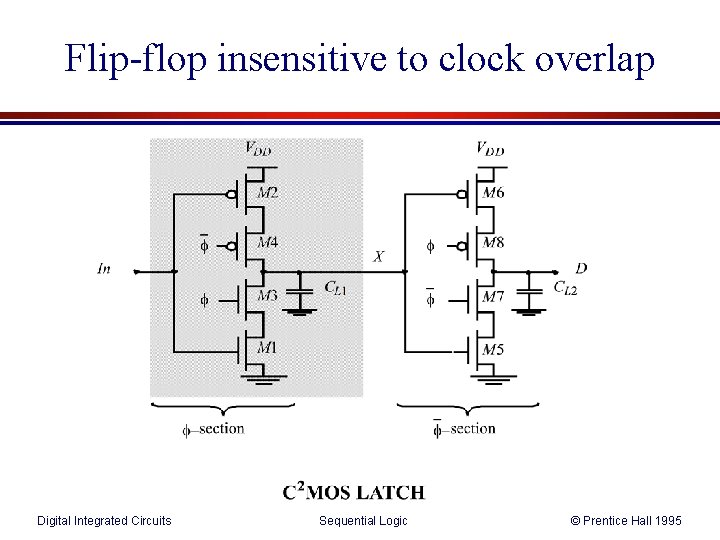

Flip-flop insensitive to clock overlap Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

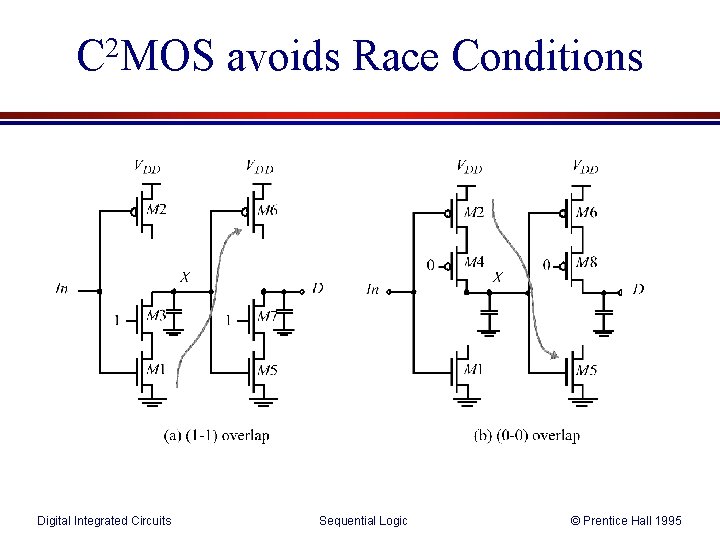

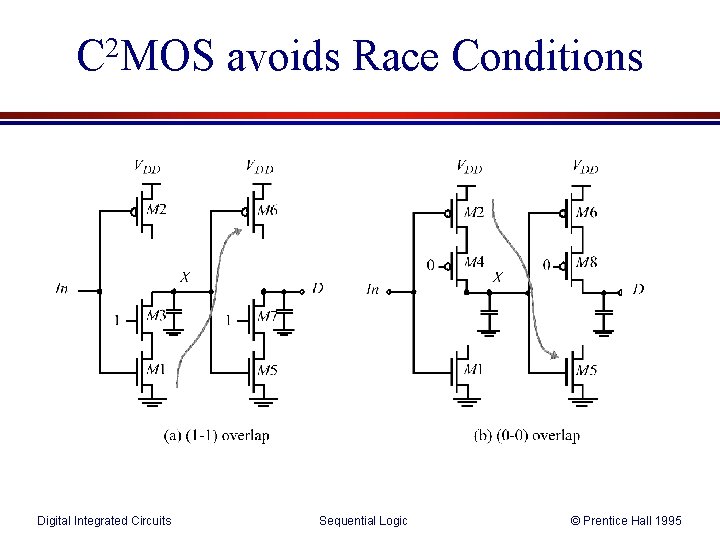

C 2 MOS avoids Race Conditions Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

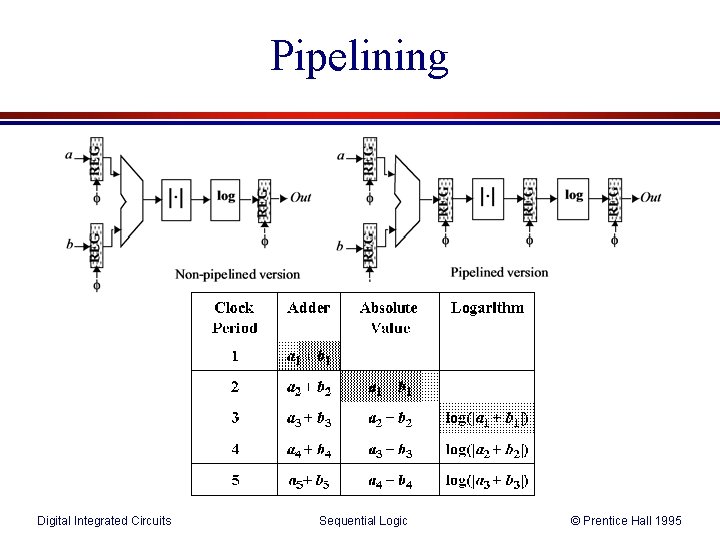

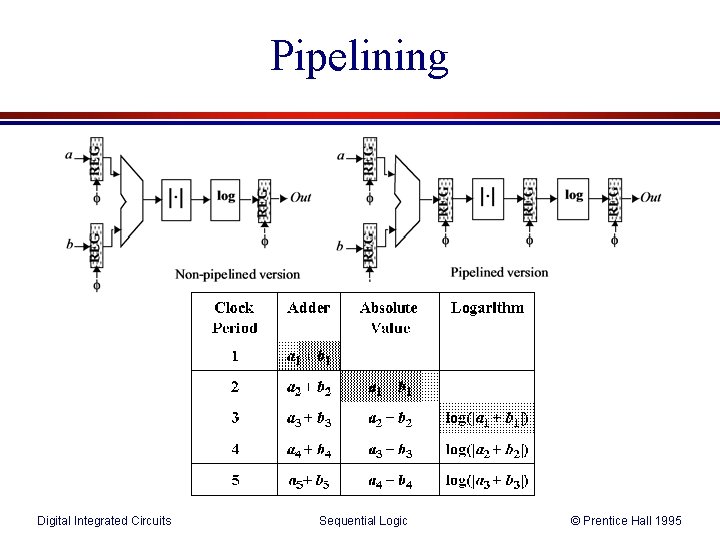

Pipelining Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

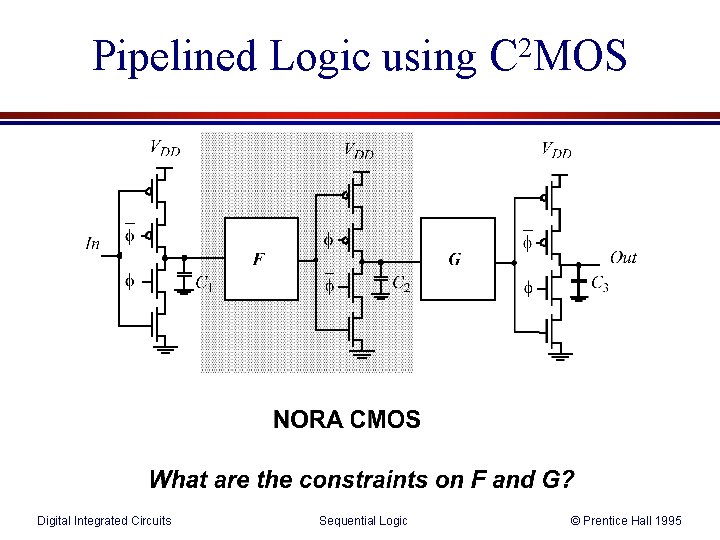

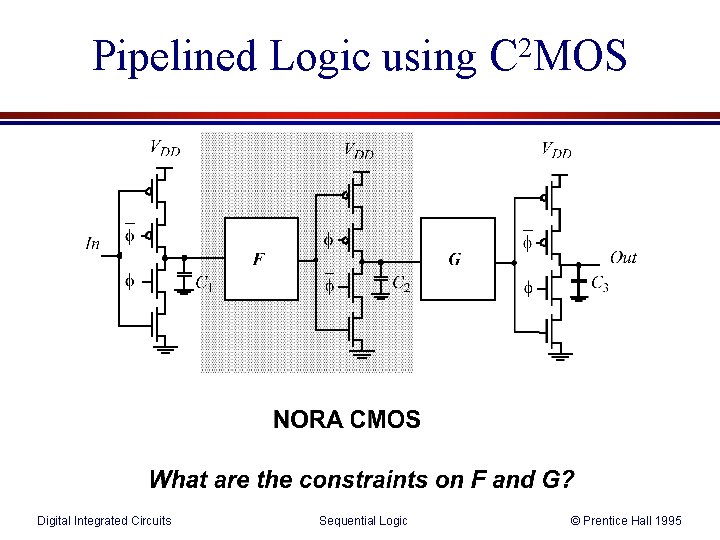

Pipelined Logic using C 2 MOS Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

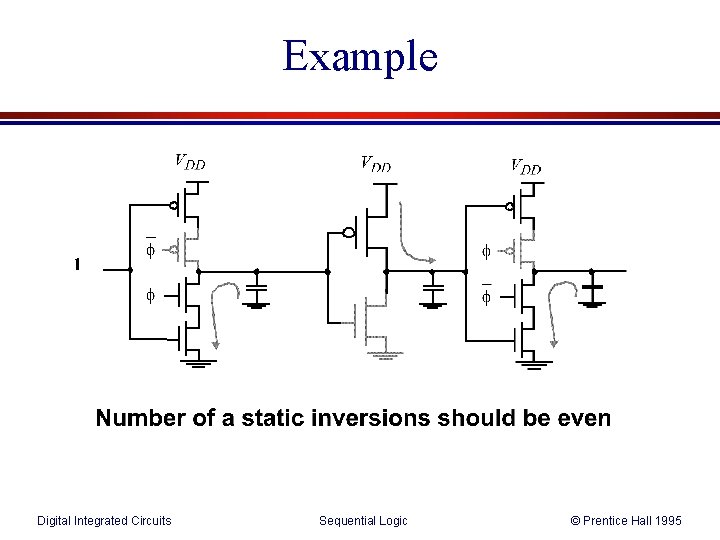

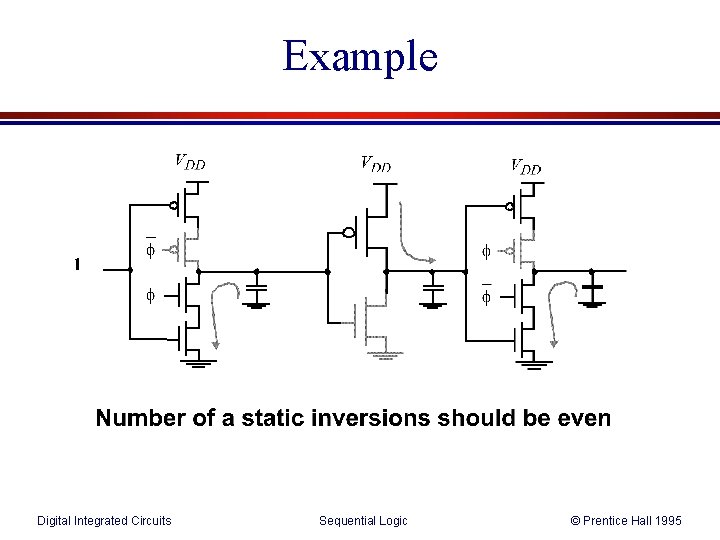

Example Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

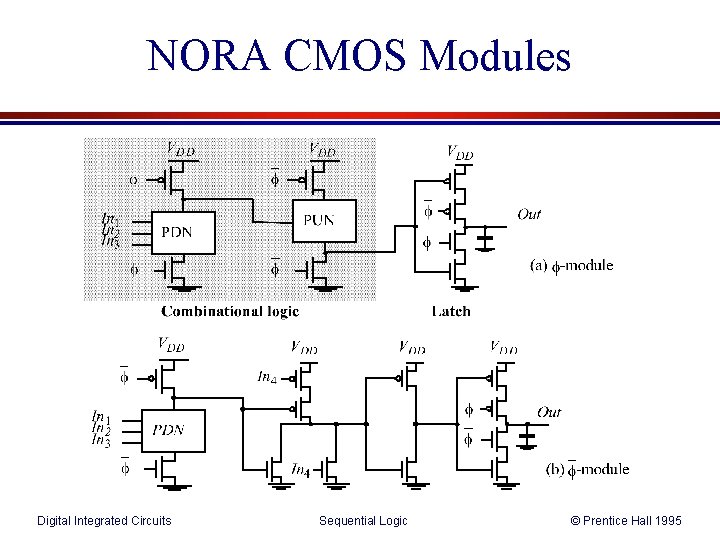

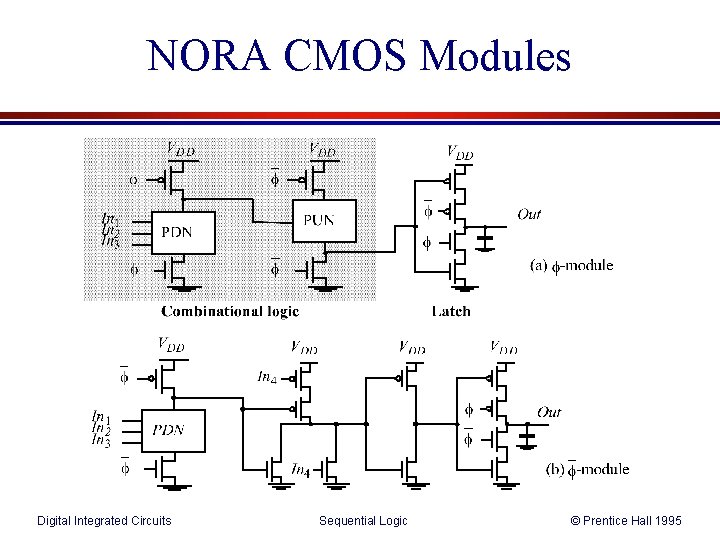

NORA CMOS Modules Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

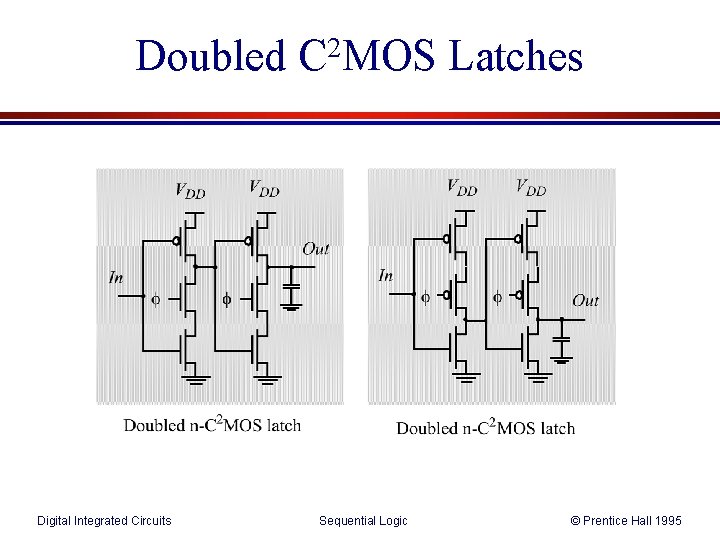

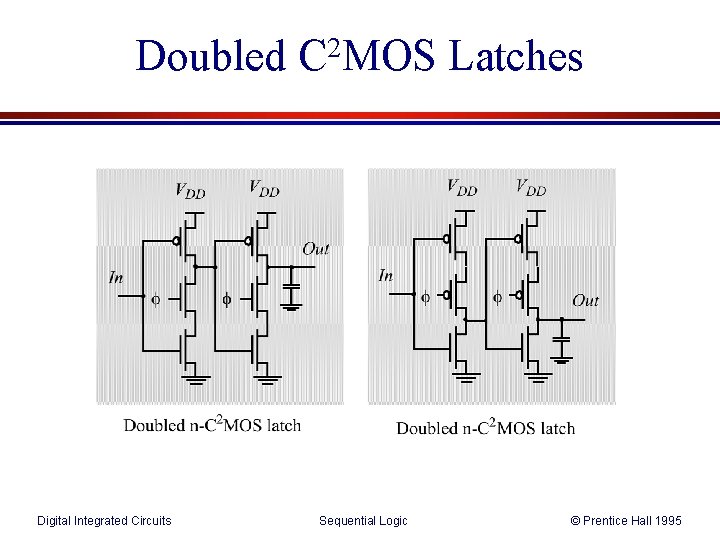

Doubled C 2 MOS Latches Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

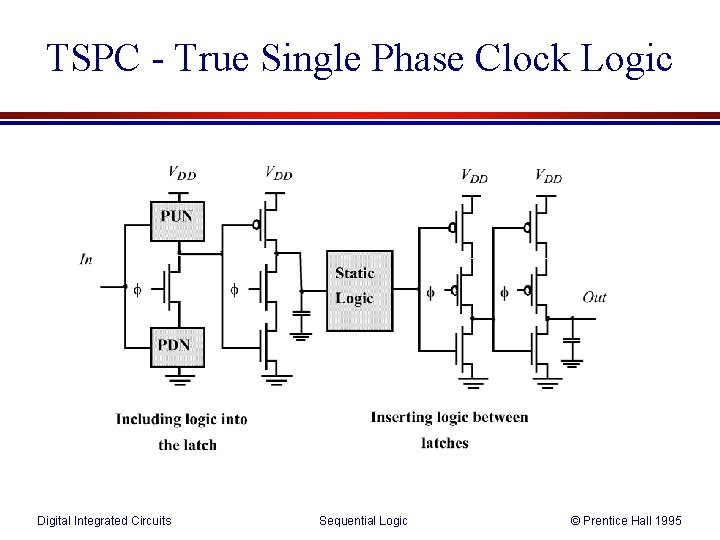

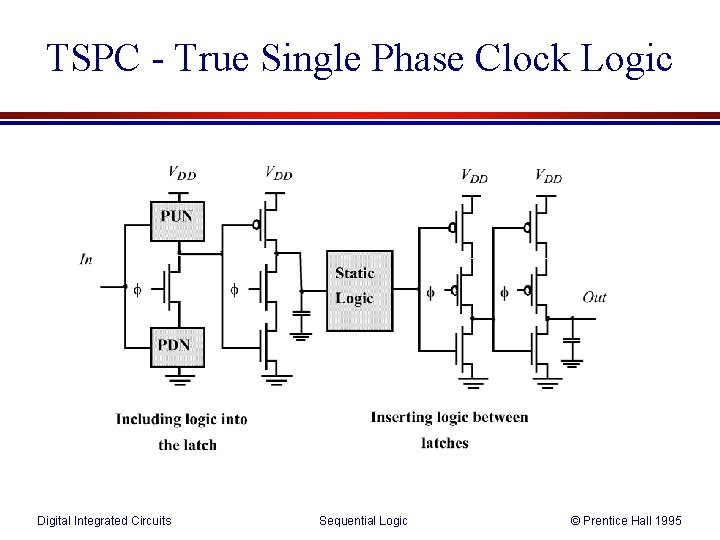

TSPC - True Single Phase Clock Logic Digital Integrated Circuits Sequential Logic © Prentice Hall 1995

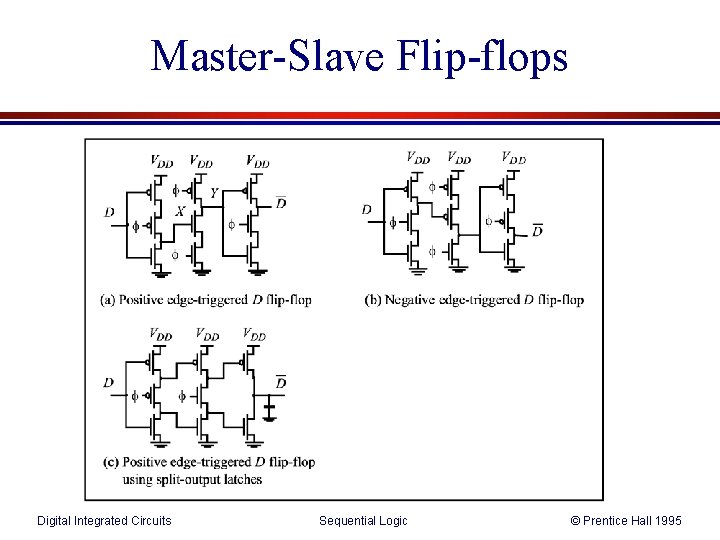

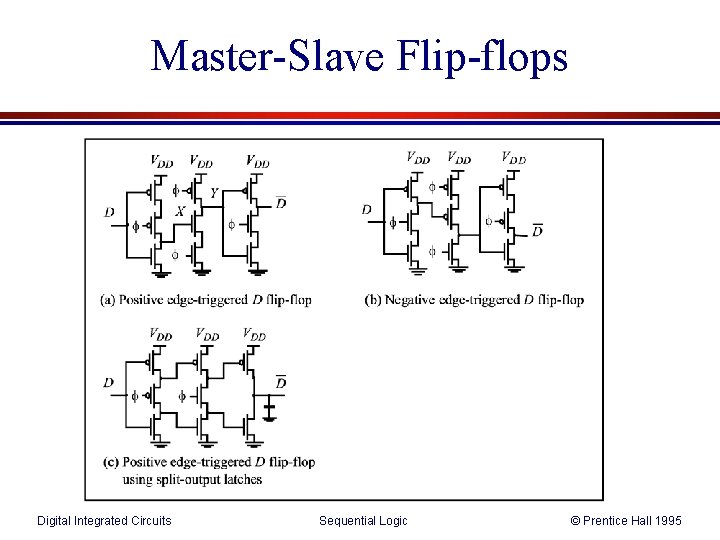

Master-Slave Flip-flops Digital Integrated Circuits Sequential Logic © Prentice Hall 1995