Sequential Logic Basic Binary Memory Elements 1 Chapter

Sequential Logic Basic Binary Memory Elements 1

Chapter Overview · Sequential Networks § § Simple Circuits with Feedback R-S Latch J-K Flipflop Edge-Triggered Flipflops · Realizing Circuits with Flipflops § Choosing a FF Type § Characteristic Equations § Conversion Among Types 2

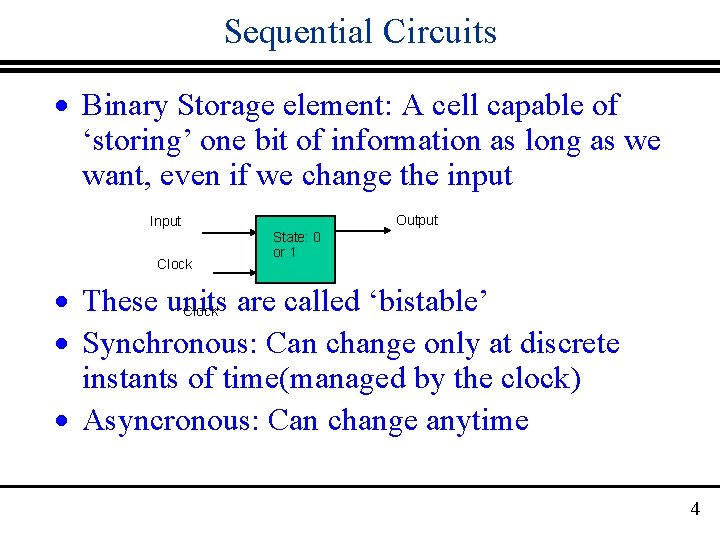

Sequential Circuits · Binary Storage element: A cell capable of ‘storing’ one bit of information as long as we want, even if we change the input Output Input Clock State: 0 or 1 · These units Clock are called ‘bistable’ · Synchronous: Can change only at discrete instants of time(managed by the clock) · Asyncronous: Can change anytime 4

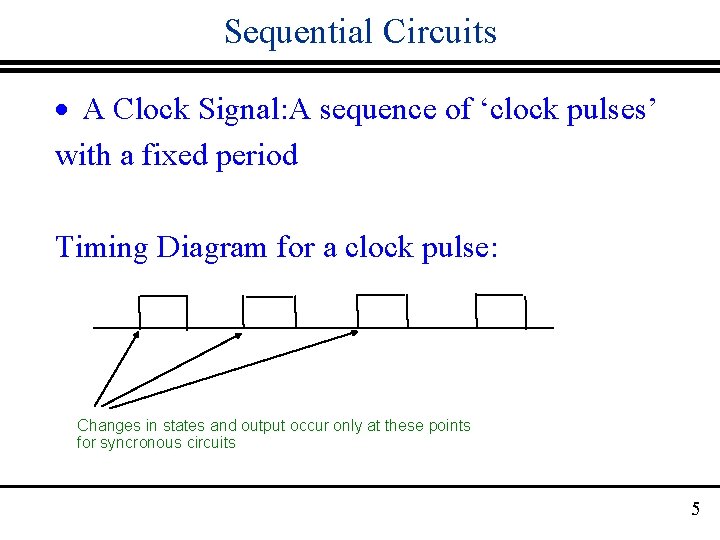

Sequential Circuits · A Clock Signal: A sequence of ‘clock pulses’ with a fixed period Timing Diagram for a clock pulse: Changes in states and output occur only at these points for syncronous circuits 5

Bi-stable Storage Element Characteristics · All bistable binary storage elements must have the following characteristics § The element must have two stable states w For a “stable” input configuration, the element can be in either of two possible states, set (1) or reset (0) § Inputs must exist to modify or hold FF state w A set of input and values must be able to change the stored value as well as hold the value § The present element state must be detectable w There must be an element output to determine what is the state of the element 6

Bistable Binary Storage Elements · Simple Circuits with Feedback § Primitive memory elements are created from cascaded gates where output is fed back to input § Simplest gate component: buffer or inverter: has a delay time tpd § Inverter: Basis for commercial static RAM designs § Present the input, remove it and the buffer will keep it • Tpd: prop. delay for the buffer • The input is effectively stored for tpd units. • İf output is connected to input, This value is kept indefinitely But no change is possible • Replace inverters with nand or nor gates to obtain the ‘Basic Latch’ 7

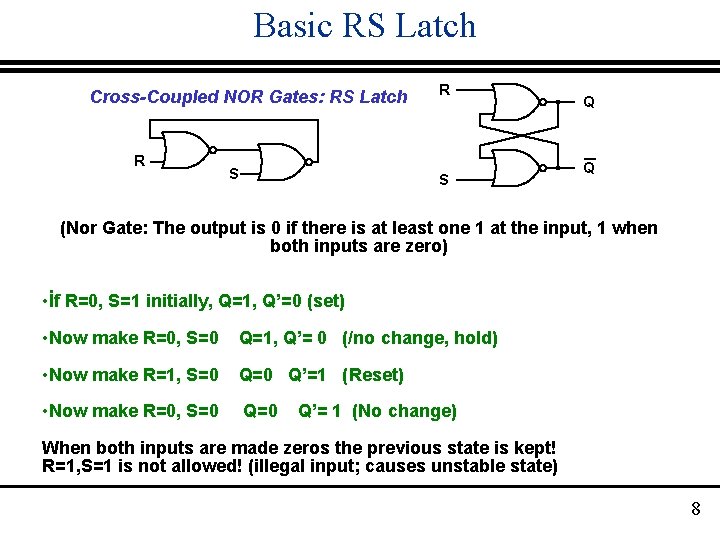

Basic RS Latch Cross-Coupled NOR Gates: RS Latch R S Q Q (Nor Gate: The output is 0 if there is at least one 1 at the input, 1 when both inputs are zero) • İf R=0, S=1 initially, Q=1, Q’=0 (set) • Now make R=0, S=0 Q=1, Q’= 0 (/no change, hold) • Now make R=1, S=0 Q’=1 (Reset) • Now make R=0, S=0 Q’= 1 (No change) When both inputs are made zeros the previous state is kept! R=1, S=1 is not allowed! (illegal input; causes unstable state) 8

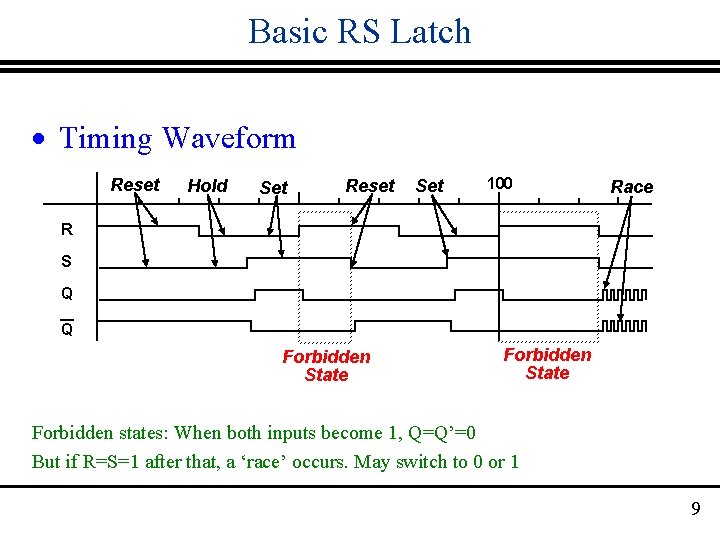

Basic RS Latch · Timing Waveform Reset Hold Set Reset Set 100 Race R S Q Q Forbidden State Forbidden states: When both inputs become 1, Q=Q’=0 But if R=S=1 after that, a ‘race’ occurs. May switch to 0 or 1 9

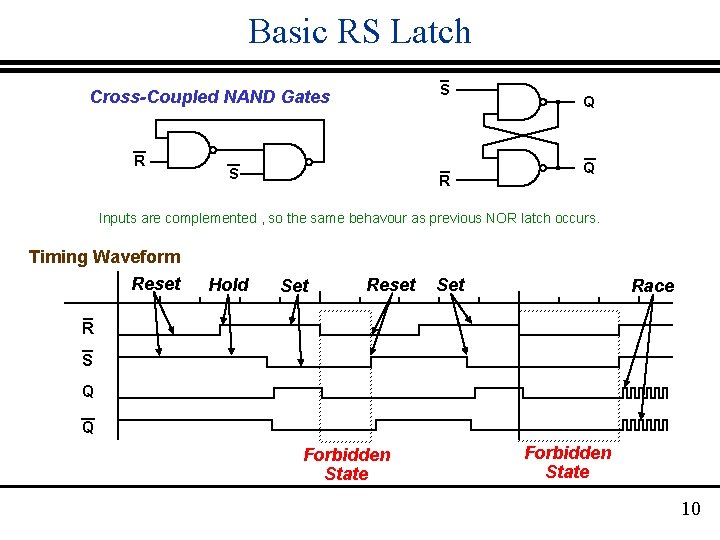

Basic RS Latch S Cross-Coupled NAND Gates R S R Q Q Inputs are complemented , so the same behavour as previous NOR latch occurs. Timing Waveform Reset Hold Set Reset Set Race R S Q Q Forbidden State 10

Basic RS Latch S R Q 0 0 hold 0 1 0 1 1 1 unstable Truth Table Summary of R-S Nor- Latch Behavior S R Q 0 0 unstable 0 1 1 1 0 0 1 1 hold Truth Table Summary of R-S NAND- Latch Behavior 11

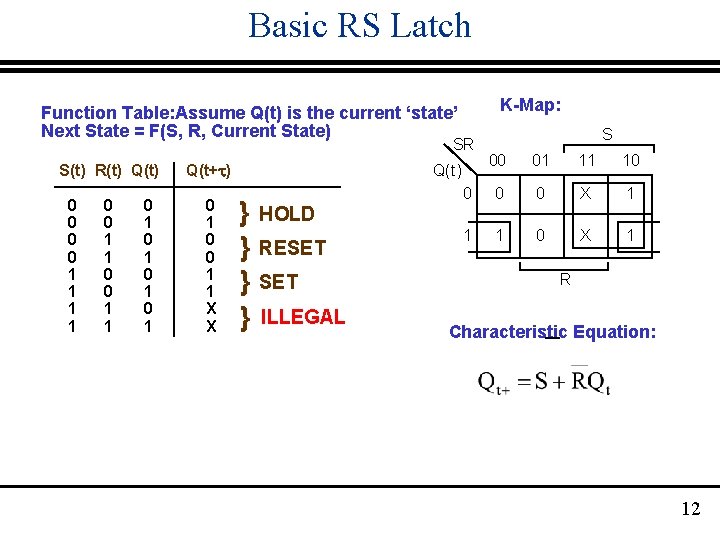

Basic RS Latch K-Map: Function Table: Assume Q(t) is the current ‘state’ Next State = F(S, R, Current State) SR S(t) R(t) Q(t) 0 0 1 1 0 1 0 1 0 1 0 0 1 1 X X 00 01 11 10 0 X 1 1 1 0 X 1 Q( t ) Q(t+ ) } HOLD } RESET } ILLEGAL S R Characteristic Equation: 12

Basic RS Latch with Clocked Latch: We want the state changes to occur only at the presence of clock pulses. Schematic: R Q Clock(EN) Q S Timing Diagram: Set 100 Reset S R EN Q Q 13

Basic RS Latch with Clock Another version: NAND implementation 14

D Latch · D stands for data · We want to eliminate the unforbidden input case · Output will follow input 15

D Latch · Timing Diagram Clock D Q · No hold state · Output follows the input 16

JK Latch J-K Latch How to eliminate the forbidden state and keep hold state? Idea: use output feedback to guarantee that R and S are never both one J, K both one yields toggle J(t) K(t) Q(t) 0 0 1 1 0 1 0 1 Q(t+ ) 0 1 0 0 1 1 1 0 J K S Q Q R Q Q } HOLD } RESET } SET Characteristic Equation: Q+ = Q K + Q J } TOGGLE 17

JK Latch J-K Latch: Race Condition Set Reset 100 Toggle J K Q Q Race Condition! Single state change per clocking event is still desired. Solution: Master/Slave Flipflop 18

Master-Slave Flip-Flop • Two SR latches connected, master’s outputs are connected to slave’s inputs • Master does not pass its state Y to slave until C=0 (Clock of slave will be 1) • So output Q will take the value Y at the negative going edge of C. Master Slave 19

Master-Slave Flip-Flop · Timing Diagram One’s catch: A level triggered catch that reflects at the output Incorrect behavior since S=0 at negative going edge 20

Master-Slave Flip-Flop Master/Slave J-K Flipflop Master Stage K S Q SR Latch R Q J Slave Stage P S Q SR Latch R Q P Q Q Clk Sample inputs while clock low Sample inputs while clock high Uses time to break feedback path from outputs to inputs! Set J K Clk P P Q Q 1's Reset Catch Toggle 100 Master outputs Correct Toggle Operation Slave outputs 21

Edge-Triggered D Flip-Flop · Master slave still ‘pulse’ triggered because of the 1’s catching effect · Consider D type Master-slave FF ; Positive Edge triggered behavior-responds only at the edges 22

Edge-Triggered D Flip-Flop · Timing Diagram: Does not catch the glitches C’ C D Y Q 23

Sequential Switching Networks 7474 Clk D Q C Q Positive edge-triggered flip-flop Edge triggered device sample inputs on the event edge Transparent latches sample inputs as long as the clock is asserted Timing Diagram: D 7476 D Q Clk C Q Q Level-sensitive latch Bubble here for active 0 input device (negative edge triggered) 7474 Q 7476 Behavior the same unless input changes while the clock is high 24

Sequential Switching Networks Definition of Terms Tsu T h Input Clock There is a timing "window" around the clocking event during which the input must remain stable and unchanged to ensure correct flip-flop operation Clock: Periodic Event, causes state of memory element to change rising edge, falling edge, high level, low level Setup Time (Tsu) Minimum time before the clocking event by which the input must be stable Hold Time (Th) Minimum time after the clocking event during which the input must remain stable 25

Sequential Switching Elements Typical Timing Specifications: Flipflops vs. Latches 74 LS 74 Positive Edge Triggered D Flipflop • Setup time • Hold time • Minimum clock width • Propagation delays (low to high, high to low, max and typical) D Clk Q Tsu 20 ns Th 5 ns Tw 25 ns Tplh 25 ns 13 ns T su 20 ns Th 5 ns T phl 40 ns 25 ns All measurements are made from the clocking event that is, the rising edge of the clock 26

Sequential Switching Networks Typical Timing Specifications: Flipflops vs. Latches 74 LS 76 Transparent Latch D • Setup time • Hold time • Minimum Clock Width • Propagation Delays: high to low, low to high, maximum, typical data to output clock to output Clk Q T su Th 20 5 ns ns Tw 20 ns Tplh C» Q 27 ns 15 ns T plh D» Q 27 ns 15 ns Tsu 20 ns Th 5 ns T phl C» Q 25 ns 14 ns T phl D» Q 16 ns 7 ns Measurements from falling clock edge or rising or falling data edge 27

Sequential Switching Networks Edge-Triggered Flipflops 1's Catching: a 0 -1 -0 glitch on the J or K inputs leads to a state change! forces designer to use hazard-free logic Solution: another edge-triggered logic, more complicated circuit D D 0 Clk=1 Holds D when clock goes low Negative Edge-Triggered D flipflop 4 -5 gate delays R Q S Q setup, hold times necessary to successfully latch the input 0 D Holds D when clock goes low D Negative edge-triggered FF when clock is high Characteristic Equation: Q+ = D 28

Sequential Switching Networks Positive vs. Negative Edge Triggered Devices 100 D Clk Qpos Positive edgetriggered FF Qpos Qneg Negative edgetriggered FF Qneg Positive Edge Triggered Inputs sampled on rising edge Outputs change after rising edge Negative Edge Triggered Inputs sampled on falling edge Outputs change after falling edge Toggle Flipflop Formed from J-K with both inputs wired together 30

Sequential Switching Networks Latches vs. Flipflops Input/Output Behavior of Latches and Flipflops Type unclocked latch When Inputs are Sampled always When Outputs are Valid propagation delay from input change level sensitive latch clock high (Tsu, Th around falling clock edge) propagation delay from input change positive edge flipflop clock lo-to-hi transition (Tsu, Th around rising clock edge) propagation delay from rising edge of clock negative edge flipflop clock hi-to-lo transition (Tsu, Th around falling clock edge) propagation delay from falling edge of clock master/slave flipflop clock hi-to-lo transition (Tsu, Th around falling clock edge) propagation delay from falling edge of clock 31

Flip-Flop Input Configurations · There are four basic FF input configurations § § SR JK D T 32

The SR Flip-Flop Characteristic Table: S(t) R(t) Q(t) 0 0 1 1 0 1 0 1 Characteristic Equation: Q(t+ ) 0 1 0 0 1 1 X X } HOLD } RESET } ILLEGAL S C R PR CL Q Q PR: Asynchronous preset CL: Asynchronous clear Available in most FF’s 33

The JK Flip-Flop Characteristic Table: J(t) K(t) Q(t) 0 0 1 1 0 1 0 1 Q(t+ ) 0 1 0 0 1 1 1 0 Characteristic Equation: Q+ = Q K + Q J } HOLD } RESET } TOGGLE J C K PR CL Q Q 34

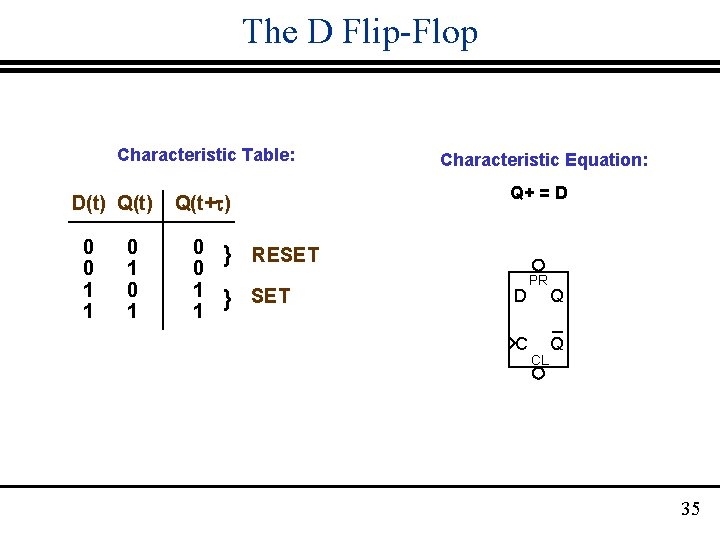

The D Flip-Flop Characteristic Table: D(t) Q(t) 0 0 1 1 0 1 Q(t+ ) 0 0 1 1 Characteristic Equation: Q+ = D } RESET } SET D C PR CL Q Q 35

The T Flip-Flop Characteristic Table: T(t) Q(t) 0 0 1 1 0 1 Q(t+ ) 0 1 1 0 Characteristic Equation: Q+ = D Q } HOLD } TOGGLE T C PR CL Q Q 36

Realizing Circuits with Different Kinds of FFs Choosing a Flipflop · R-S Clocked Latch: § used as storage element in narrow width clocked systems its use is not recommended! § however, fundamental building block of other flipflop types · J-K Flipflop: § versatile building block § can be used to implement D and T FFs § usually requires least amount of logic to implement ƒ(In, Q, Q+) but has two inputs with increased wiring complexity § because of 1's catching, never use master/slave J-K FFs; edgetriggered varieties exist 43

Realizing Circuits with Different Kinds of FFs Choosing a Flipflop · D Flipflop: § minimizes wires, much preferred in VLSI technologies § simplest design technique § best choice for storage registers · T Flipflops: § don't really exist, constructed from J-K FFs § usually best choice for implementing counters · Preset and Clear inputs highly desirable!! 44

- Slides: 36