Sequential Execution l Normally CPU sequentially executes instructions

- Slides: 18

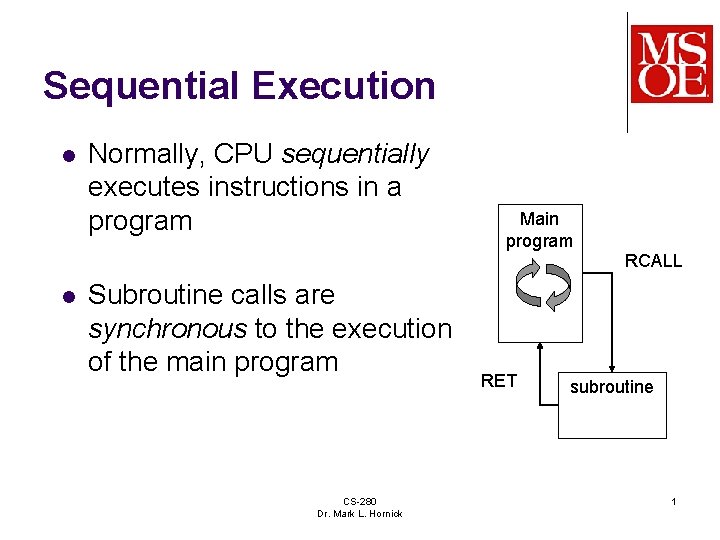

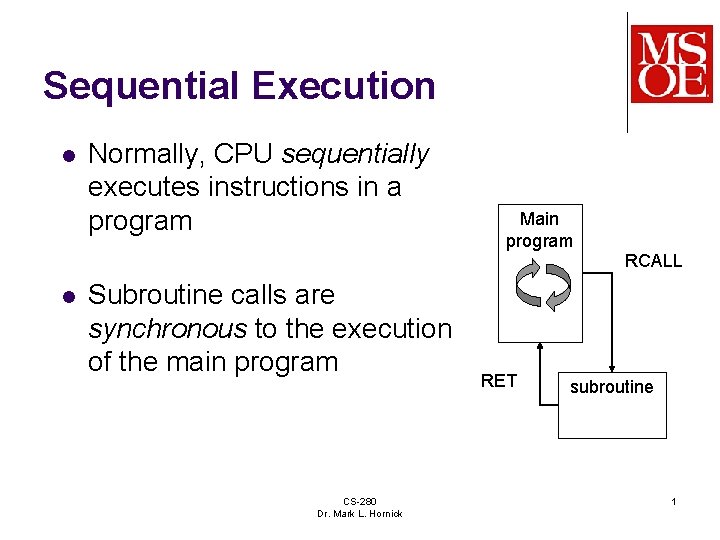

Sequential Execution l Normally, CPU sequentially executes instructions in a program Main program RCALL l Subroutine calls are synchronous to the execution of the main program CS-280 Dr. Mark L. Hornick RET subroutine 1

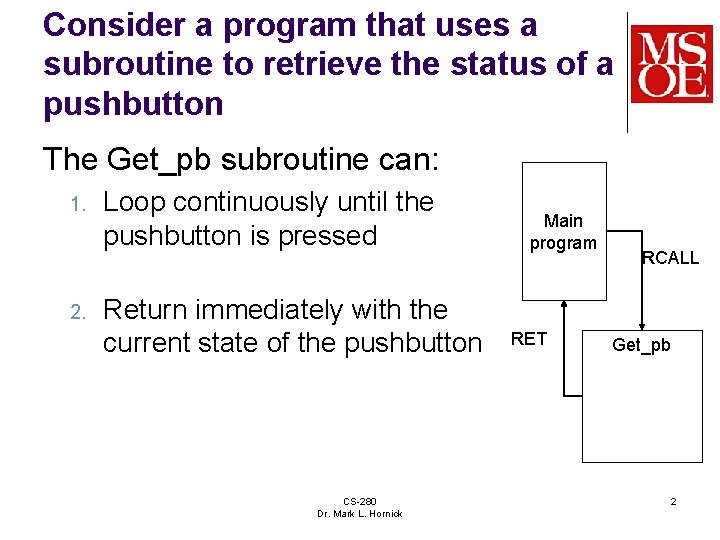

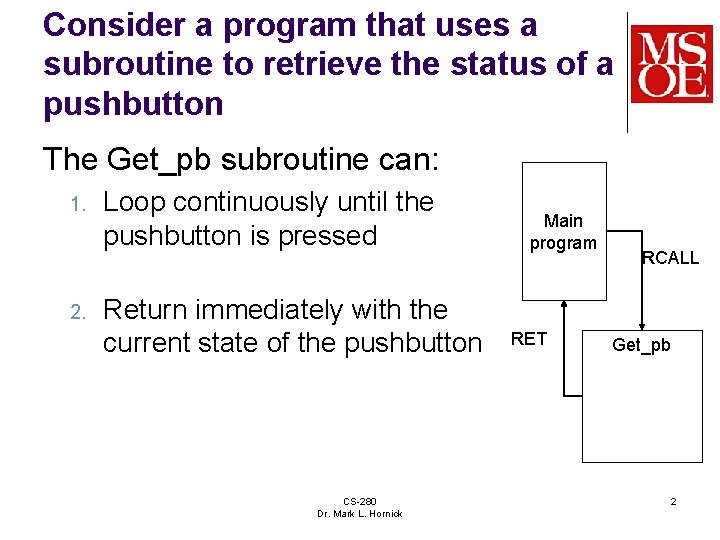

Consider a program that uses a subroutine to retrieve the status of a pushbutton The Get_pb subroutine can: 1. 2. Loop continuously until the pushbutton is pressed Return immediately with the current state of the pushbutton CS-280 Dr. Mark L. Hornick Main program RET RCALL Get_pb 2

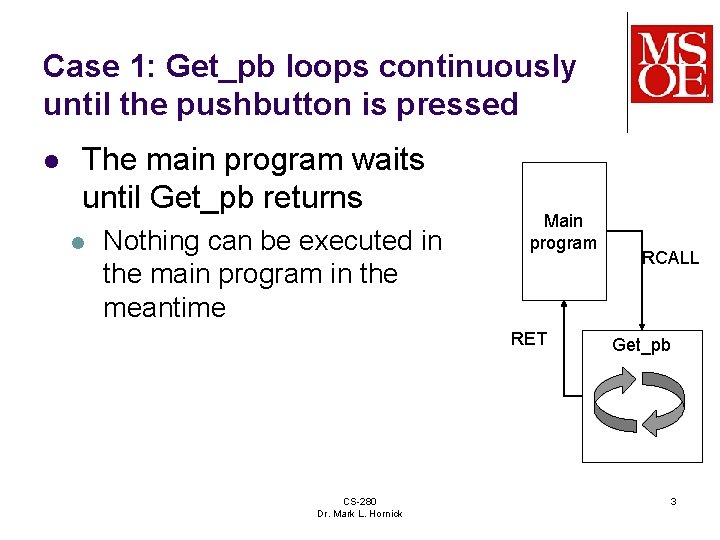

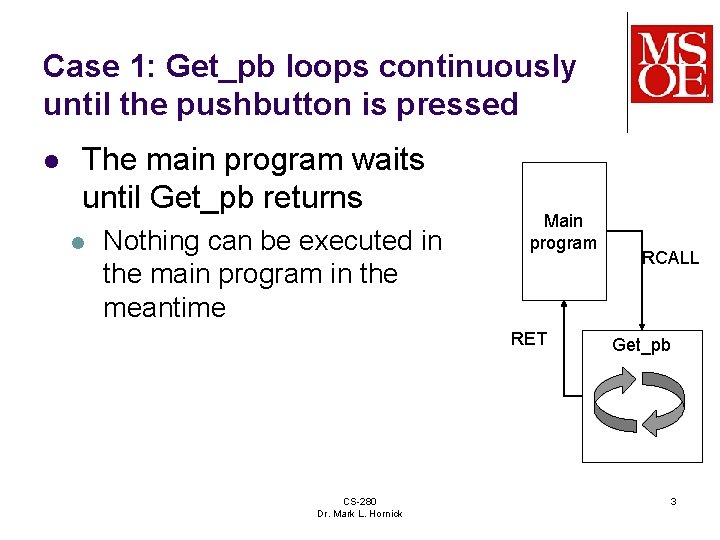

Case 1: Get_pb loops continuously until the pushbutton is pressed l The main program waits until Get_pb returns l Nothing can be executed in the main program in the meantime Main program RET CS-280 Dr. Mark L. Hornick RCALL Get_pb 3

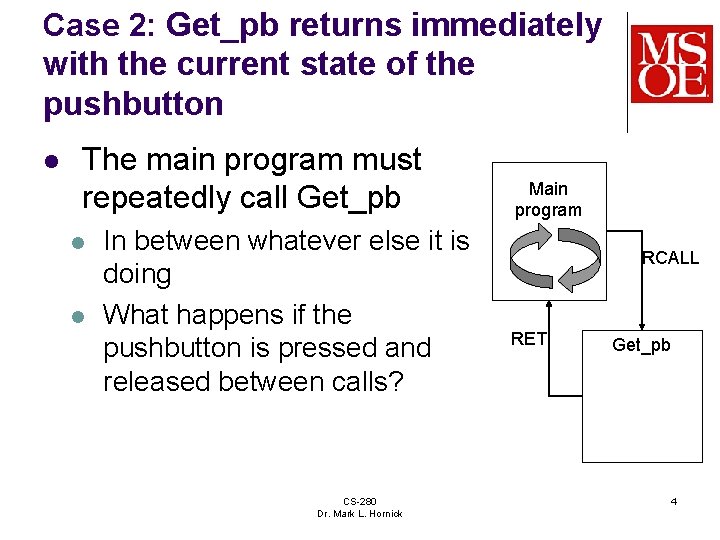

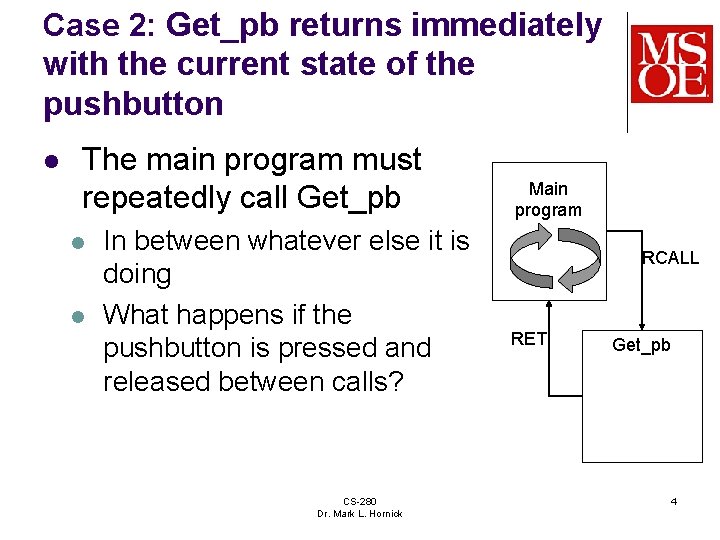

Case 2: Get_pb returns immediately with the current state of the pushbutton l The main program must repeatedly call Get_pb l l In between whatever else it is doing What happens if the pushbutton is pressed and released between calls? CS-280 Dr. Mark L. Hornick Main program RCALL RET Get_pb 4

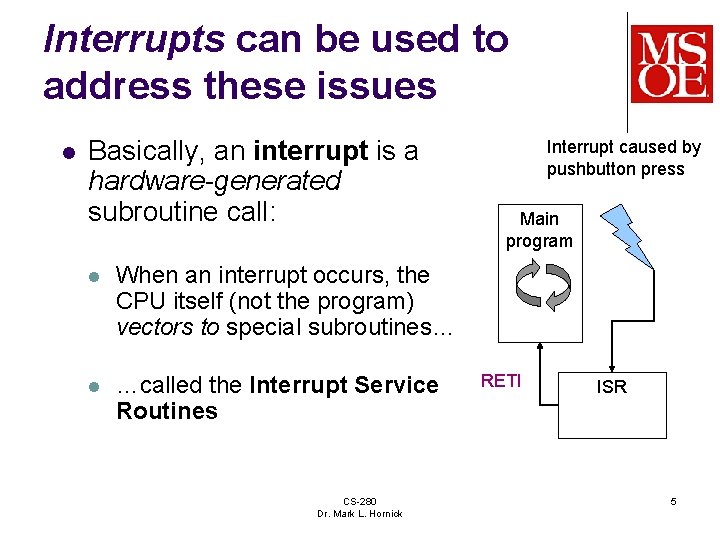

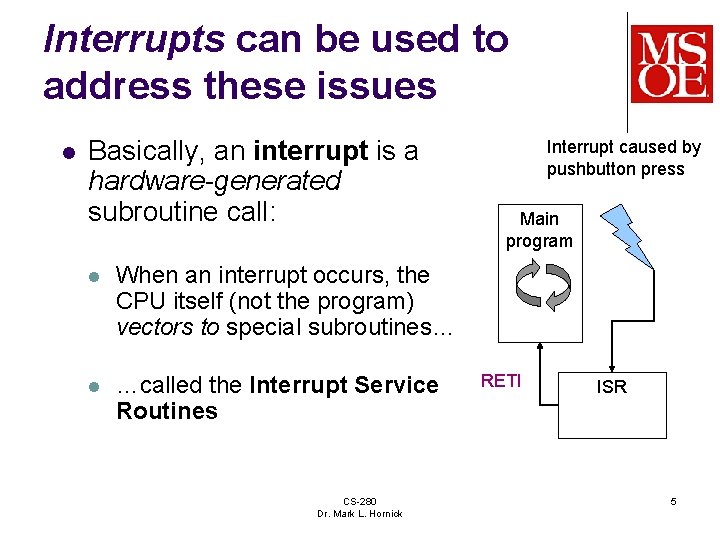

Interrupts can be used to address these issues l Basically, an interrupt is a hardware-generated subroutine call: l When an interrupt occurs, the CPU itself (not the program) vectors to special subroutines… l …called the Interrupt Service Routines CS-280 Dr. Mark L. Hornick Interrupt caused by pushbutton press Main program RETI ISR 5

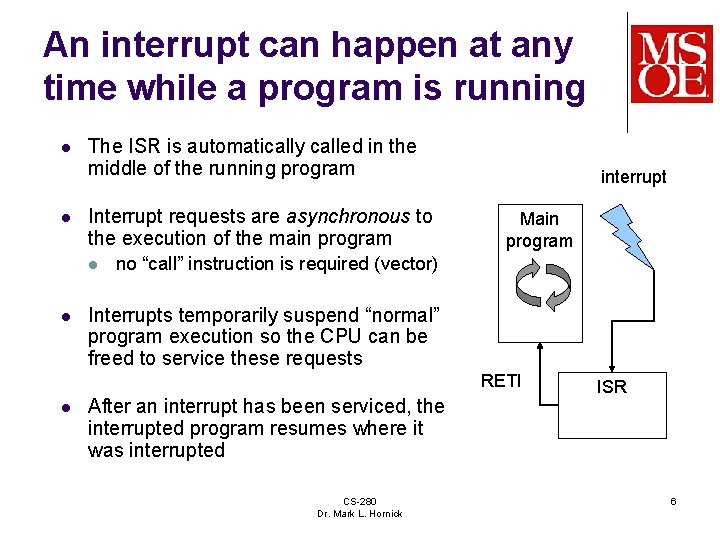

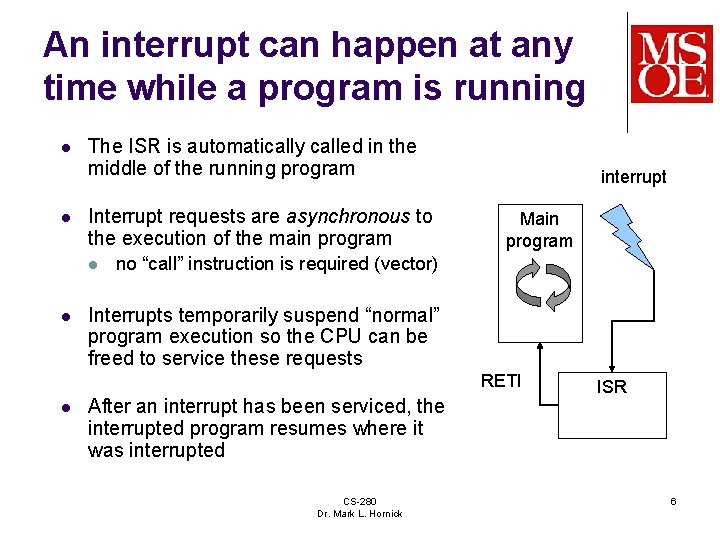

An interrupt can happen at any time while a program is running l l The ISR is automatically called in the middle of the running program Interrupt requests are asynchronous to the execution of the main program l l interrupt Main program no “call” instruction is required (vector) Interrupts temporarily suspend “normal” program execution so the CPU can be freed to service these requests RETI l After an interrupt has been serviced, the interrupted program resumes where it was interrupted CS-280 Dr. Mark L. Hornick ISR 6

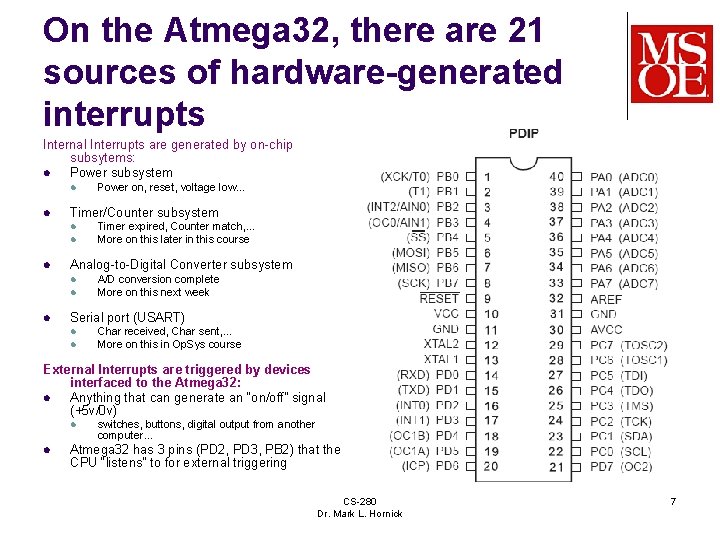

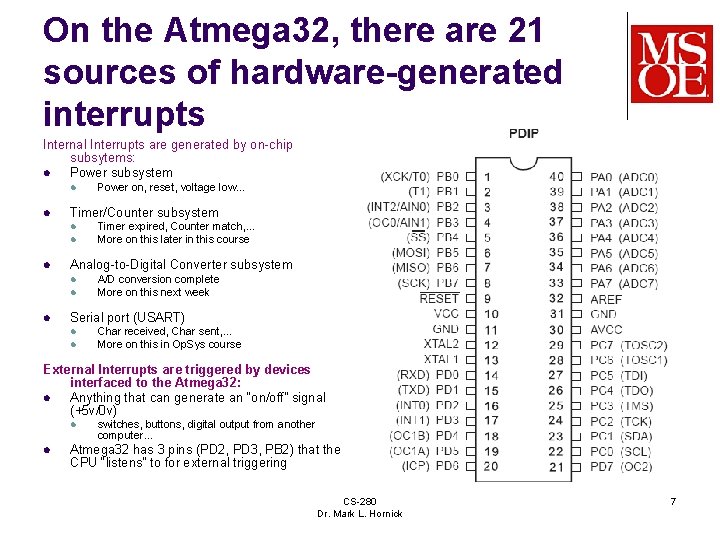

On the Atmega 32, there are 21 sources of hardware-generated interrupts Internal Interrupts are generated by on-chip subsytems: l Power subsystem l l Timer/Counter subsystem l l l Timer expired, Counter match, … More on this later in this course Analog-to-Digital Converter subsystem l l l Power on, reset, voltage low… A/D conversion complete More on this next week Serial port (USART) l l Char received, Char sent, … More on this in Op. Sys course External Interrupts are triggered by devices interfaced to the Atmega 32: l Anything that can generate an “on/off” signal (+5 v/0 v) l l switches, buttons, digital output from another computer… Atmega 32 has 3 pins (PD 2, PD 3, PB 2) that the CPU “listens” to for external triggering CS-280 Dr. Mark L. Hornick 7

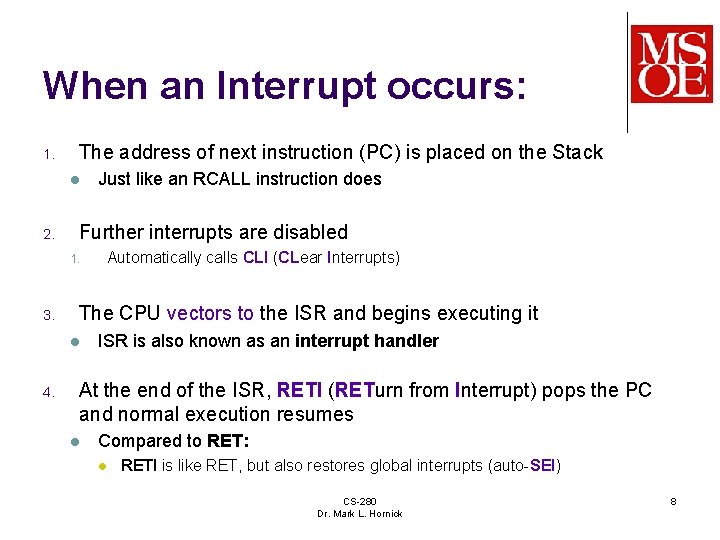

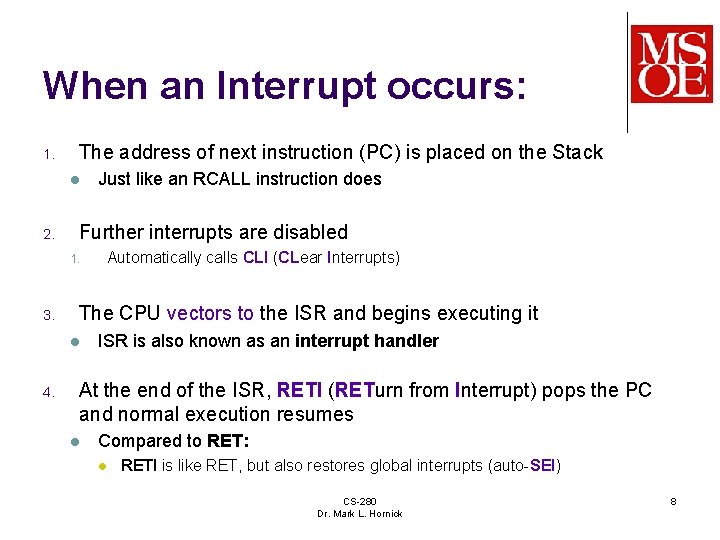

When an Interrupt occurs: 1. The address of next instruction (PC) is placed on the Stack l 2. Just like an RCALL instruction does Further interrupts are disabled Automatically calls CLI (CLear Interrupts) 1. 3. The CPU vectors to the ISR and begins executing it l 4. ISR is also known as an interrupt handler At the end of the ISR, RETI (RETurn from Interrupt) pops the PC and normal execution resumes l Compared to RET: l RETI is like RET, but also restores global interrupts (auto-SEI) CS-280 Dr. Mark L. Hornick 8

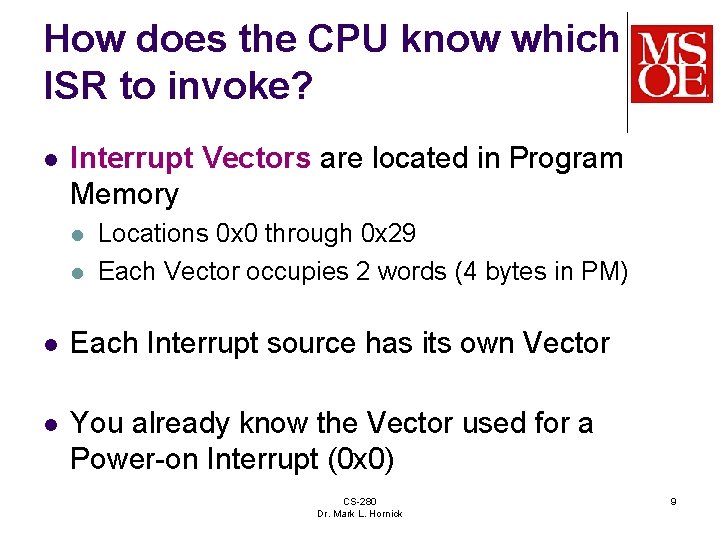

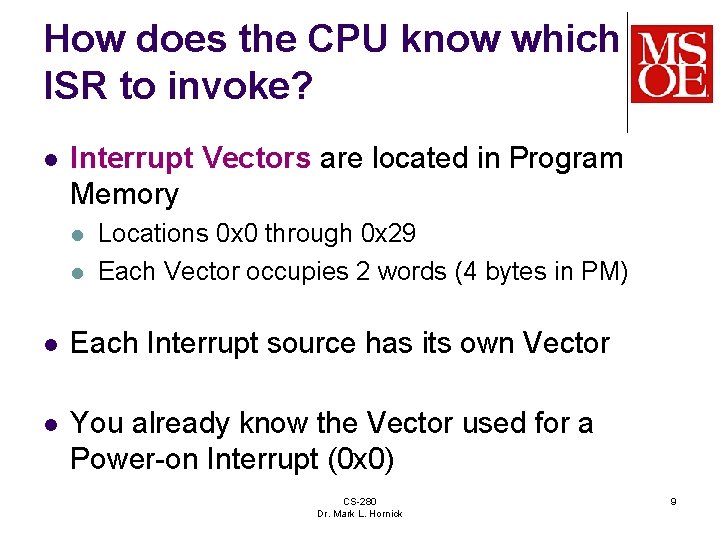

How does the CPU know which ISR to invoke? l Interrupt Vectors are located in Program Memory l l Locations 0 x 0 through 0 x 29 Each Vector occupies 2 words (4 bytes in PM) l Each Interrupt source has its own Vector l You already know the Vector used for a Power-on Interrupt (0 x 0) CS-280 Dr. Mark L. Hornick 9

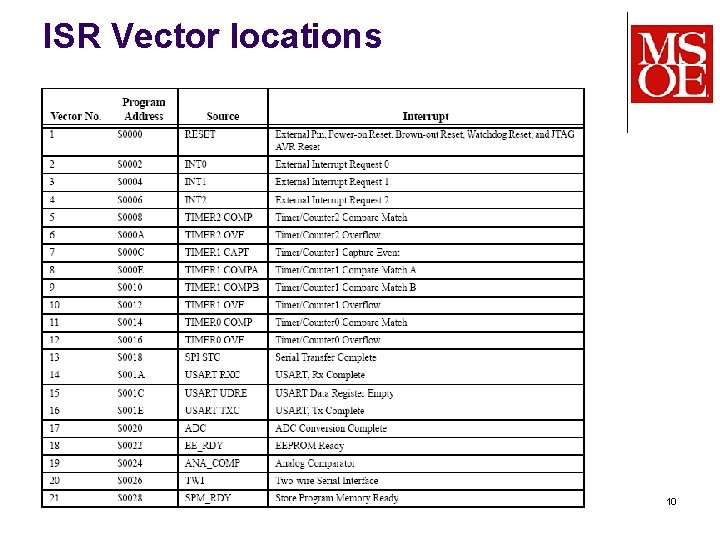

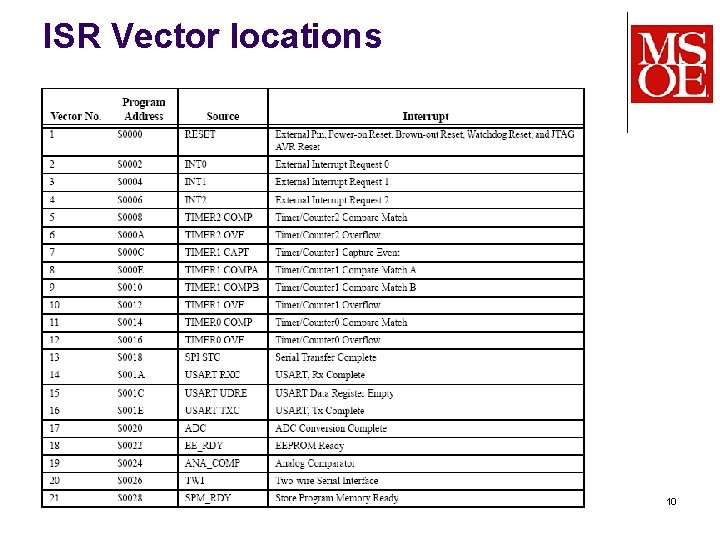

ISR Vector locations CS-280 Dr. Mark L. Hornick 10

SREG has a special-purpose bit (I) that enables or disables the operation of all Interrupts Normally, the I-bit is unset meaning interrupts are masked, or disabled. • use SEI / CLI to set/clear the I flag CS-280 Dr. Mark L. Hornick 11

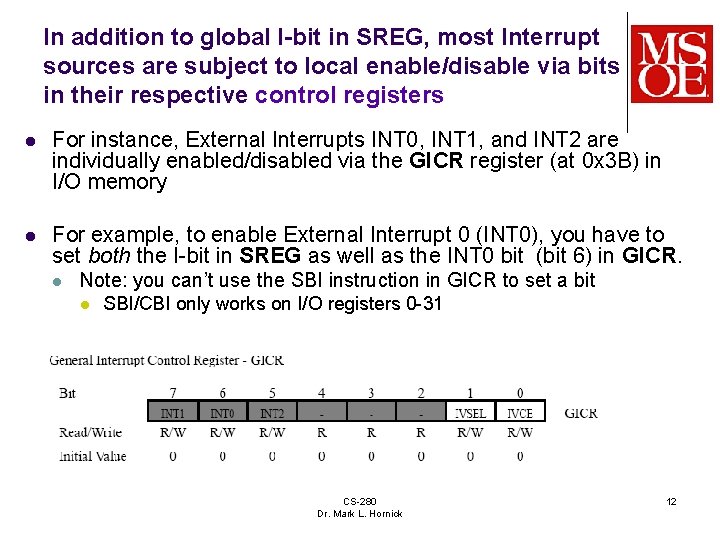

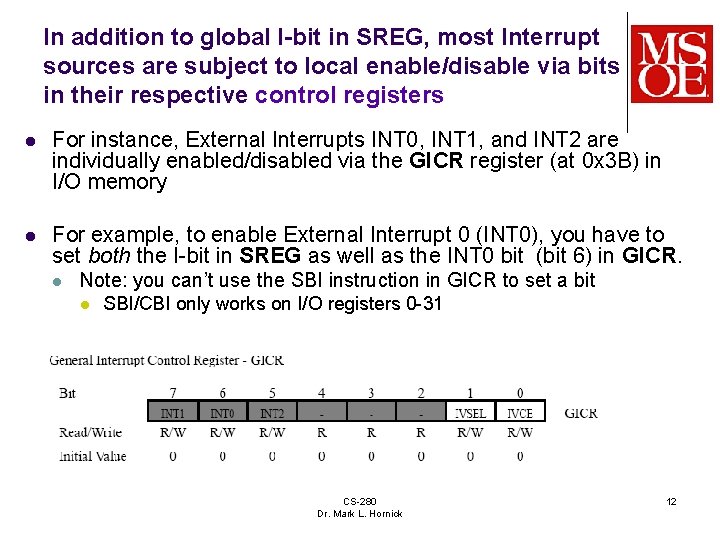

In addition to global I-bit in SREG, most Interrupt sources are subject to local enable/disable via bits in their respective control registers l For instance, External Interrupts INT 0, INT 1, and INT 2 are individually enabled/disabled via the GICR register (at 0 x 3 B) in I/O memory l For example, to enable External Interrupt 0 (INT 0), you have to set both the I-bit in SREG as well as the INT 0 bit (bit 6) in GICR. l Note: you can’t use the SBI instruction in GICR to set a bit l SBI/CBI only works on I/O registers 0 -31 CS-280 Dr. Mark L. Hornick 12

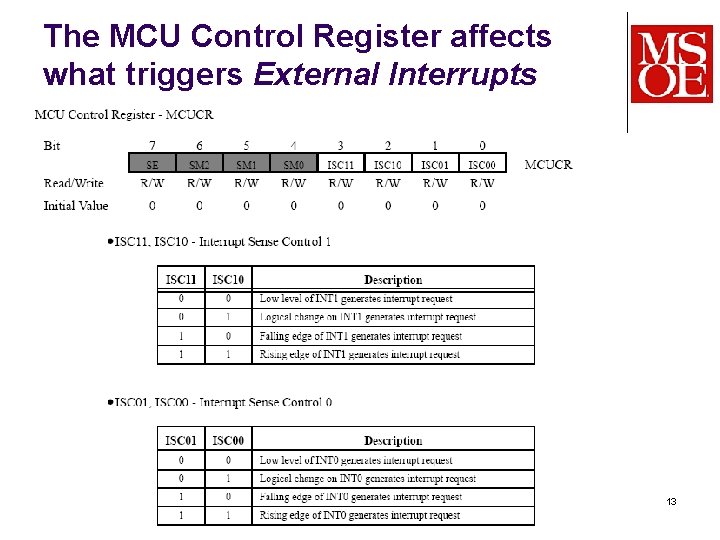

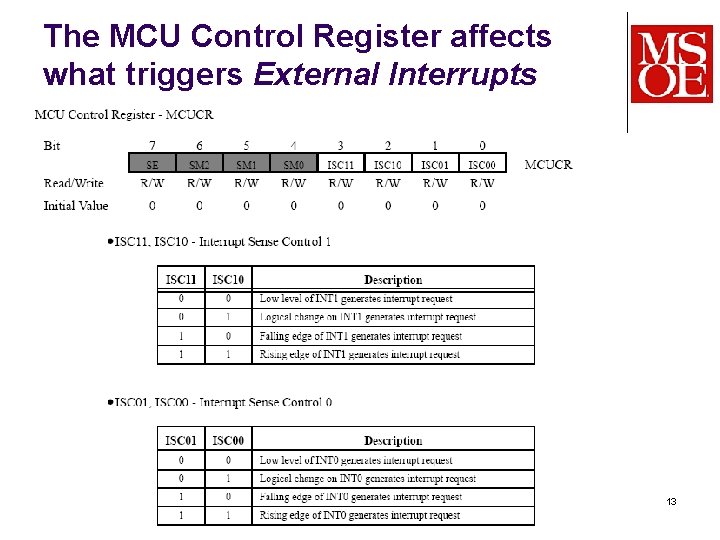

The MCU Control Register affects what triggers External Interrupts CS-280 Dr. Mark L. Hornick 13

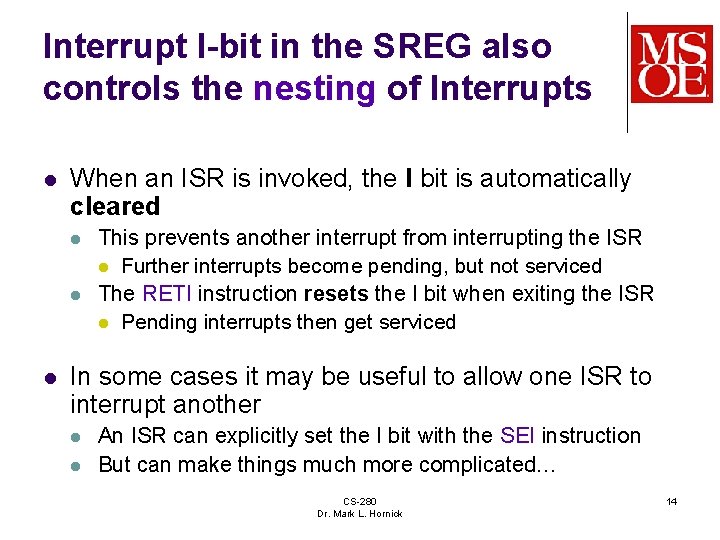

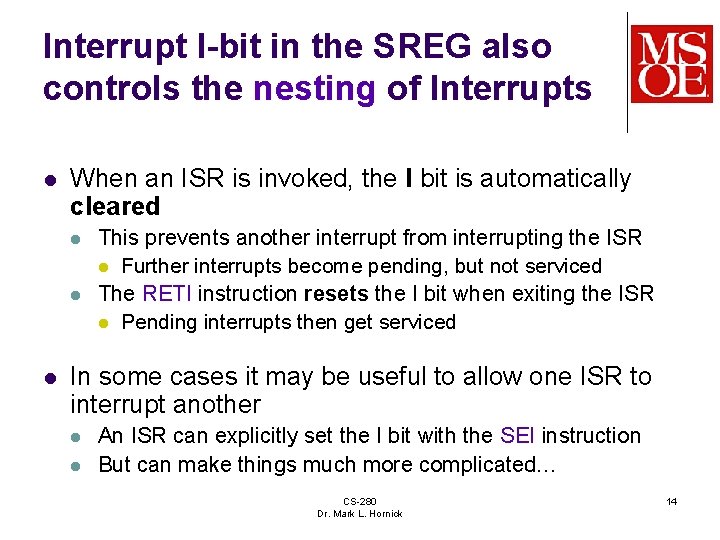

Interrupt I-bit in the SREG also controls the nesting of Interrupts l When an ISR is invoked, the I bit is automatically cleared l l l This prevents another interrupt from interrupting the ISR l Further interrupts become pending, but not serviced The RETI instruction resets the I bit when exiting the ISR l Pending interrupts then get serviced In some cases it may be useful to allow one ISR to interrupt another l l An ISR can explicitly set the I bit with the SEI instruction But can make things much more complicated… CS-280 Dr. Mark L. Hornick 14

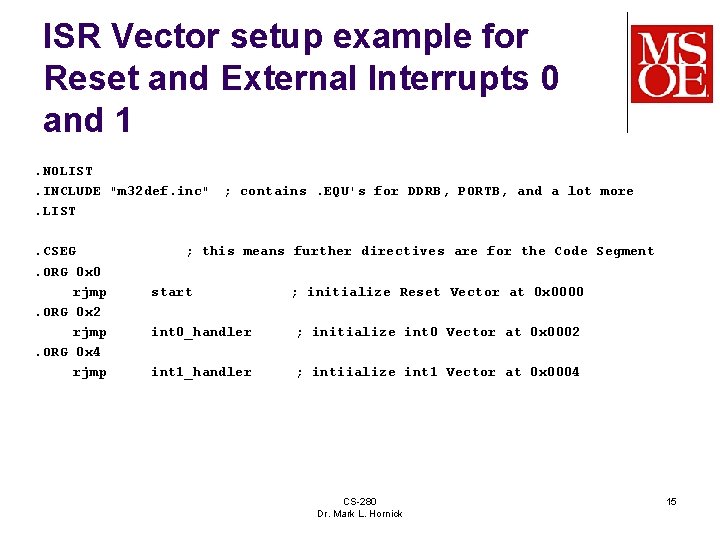

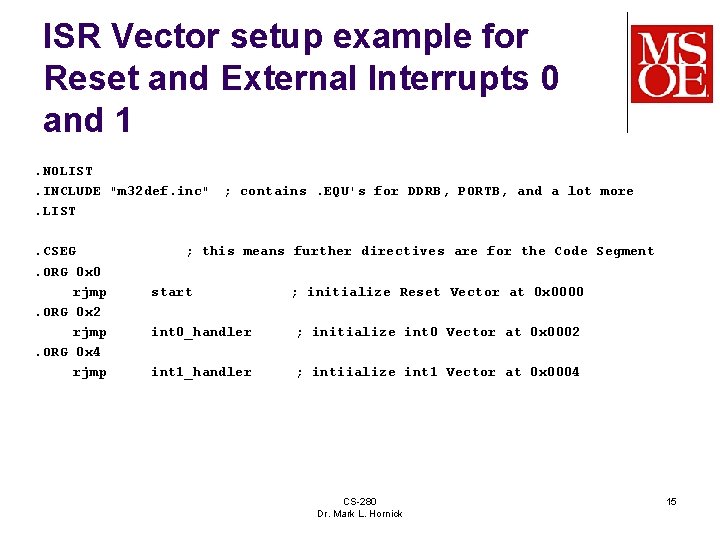

ISR Vector setup example for Reset and External Interrupts 0 and 1. NOLIST. INCLUDE "m 32 def. inc" ; contains. EQU's for DDRB, PORTB, and a lot more. LIST. CSEG. ORG 0 x 0 rjmp. ORG 0 x 2 rjmp. ORG 0 x 4 rjmp ; this means further directives are for the Code Segment start ; initialize Reset Vector at 0 x 0000 int 0_handler ; initialize int 0 Vector at 0 x 0002 int 1_handler ; intiialize int 1 Vector at 0 x 0004 CS-280 Dr. Mark L. Hornick 15

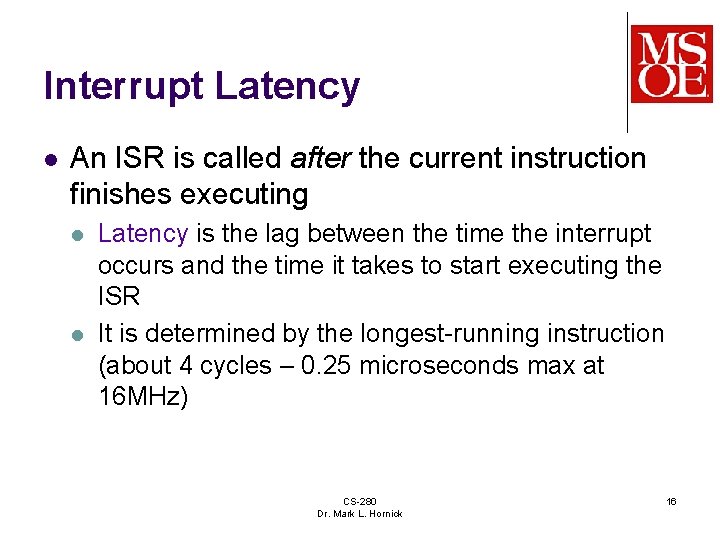

Interrupt Latency l An ISR is called after the current instruction finishes executing l l Latency is the lag between the time the interrupt occurs and the time it takes to start executing the ISR It is determined by the longest-running instruction (about 4 cycles – 0. 25 microseconds max at 16 MHz) CS-280 Dr. Mark L. Hornick 16

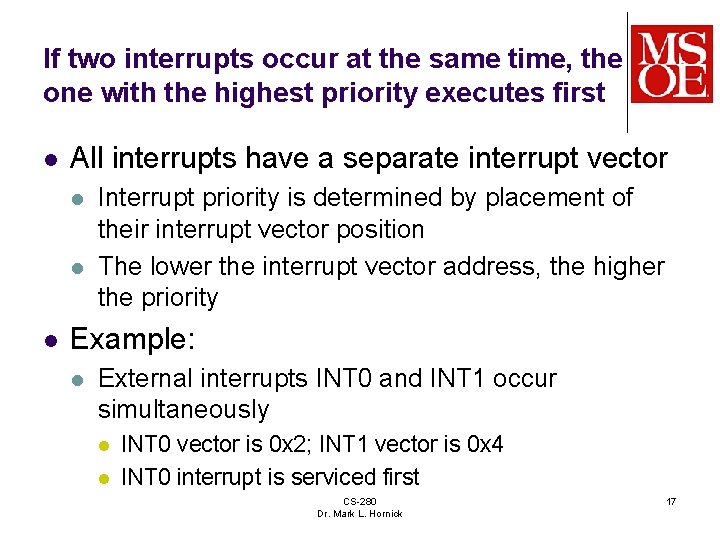

If two interrupts occur at the same time, the one with the highest priority executes first l All interrupts have a separate interrupt vector l l l Interrupt priority is determined by placement of their interrupt vector position The lower the interrupt vector address, the higher the priority Example: l External interrupts INT 0 and INT 1 occur simultaneously l l INT 0 vector is 0 x 2; INT 1 vector is 0 x 4 INT 0 interrupt is serviced first CS-280 Dr. Mark L. Hornick 17

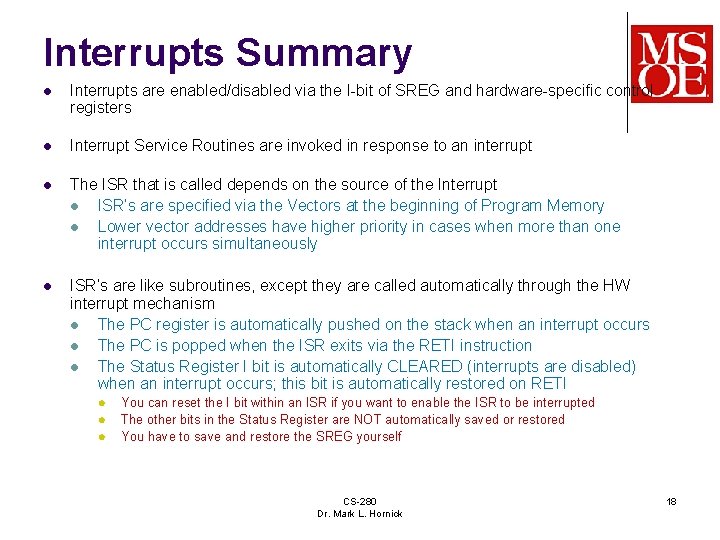

Interrupts Summary l Interrupts are enabled/disabled via the I-bit of SREG and hardware-specific control registers l Interrupt Service Routines are invoked in response to an interrupt l The ISR that is called depends on the source of the Interrupt l ISR’s are specified via the Vectors at the beginning of Program Memory l Lower vector addresses have higher priority in cases when more than one interrupt occurs simultaneously l ISR’s are like subroutines, except they are called automatically through the HW interrupt mechanism l The PC register is automatically pushed on the stack when an interrupt occurs l The PC is popped when the ISR exits via the RETI instruction l The Status Register I bit is automatically CLEARED (interrupts are disabled) when an interrupt occurs; this bit is automatically restored on RETI l l l You can reset the I bit within an ISR if you want to enable the ISR to be interrupted The other bits in the Status Register are NOT automatically saved or restored You have to save and restore the SREG yourself CS-280 Dr. Mark L. Hornick 18