Sequential Cirucits 91509 L 19 Sequential Circuits Copyright

- Slides: 14

Sequential Cirucits 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 1

Class 19 – Sequential Circuits o o Definitions Latches n n o Set-Reset – SR The D Latch Material from section 5 -1 and 5 -2 of text 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 2

Combination Logic o o o Logic that performs some transformation operation on the inputs to produce outputs which are simple logic functions of the input. The outputs reflect a function of the current values on the inputs. There is not the capability to hold the value of the input. 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 3

Sequential Logic o o o Logic elements capable of storing a logic value. Sequential circuits are those circuits that employ these elements. Will be looking at the methodologies for sequential circuit design. 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 4

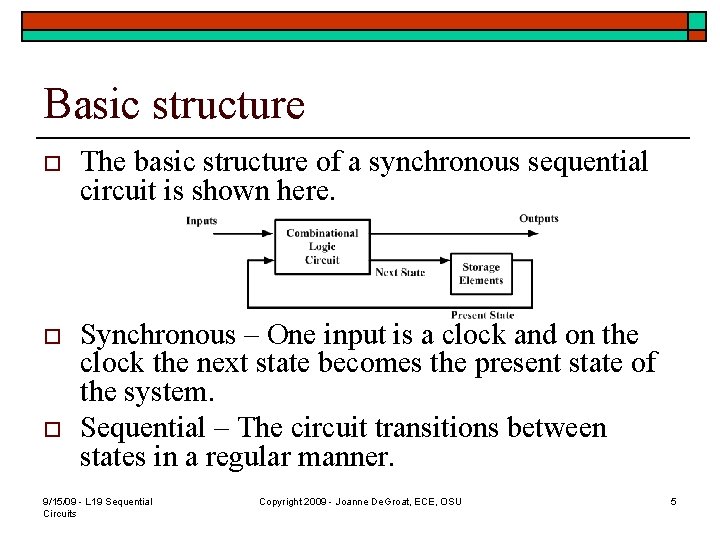

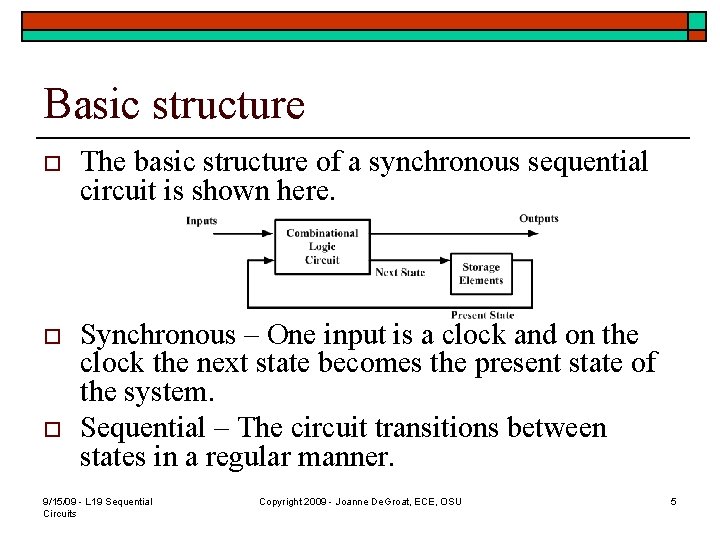

Basic structure o The basic structure of a synchronous sequential circuit is shown here. o Synchronous – One input is a clock and on the clock the next state becomes the present state of the system. Sequential – The circuit transitions between states in a regular manner. o 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 5

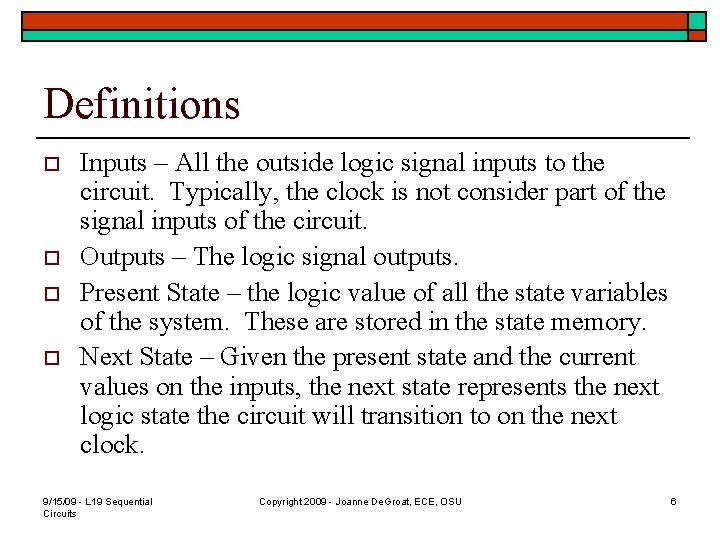

Definitions o o Inputs – All the outside logic signal inputs to the circuit. Typically, the clock is not consider part of the signal inputs of the circuit. Outputs – The logic signal outputs. Present State – the logic value of all the state variables of the system. These are stored in the state memory. Next State – Given the present state and the current values on the inputs, the next state represents the next logic state the circuit will transition to on the next clock. 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 6

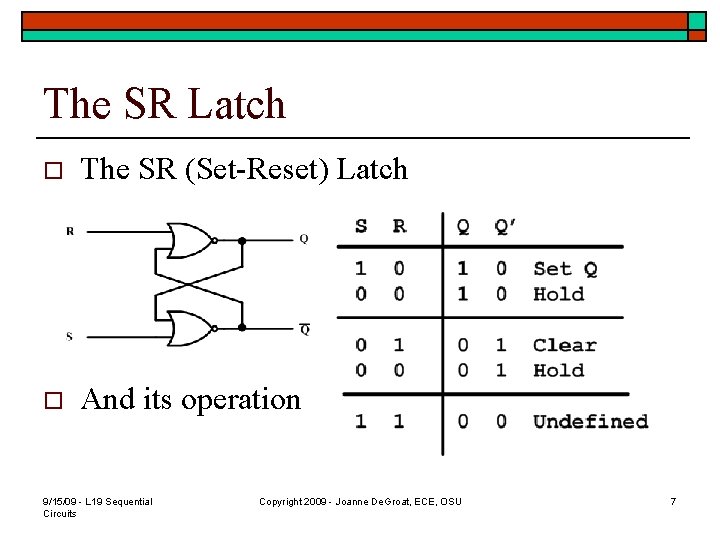

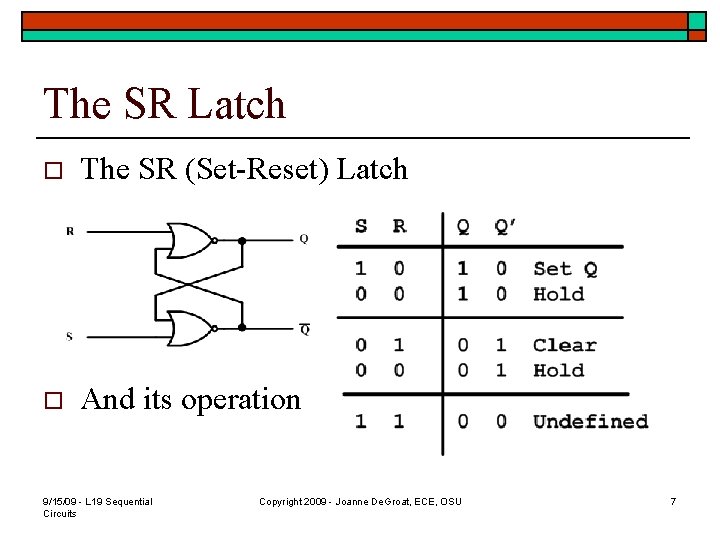

The SR Latch o The SR (Set-Reset) Latch o And its operation 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 7

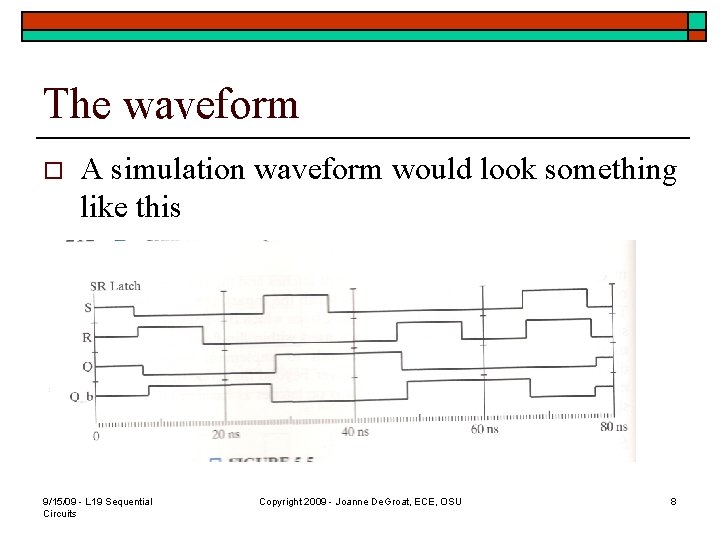

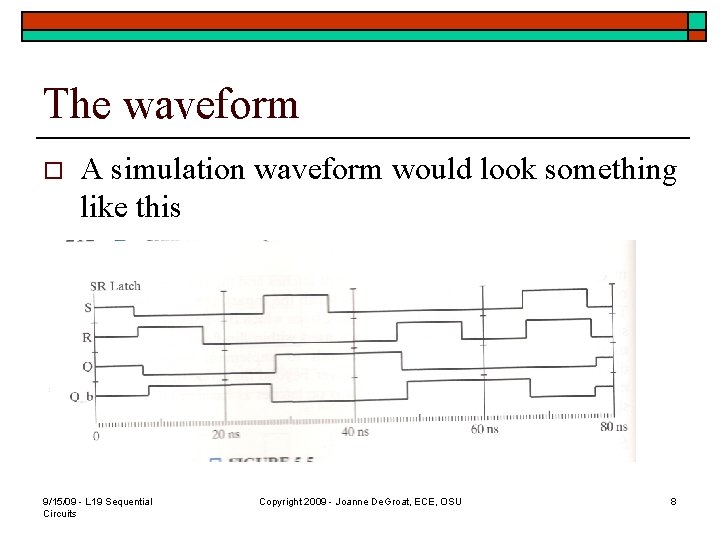

The waveform o A simulation waveform would look something like this 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 8

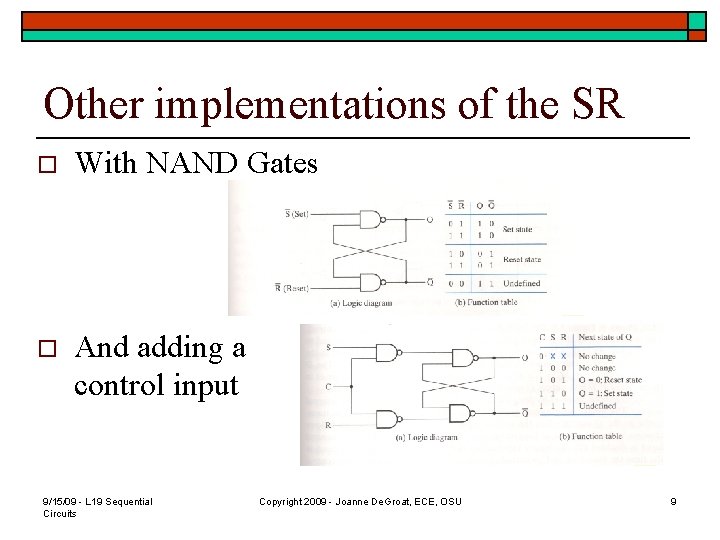

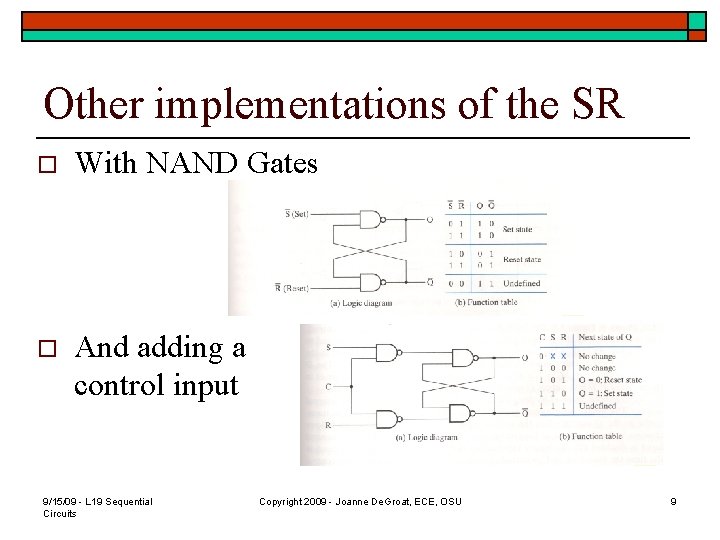

Other implementations of the SR o With NAND Gates o And adding a control input 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 9

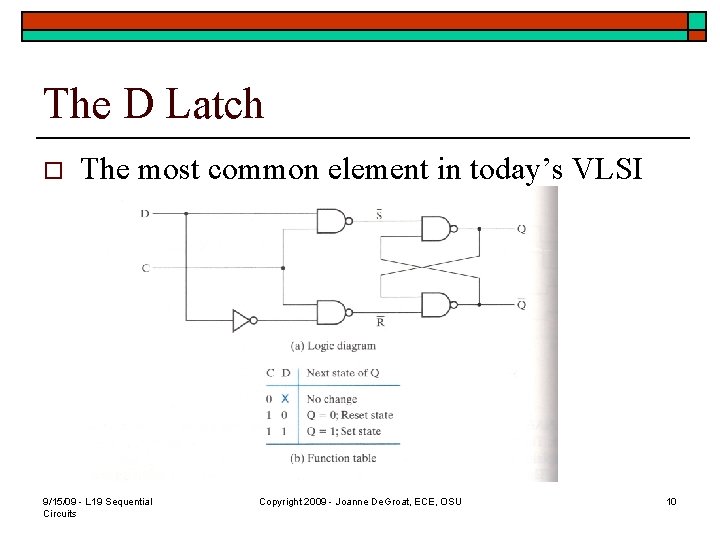

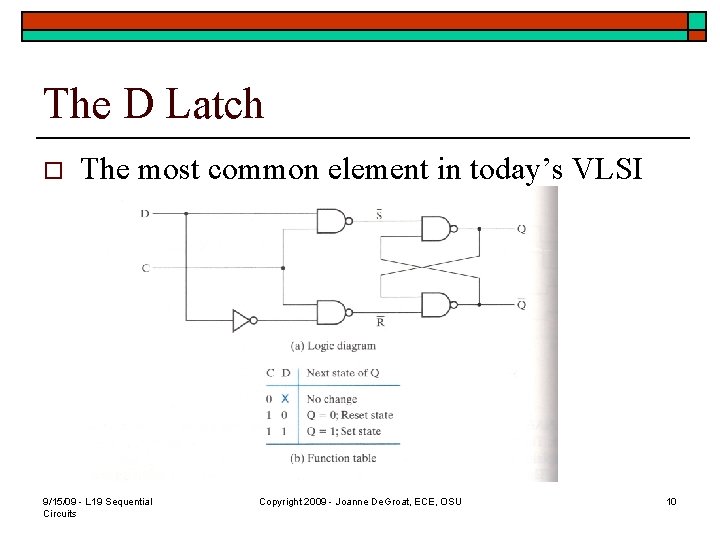

The D Latch o The most common element in today’s VLSI 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 10

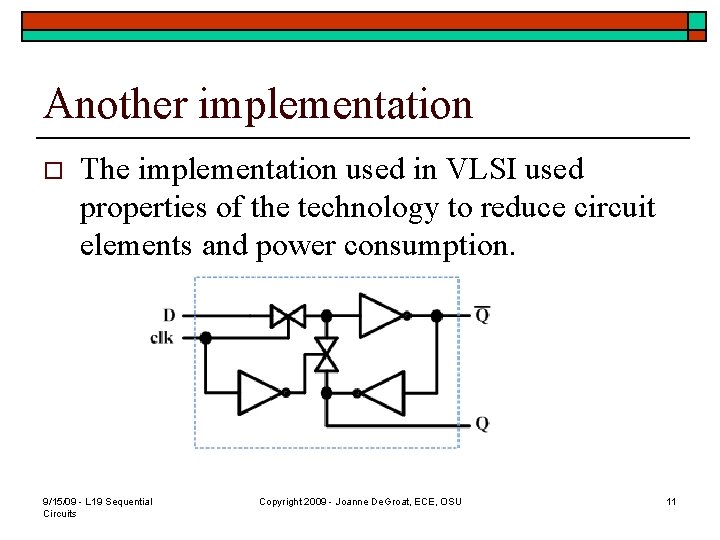

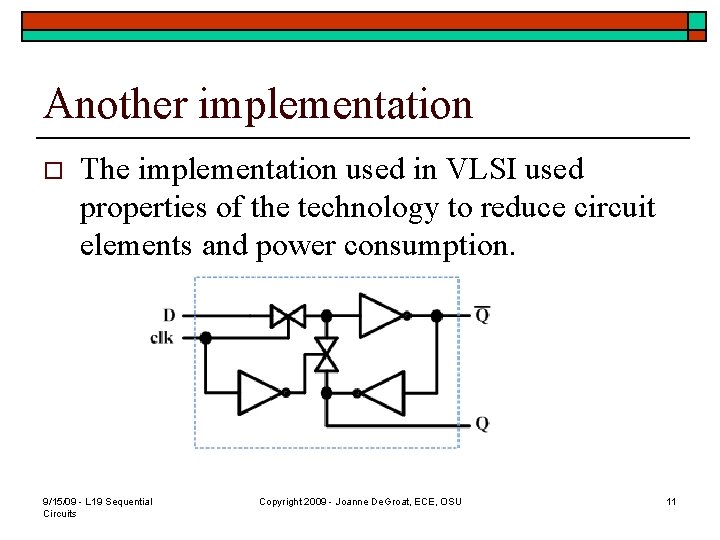

Another implementation o The implementation used in VLSI used properties of the technology to reduce circuit elements and power consumption. 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 11

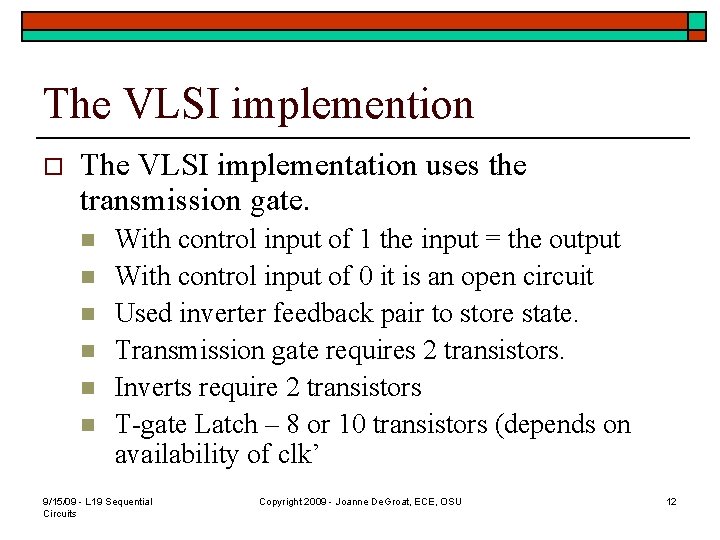

The VLSI implemention o The VLSI implementation uses the transmission gate. n n n With control input of 1 the input = the output With control input of 0 it is an open circuit Used inverter feedback pair to store state. Transmission gate requires 2 transistors. Inverts require 2 transistors T-gate Latch – 8 or 10 transistors (depends on availability of clk’ 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 12

Contrast with the gate circuit o o The D latch circuit in the text would take 18 transistors in a VLSI circuit. This is contrasted to 8 or 10 transistors. 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 13

Class 19 assignment o o Covered sections 5 -1 and 5 -2 Problems for hand in n o Problems for practice n o none 5 -2 Reading for next class: sections 5 -3 9/15/09 - L 19 Sequential Circuits Copyright 2009 - Joanne De. Groat, ECE, OSU 14