Seqeuential Logic State Machines Memory Note I did

![Memory Design – 1 K x 4 A[09: 00] Addr Block Select D[03: 00] Memory Design – 1 K x 4 A[09: 00] Addr Block Select D[03: 00]](https://slidetodoc.com/presentation_image_h2/02c5e810029ef78cb93277d82c6b005b/image-14.jpg)

![Memory Design – 1 K x 8 D[07: 04] D[03: 00] A[09: 00] D[03: Memory Design – 1 K x 8 D[07: 04] D[03: 00] A[09: 00] D[03:](https://slidetodoc.com/presentation_image_h2/02c5e810029ef78cb93277d82c6b005b/image-15.jpg)

![Memory Design - 2 k x 8 D[07: 04] Block 01 Block 00 D[03: Memory Design - 2 k x 8 D[07: 04] Block 01 Block 00 D[03:](https://slidetodoc.com/presentation_image_h2/02c5e810029ef78cb93277d82c6b005b/image-16.jpg)

![Memory Design - 4 k x 8 D[07: 04] Block 11 Block 10 Block Memory Design - 4 k x 8 D[07: 04] Block 11 Block 10 Block](https://slidetodoc.com/presentation_image_h2/02c5e810029ef78cb93277d82c6b005b/image-17.jpg)

- Slides: 34

• Seqeuential Logic • State Machines • Memory Note: I did clean up the slides from last period, particularly improving the Flip. Flop transition tables. Note: About making past midterms and finals available.

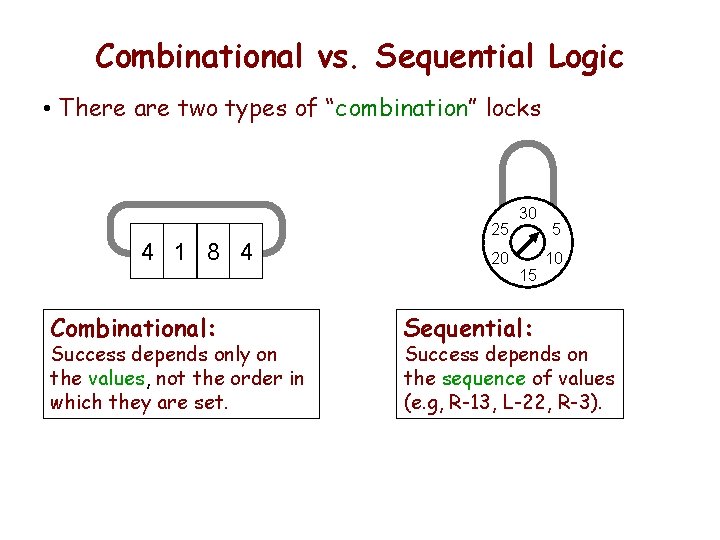

Combinational vs. Sequential Logic • There are two types of “combination” locks 25 4 1 8 4 Combinational: Success depends only on the values, not the order in which they are set. 20 30 15 Sequential: 5 10 Success depends on the sequence of values (e. g, R-13, L-22, R-3).

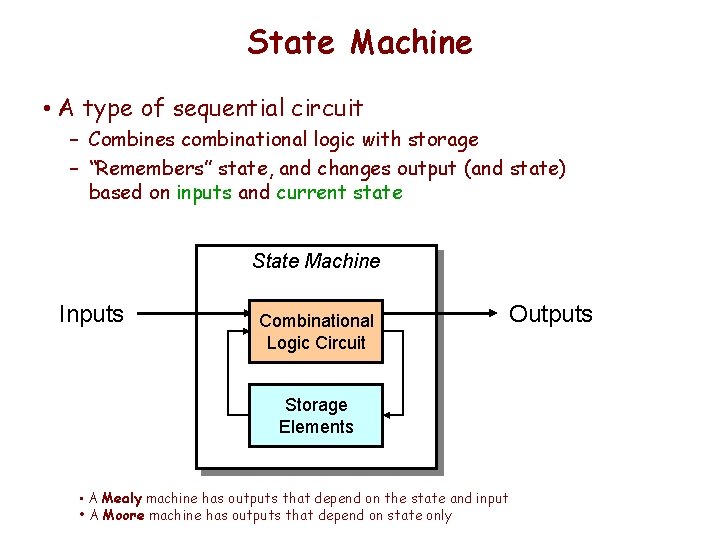

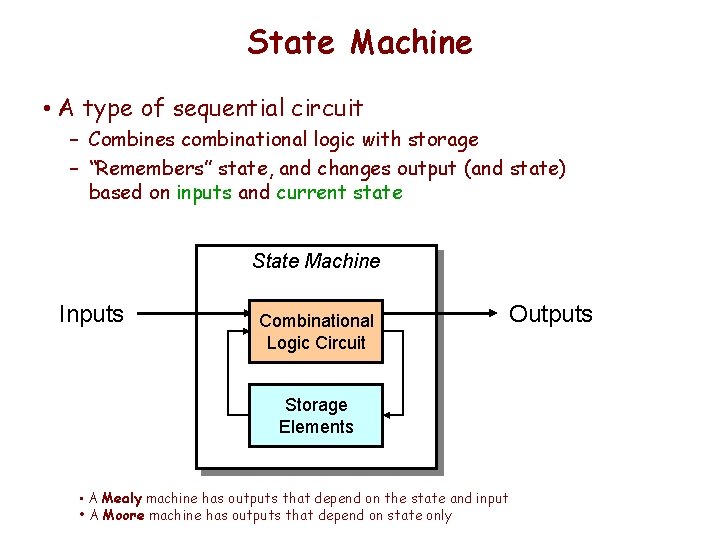

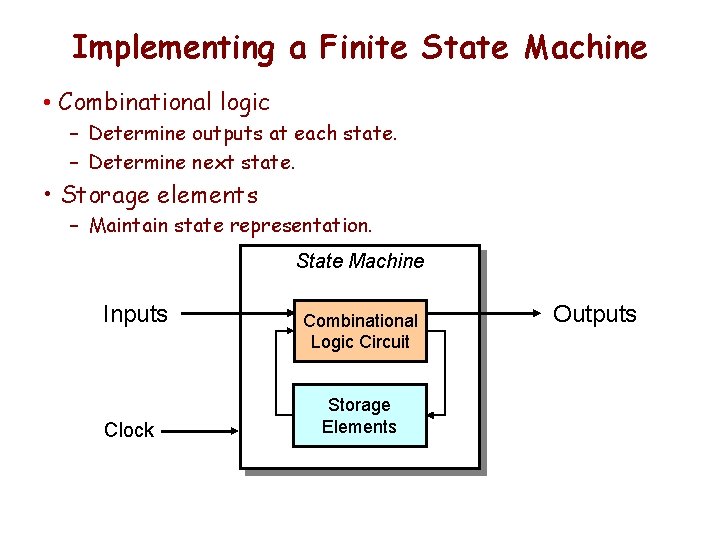

State Machine • A type of sequential circuit – Combines combinational logic with storage – “Remembers” state, and changes output (and state) based on inputs and current state State Machine Inputs Combinational Logic Circuit Storage Elements • A Mealy machine has outputs that depend on the state and input • A Moore machine has outputs that depend on state only Outputs

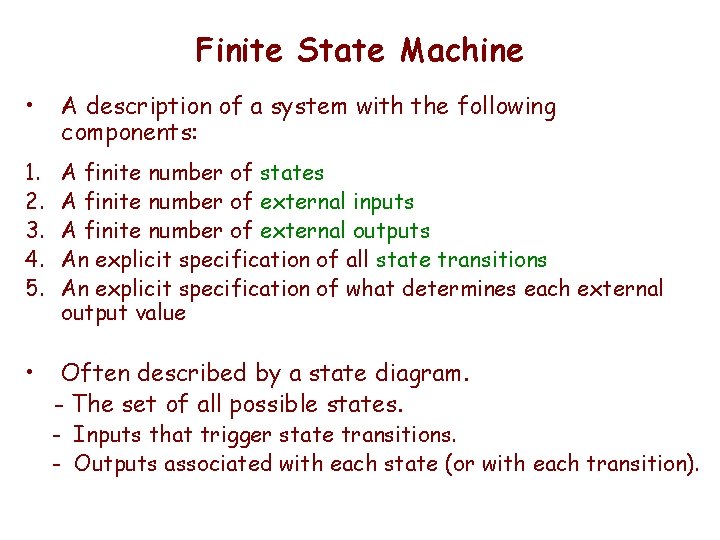

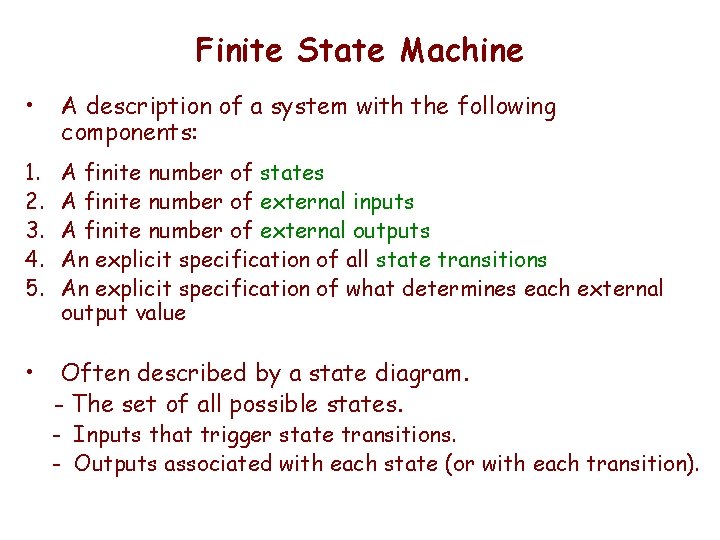

Finite State Machine • A description of a system with the following components: 1. 2. 3. 4. 5. A finite number of states A finite number of external inputs A finite number of external outputs An explicit specification of all state transitions An explicit specification of what determines each external output value • Often described by a state diagram. - The set of all possible states. - Inputs that trigger state transitions. - Outputs associated with each state (or with each transition).

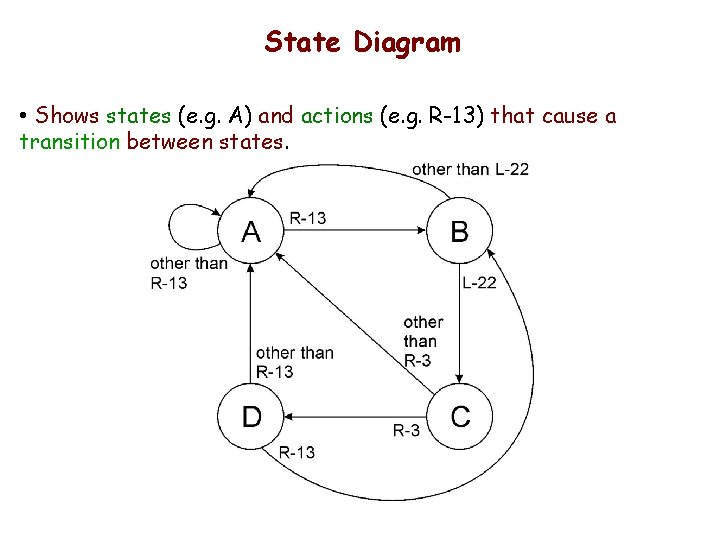

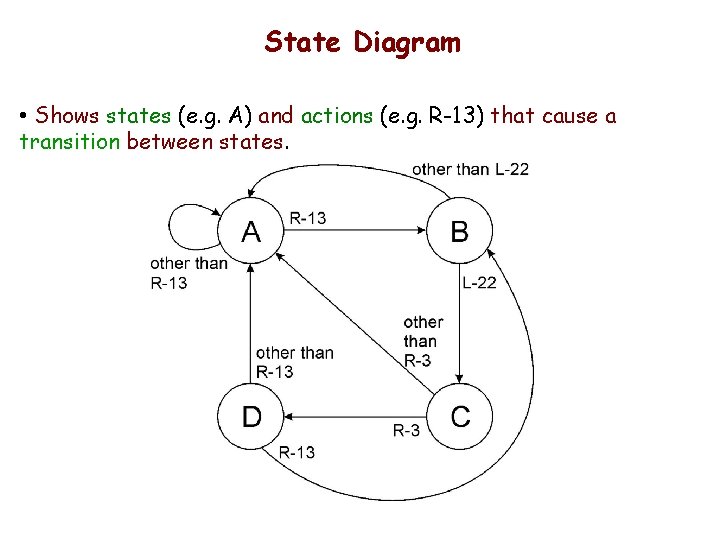

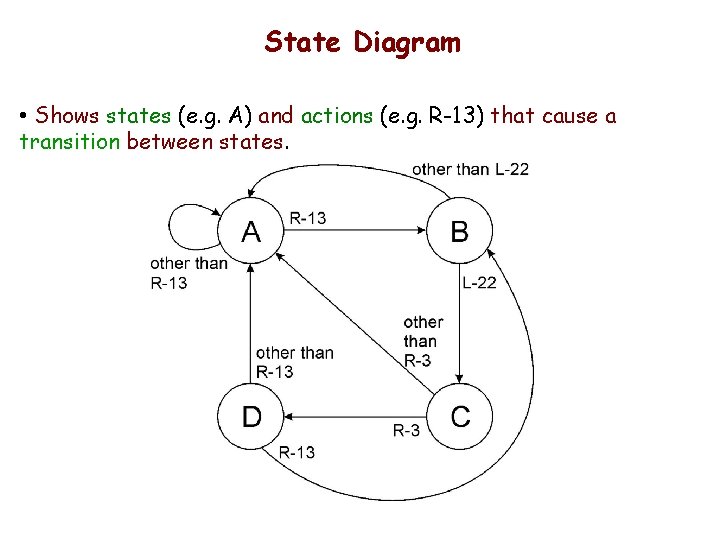

State Diagram • Shows states (e. g. A) and actions (e. g. R-13) that cause a transition between states.

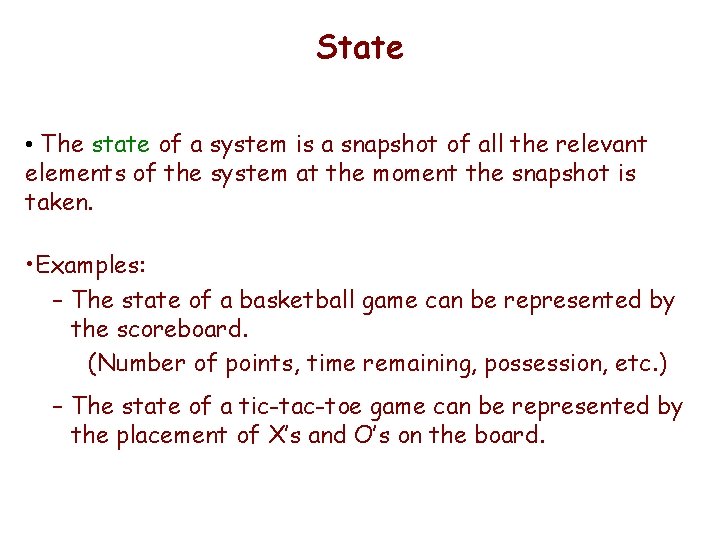

State • The state of a system is a snapshot of all the relevant elements of the system at the moment the snapshot is taken. • Examples: – The state of a basketball game can be represented by the scoreboard. (Number of points, time remaining, possession, etc. ) – The state of a tic-tac-toe game can be represented by the placement of X’s and O’s on the board.

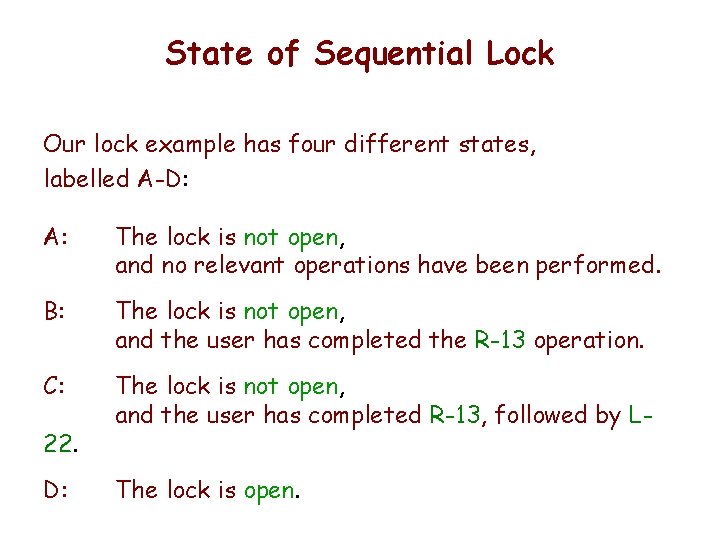

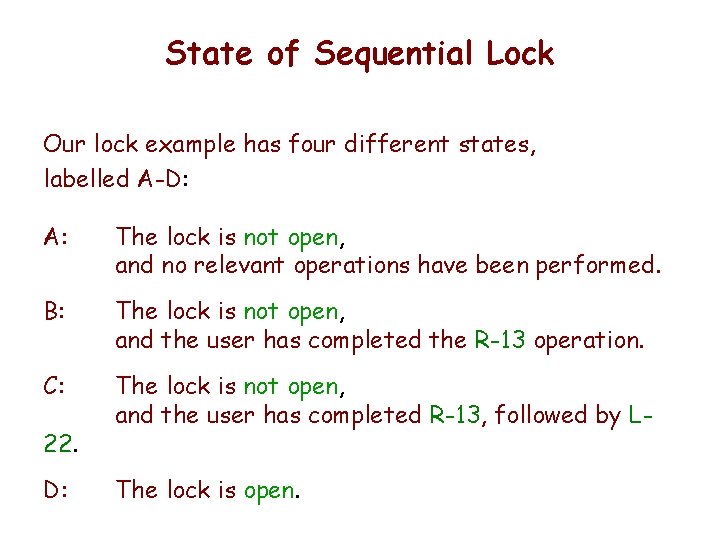

State of Sequential Lock Our lock example has four different states, labelled A-D: A: The lock is not open, and no relevant operations have been performed. B: The lock is not open, and the user has completed the R-13 operation. C: The lock is not open, and the user has completed R-13, followed by L- 22. D: The lock is open.

State Diagram • Shows states (e. g. A) and actions (e. g. R-13) that cause a transition between states.

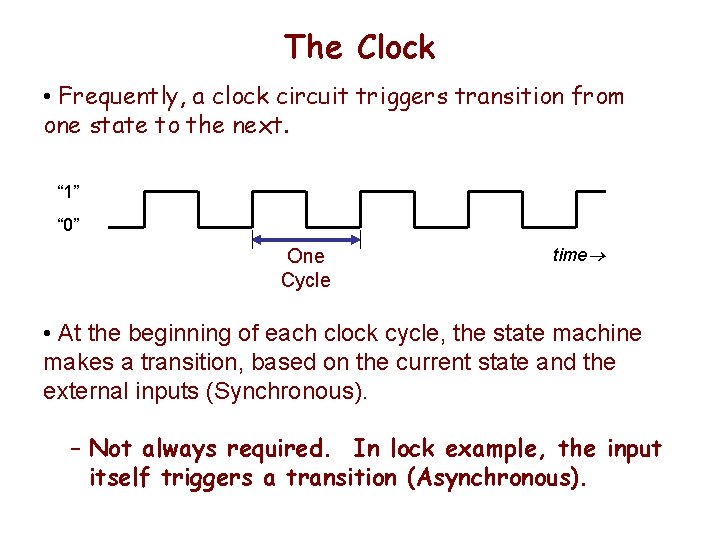

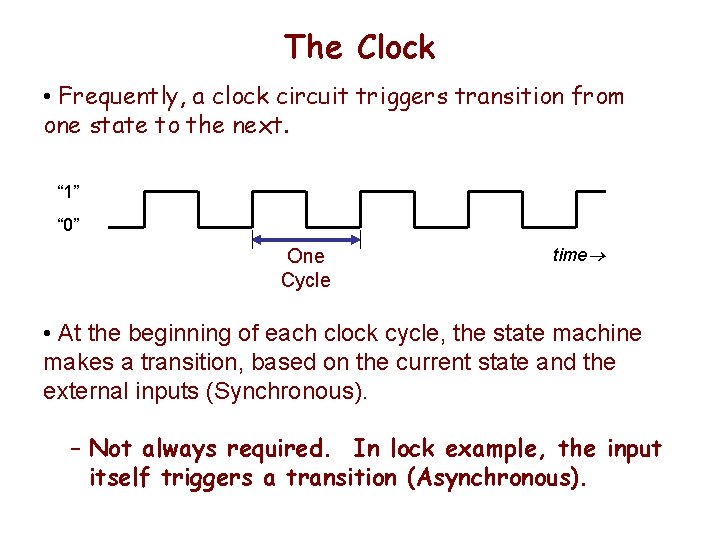

The Clock • Frequently, a clock circuit triggers transition from one state to the next. “ 1” “ 0” One Cycle time • At the beginning of each clock cycle, the state machine makes a transition, based on the current state and the external inputs (Synchronous). – Not always required. In lock example, the input itself triggers a transition (Asynchronous).

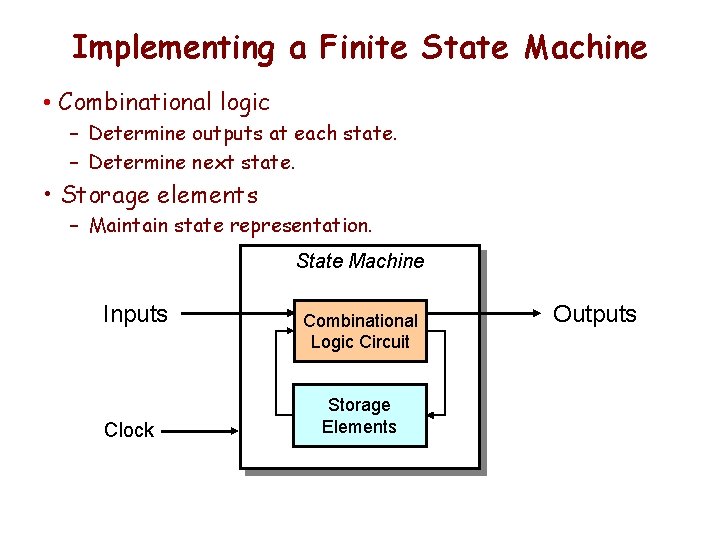

Implementing a Finite State Machine • Combinational logic – Determine outputs at each state. – Determine next state. • Storage elements – Maintain state representation. State Machine Inputs Clock Combinational Logic Circuit Storage Elements Outputs

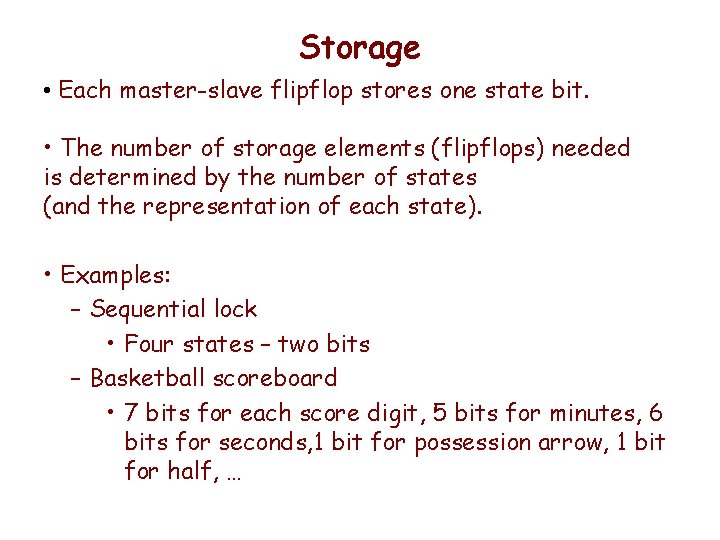

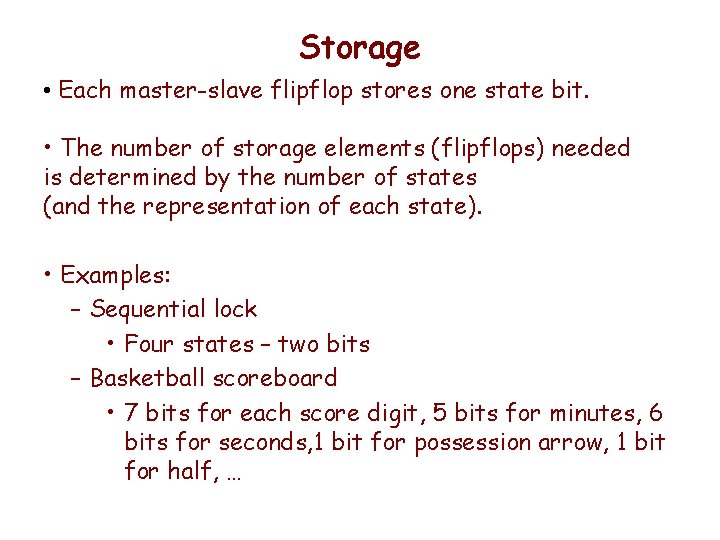

Storage • Each master-slave flipflop stores one state bit. • The number of storage elements (flipflops) needed is determined by the number of states (and the representation of each state). • Examples: – Sequential lock • Four states – two bits – Basketball scoreboard • 7 bits for each score digit, 5 bits for minutes, 6 bits for seconds, 1 bit for possession arrow, 1 bit for half, …

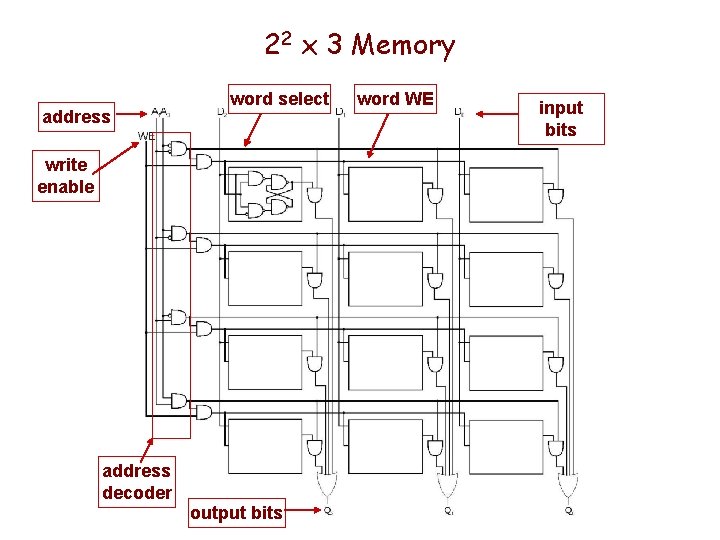

22 x 3 Memory address word select write enable address decoder output bits word WE input bits

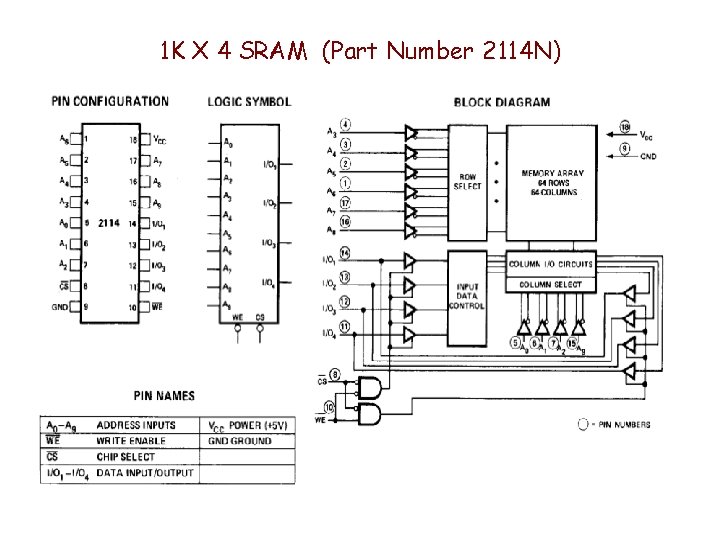

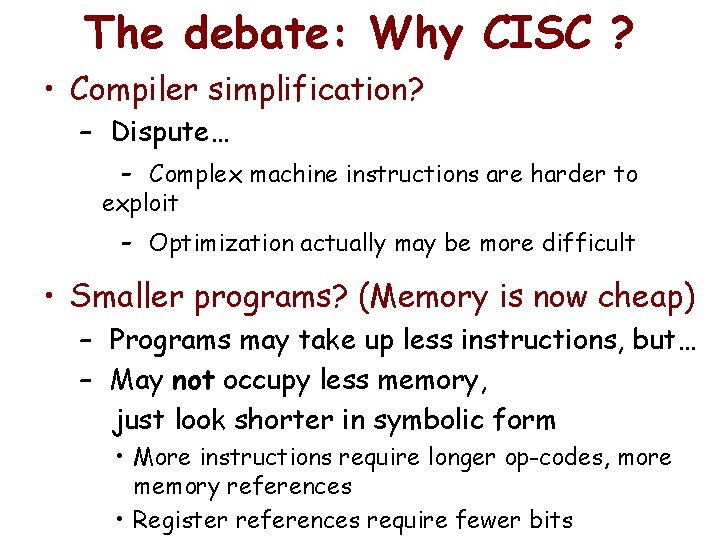

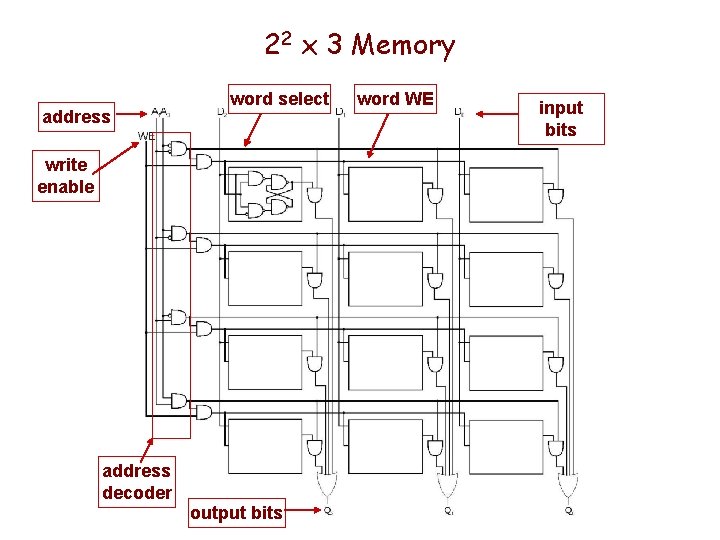

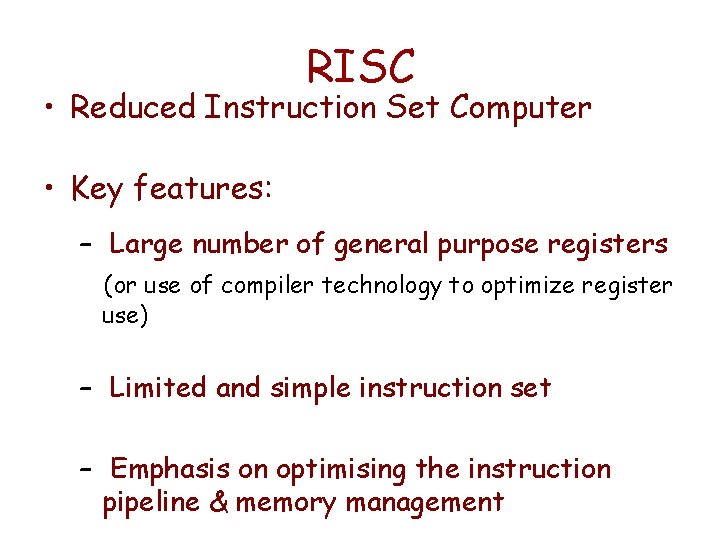

1 K X 4 SRAM (Part Number 2114 N)

![Memory Design 1 K x 4 A09 00 Addr Block Select D03 00 Memory Design – 1 K x 4 A[09: 00] Addr Block Select D[03: 00]](https://slidetodoc.com/presentation_image_h2/02c5e810029ef78cb93277d82c6b005b/image-14.jpg)

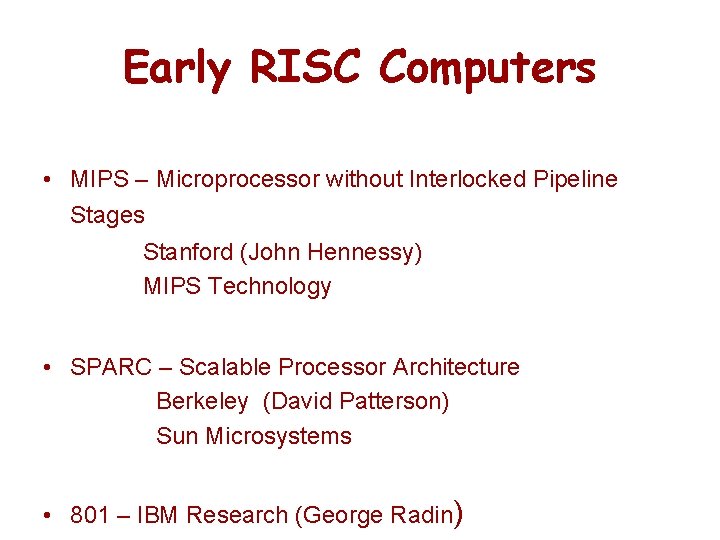

Memory Design – 1 K x 4 A[09: 00] Addr Block Select D[03: 00]

![Memory Design 1 K x 8 D07 04 D03 00 A09 00 D03 Memory Design – 1 K x 8 D[07: 04] D[03: 00] A[09: 00] D[03:](https://slidetodoc.com/presentation_image_h2/02c5e810029ef78cb93277d82c6b005b/image-15.jpg)

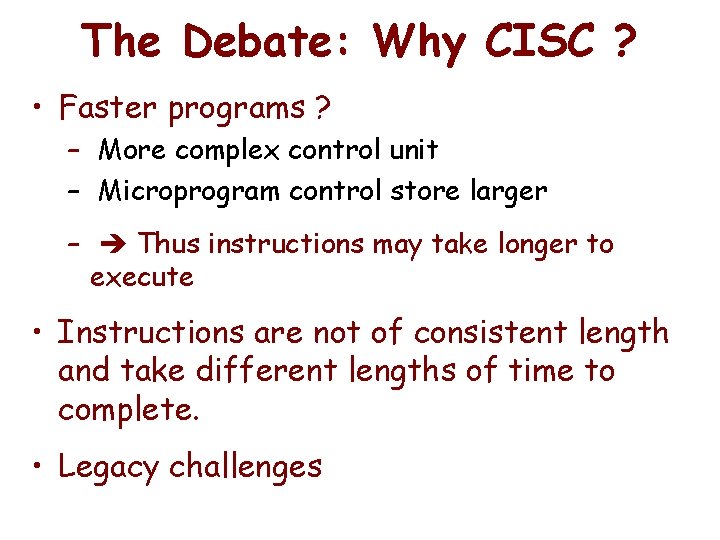

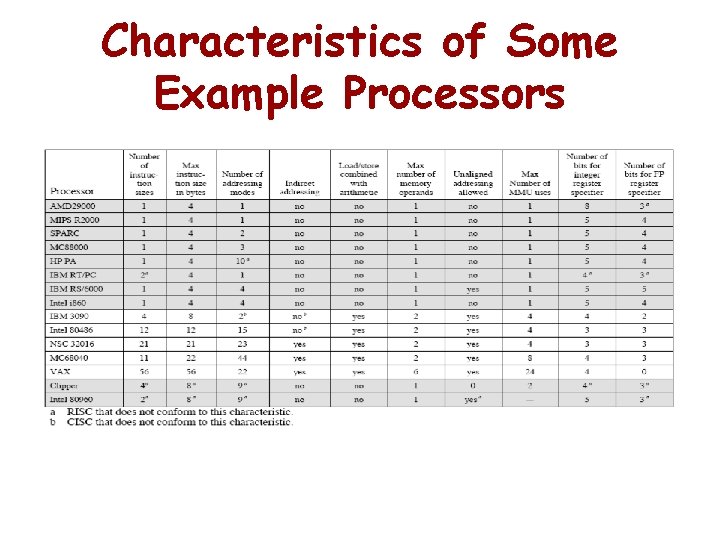

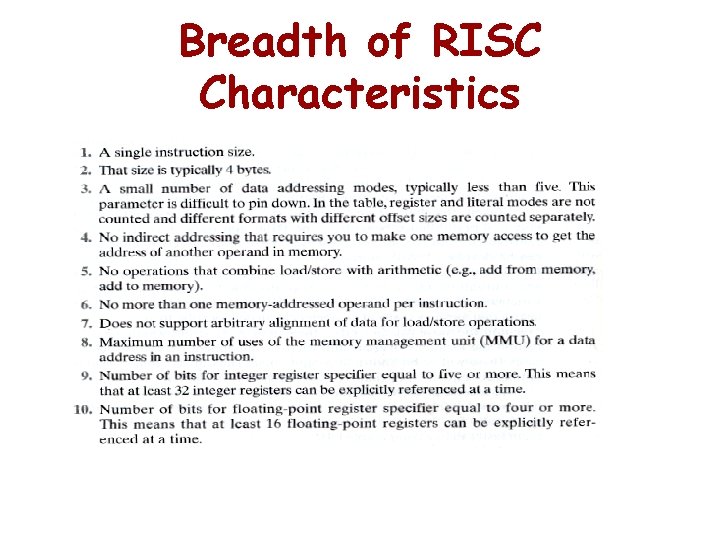

Memory Design – 1 K x 8 D[07: 04] D[03: 00] A[09: 00] D[03: 00] D[07: 04] Addr Block Select =>

![Memory Design 2 k x 8 D07 04 Block 01 Block 00 D03 Memory Design - 2 k x 8 D[07: 04] Block 01 Block 00 D[03:](https://slidetodoc.com/presentation_image_h2/02c5e810029ef78cb93277d82c6b005b/image-16.jpg)

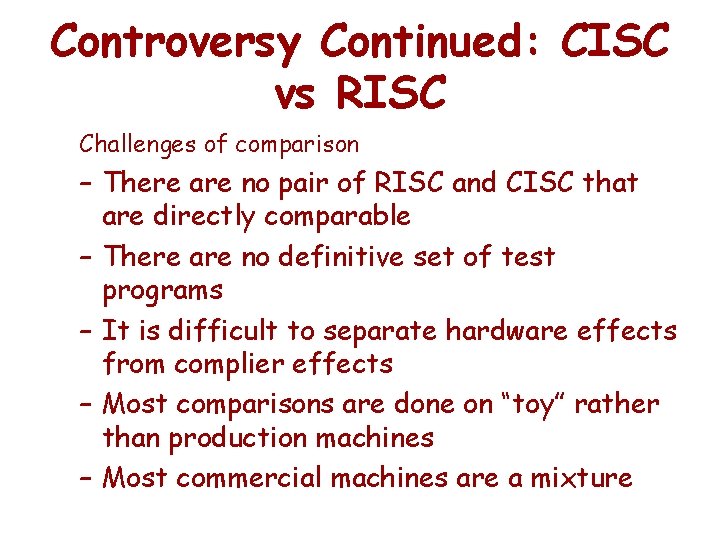

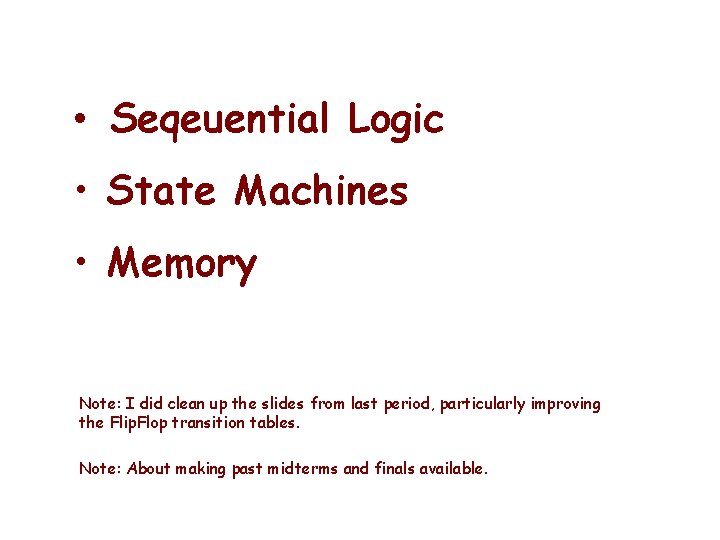

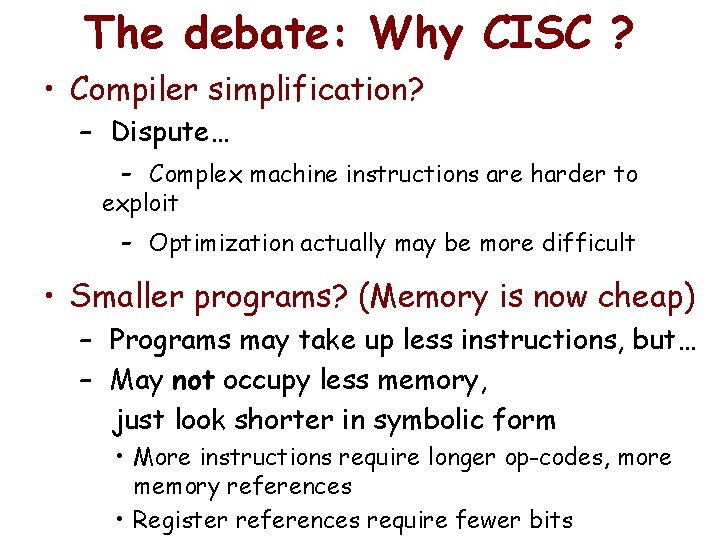

Memory Design - 2 k x 8 D[07: 04] Block 01 Block 00 D[03: 00]

![Memory Design 4 k x 8 D07 04 Block 11 Block 10 Block Memory Design - 4 k x 8 D[07: 04] Block 11 Block 10 Block](https://slidetodoc.com/presentation_image_h2/02c5e810029ef78cb93277d82c6b005b/image-17.jpg)

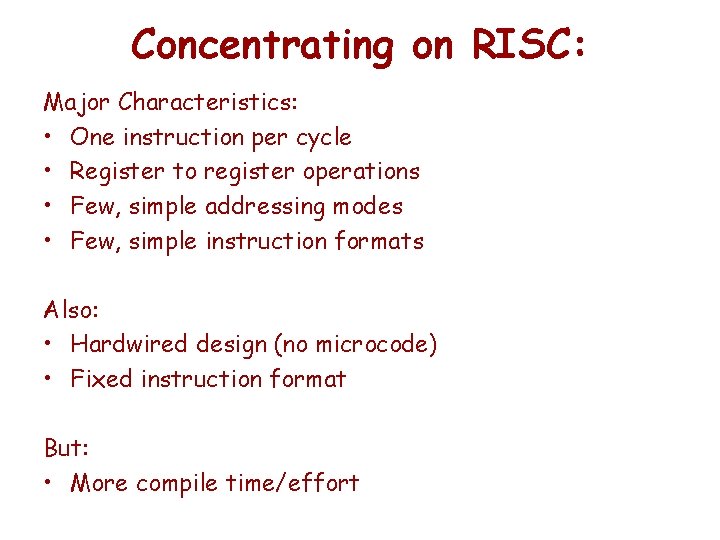

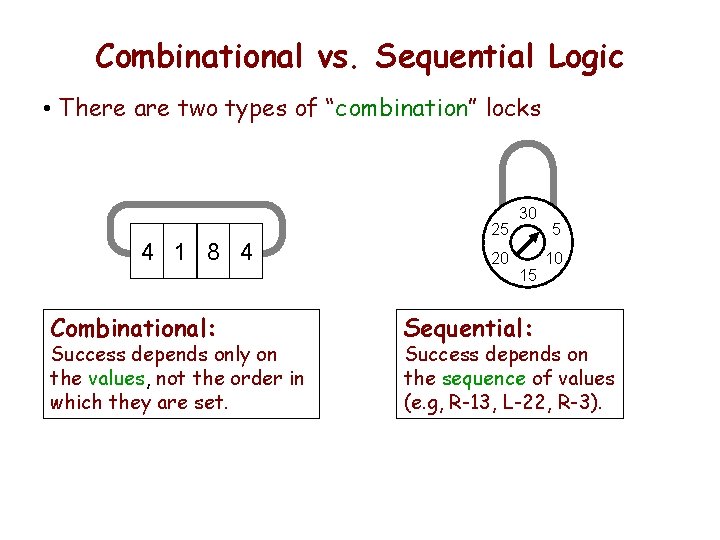

Memory Design - 4 k x 8 D[07: 04] Block 11 Block 10 Block 01 Block 00 D[03: 00]

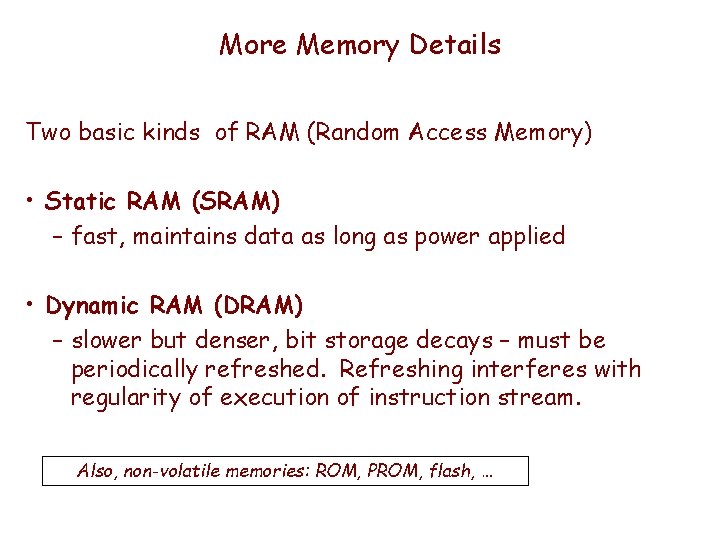

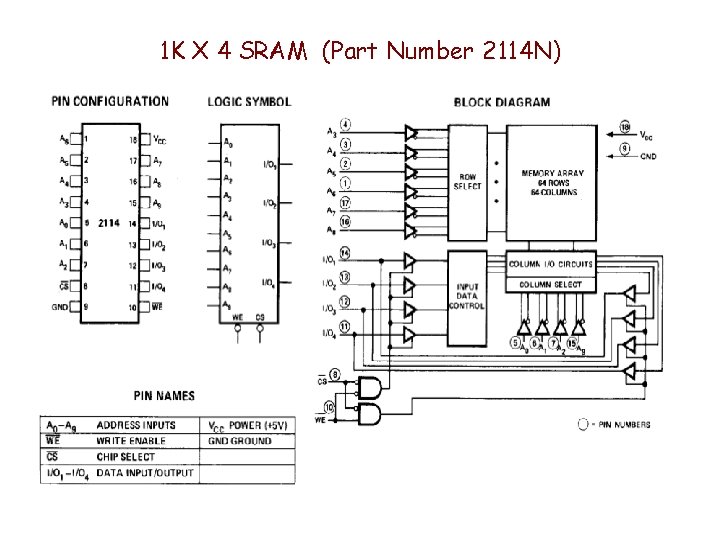

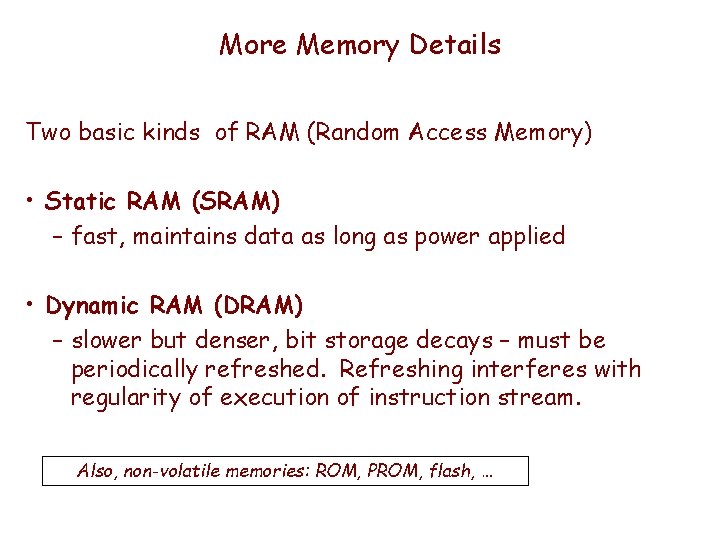

More Memory Details Two basic kinds of RAM (Random Access Memory) • Static RAM (SRAM) – fast, maintains data as long as power applied • Dynamic RAM (DRAM) – slower but denser, bit storage decays – must be periodically refreshed. Refreshing interferes with regularity of execution of instruction stream. Also, non-volatile memories: ROM, PROM, flash, …

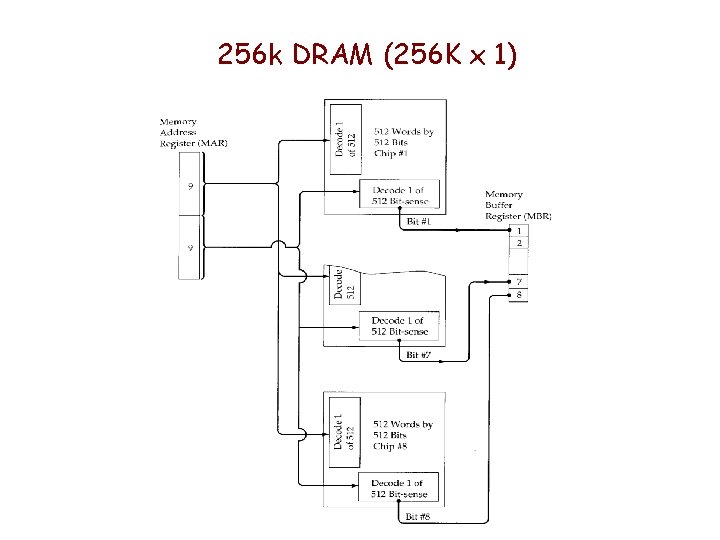

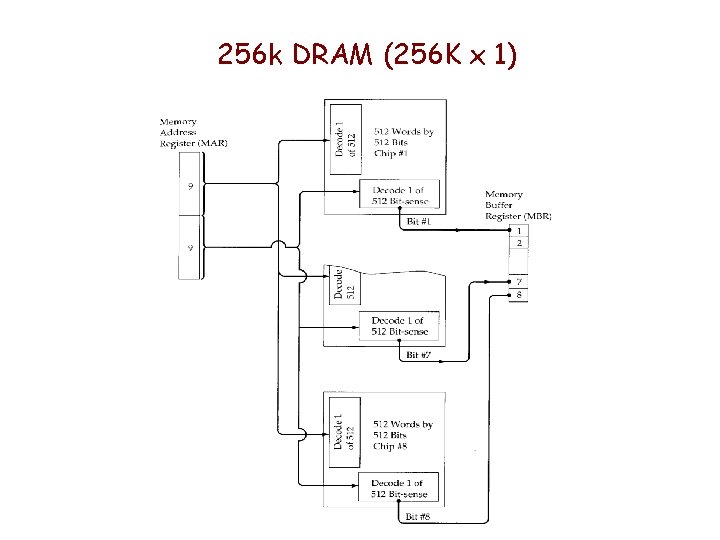

256 k DRAM (256 K x 1)

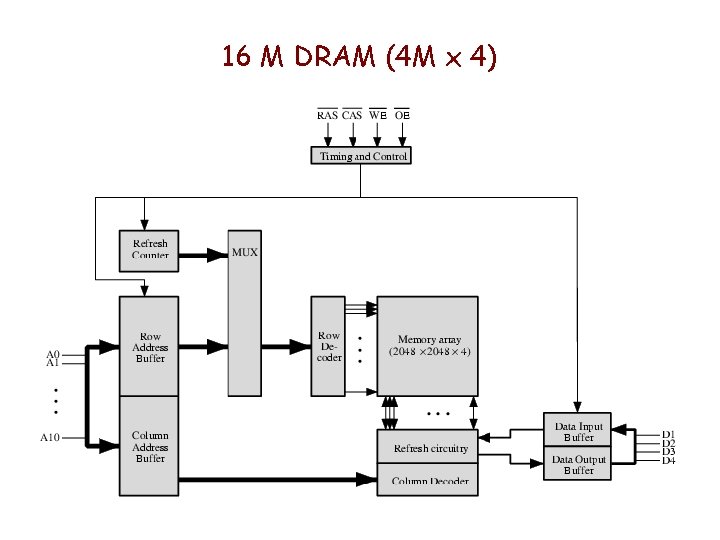

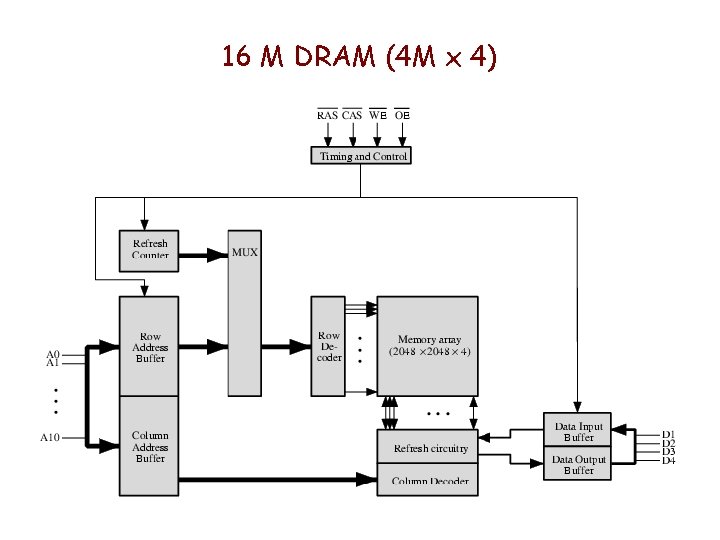

16 M DRAM (4 M x 4)

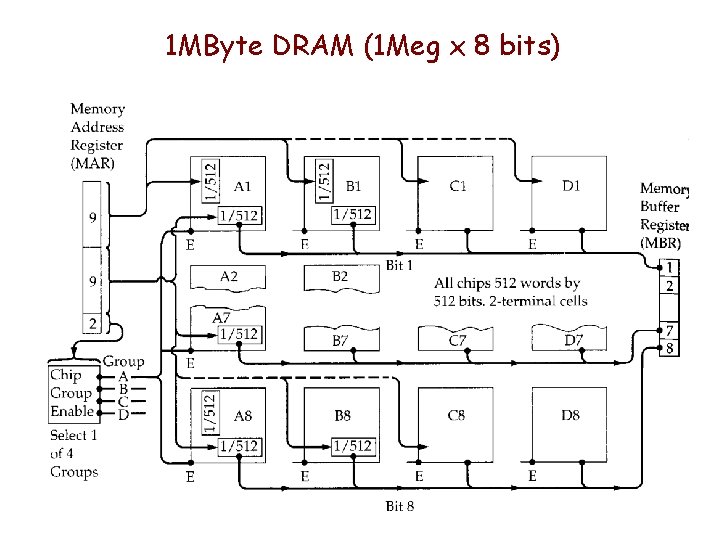

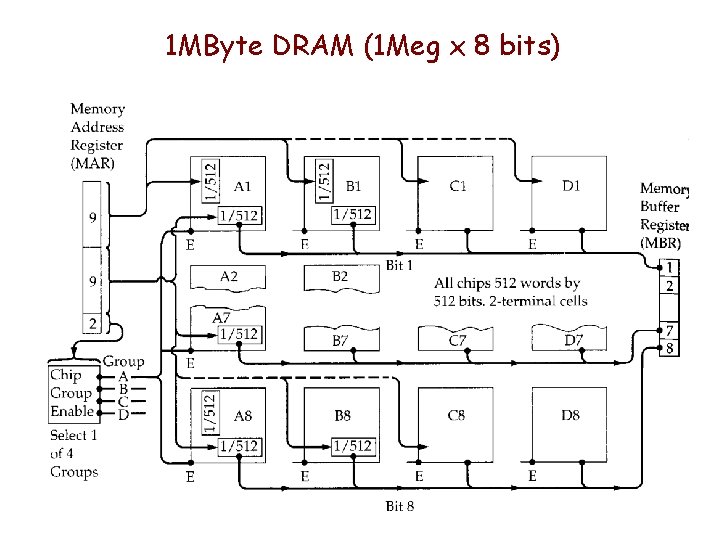

1 MByte DRAM (1 Meg x 8 bits)

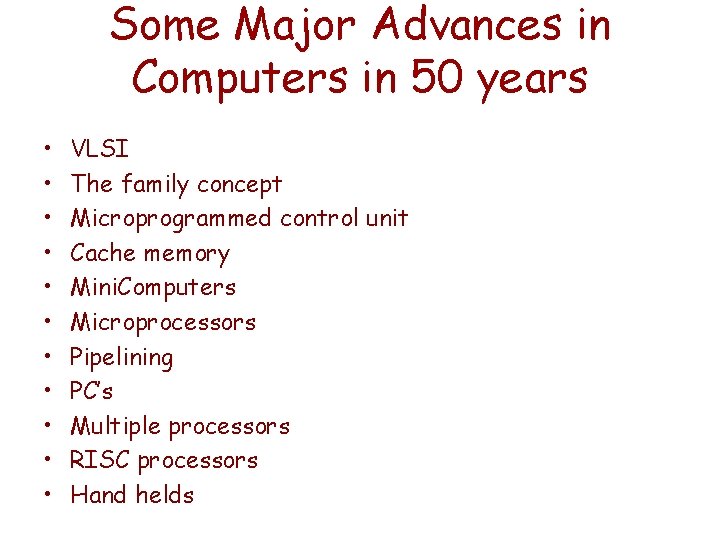

Some Major Advances in Computers in 50 years • • • VLSI The family concept Microprogrammed control unit Cache memory Mini. Computers Microprocessors Pipelining PC’s Multiple processors RISC processors Hand helds

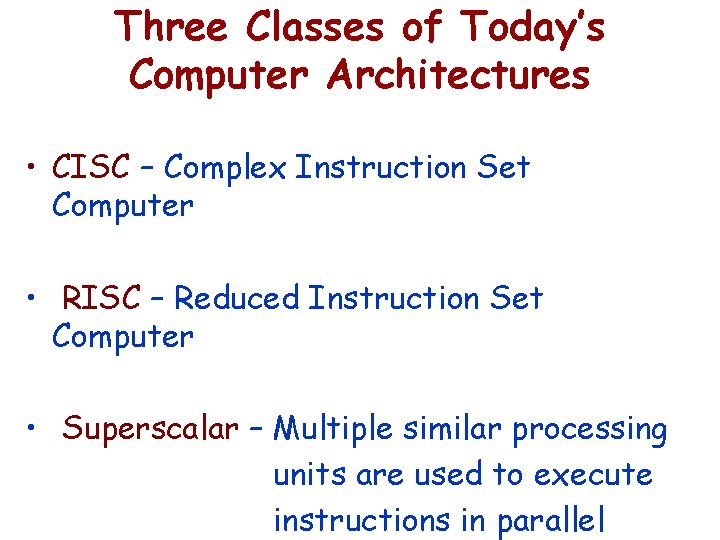

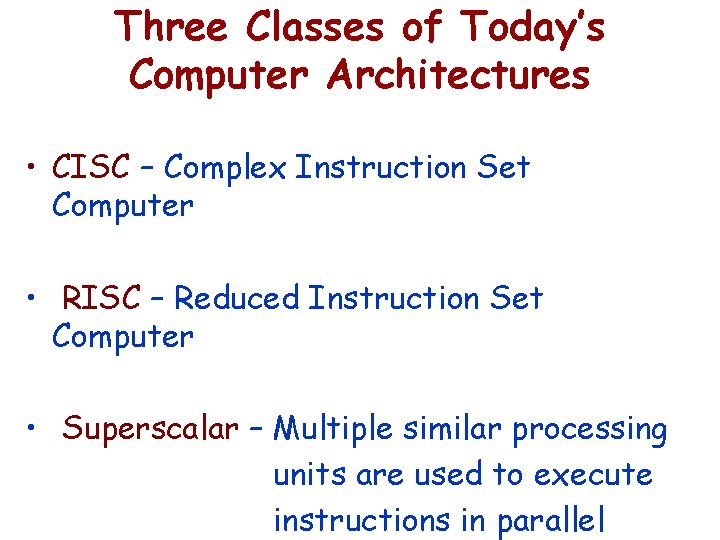

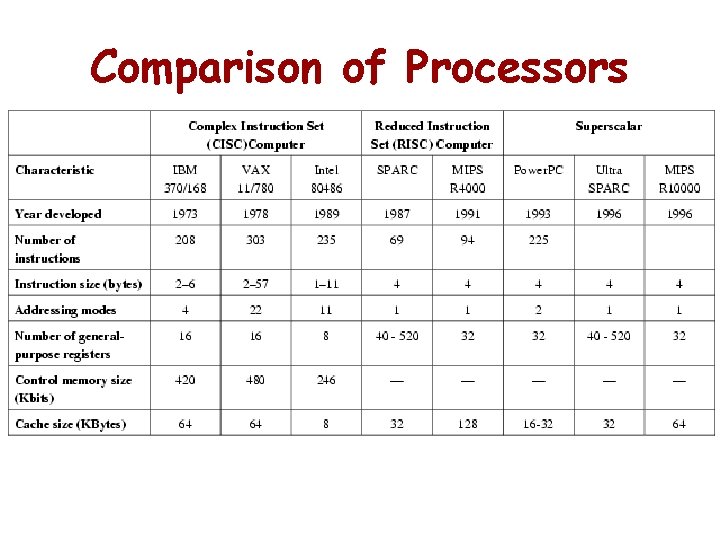

Three Classes of Today’s Computer Architectures • CISC – Complex Instruction Set Computer • RISC – Reduced Instruction Set Computer • Superscalar – Multiple similar processing units are used to execute instructions in parallel

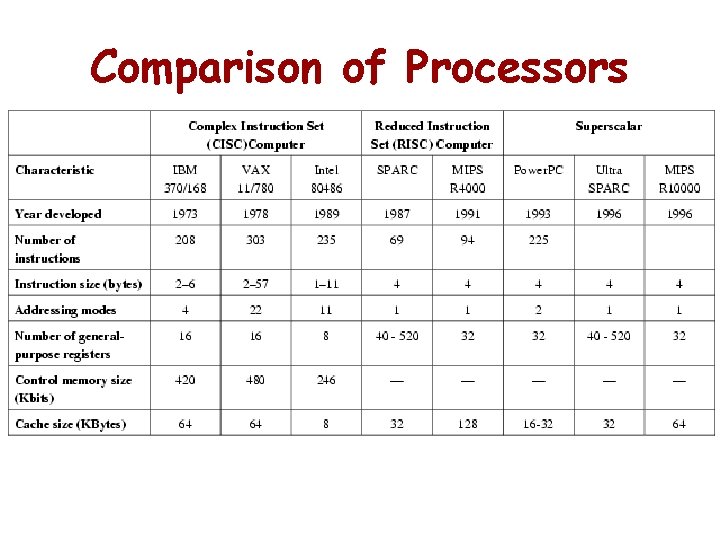

Comparison of Processors

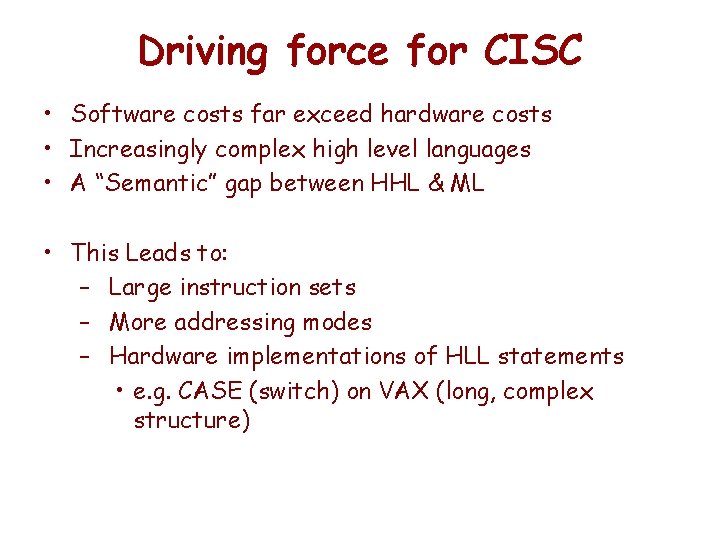

Driving force for CISC • Software costs far exceed hardware costs • Increasingly complex high level languages • A “Semantic” gap between HHL & ML • This Leads to: – Large instruction sets – More addressing modes – Hardware implementations of HLL statements • e. g. CASE (switch) on VAX (long, complex structure)

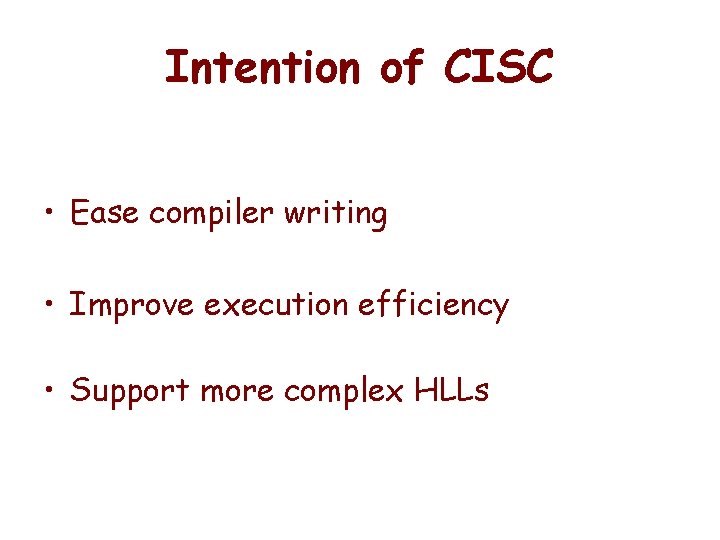

Intention of CISC • Ease compiler writing • Improve execution efficiency • Support more complex HLLs

RISC • Reduced Instruction Set Computer • Key features: – Large number of general purpose registers (or use of compiler technology to optimize register use) – Limited and simple instruction set – Emphasis on optimising the instruction pipeline & memory management

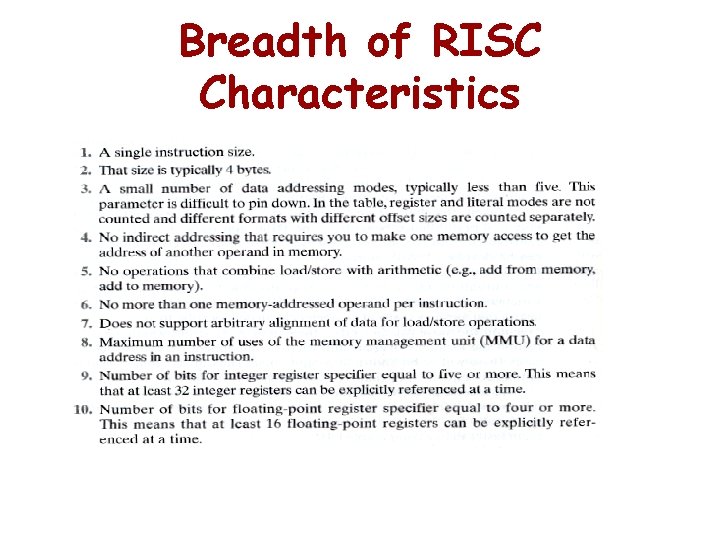

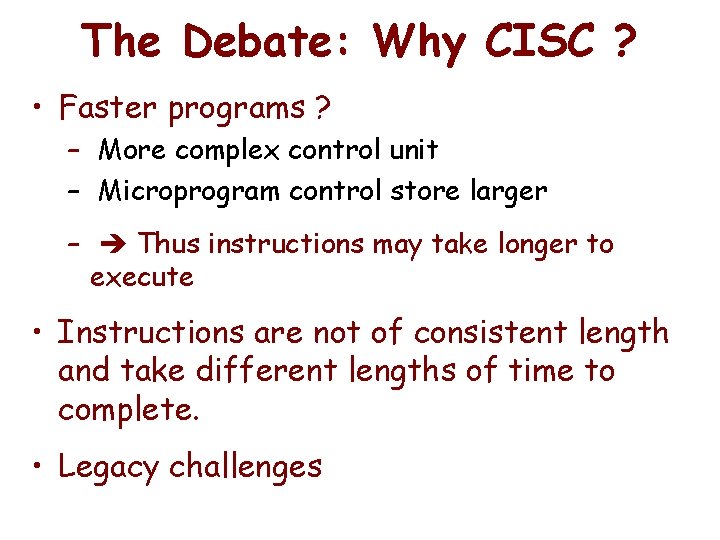

Breadth of RISC Characteristics

The debate: Why CISC ? • Compiler simplification? – Dispute… - Complex machine instructions are harder to exploit - Optimization actually may be more difficult • Smaller programs? (Memory is now cheap) – Programs may take up less instructions, but… – May not occupy less memory, just look shorter in symbolic form • More instructions require longer op-codes, more memory references • Register references require fewer bits

The Debate: Why CISC ? • Faster programs ? – More complex control unit – Microprogram control store larger – Thus instructions may take longer to execute • Instructions are not of consistent length and take different lengths of time to complete. • Legacy challenges

Controversy Continued: CISC vs RISC Challenges of comparison – There are no pair of RISC and CISC that are directly comparable – There are no definitive set of test programs – It is difficult to separate hardware effects from complier effects – Most comparisons are done on “toy” rather than production machines – Most commercial machines are a mixture

Concentrating on RISC: Major Characteristics: • One instruction per cycle • Register to register operations • Few, simple addressing modes • Few, simple instruction formats Also: • Hardwired design (no microcode) • Fixed instruction format But: • More compile time/effort

Early RISC Computers • MIPS – Microprocessor without Interlocked Pipeline Stages Stanford (John Hennessy) MIPS Technology • SPARC – Scalable Processor Architecture Berkeley (David Patterson) Sun Microsystems • 801 – IBM Research (George Radin)

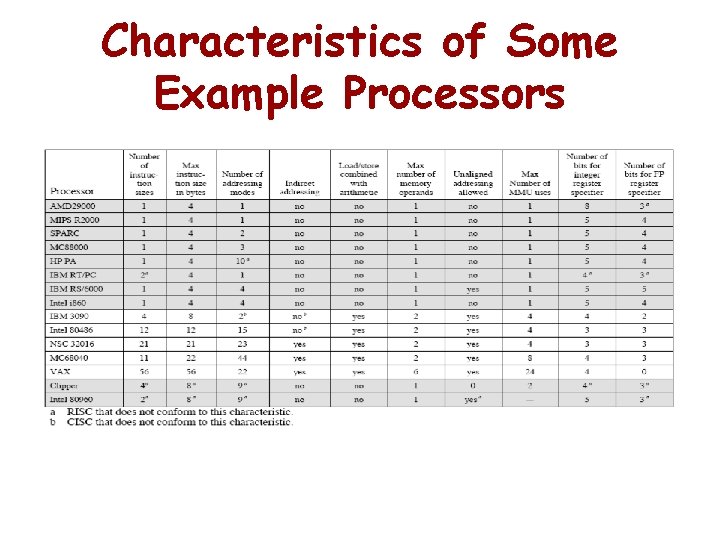

Characteristics of Some Example Processors