September 2004 doc IEEE 802 15 040516 r

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Project: IEEE P 802. 15 Working Group for Wireless Personal Area Networks (WPANs) Submission Title: [DS-UWB Responses to TG 3 a. Voter NO Comments – Proposal Description] Date Submitted: [September 2004] Source: [Matt Welborn] Company [Freescale Semiconductor, Inc] Address [8133 Leesburg Pike] Voice: [703 -269 -3000], E-Mail: [matt. welborn @freescale. com] Re: [] Abstract: [Response to NO voter comments and feedback regarding the DS-UWB (Merger #2) Proposal] Purpose: [Provide technical information to the TG 3 a voters regarding DS-UWB (Merger #2) Proposal] Notice: This document has been prepared to assist the IEEE P 802. 15. It is offered as a basis for discussion and is not binding on the contributing individual(s) or organization(s). The material in this document is subject to change in form and content after further study. The contributor(s) reserve(s) the right to add, amend or withdraw material contained herein. Release: The contributor acknowledges and accepts that this contribution becomes the property of IEEE and may be made publicly available by P 802. 15. Submission 1 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Topic: Consistency • Typical comments – The information presented by merge proposal #2 is in a fashion that is confusing as it does not stay true to modes of operation, performance capabilities and complexity/power consumption. There are insufficient details on the transmitter and receiver architecture, coding schemes, modulation for validation of the claims presented by merge proposal #2. – Another critical aspect of the PHY will be robustness. I do not yet have the confidence that the proposed system will deliver the performance necessary to achieve market place acceptance in consumer applications. I do not question the performance numbers but functions relegated to the digital realm. Extensive digital processing of these wide band manner. When these items are addressed and if I find no other compelling reasons for voting no, I will consider changing my vote from no to yes. Submission 2 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Topic: Consistency • Typical comments – In presenting merged proposal #2, the authors often cite statistics out of context, or change operational parameters in order to maximize performance in the particular direction. It places undue strain on voters to independently verify each assertion of the proposal, in order to determine what was given up in order to reach stated level of performance. – I am not convinced that the performance simulation results are sufficient to prove its high-speed connectivity in real-world situations, considering that your proposal underwent a major change quite recently last March Submission 3 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Response • A review of the history of the Merger#2 proposal • A clear summary presentation of the DS-UWB proposal • Consistent & complete performance and complexity results Submission 4 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 History of Merger #2 Proposal • Merger #2 proposal history – Merger between two proposals (Xtreme. Spectrum & Parthus Ceva) in July 2003 – Merger with CRL & Oki in September 2003 – Modifications in March 2004: • • In response to extensive feedback from MB-OFDM team Exclusively BPSK (4 -BOK only in optional modes) Added shorter code lengths (same L=24 codes as before) Changed FEC back to k=6 (k=4 optional) instead of k=7 – March/May/July/September 2004 • Proposal is stable, presented numerous simulation results & complexity/performance analyses Submission 5 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Key Features of DS-UWB • Based on true Ultra-wideband principles – Large fractional bandwidth signals in two different bands – Benefits from low fading due to wide bandwidth (>1. 5 GHz) • An excellent combination of high performance and low complexity for WPAN applications – Support scalability to ultra-low power operation for short range (1 -2 m) very high rates using low-complexity or no coding – Performance exceeds the Selection Criteria in all aspect – Better performance and lower power than any other proposal considered by TG 3 a Submission 6 Welborn, Freescale

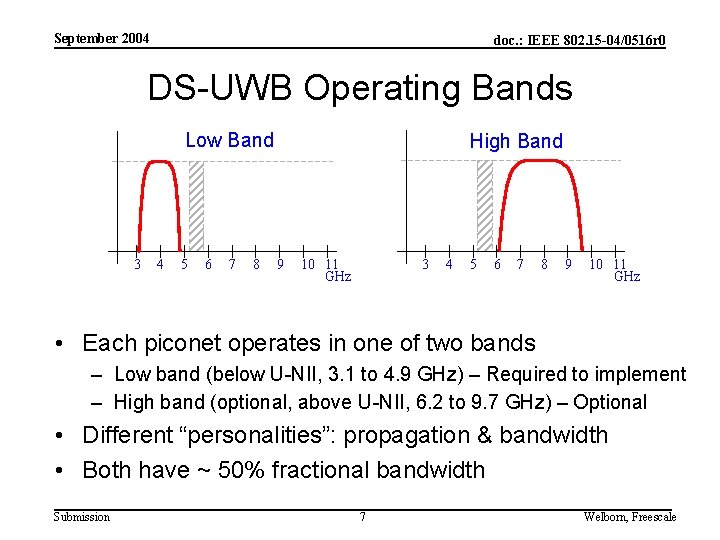

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 DS-UWB Operating Bands Low Band 3 4 5 6 7 8 High Band 9 10 11 GHz 3 4 5 6 7 8 9 10 11 GHz • Each piconet operates in one of two bands – Low band (below U-NII, 3. 1 to 4. 9 GHz) – Required to implement – High band (optional, above U-NII, 6. 2 to 9. 7 GHz) – Optional • Different “personalities”: propagation & bandwidth • Both have ~ 50% fractional bandwidth Submission 7 Welborn, Freescale

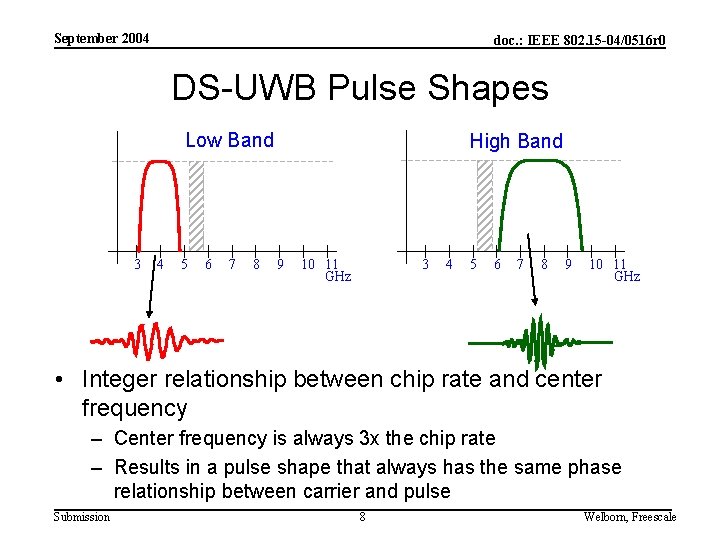

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 DS-UWB Pulse Shapes Low Band 3 4 5 6 7 8 High Band 9 10 11 GHz 3 4 5 6 7 8 9 10 11 GHz • Integer relationship between chip rate and center frequency – Center frequency is always 3 x the chip rate – Results in a pulse shape that always has the same phase relationship between carrier and pulse Submission 8 Welborn, Freescale

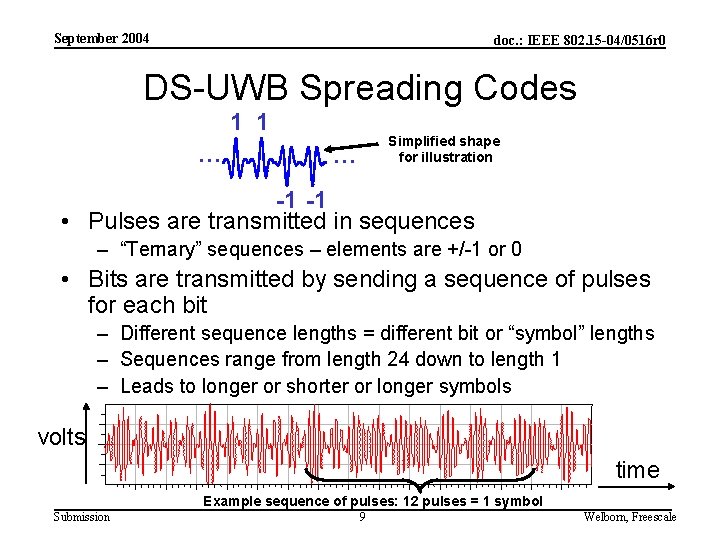

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 DS-UWB Spreading Codes 1 1 … Simplified shape for illustration … -1 -1 • Pulses are transmitted in sequences – “Ternary” sequences – elements are +/-1 or 0 • Bits are transmitted by sending a sequence of pulses for each bit – Different sequence lengths = different bit or “symbol” lengths – Sequences range from length 24 down to length 1 – Leads to longer or shorter or longer symbols volts time Example sequence of pulses: 12 pulses = 1 symbol Submission 9 Welborn, Freescale

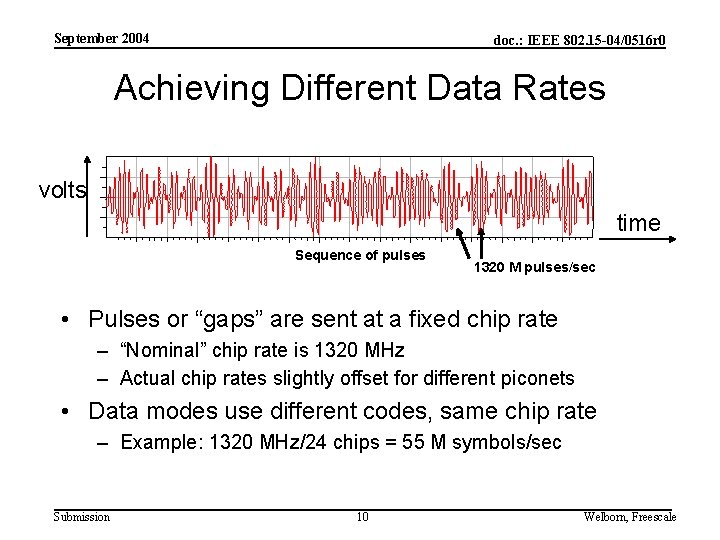

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Achieving Different Data Rates volts time Sequence of pulses 1320 M pulses/sec • Pulses or “gaps” are sent at a fixed chip rate – “Nominal” chip rate is 1320 MHz – Actual chip rates slightly offset for different piconets • Data modes use different codes, same chip rate – Example: 1320 MHz/24 chips = 55 M symbols/sec Submission 10 Welborn, Freescale

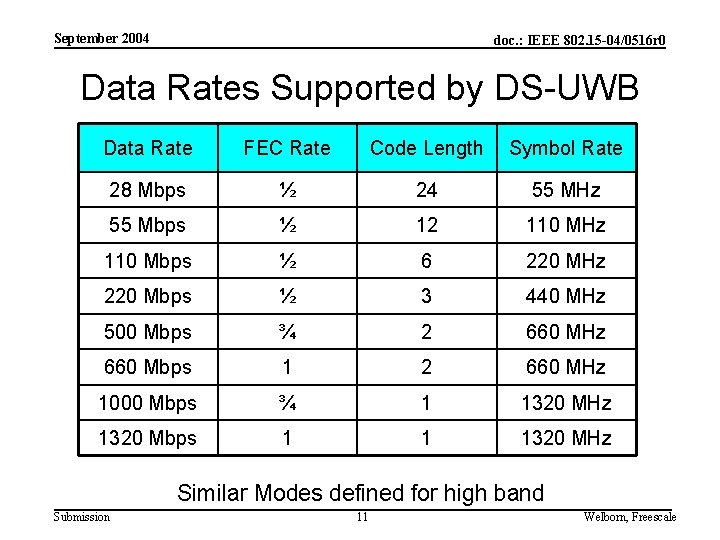

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Data Rates Supported by DS-UWB Data Rate FEC Rate Code Length Symbol Rate 28 Mbps ½ 24 55 MHz 55 Mbps ½ 12 110 MHz 110 Mbps ½ 6 220 MHz 220 Mbps ½ 3 440 MHz 500 Mbps ¾ 2 660 MHz 660 Mbps 1 2 660 MHz 1000 Mbps ¾ 1 1320 MHz 1320 Mbps 1 1 1320 MHz Similar Modes defined for high band Submission 11 Welborn, Freescale

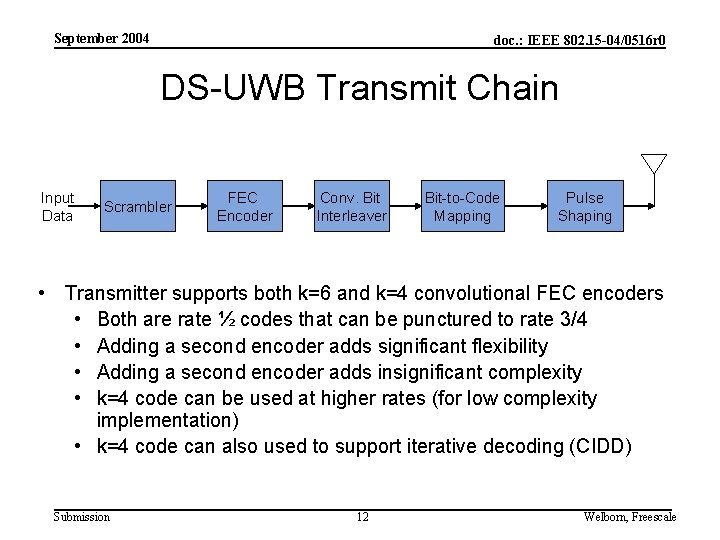

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 DS-UWB Transmit Chain Input Data Scrambler FEC Encoder Conv. Bit Interleaver Bit-to-Code Mapping Pulse Shaping • Transmitter supports both k=6 and k=4 convolutional FEC encoders • Both are rate ½ codes that can be punctured to rate 3/4 • Adding a second encoder adds significant flexibility • Adding a second encoder adds insignificant complexity • k=4 code can be used at higher rates (for low complexity implementation) • k=4 code can also used to support iterative decoding (CIDD) Submission 12 Welborn, Freescale

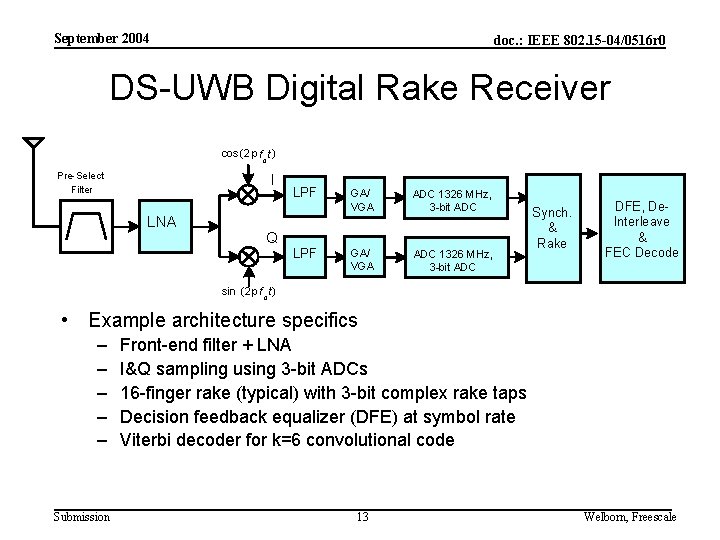

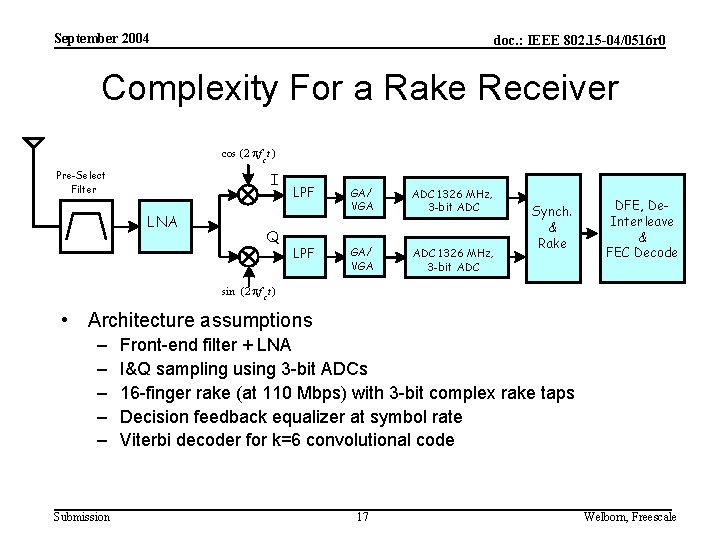

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 DS-UWB Digital Rake Receiver cos (2 pf t ) c Pre-Select Filter I LNA LPF GA/ VGA ADC 1326 MHz, 3 -bit ADC Q LPF Synch. & Rake DFE, De. Interleave & FEC Decode sin (2 pf t ) c • Example architecture specifics – – – Submission Front-end filter + LNA I&Q sampling using 3 -bit ADCs 16 -finger rake (typical) with 3 -bit complex rake taps Decision feedback equalizer (DFE) at symbol rate Viterbi decoder for k=6 convolutional code 13 Welborn, Freescale

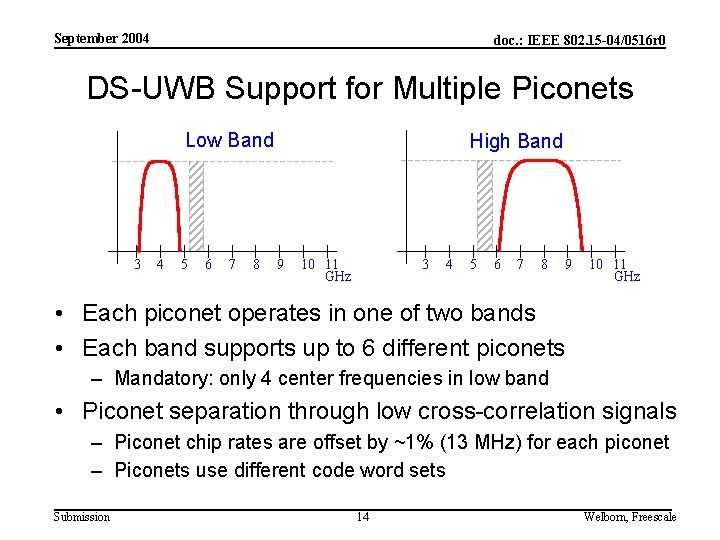

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 DS-UWB Support for Multiple Piconets Low Band 3 4 5 6 7 8 High Band 9 10 11 GHz 3 4 5 6 7 8 9 10 11 GHz • Each piconet operates in one of two bands • Each band supports up to 6 different piconets – Mandatory: only 4 center frequencies in low band • Piconet separation through low cross-correlation signals – Piconet chip rates are offset by ~1% (13 MHz) for each piconet – Piconets use different code word sets Submission 14 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Topic: Complexity Estimates • Typical comments – Merge proposal #2 would need to show performance criteria with a direct correlation to transceiver architecture and complexity for me to be comfortable with its ability to operate in more sever channels such as CM 2, CM 3, and CM 4. – The proposal #2 team has provided simulation results on the implementation of a sophisticated rake structure to solve early product multipath issues. The claim is that it can be implemented in a remarkably small silicon area. – I would vote YES if. . . the DS-UWB scheme had a less complex method for their digital rake receiver, so that a complex analog rake would not be needed. – Unclear correlation between various options for improvement and estimates of power consumption/complexity. – Digital gate count is not accurate and needs to be updated to more accurately reflect the complexity required to implement all data rates and must account for a chip-level equalizer. Submission 15 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 UWB System Complexity & Power Consumption • Two primary factors drive UWB complexity & power consumption – Processing needed to compensate for multipath channel – Modulation requirements (I. e. low-order versus high-order) • DS-UWB designed to use simple BPSK modulation for all rates – Receiver functions (Rake & EQ) operate at the symbol rate • DS-UWB can use lower complexity FEC due to relatively low multipath fading Submission 16 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Complexity For a Rake Receiver cos (2 pf t ) c Pre-Select Filter I LNA Q LPF GA/ VGA ADC 1326 MHz, 3 -bit ADC Synch. & Rake DFE, De. Interleave & FEC Decode sin (2 pf t ) c • Architecture assumptions – – – Submission Front-end filter + LNA I&Q sampling using 3 -bit ADCs 16 -finger rake (at 110 Mbps) with 3 -bit complex rake taps Decision feedback equalizer at symbol rate Viterbi decoder for k=6 convolutional code 17 Welborn, Freescale

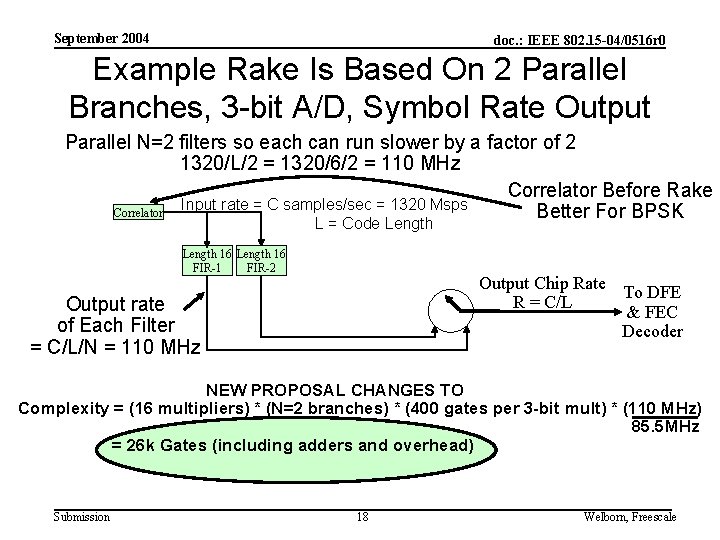

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Example Rake Is Based On 2 Parallel Branches, 3 -bit A/D, Symbol Rate Output Parallel N=2 filters so each can run slower by a factor of 2 1320/L/2 = 1320/6/2 = 110 MHz Correlator Before Rake Input rate = C samples/sec = 1320 Msps Correlator Better For BPSK L = Code Length 16 FIR-1 FIR-2 Output Chip Rate To DFE R = C/L & FEC Decoder Output rate of Each Filter = C/L/N = 110 MHz NEW PROPOSAL CHANGES TO Complexity = (16 multipliers) * (N=2 branches) * (400 gates per 3 -bit mult) * (110 MHz) 85. 5 MHz = 26 k Gates (including adders and overhead) Submission 18 Welborn, Freescale

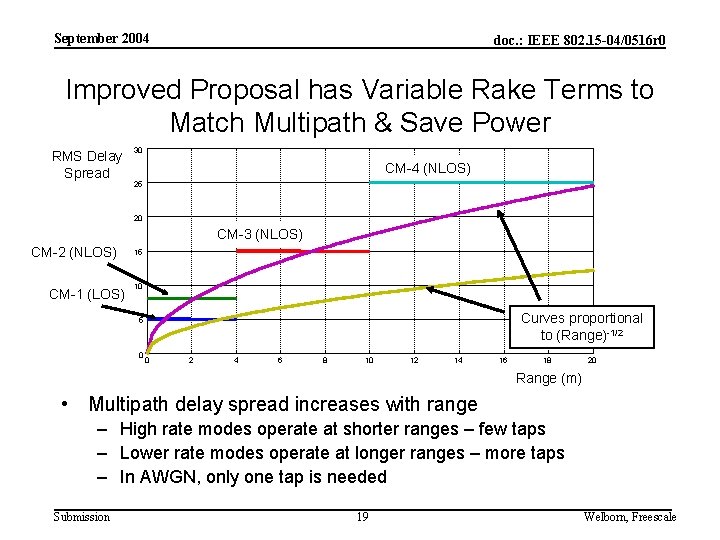

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Improved Proposal has Variable Rake Terms to Match Multipath & Save Power RMS Delay Spread 30 CM-4 (NLOS) 25 20 CM-3 (NLOS) CM-2 (NLOS) CM-1 (LOS) 15 10 Curves proportional to (Range)-1/2 5 0 0 2 4 6 8 10 12 14 16 18 20 Range (m) • Multipath delay spread increases with range – High rate modes operate at shorter ranges – few taps – Lower rate modes operate at longer ranges – more taps – In AWGN, only one tap is needed Submission 19 Welborn, Freescale

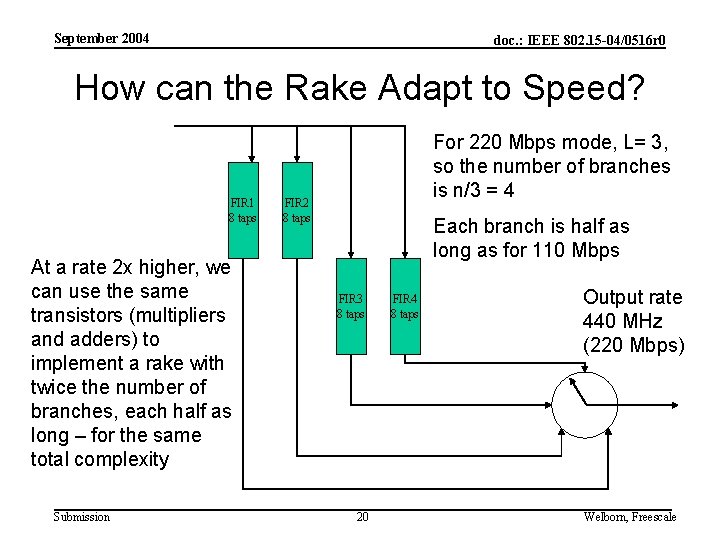

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 How can the Rake Adapt to Speed? FIR 1 8 taps At a rate 2 x higher, we can use the same transistors (multipliers and adders) to implement a rake with twice the number of branches, each half as long – for the same total complexity Submission For 220 Mbps mode, L= 3, so the number of branches is n/3 = 4 FIR 2 8 taps Each branch is half as long as for 110 Mbps FIR 3 8 taps 20 FIR 4 8 taps Output rate 440 MHz (220 Mbps) Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Low Rake Complexity for 16 Fingers • Example of reconfigurable rake complexity – – • 16 taps at 110 Mbps (220 MHz symbol rate - before FEC) 8 taps at 220 Mbps (6 -10 meters) 5 taps at 500 Mbps (3 -4 meters) 2 taps at 1000 Mbps (1 -2 meters) Example gate counts for a 16 -finger rake implementation @ 110 Mbps – – – – Submission Assume 400 gates/3 -bit complex multiply Needs 16 3 -bit complex multiplies at 220 MHz output rate Needs 2 parallel branches for 110 MHz clock (n=2) Total is 32 multipliers for 12, 800 gates Also add 64 adders at average 34 gates/adder 2200 gates Add 5000 gates (33%) for miscellaneous overhead Total gate count is 20, 000 at 110 MHz Equivalent to 26 K gates at 85. 5 MHz (per 03/449 r 0 methodology) 21 Welborn, Freescale

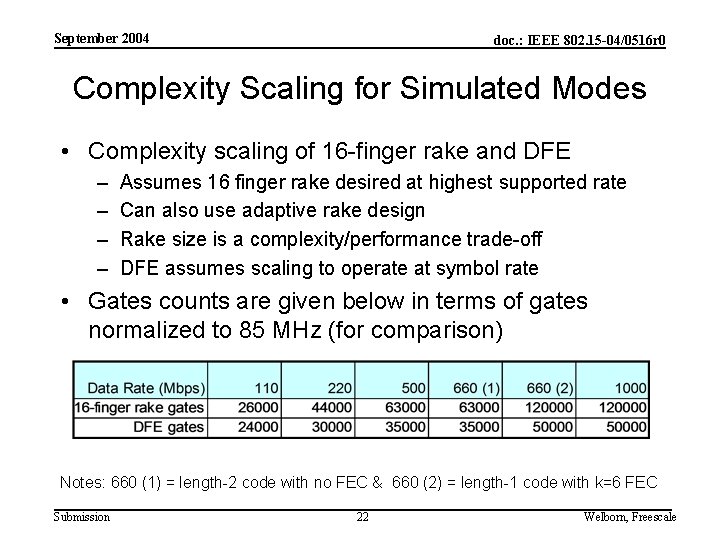

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Complexity Scaling for Simulated Modes • Complexity scaling of 16 -finger rake and DFE – – Assumes 16 finger rake desired at highest supported rate Can also use adaptive rake design Rake size is a complexity/performance trade-off DFE assumes scaling to operate at symbol rate • Gates counts are given below in terms of gates normalized to 85 MHz (for comparison) Notes: 660 (1) = length-2 code with no FEC & 660 (2) = length-1 code with k=6 FEC Submission 22 Welborn, Freescale

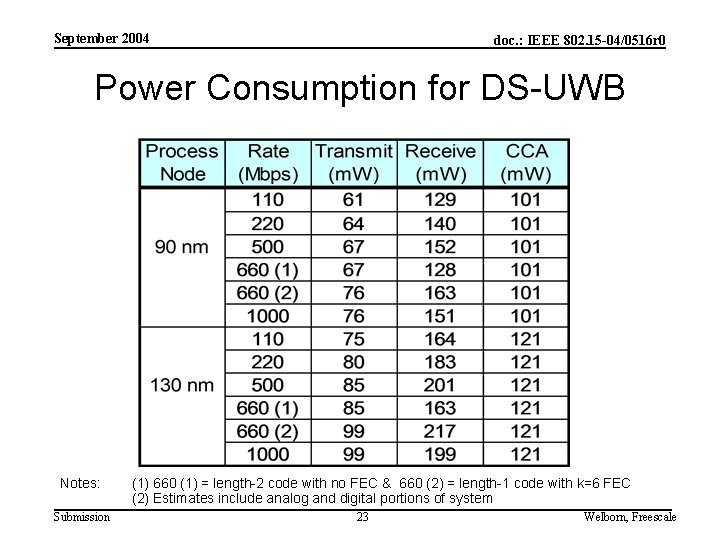

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Power Consumption for DS-UWB Notes: Submission (1) 660 (1) = length-2 code with no FEC & 660 (2) = length-1 code with k=6 FEC (2) Estimates include analog and digital portions of system 23 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Performance and Complexity • Response – A review of the history of the Merger#2 proposal • The DS-UWB proposal is stable and well-defined – A clear summary presentation of the DS-UWB proposal – Consistent & complete performance and complexity results • Superior performance with lower complexity – the right solution Submission 24 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 • Back-up Slides Submission 25 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 History of Merger #1 Proposal • Last merger was in July 2003 (with ST Micro) • Modifications to Merger#1 – – – – Submission Changes acquisition preambles Added Mode II Changed to “Zero-padded prefix” Removed Mode II Added “Band Group” FDM modes Changed Guard Tone mapping Changed Data rate modes (use rate 1/3 FEC) 26 Welborn, Freescale

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 Miscellaneous Comments • Acquisition curves at Eb/No = 4 d. B shows that approx. 15% of the packets are missed even when the false alarm probability is set a value higher than 1%. This is a serious deficiency in the system and will have an impact at lower rates • Response: The correct figures are found from the plot on page 47 of 04/099 r 1. This plot shows less than ½% probability of missed detection for a 1% false alarm rate or less than 1. 5% probability of missed detection for a 0. 1% rate of false alarm (based on 9 parallel correlators at 4 d. B Eb/No). This acquisition performance & operating point are a function of the desired level of complexity (e. g. number of correlators) and the values selected for the acquisition parameters. Submission 27 Welborn, Freescale

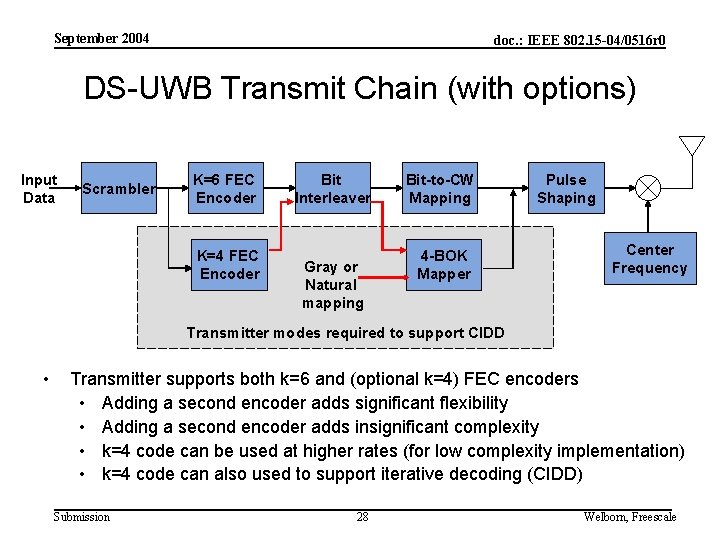

September 2004 doc. : IEEE 802. 15 -04/0516 r 0 DS-UWB Transmit Chain (with options) Input Data Scrambler K=6 FEC Encoder K=4 FEC Encoder Bit Interleaver Gray or Natural mapping Bit-to-CW Mapping 4 -BOK Mapper Pulse Shaping Center Frequency Transmitter modes required to support CIDD • Transmitter supports both k=6 and (optional k=4) FEC encoders • Adding a second encoder adds significant flexibility • Adding a second encoder adds insignificant complexity • k=4 code can be used at higher rates (for low complexity implementation) • k=4 code can also used to support iterative decoding (CIDD) Submission 28 Welborn, Freescale

- Slides: 28