Senior Capstone Project GPS Signal Simulator May 2

- Slides: 25

Senior Capstone Project GPS Signal Simulator May 2, 2006 Benjamin Herreid Anthony Hoehne Advisor: Dr. In Soo Ahn Sponsored By:

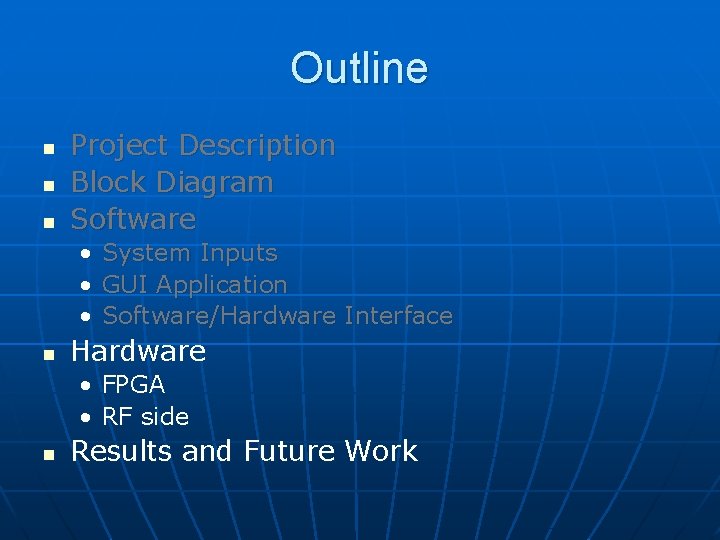

Outline n n n Project Description Block Diagram Software • System Inputs • GUI Application • Software/Hardware Interface n Hardware • FPGA • RF side n Results and Future Work

Project Summary n Global Positioning System (GPS) • Satellite based navigation system • Guaranteed worldwide coverage n n n Solve problem backwards Generate the simulated GPS signals for up to 4 visible satellites (channels) Use generated signals to drive a commercial receiver

Project Application n Model a scenario that uses GPS signals Useful in developing a GPS receiver Much cheaper than physical testing • Airplanes • Spacecraft n Tests that are impossible in real life • Repeatability • High-dynamics

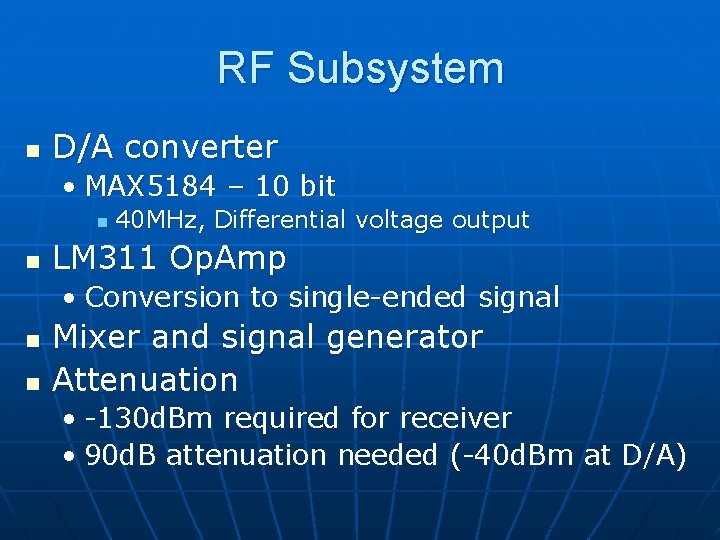

Equipment n n PC – Windows XP, Parallel Port FPGA – Altera Cyclone • Altera UP 3 Development Board n D/A Converter, Op. Amp • MAX 5184, 10 bits • LM 311 n Mixer and Oscillator • RF Signal Generator n Commercial Receiver • Ashtech G 8

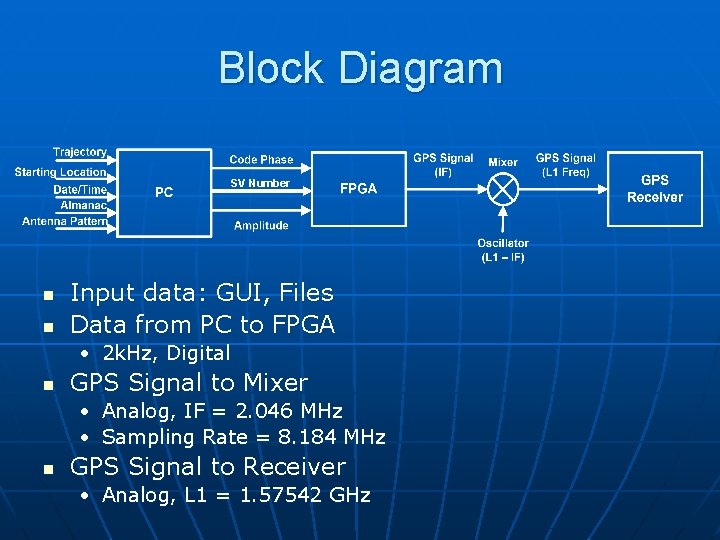

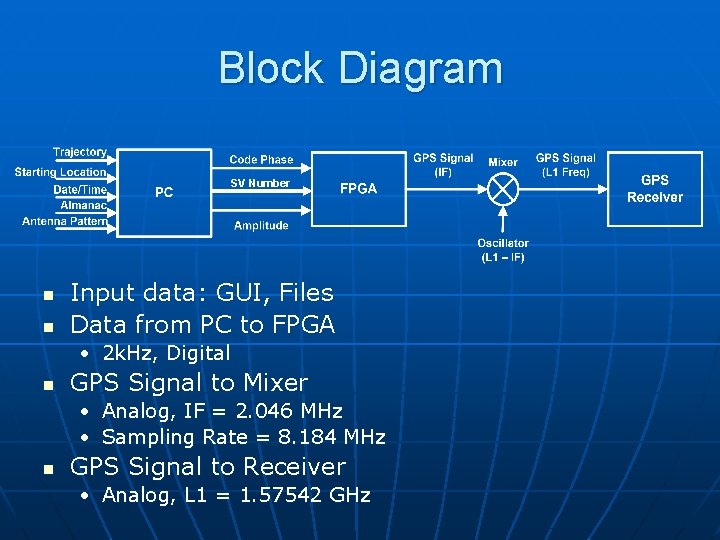

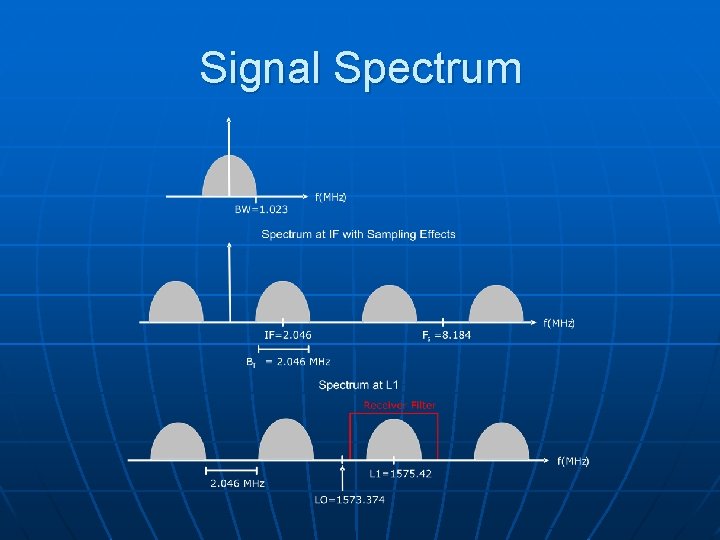

Block Diagram SV Number n n Input data: GUI, Files Data from PC to FPGA • 2 k. Hz, Digital n GPS Signal to Mixer • Analog, IF = 2. 046 MHz • Sampling Rate = 8. 184 MHz n GPS Signal to Receiver • Analog, L 1 = 1. 57542 GHz

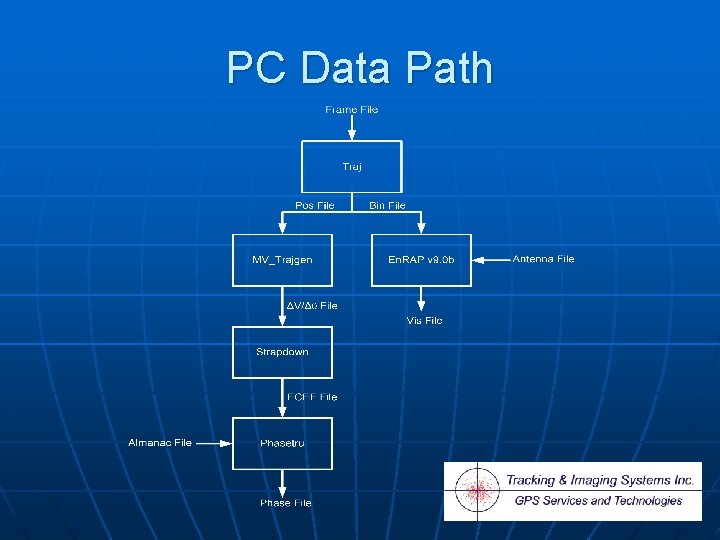

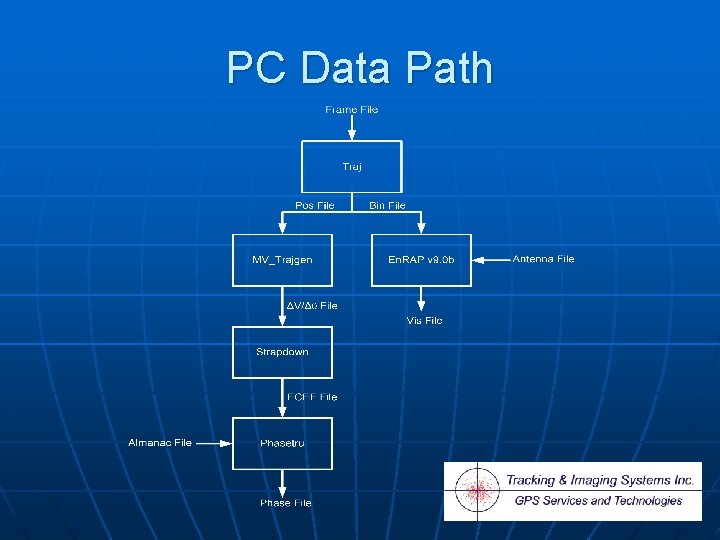

PC Data Path

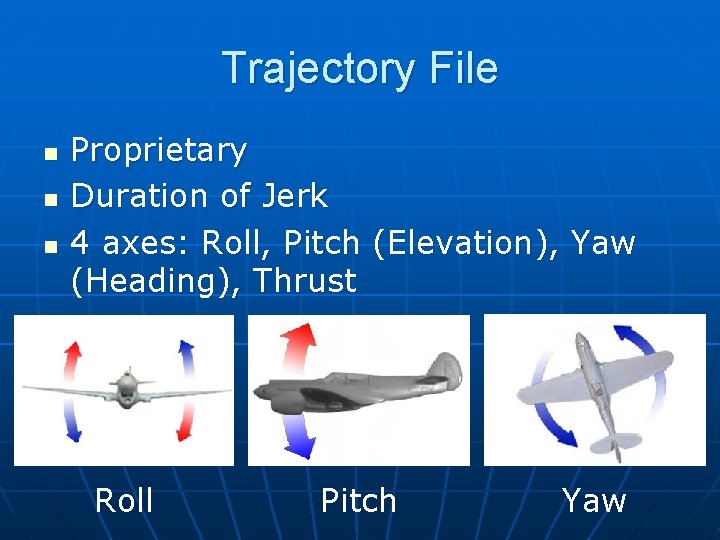

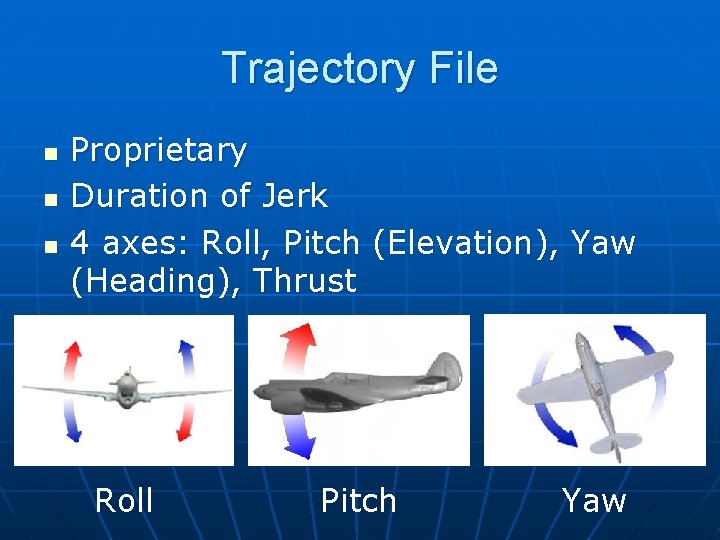

Trajectory File n n n Proprietary Duration of Jerk 4 axes: Roll, Pitch (Elevation), Yaw (Heading), Thrust Roll Pitch Yaw

Initial Conditions n n 3 rd Derivative Requires initial conditions for lower order parameters • Acceleration: 0 • Velocity: 0 • Attitude: 0 (level, due North) • Position: Specified by User

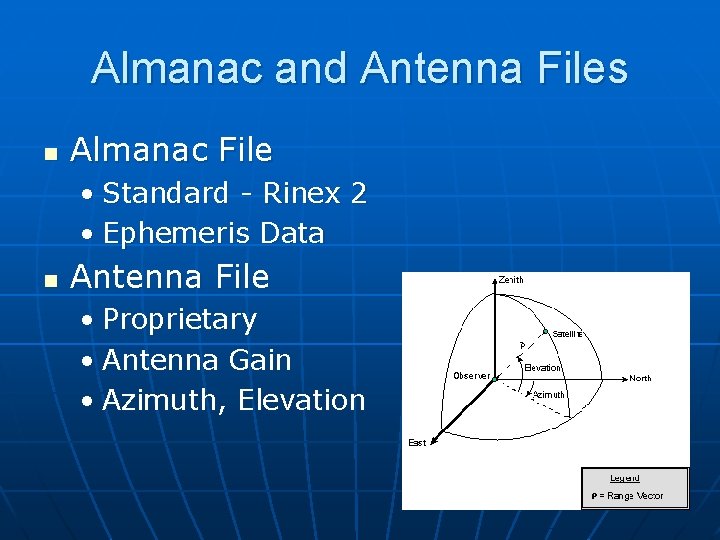

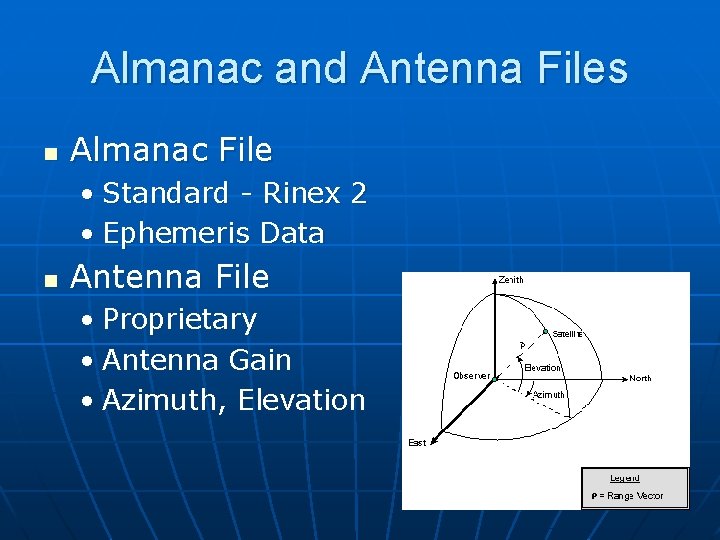

Almanac and Antenna Files n Almanac File • Standard - Rinex 2 • Ephemeris Data n Antenna File • Proprietary • Antenna Gain • Azimuth, Elevation

Phase and Visibility Files n Phase File • Phase (distance) to each satellite in radians • At fixed frequency, wavelength is constant so phase and distance are interchangeable (fλ=c) n Visibility File • Azimuth and Elevation of each satellite • Signal Power from each satellite

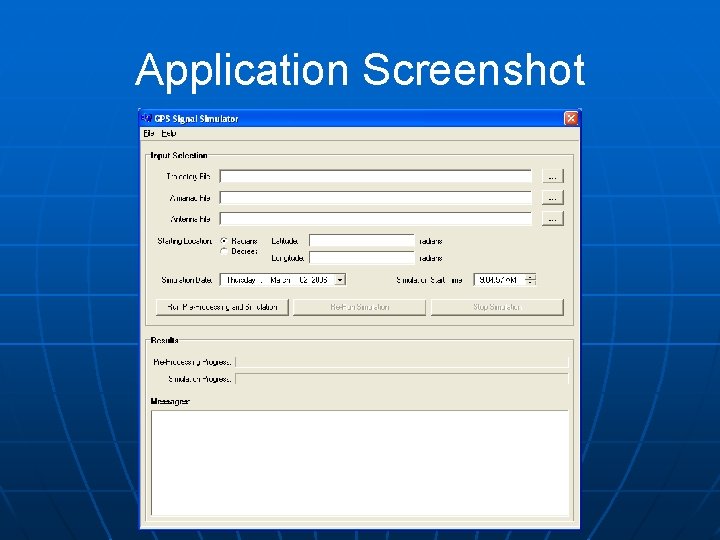

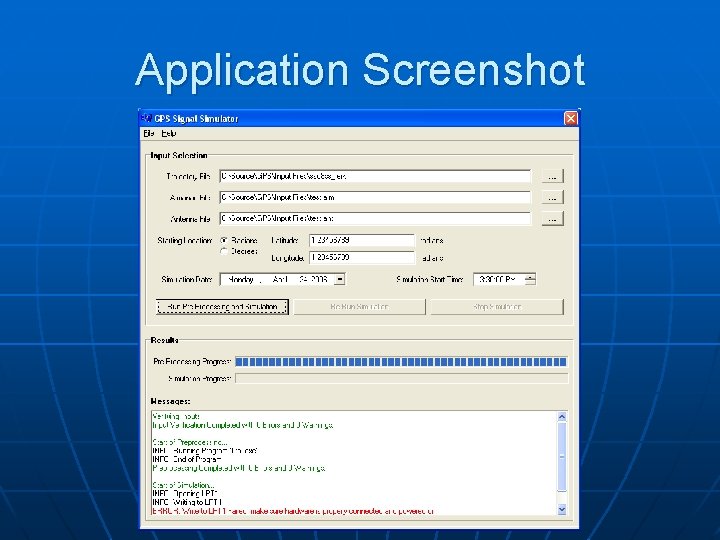

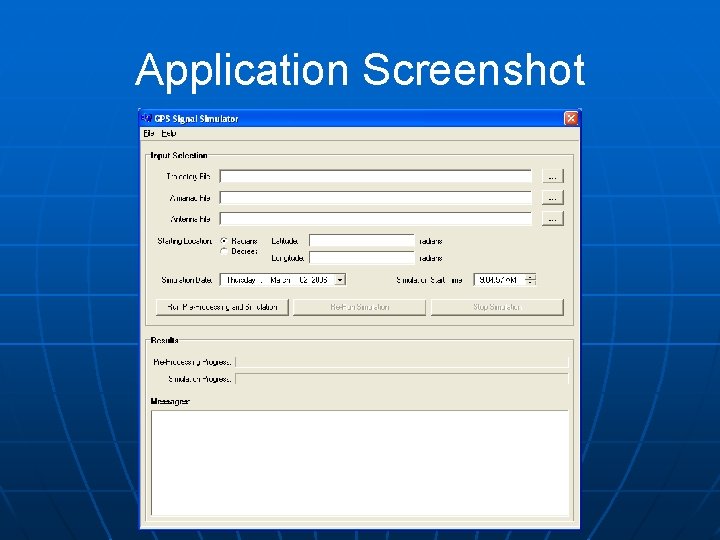

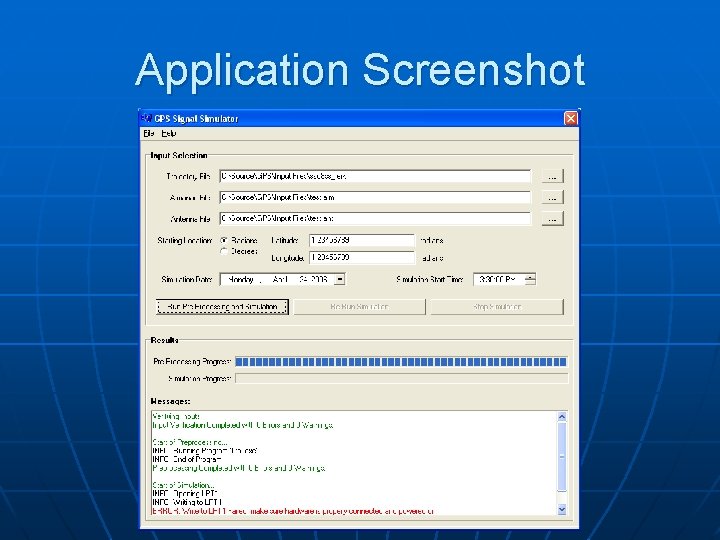

Application Screenshot

Application Screenshot

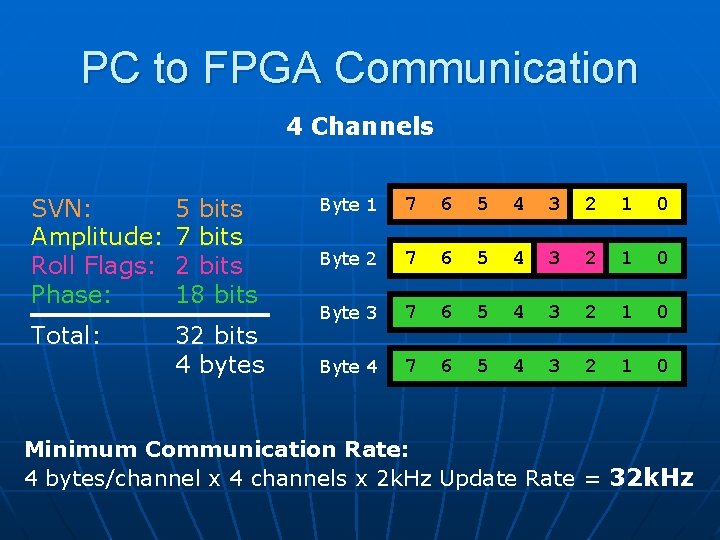

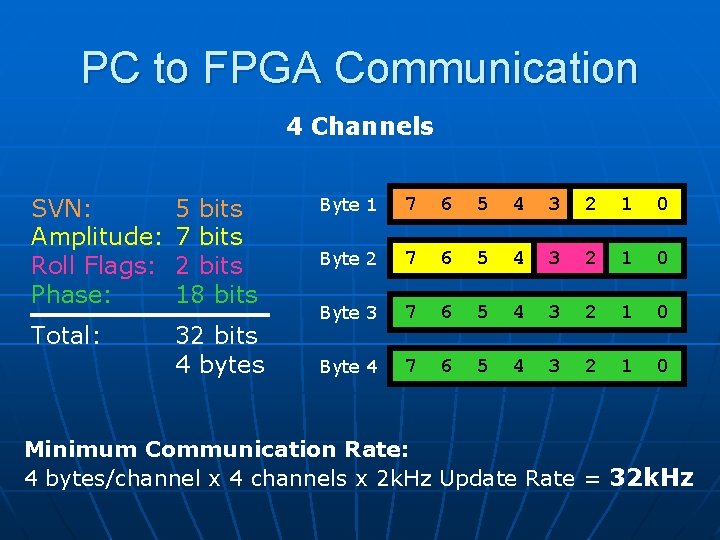

PC to FPGA Communication 4 Channels SVN: Amplitude: Roll Flags: Phase: 5 bits 7 bits 2 bits 18 bits Total: 32 bits 4 bytes Byte 1 7 6 5 4 3 2 1 0 Byte 2 7 6 5 4 3 2 1 0 Byte 3 7 6 5 4 3 2 1 0 Byte 4 7 6 5 4 3 2 1 0 Minimum Communication Rate: 4 bytes/channel x 4 channels x 2 k. Hz Update Rate = 32 k. Hz

Outline n n n Project Description Block Diagram Software • System Inputs • GUI Application • Software/Hardware Interface n Hardware • FPGA • RF side n Results and Future Work

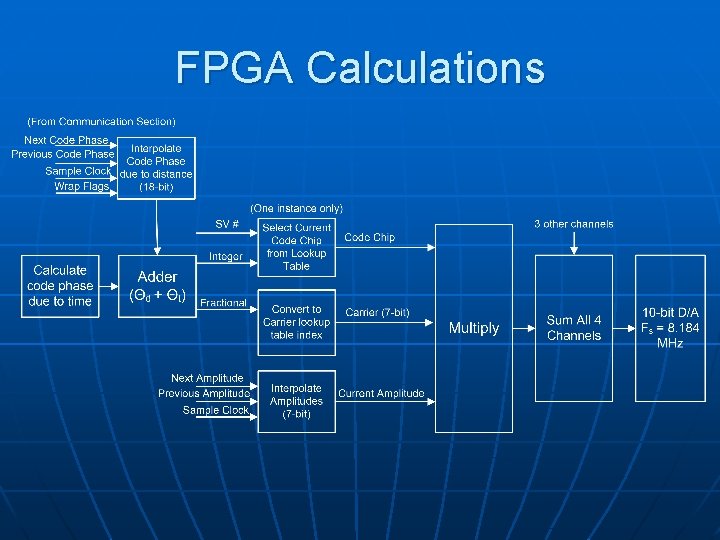

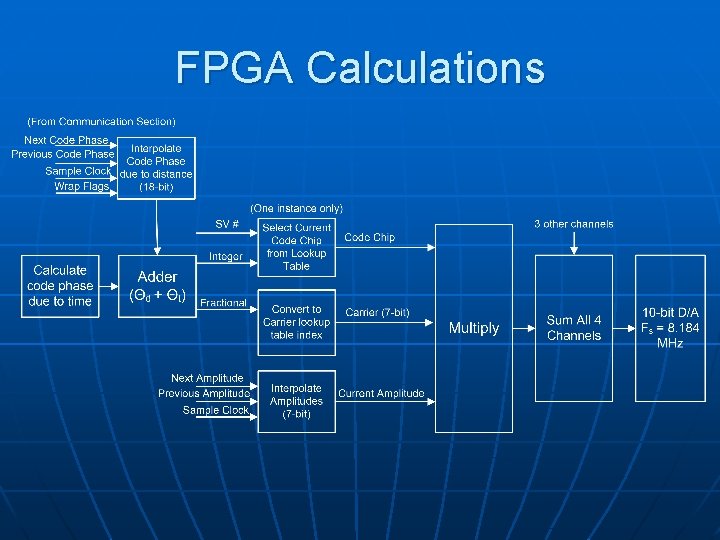

FPGA Calculations

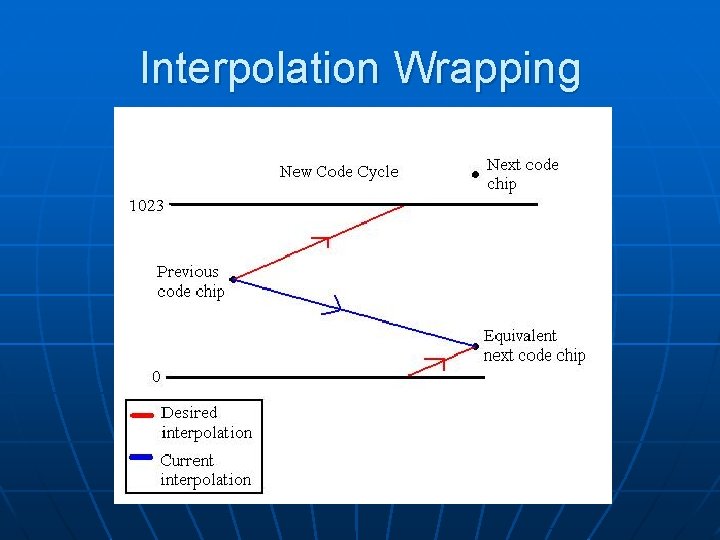

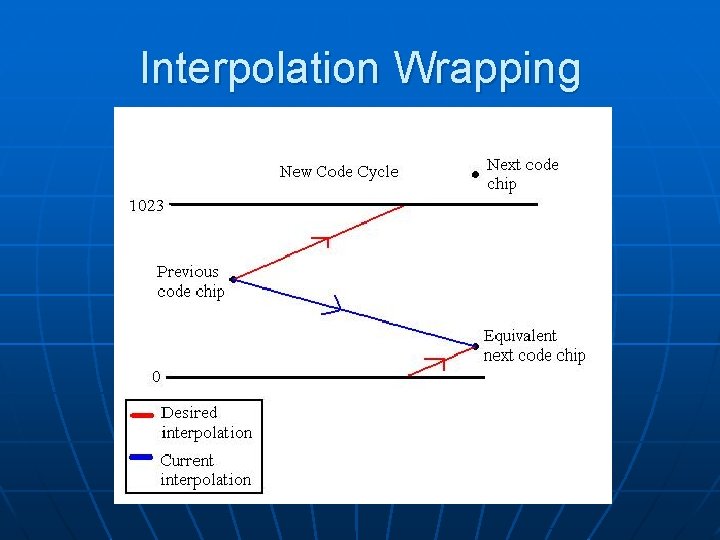

Interpolation Wrapping

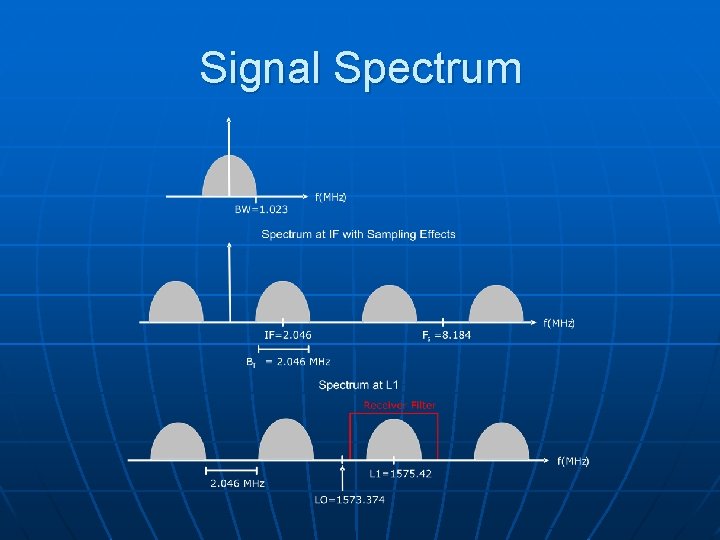

Signal Spectrum

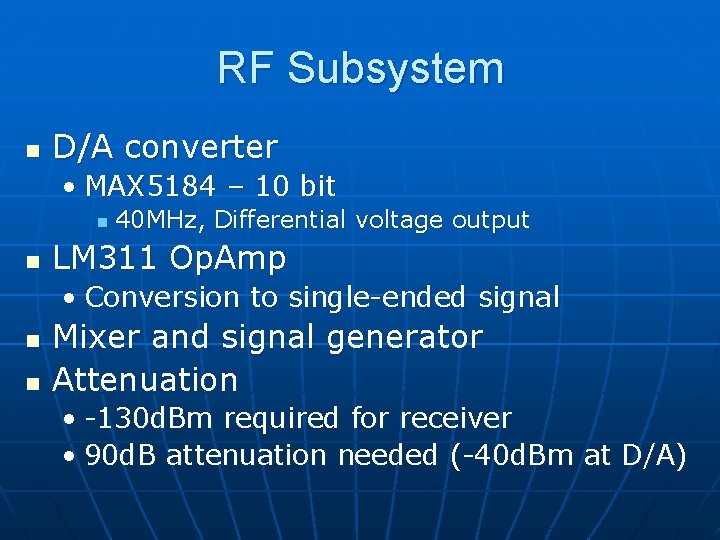

RF Subsystem n D/A converter • MAX 5184 – 10 bit n n 40 MHz, Differential voltage output LM 311 Op. Amp • Conversion to single-ended signal n n Mixer and signal generator Attenuation • -130 d. Bm required for receiver • 90 d. B attenuation needed (-40 d. Bm at D/A)

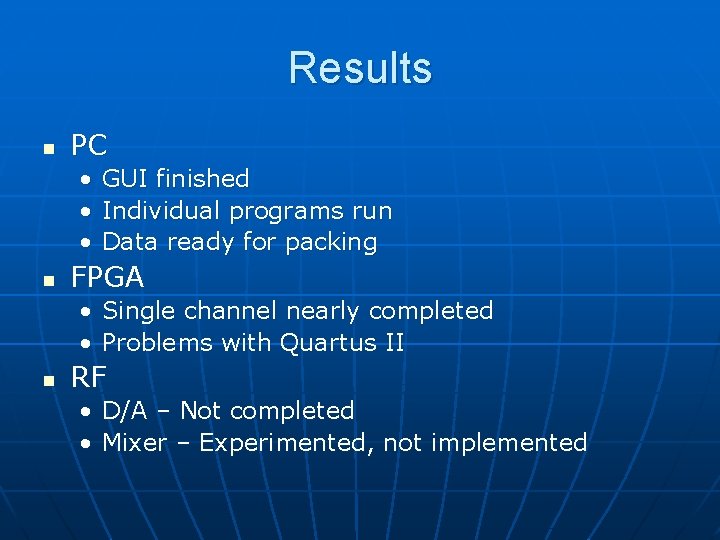

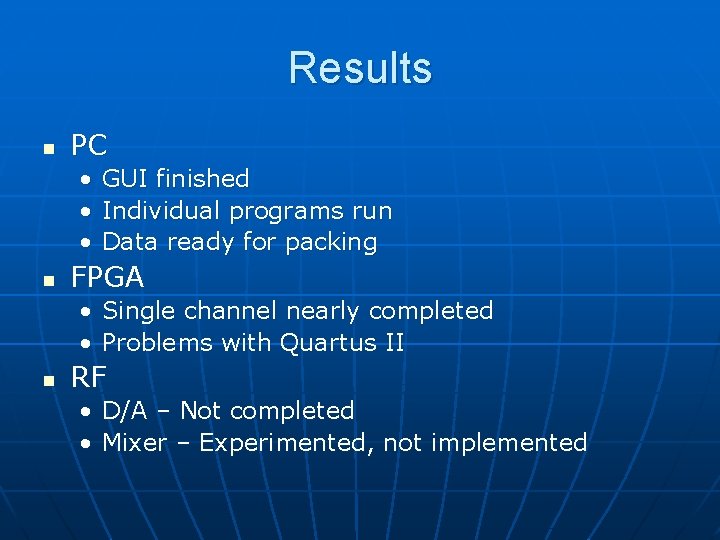

Results n PC • • • n GUI finished Individual programs run Data ready for packing FPGA • Single channel nearly completed • Problems with Quartus II n RF • • D/A – Not completed Mixer – Experimented, not implemented

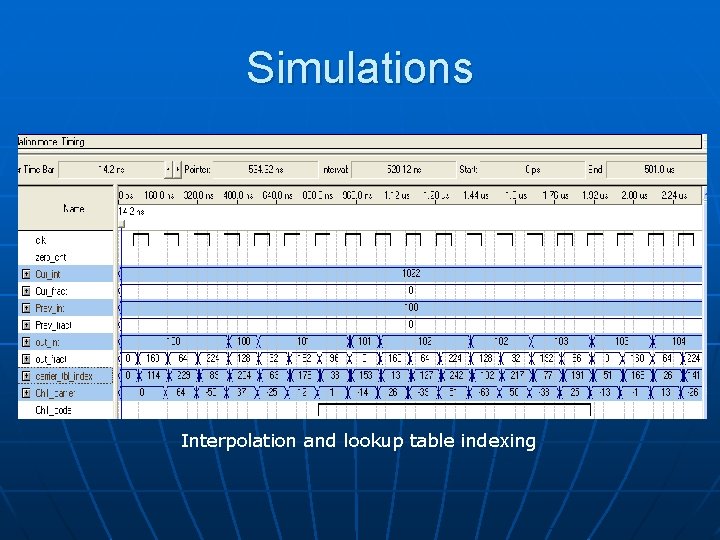

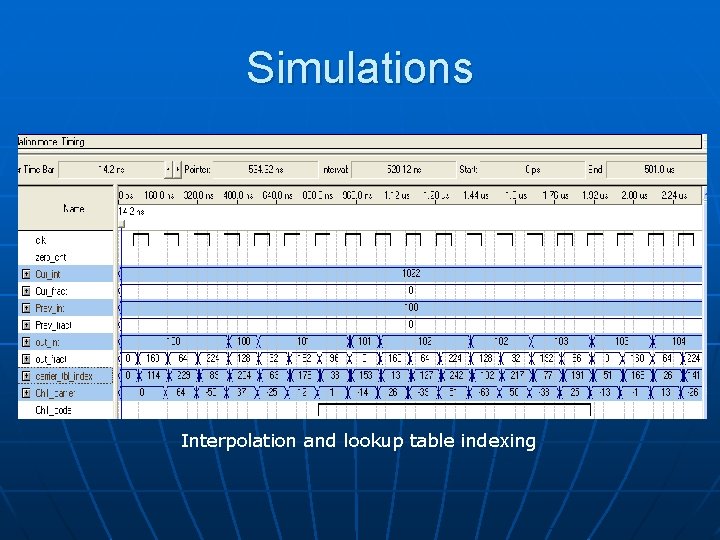

Simulations Interpolation and lookup table indexing

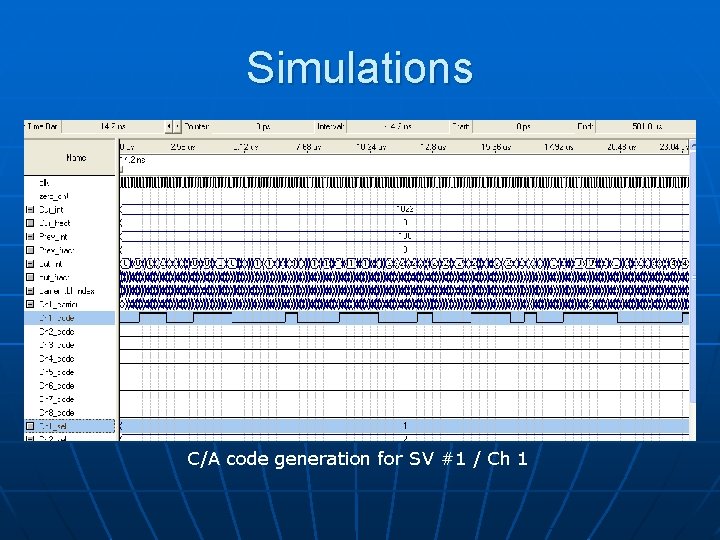

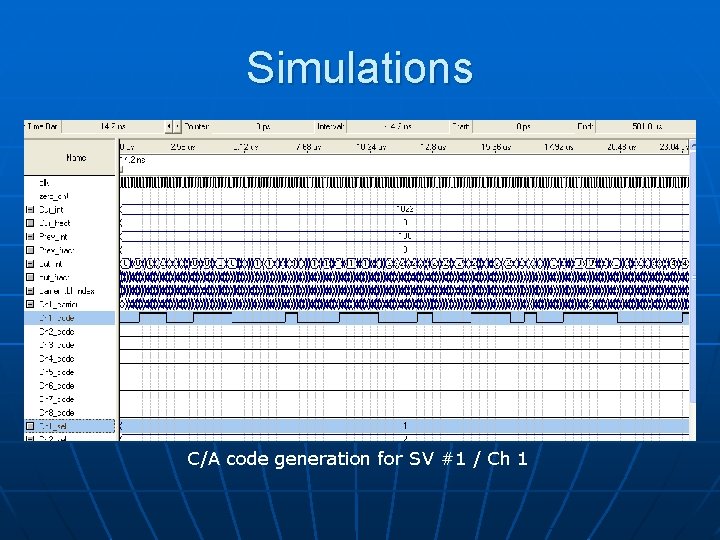

Simulations C/A code generation for SV #1 / Ch 1

Future Work n n n Establish Communication Add navigation data Additional features • Ionosphere and troposphere effects • Multipath • Additional channels (multiple FPGA’s) • Instrument panel in GUI

Questions?

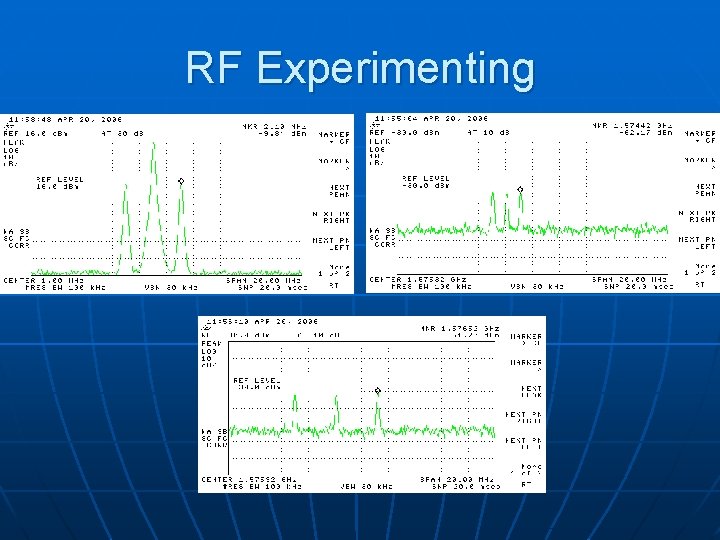

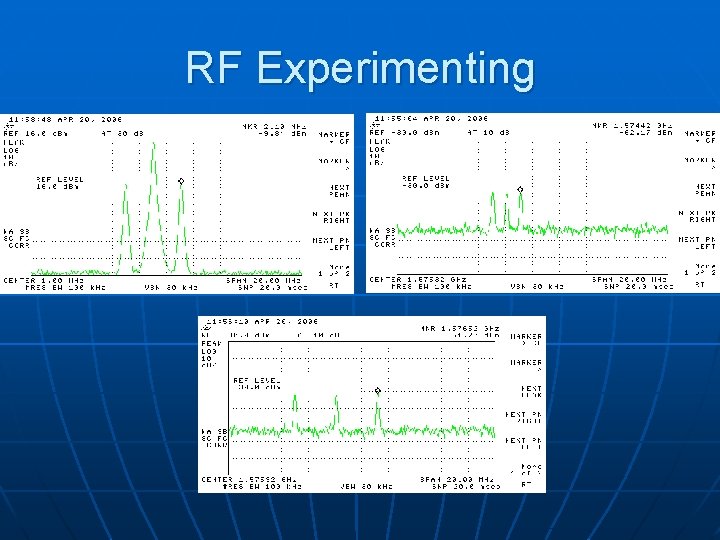

RF Experimenting