SEMICONDUCTOR MEMORIES Digital Integrated Circuits Memory Prentice Hall

![Yield curves at different stages of process maturity (from [Veendrick 92]) Digital Integrated Circuits Yield curves at different stages of process maturity (from [Veendrick 92]) Digital Integrated Circuits](https://slidetodoc.com/presentation_image/368cca29aaf098bee624d5a859edb23c/image-59.jpg)

- Slides: 70

SEMICONDUCTOR MEMORIES Digital Integrated Circuits Memory © Prentice Hall 1995

Chapter Overview Digital Integrated Circuits Memory © Prentice Hall 1995

Semiconductor Memory Classification Digital Integrated Circuits Memory © Prentice Hall 1995

Memory Architecture: Decoders Digital Integrated Circuits Memory © Prentice Hall 1995

Array-Structured Memory Architecture Digital Integrated Circuits Memory © Prentice Hall 1995

Hierarchical Memory Architecture Digital Integrated Circuits Memory © Prentice Hall 1995

Memory Timing: Definitions Digital Integrated Circuits Memory © Prentice Hall 1995

Memory Timing: Approaches Digital Integrated Circuits Memory © Prentice Hall 1995

MOS NOR ROM Digital Integrated Circuits Memory © Prentice Hall 1995

MOS NOR ROM Layout Digital Integrated Circuits Memory © Prentice Hall 1995

MOS NOR ROM Layout Digital Integrated Circuits Memory © Prentice Hall 1995

MOS NAND ROM Digital Integrated Circuits Memory © Prentice Hall 1995

MOS NAND ROM Layout Digital Integrated Circuits Memory © Prentice Hall 1995

Equivalent Transient Model for MOS NOR ROM Digital Integrated Circuits Memory © Prentice Hall 1995

Equivalent Transient Model for MOS NAND ROM Digital Integrated Circuits Memory © Prentice Hall 1995

Propagation Delay of NOR ROM Digital Integrated Circuits Memory © Prentice Hall 1995

Decreasing Word Line Delay Digital Integrated Circuits Memory © Prentice Hall 1995

Precharged MOS NOR ROM Digital Integrated Circuits Memory © Prentice Hall 1995

Floating-gate transistor (FAMOS) Digital Integrated Circuits Memory © Prentice Hall 1995

Floating-Gate Transistor Programming Digital Integrated Circuits Memory © Prentice Hall 1995

FLOTOX EEPROM Digital Integrated Circuits Memory © Prentice Hall 1995

Flash EEPROM Digital Integrated Circuits Memory © Prentice Hall 1995

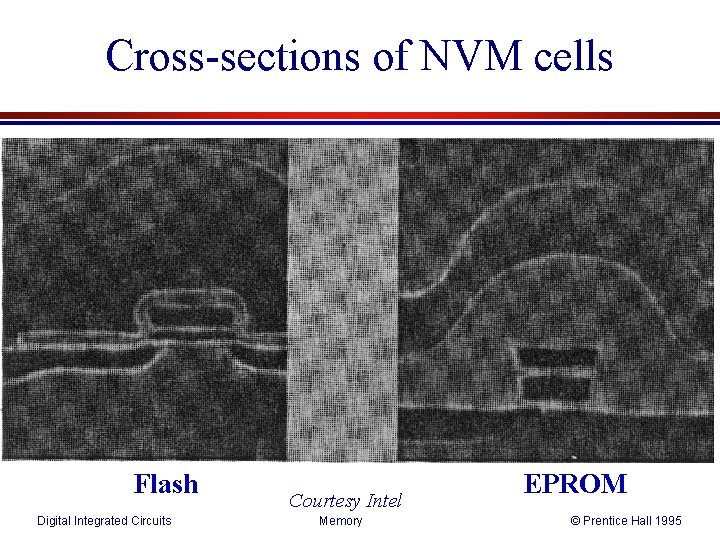

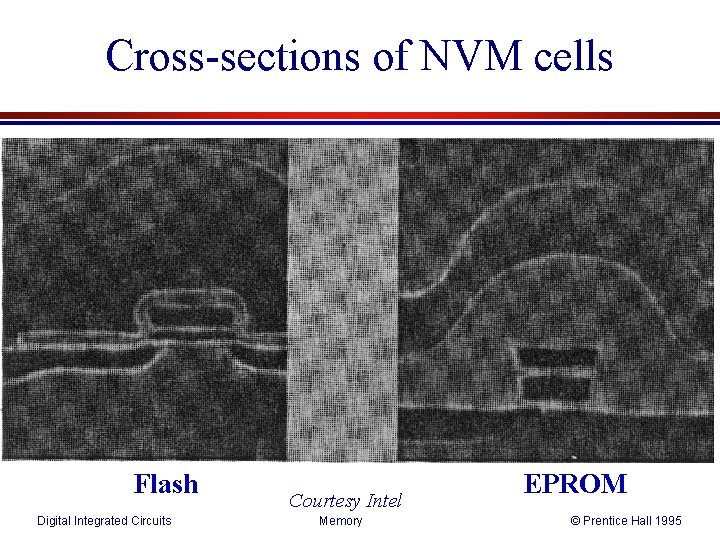

Cross-sections of NVM cells Flash Digital Integrated Circuits Courtesy Intel Memory EPROM © Prentice Hall 1995

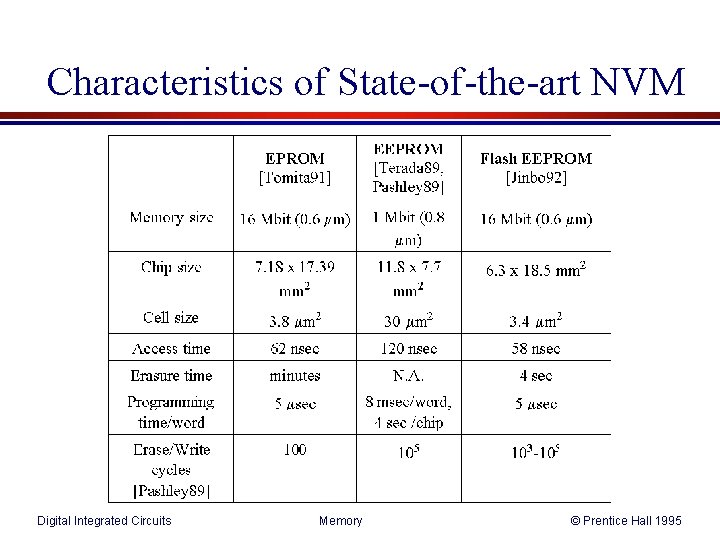

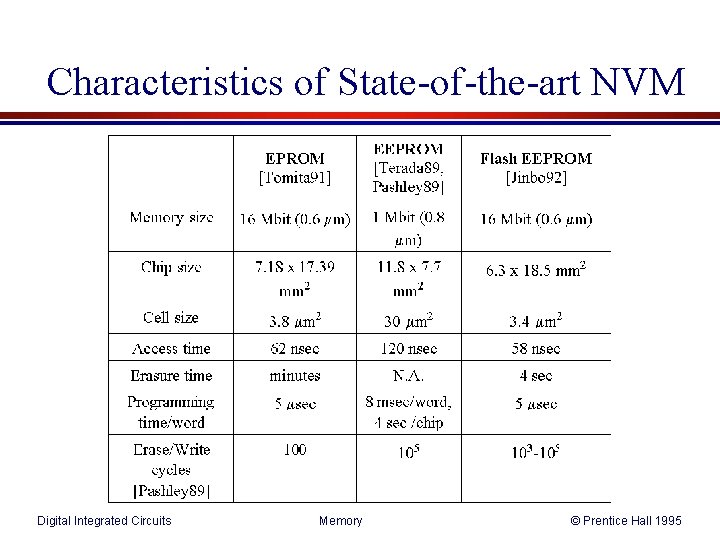

Characteristics of State-of-the-art NVM Digital Integrated Circuits Memory © Prentice Hall 1995

Read-Write Memories (RAM) Digital Integrated Circuits Memory © Prentice Hall 1995

6 -transistor CMOS SRAM Cell Digital Integrated Circuits Memory © Prentice Hall 1995

CMOS SRAM Analysis (Write) Digital Integrated Circuits Memory © Prentice Hall 1995

CMOS SRAM Analysis (Read) Digital Integrated Circuits Memory © Prentice Hall 1995

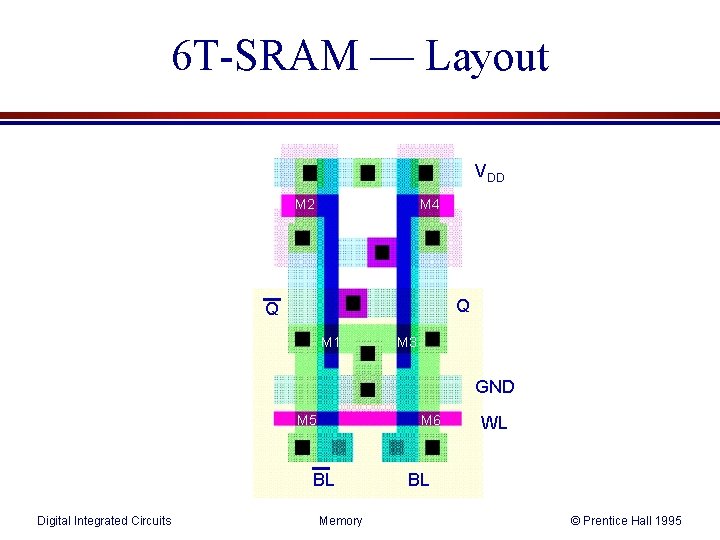

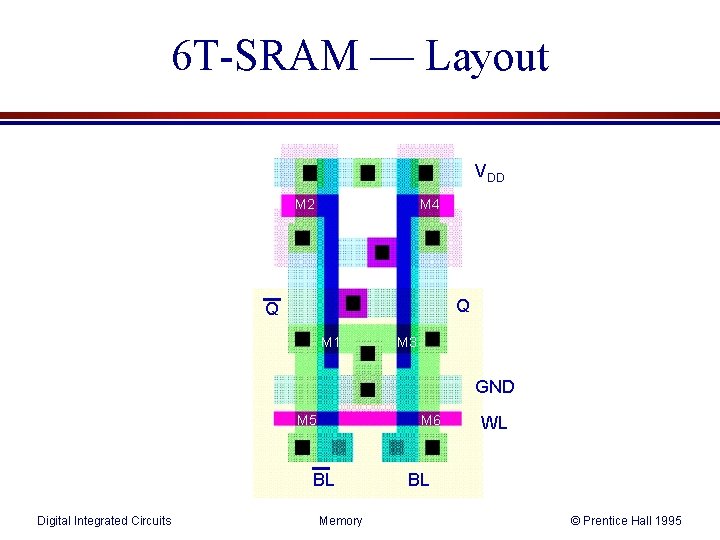

6 T-SRAM — Layout VDD M 2 M 4 Q Q M 1 M 3 GND M 5 M 6 BL Digital Integrated Circuits Memory WL BL © Prentice Hall 1995

Resistance-load SRAM Cell Digital Integrated Circuits Memory © Prentice Hall 1995

3 -Transistor DRAM Cell Digital Integrated Circuits Memory © Prentice Hall 1995

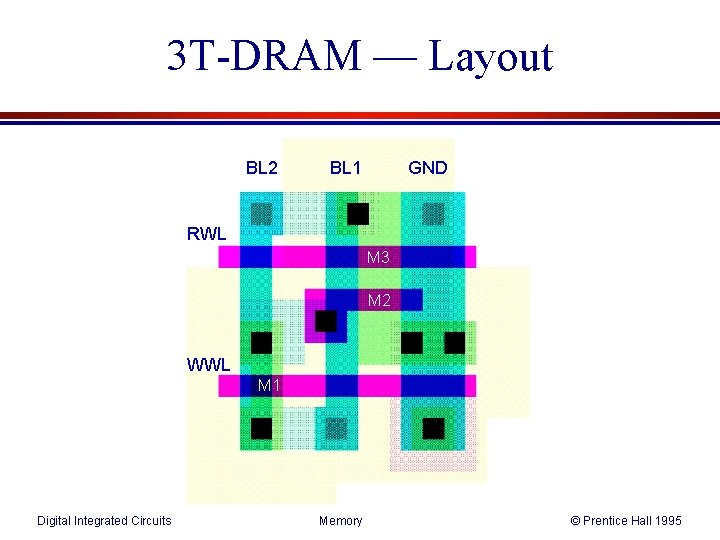

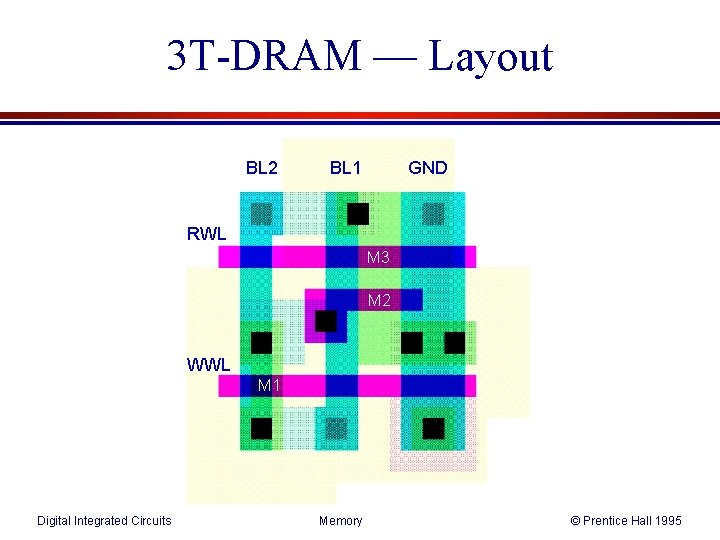

3 T-DRAM — Layout BL 2 BL 1 GND RWL M 3 M 2 WWL M 1 Digital Integrated Circuits Memory © Prentice Hall 1995

1 -Transistor DRAM Cell Digital Integrated Circuits Memory © Prentice Hall 1995

DRAM Cell Observations Digital Integrated Circuits Memory © Prentice Hall 1995

1 -T DRAM Cell Digital Integrated Circuits Memory © Prentice Hall 1995

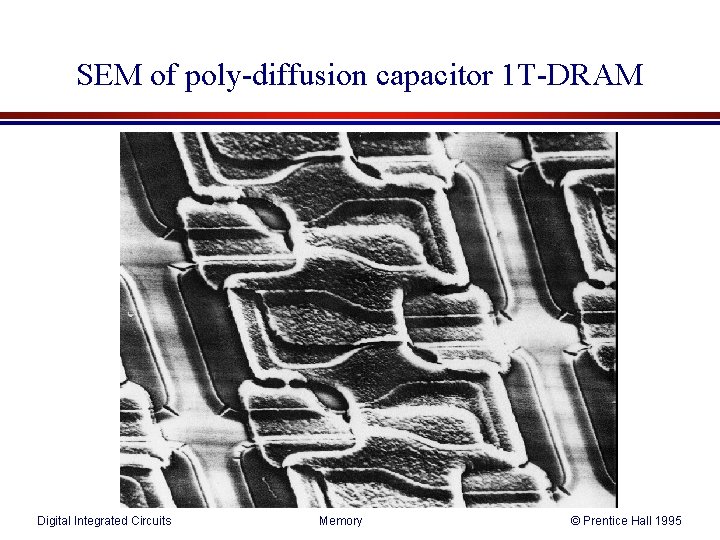

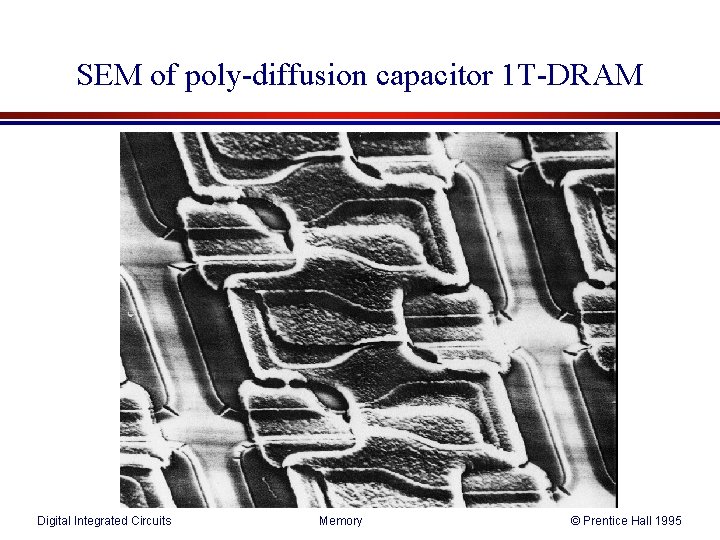

SEM of poly-diffusion capacitor 1 T-DRAM Digital Integrated Circuits Memory © Prentice Hall 1995

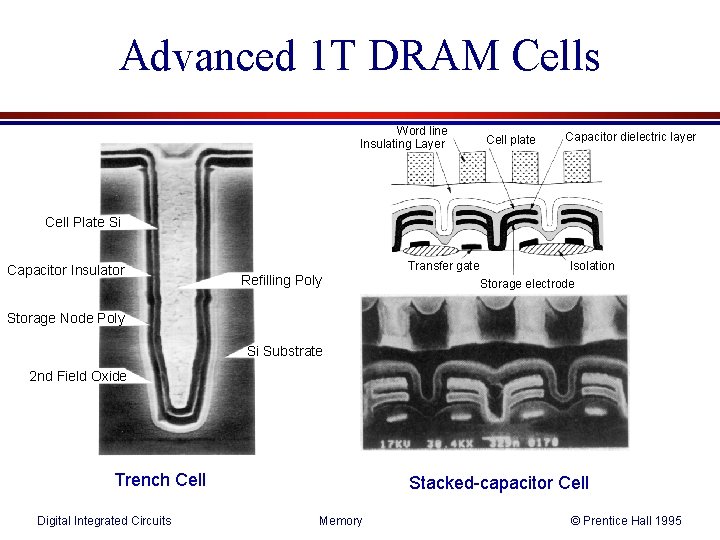

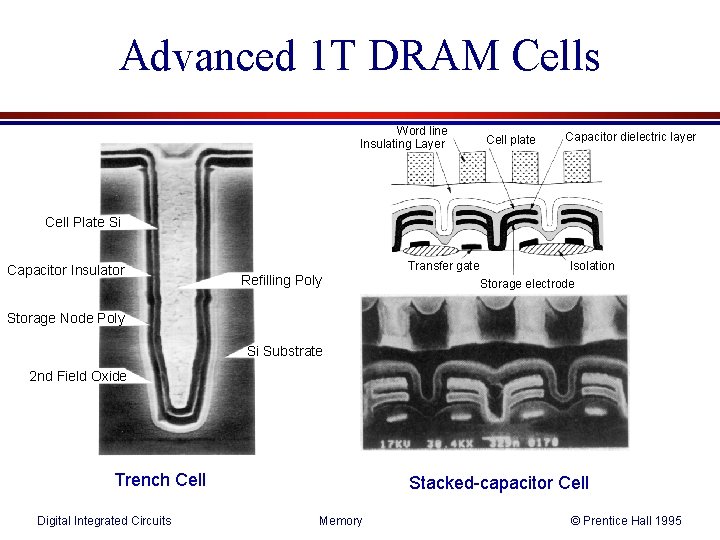

Advanced 1 T DRAM Cells Word line Insulating Layer Cell plate Capacitor dielectric layer Cell Plate Si Capacitor Insulator Transfer gate Refilling Poly Isolation Storage electrode Storage Node Poly Si Substrate 2 nd Field Oxide Trench Cell Digital Integrated Circuits Stacked-capacitor Cell Memory © Prentice Hall 1995

Periphery Digital Integrated Circuits Memory © Prentice Hall 1995

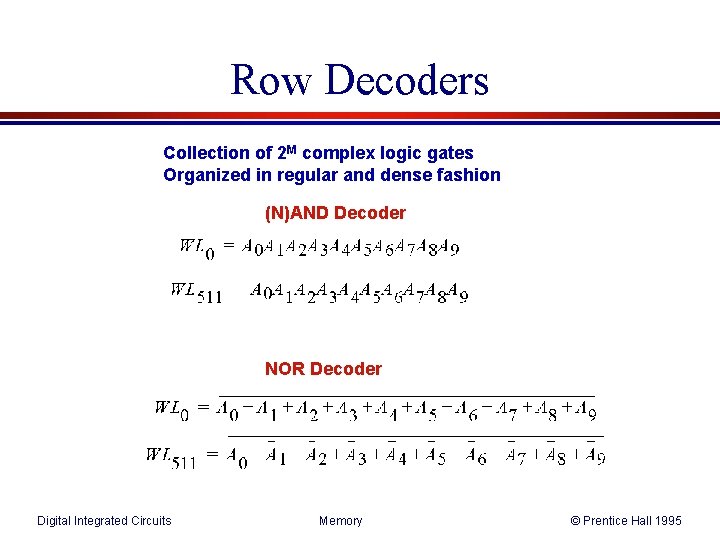

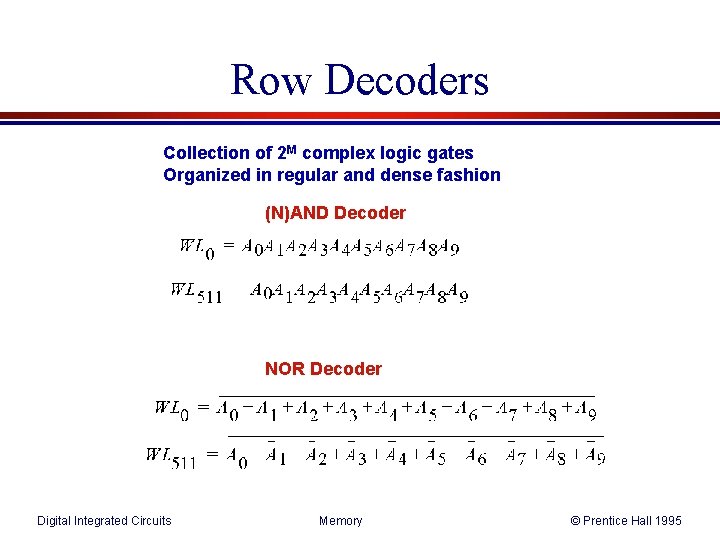

Row Decoders Collection of 2 M complex logic gates Organized in regular and dense fashion (N)AND Decoder NOR Decoder Digital Integrated Circuits Memory © Prentice Hall 1995

Dynamic Decoders Digital Integrated Circuits Memory © Prentice Hall 1995

A NAND decoder using 2 -input pre-decoders Digital Integrated Circuits Memory © Prentice Hall 1995

4 input pass-transistor based column decoder Digital Integrated Circuits Memory © Prentice Hall 1995

4 -to-1 tree based column decoder Digital Integrated Circuits Memory © Prentice Hall 1995

Decoder for circular shift-register Digital Integrated Circuits Memory © Prentice Hall 1995

Sense Amplifiers Digital Integrated Circuits Memory © Prentice Hall 1995

Differential Sensing - SRAM Digital Integrated Circuits Memory © Prentice Hall 1995

Latch-Based Sense Amplifier Digital Integrated Circuits Memory © Prentice Hall 1995

Single-to-Differential Conversion Digital Integrated Circuits Memory © Prentice Hall 1995

Open bitline architecture Digital Integrated Circuits Memory © Prentice Hall 1995

DRAM Read Process with Dummy Cell Digital Integrated Circuits Memory © Prentice Hall 1995

Single-Ended Cascode Amplifier Digital Integrated Circuits Memory © Prentice Hall 1995

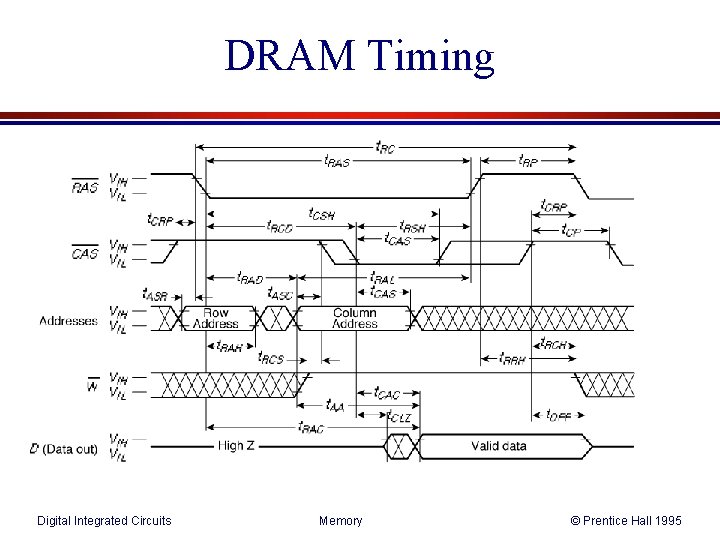

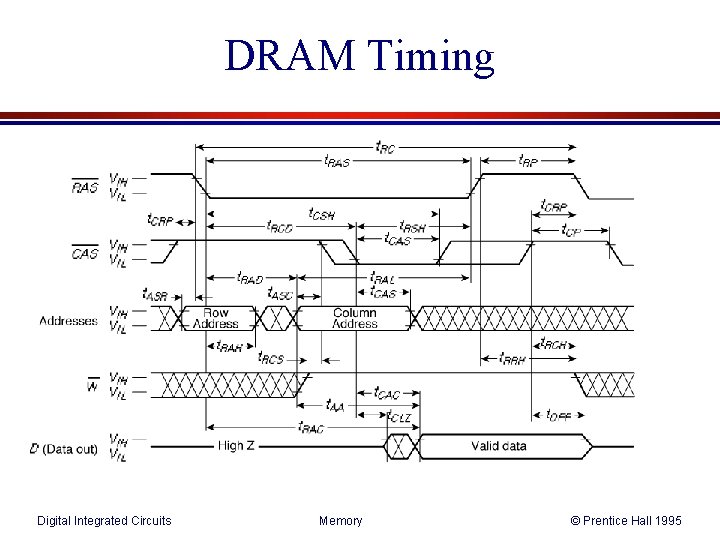

DRAM Timing Digital Integrated Circuits Memory © Prentice Hall 1995

Address Transition Detection Digital Integrated Circuits Memory © Prentice Hall 1995

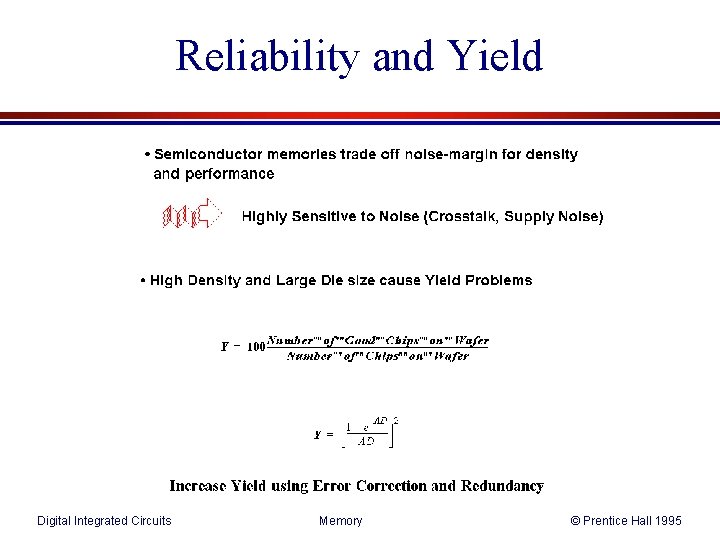

Reliability and Yield Digital Integrated Circuits Memory © Prentice Hall 1995

Open Bit-line Architecture —Cross Coupling Digital Integrated Circuits Memory © Prentice Hall 1995

Folded-Bitline Architecture Digital Integrated Circuits Memory © Prentice Hall 1995

Transposed-Bitline Architecture Digital Integrated Circuits Memory © Prentice Hall 1995

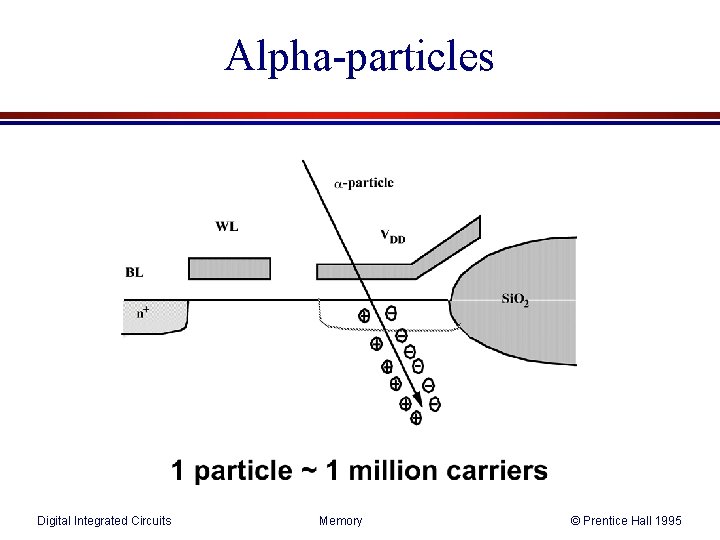

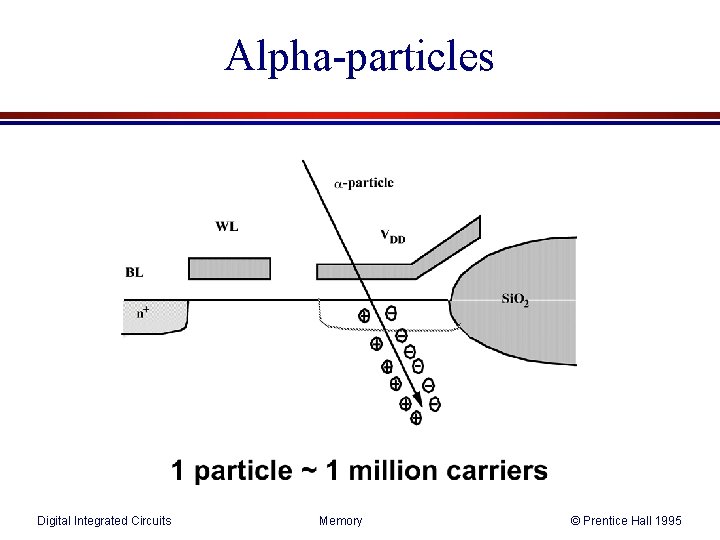

Alpha-particles Digital Integrated Circuits Memory © Prentice Hall 1995

![Yield curves at different stages of process maturity from Veendrick 92 Digital Integrated Circuits Yield curves at different stages of process maturity (from [Veendrick 92]) Digital Integrated Circuits](https://slidetodoc.com/presentation_image/368cca29aaf098bee624d5a859edb23c/image-59.jpg)

Yield curves at different stages of process maturity (from [Veendrick 92]) Digital Integrated Circuits Memory © Prentice Hall 1995

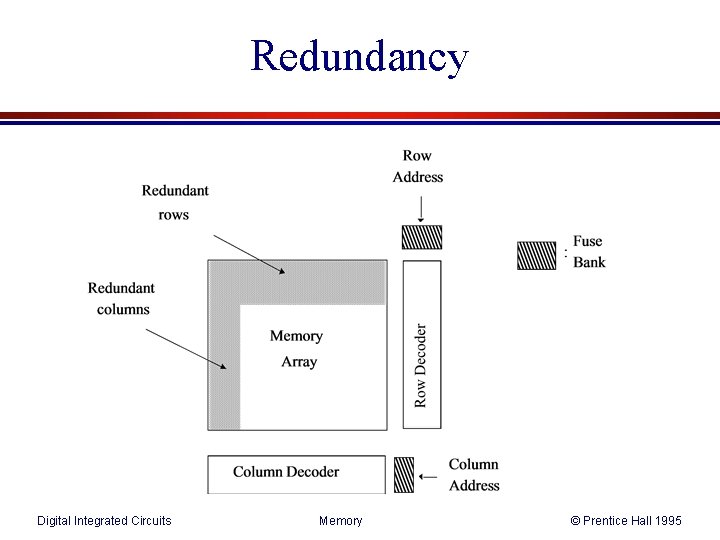

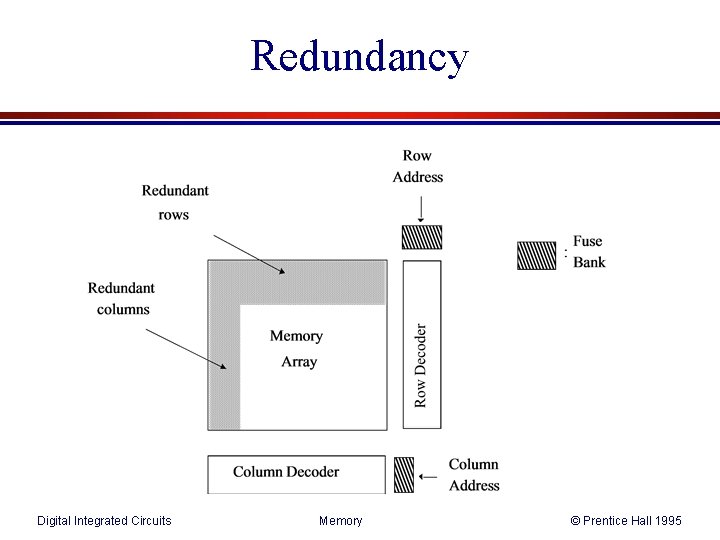

Redundancy Digital Integrated Circuits Memory © Prentice Hall 1995

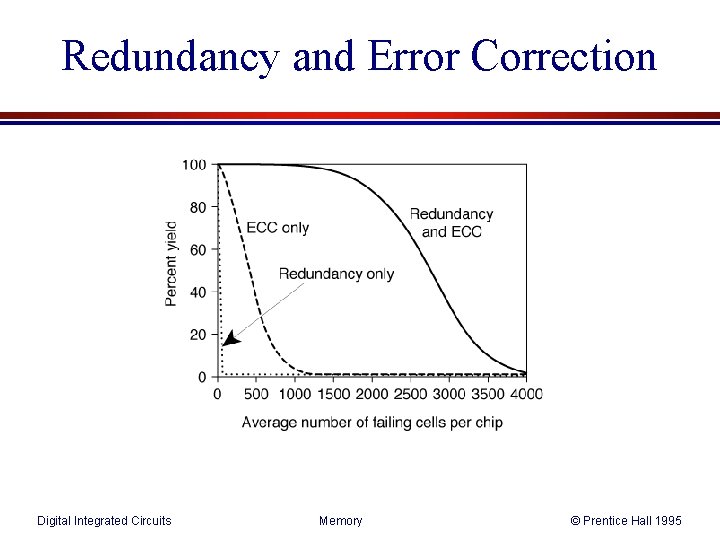

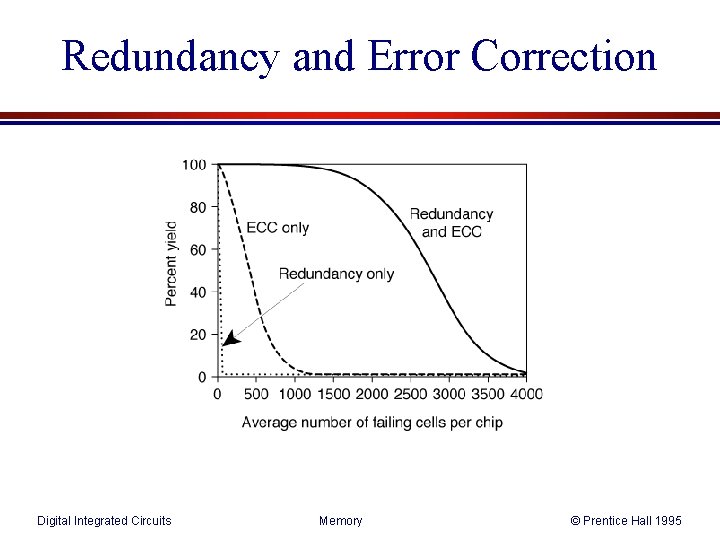

Redundancy and Error Correction Digital Integrated Circuits Memory © Prentice Hall 1995

Programmable Logic Array Digital Integrated Circuits Memory © Prentice Hall 1995

Pseudo-Static PLA Digital Integrated Circuits Memory © Prentice Hall 1995

Dynamic PLA Digital Integrated Circuits Memory © Prentice Hall 1995

Clock Signal Generation for self-timed dynamic PLA Digital Integrated Circuits Memory © Prentice Hall 1995

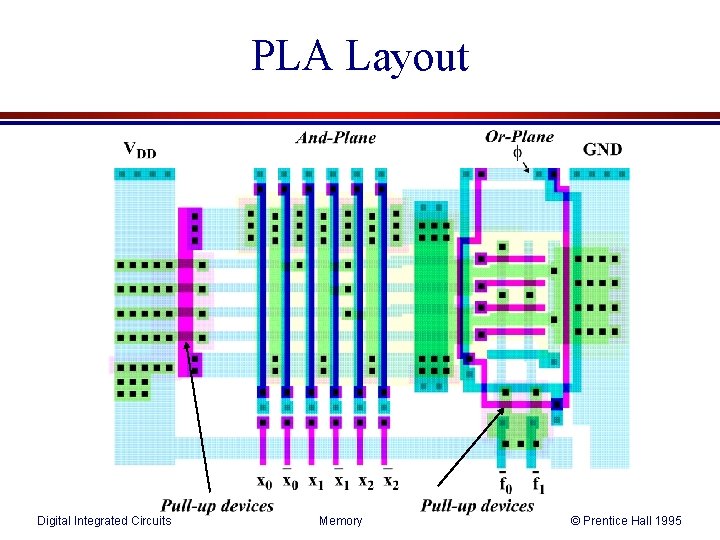

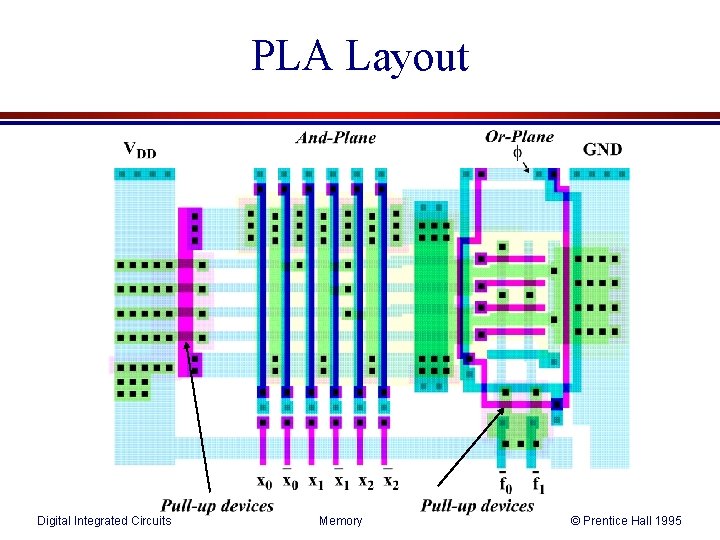

PLA Layout Digital Integrated Circuits Memory © Prentice Hall 1995

PLA versus ROM Digital Integrated Circuits Memory © Prentice Hall 1995

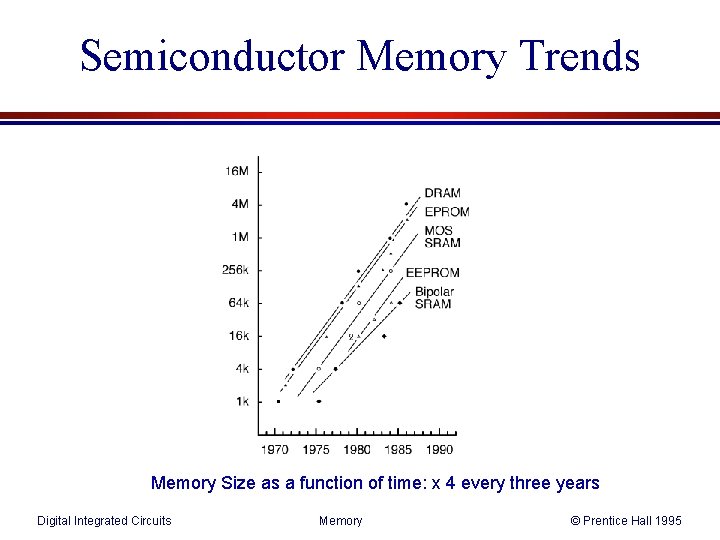

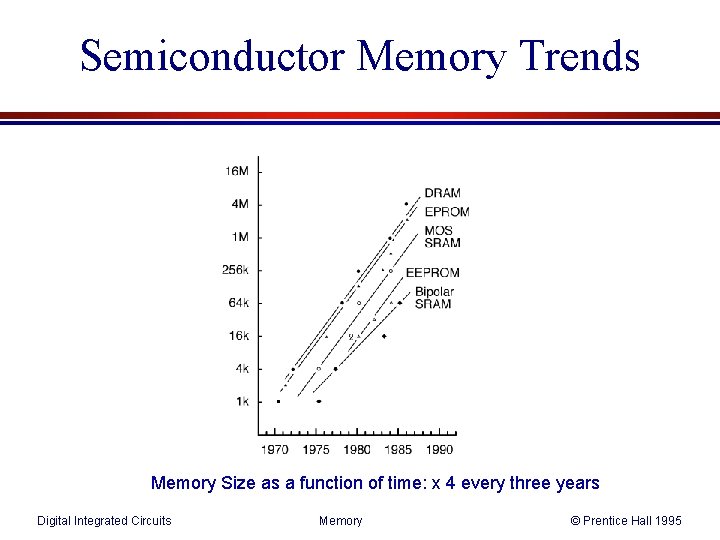

Semiconductor Memory Trends Memory Size as a function of time: x 4 every three years Digital Integrated Circuits Memory © Prentice Hall 1995

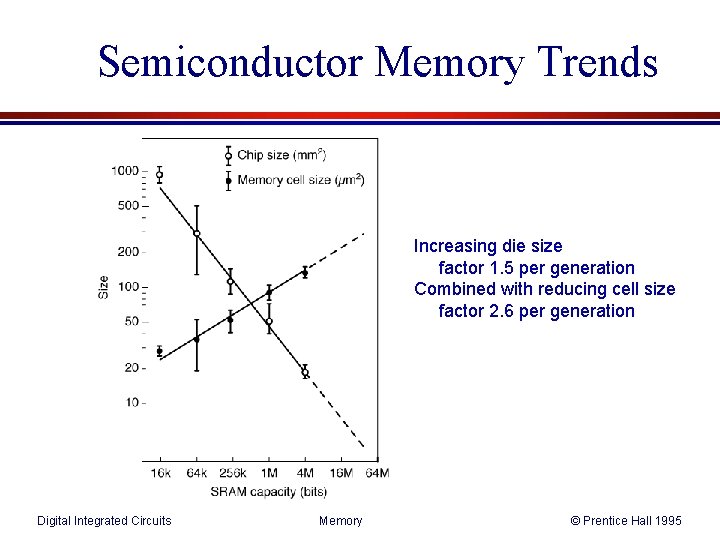

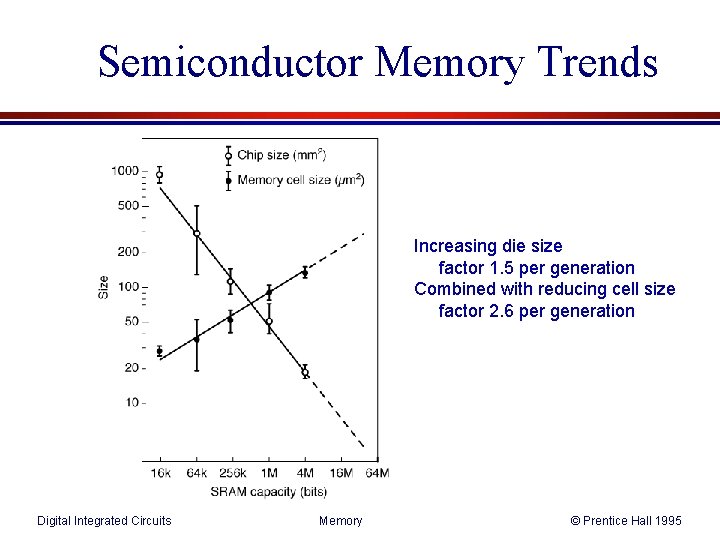

Semiconductor Memory Trends Increasing die size factor 1. 5 per generation Combined with reducing cell size factor 2. 6 per generation Digital Integrated Circuits Memory © Prentice Hall 1995

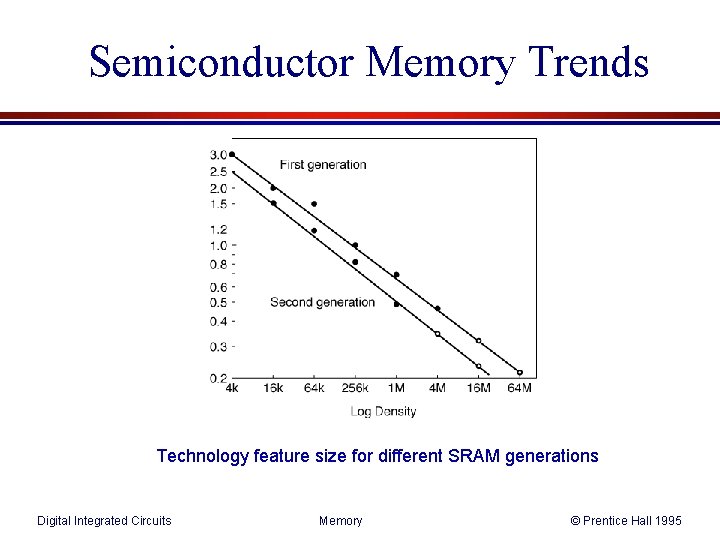

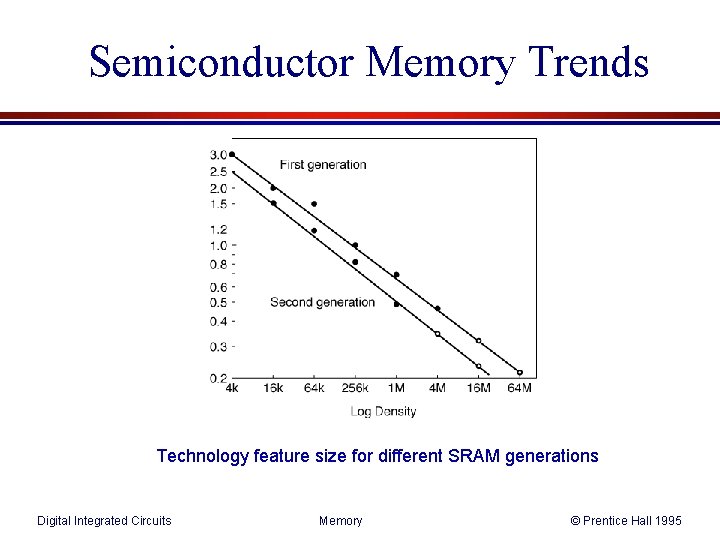

Semiconductor Memory Trends Technology feature size for different SRAM generations Digital Integrated Circuits Memory © Prentice Hall 1995