SEMICONDUCTOR MEMORIES Digital Integrated Circuits Memory Prentice Hall

- Slides: 43

SEMICONDUCTOR MEMORIES Digital Integrated Circuits Memory © Prentice Hall 1995

Chapter Overview Digital Integrated Circuits Memory © Prentice Hall 1995

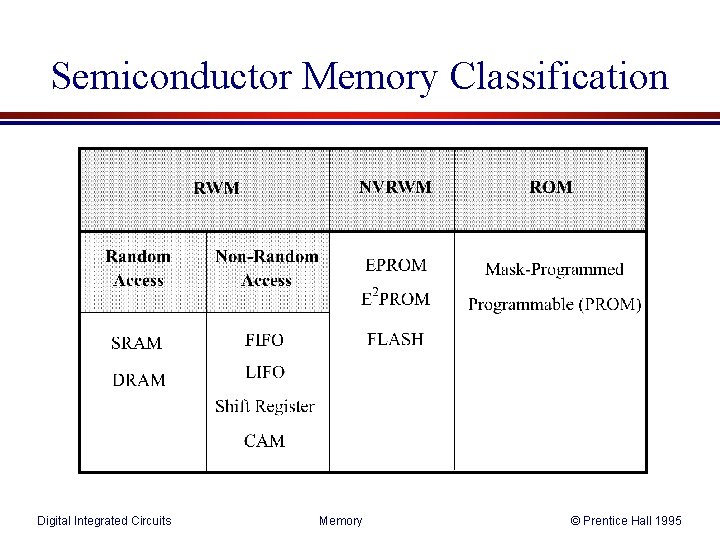

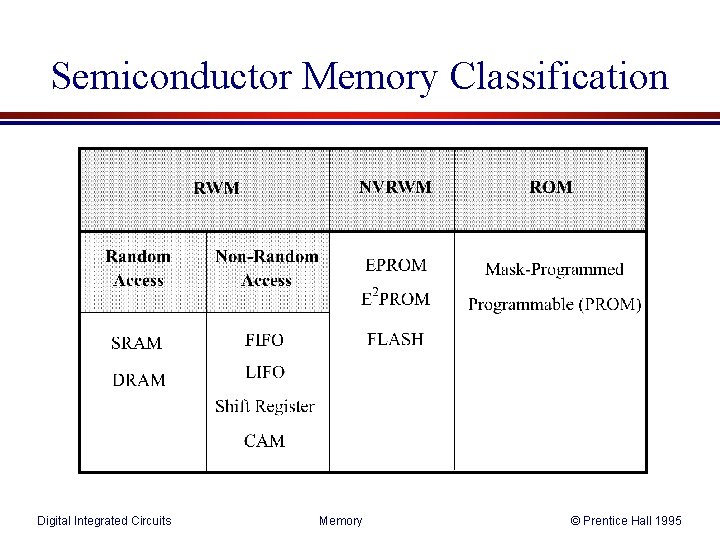

Semiconductor Memory Classification Digital Integrated Circuits Memory © Prentice Hall 1995

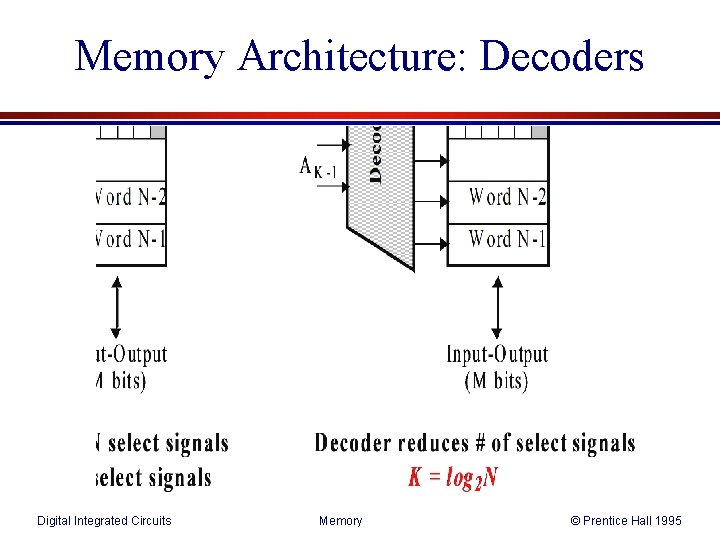

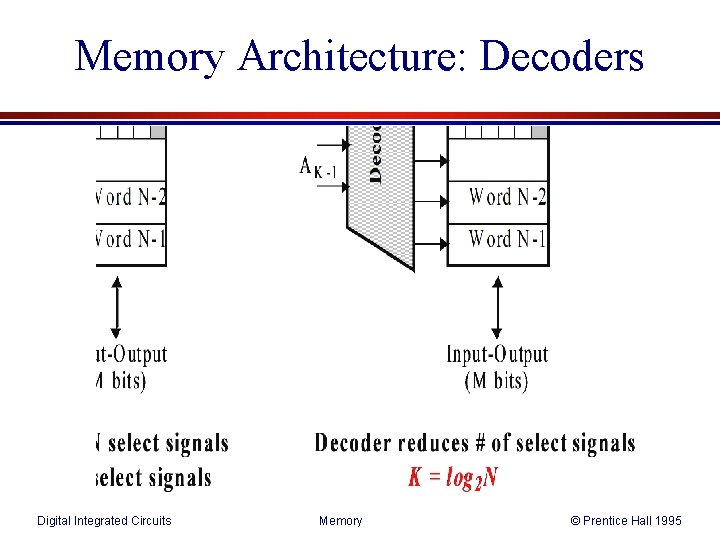

Memory Architecture: Decoders Digital Integrated Circuits Memory © Prentice Hall 1995

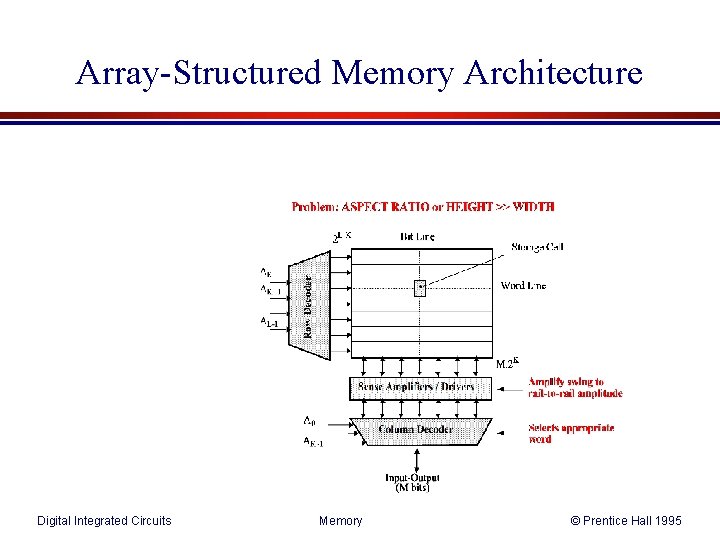

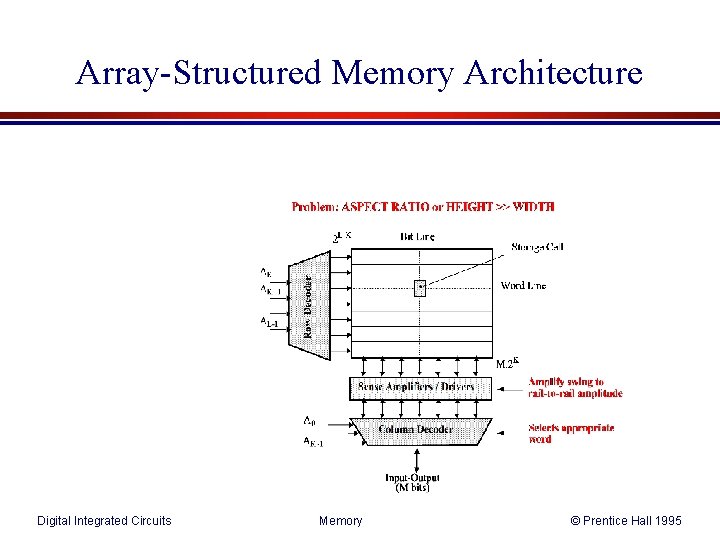

Array-Structured Memory Architecture Digital Integrated Circuits Memory © Prentice Hall 1995

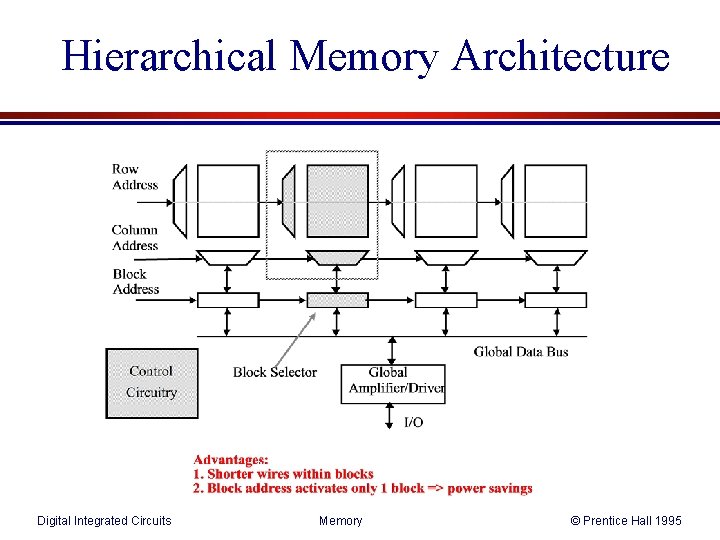

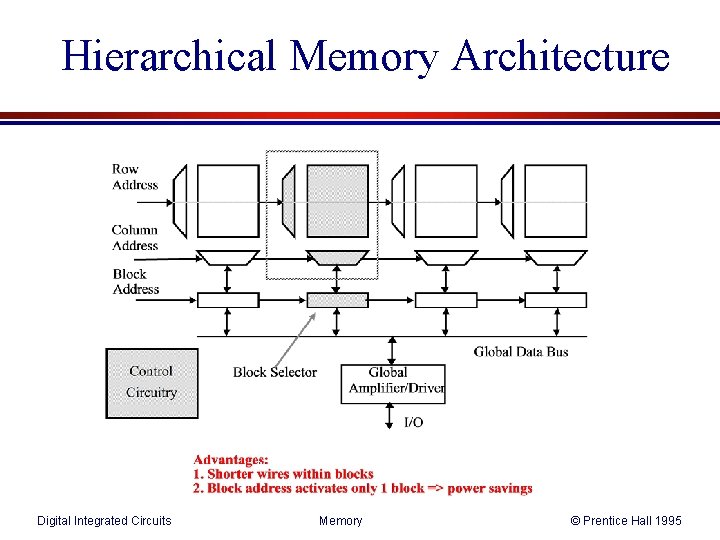

Hierarchical Memory Architecture Digital Integrated Circuits Memory © Prentice Hall 1995

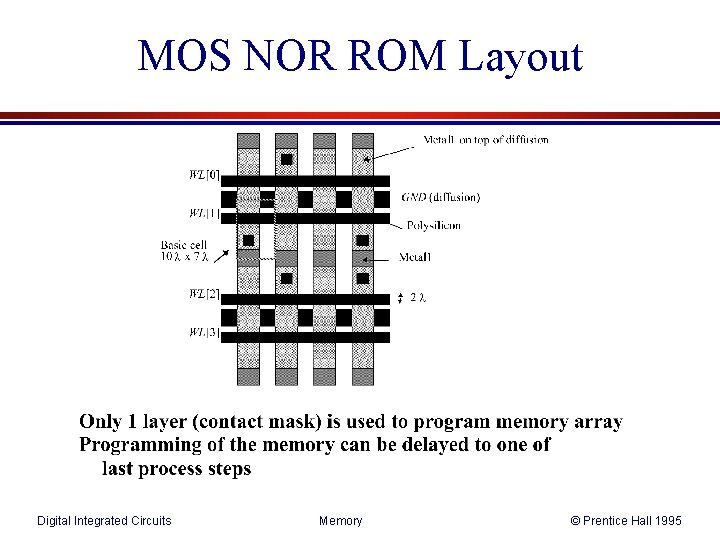

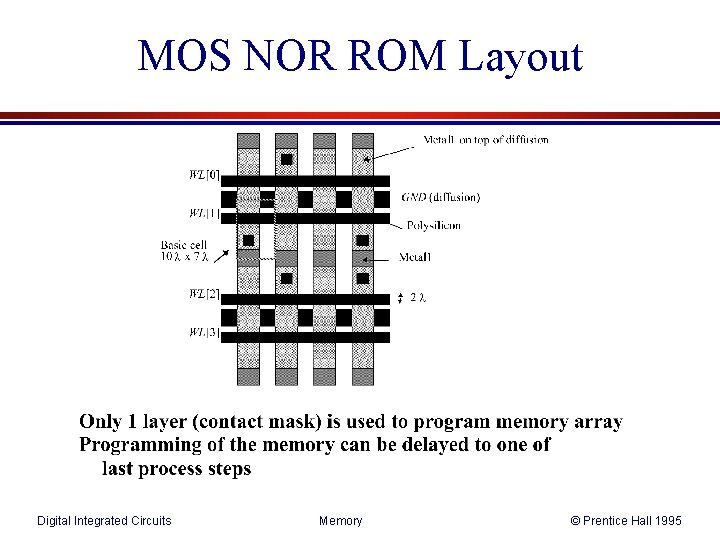

MOS NOR ROM Layout Digital Integrated Circuits Memory © Prentice Hall 1995

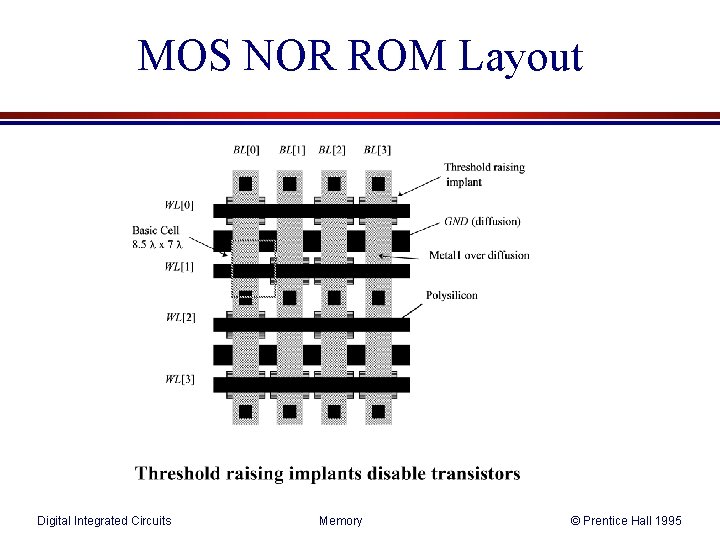

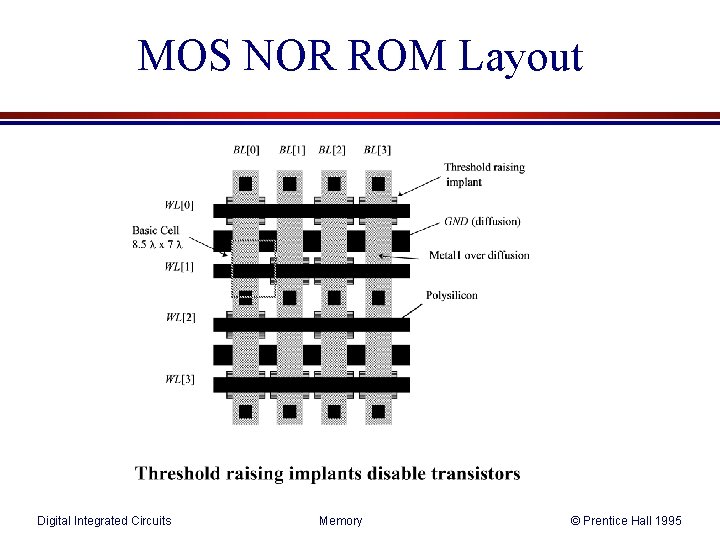

MOS NOR ROM Layout Digital Integrated Circuits Memory © Prentice Hall 1995

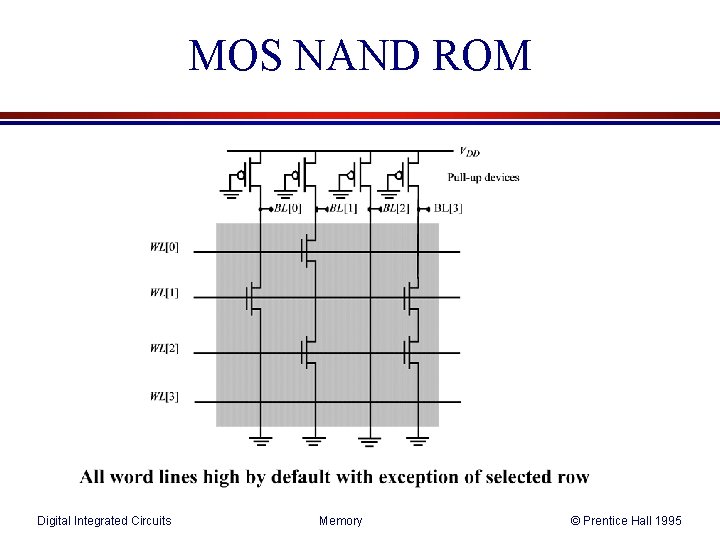

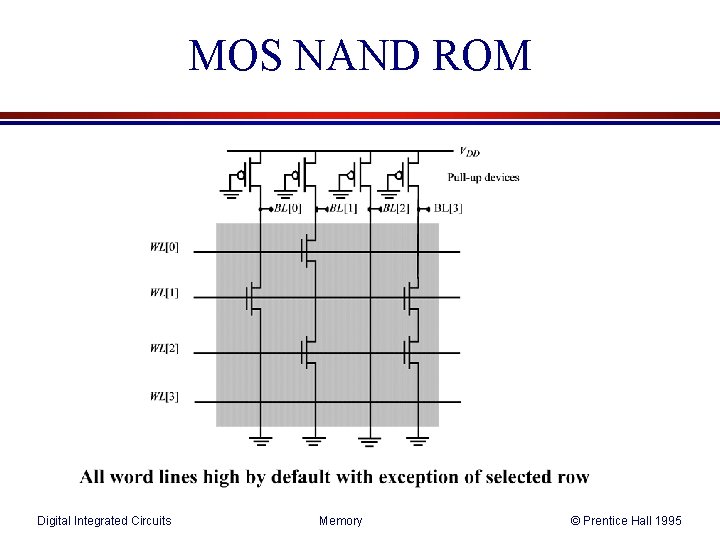

MOS NAND ROM Digital Integrated Circuits Memory © Prentice Hall 1995

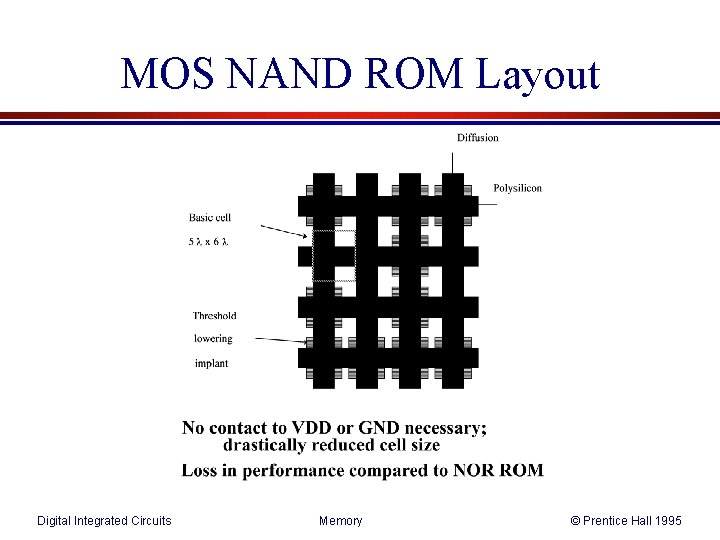

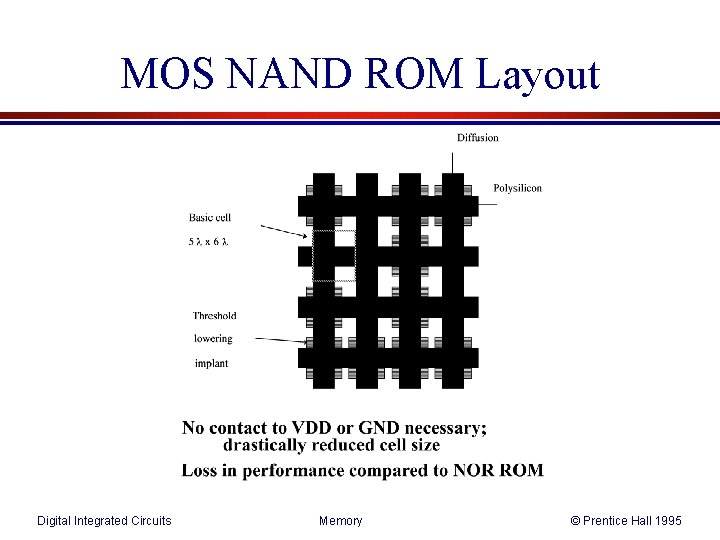

MOS NAND ROM Layout Digital Integrated Circuits Memory © Prentice Hall 1995

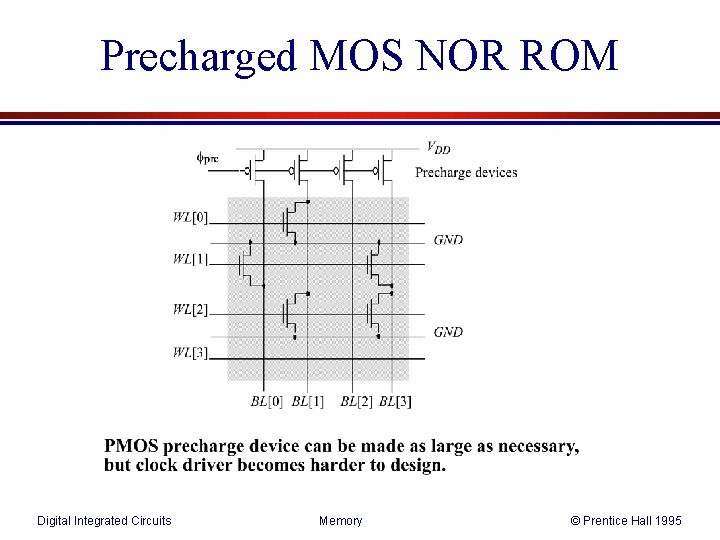

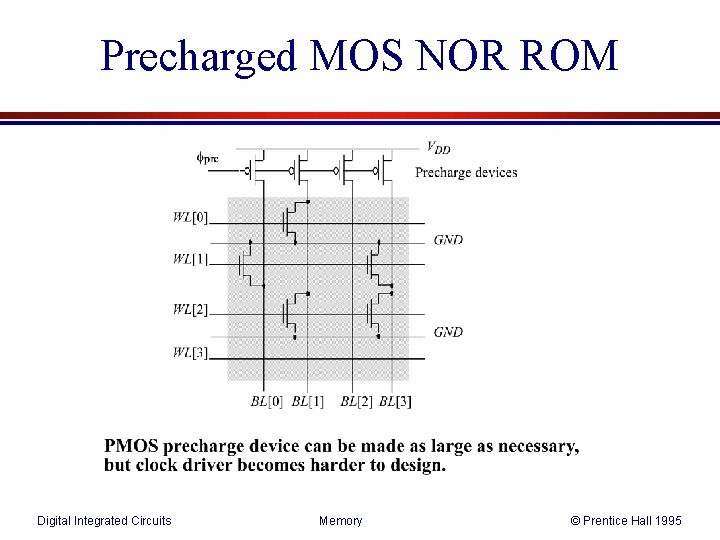

Precharged MOS NOR ROM Digital Integrated Circuits Memory © Prentice Hall 1995

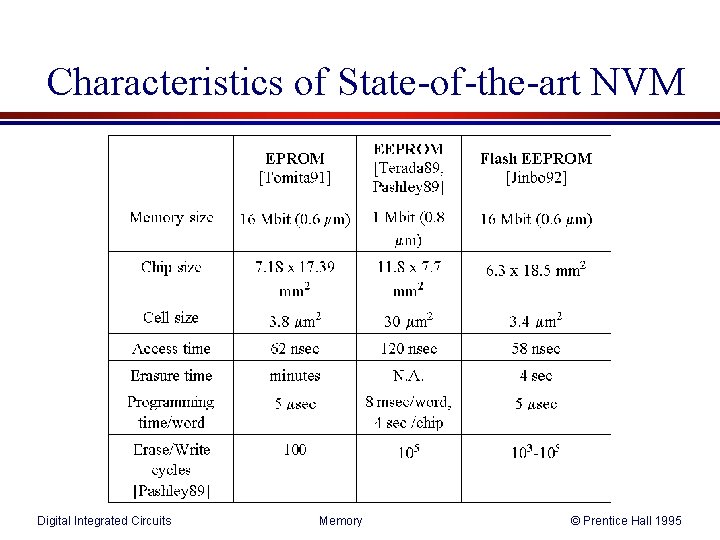

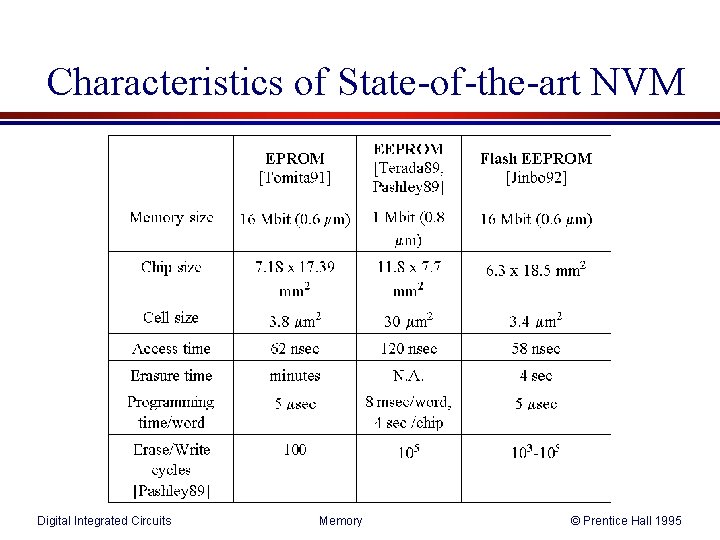

Characteristics of State-of-the-art NVM Digital Integrated Circuits Memory © Prentice Hall 1995

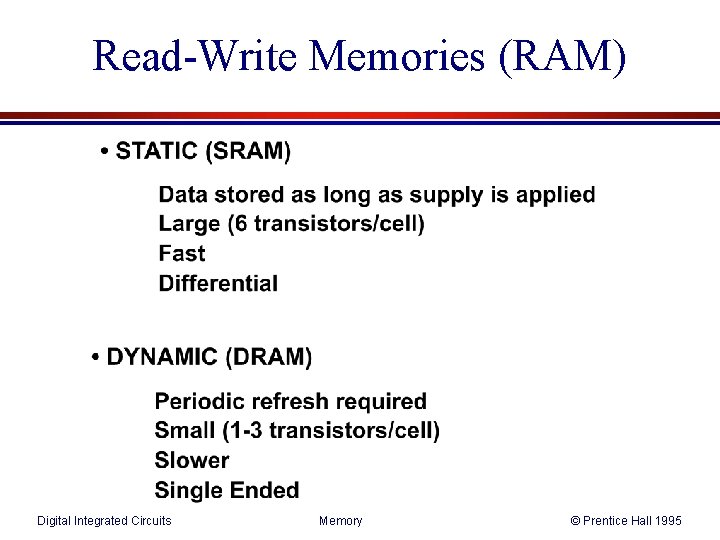

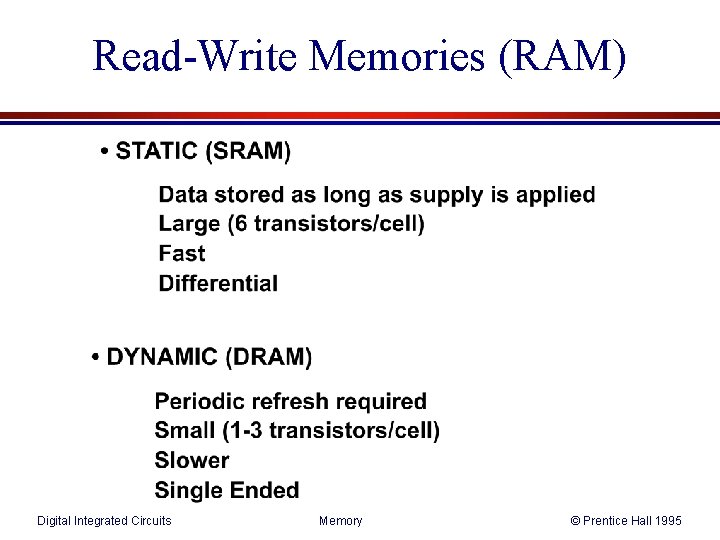

Read-Write Memories (RAM) Digital Integrated Circuits Memory © Prentice Hall 1995

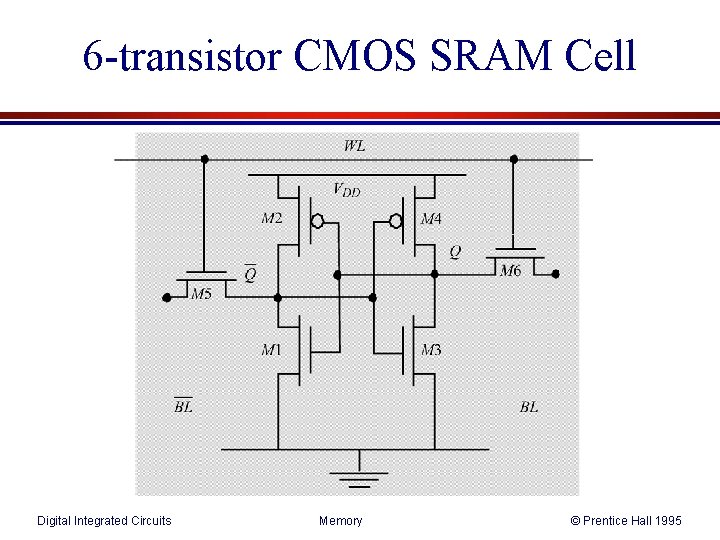

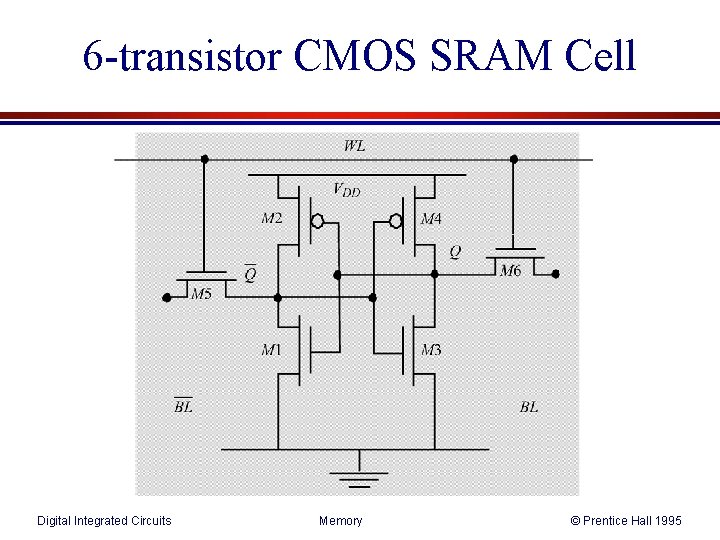

6 -transistor CMOS SRAM Cell Digital Integrated Circuits Memory © Prentice Hall 1995

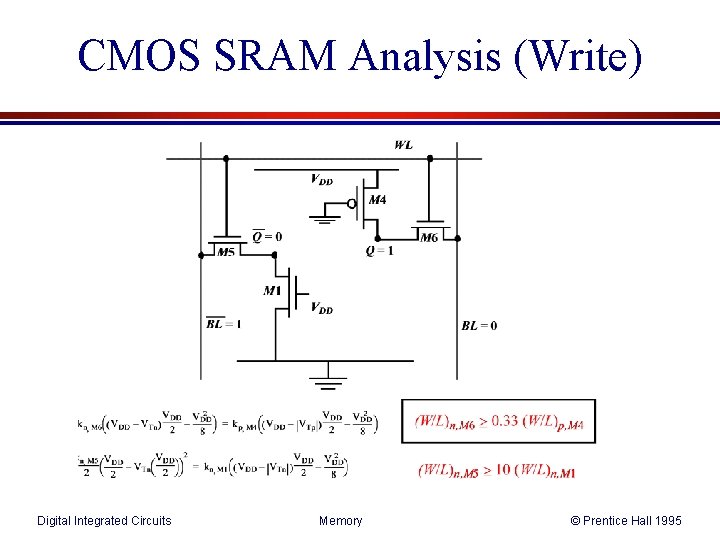

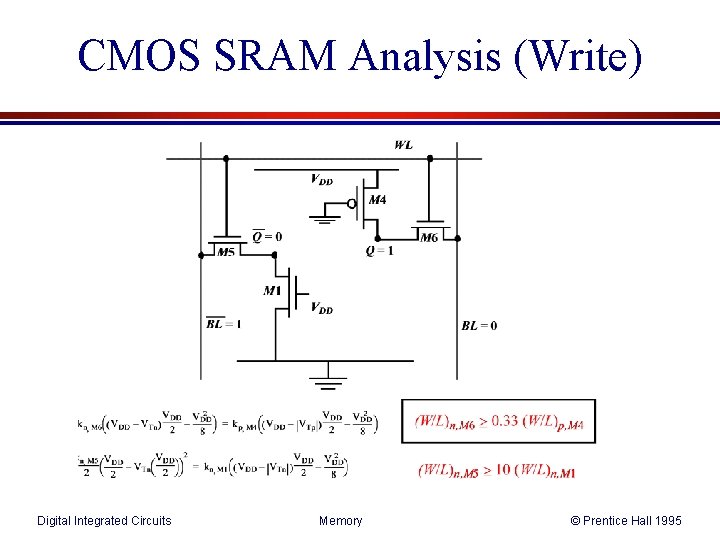

CMOS SRAM Analysis (Write) Digital Integrated Circuits Memory © Prentice Hall 1995

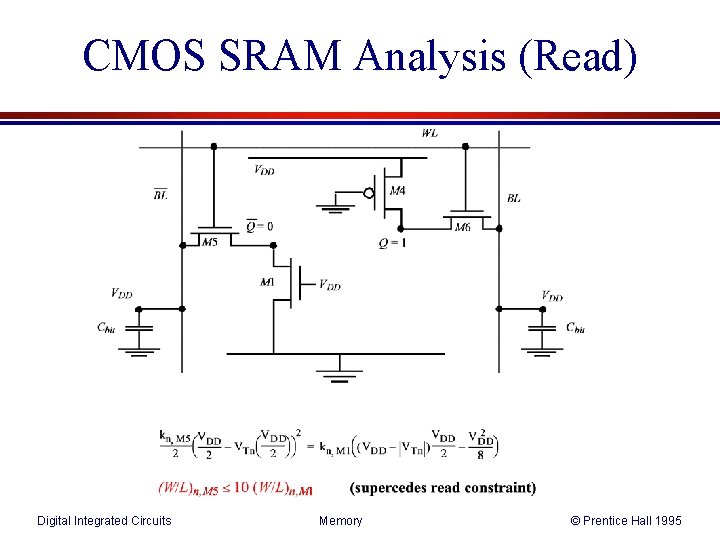

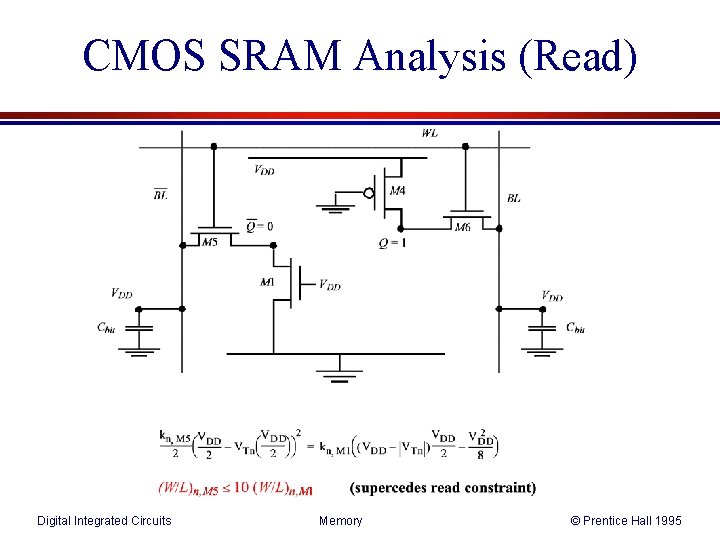

CMOS SRAM Analysis (Read) Digital Integrated Circuits Memory © Prentice Hall 1995

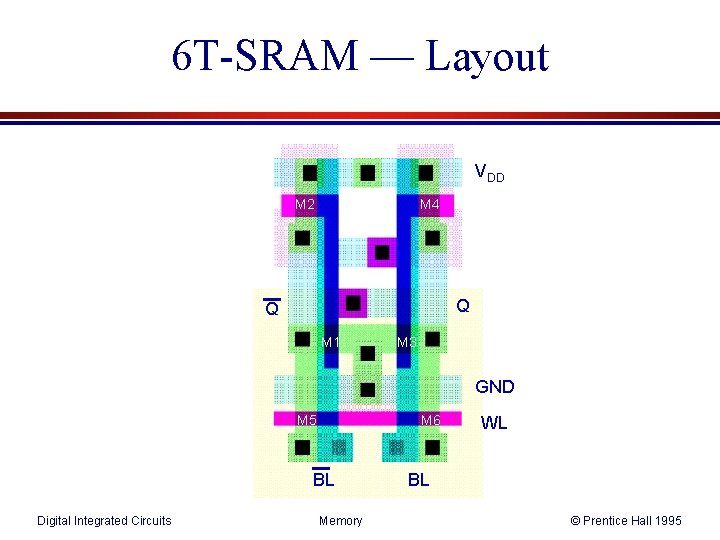

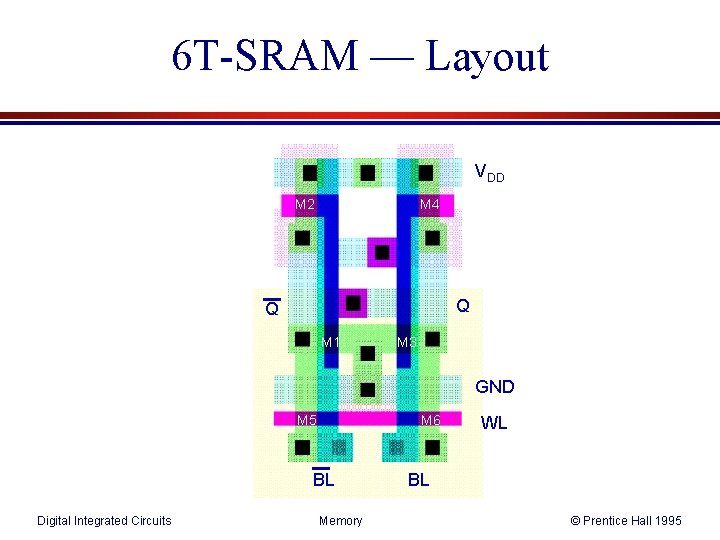

6 T-SRAM — Layout VDD M 2 M 4 Q Q M 1 M 3 GND M 5 M 6 BL Digital Integrated Circuits Memory WL BL © Prentice Hall 1995

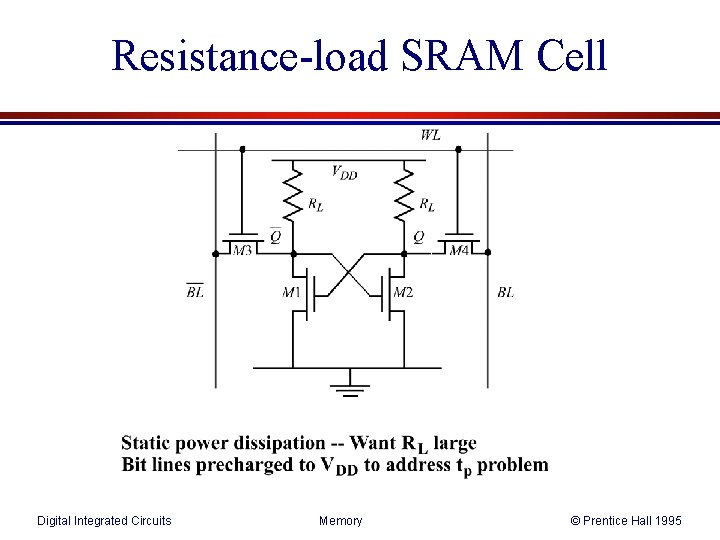

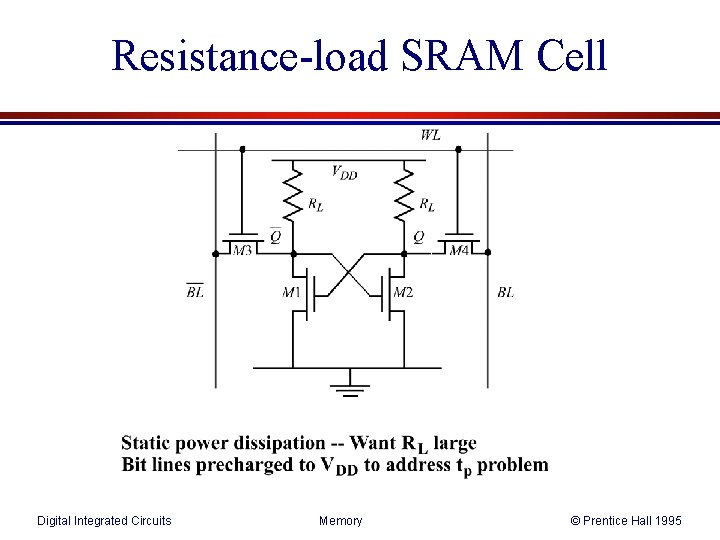

Resistance-load SRAM Cell Digital Integrated Circuits Memory © Prentice Hall 1995

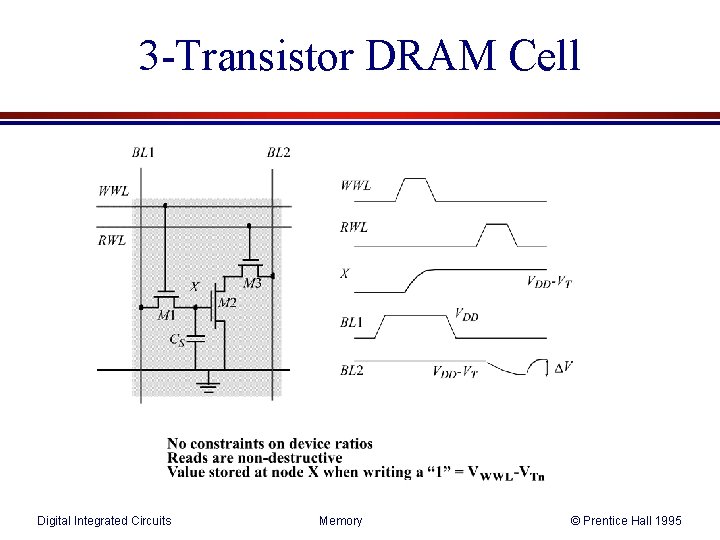

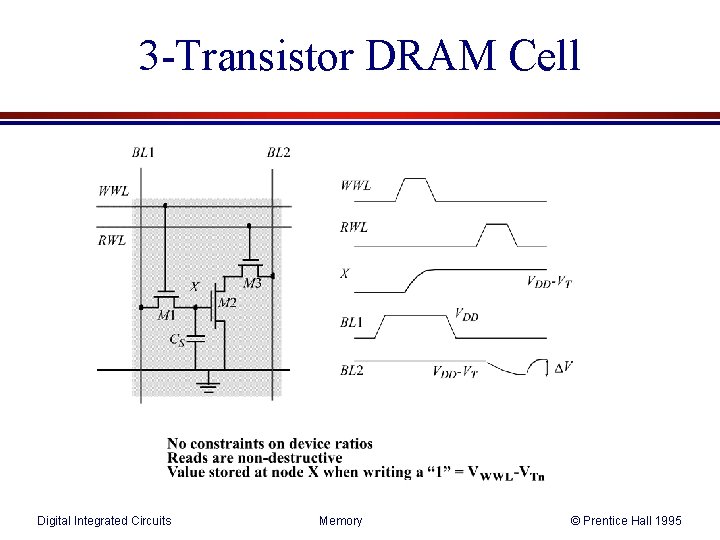

3 -Transistor DRAM Cell Digital Integrated Circuits Memory © Prentice Hall 1995

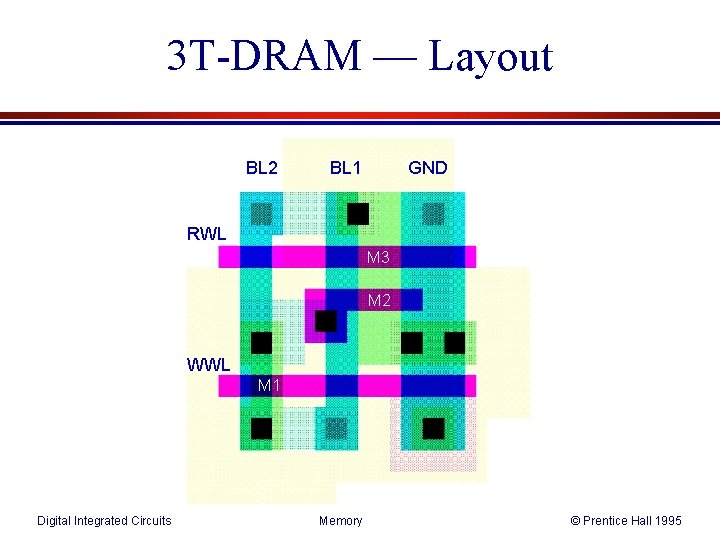

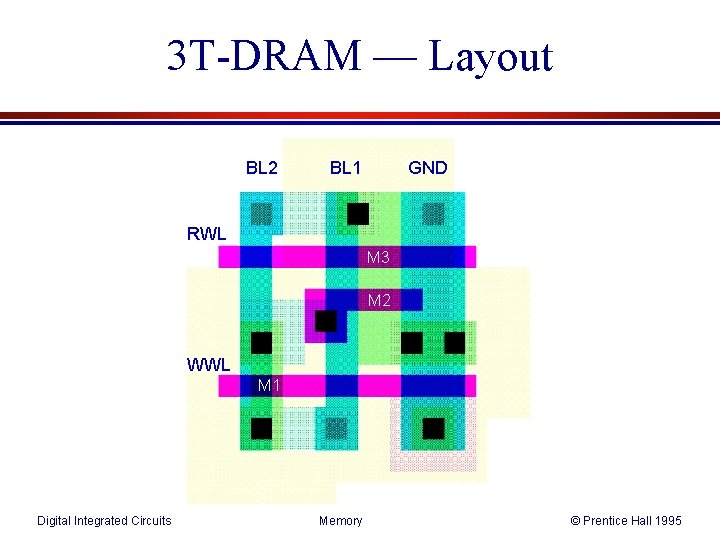

3 T-DRAM — Layout BL 2 BL 1 GND RWL M 3 M 2 WWL M 1 Digital Integrated Circuits Memory © Prentice Hall 1995

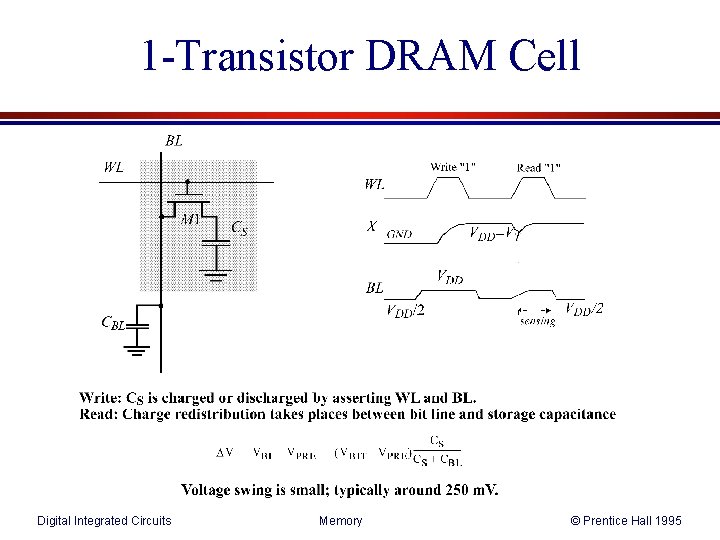

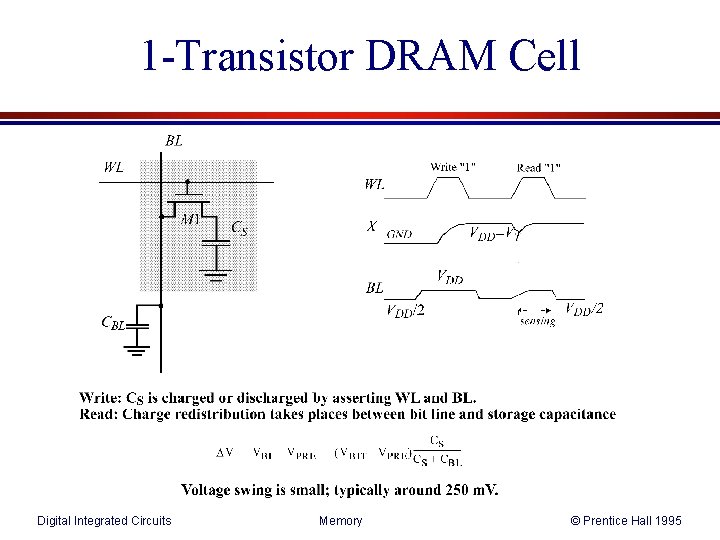

1 -Transistor DRAM Cell Digital Integrated Circuits Memory © Prentice Hall 1995

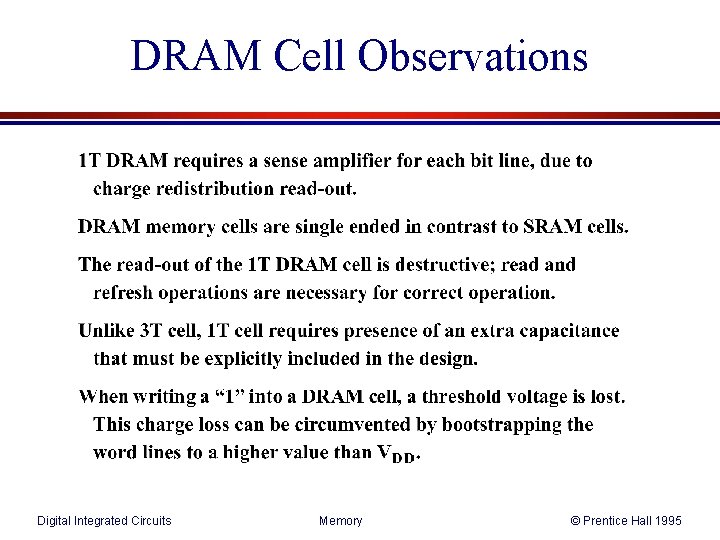

DRAM Cell Observations Digital Integrated Circuits Memory © Prentice Hall 1995

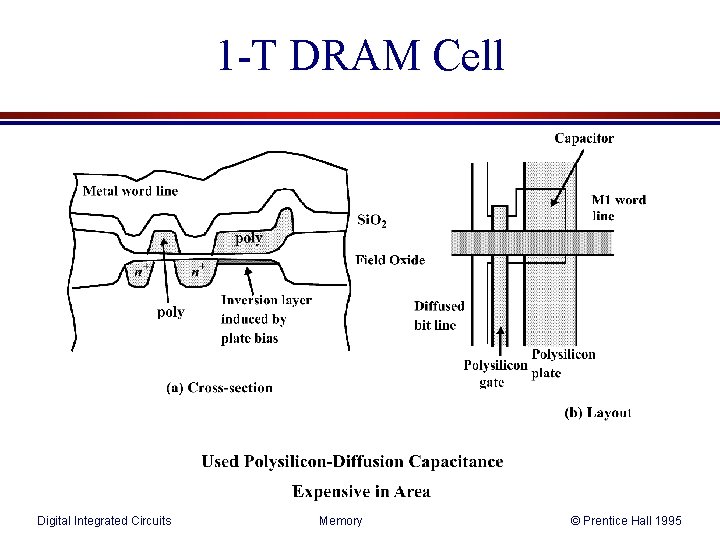

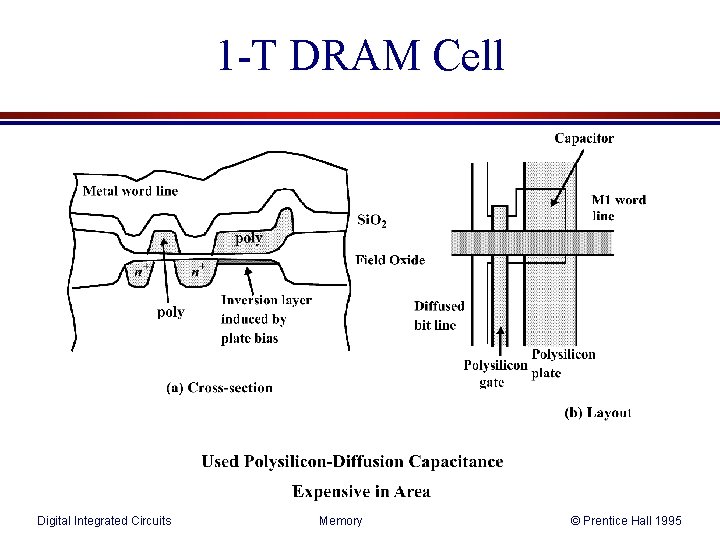

1 -T DRAM Cell Digital Integrated Circuits Memory © Prentice Hall 1995

Periphery Digital Integrated Circuits Memory © Prentice Hall 1995

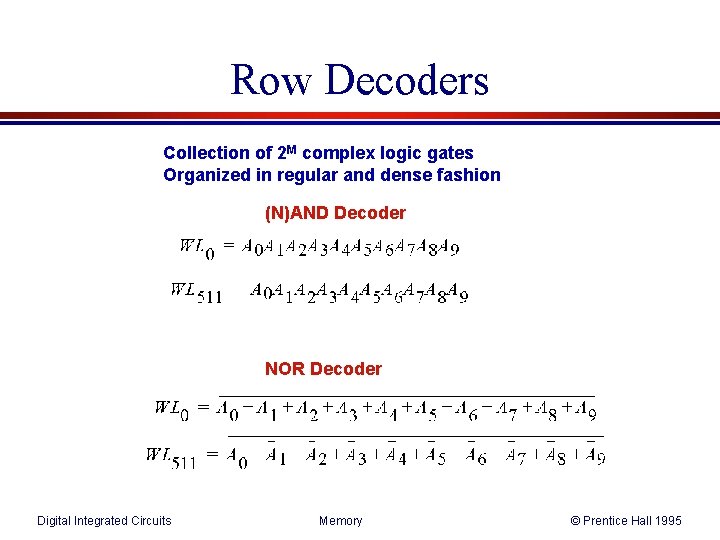

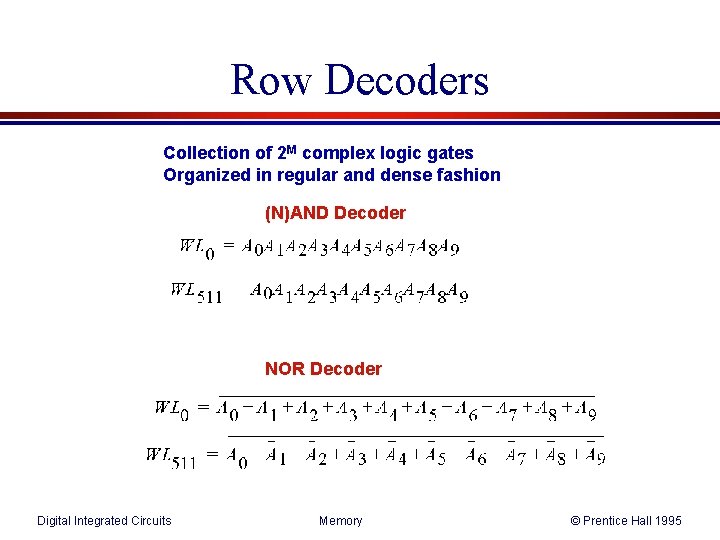

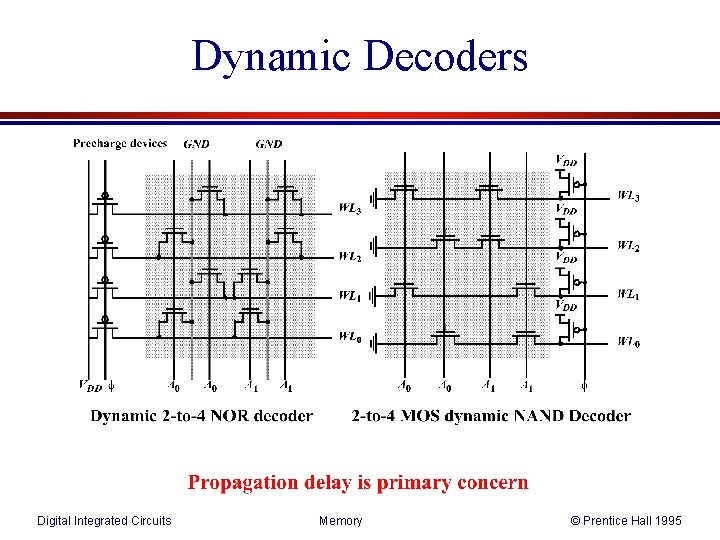

Row Decoders Collection of 2 M complex logic gates Organized in regular and dense fashion (N)AND Decoder NOR Decoder Digital Integrated Circuits Memory © Prentice Hall 1995

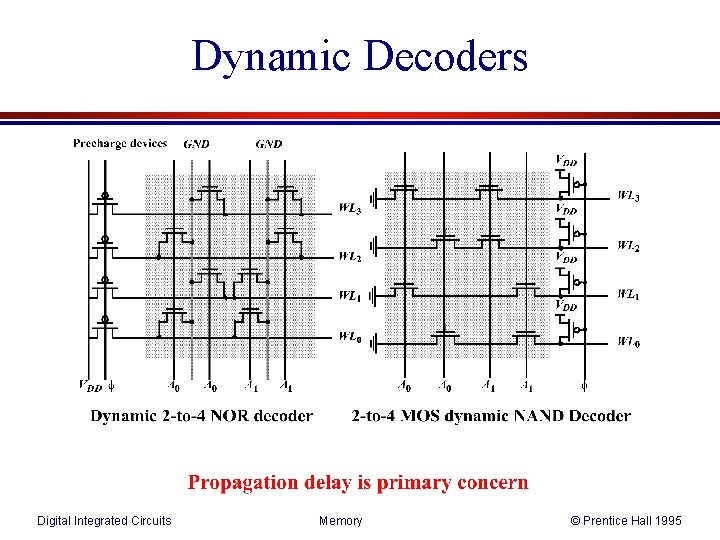

Dynamic Decoders Digital Integrated Circuits Memory © Prentice Hall 1995

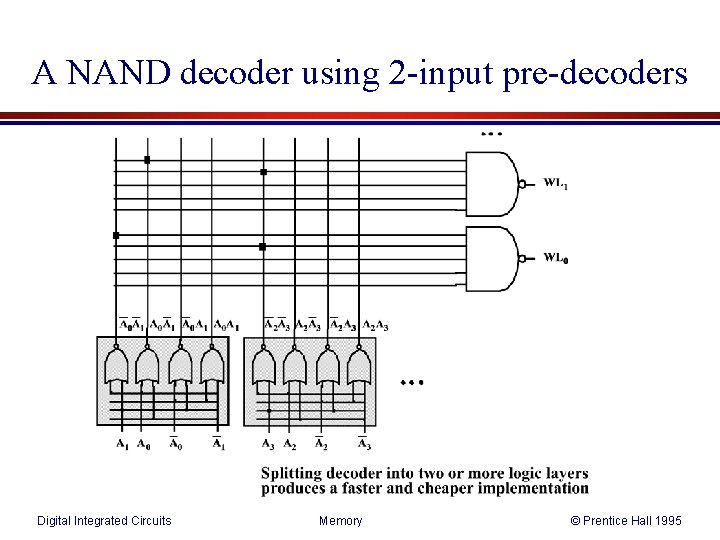

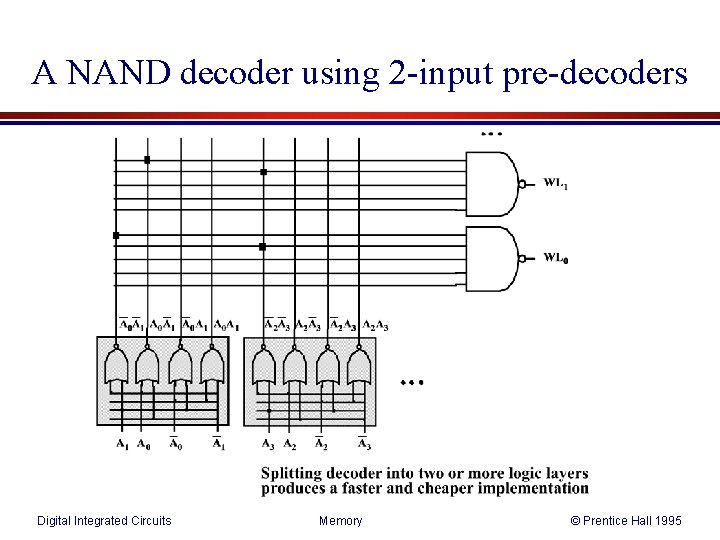

A NAND decoder using 2 -input pre-decoders Digital Integrated Circuits Memory © Prentice Hall 1995

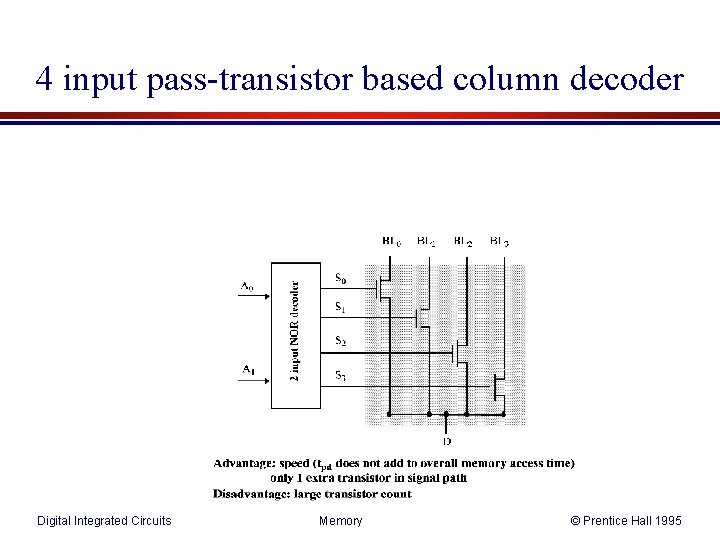

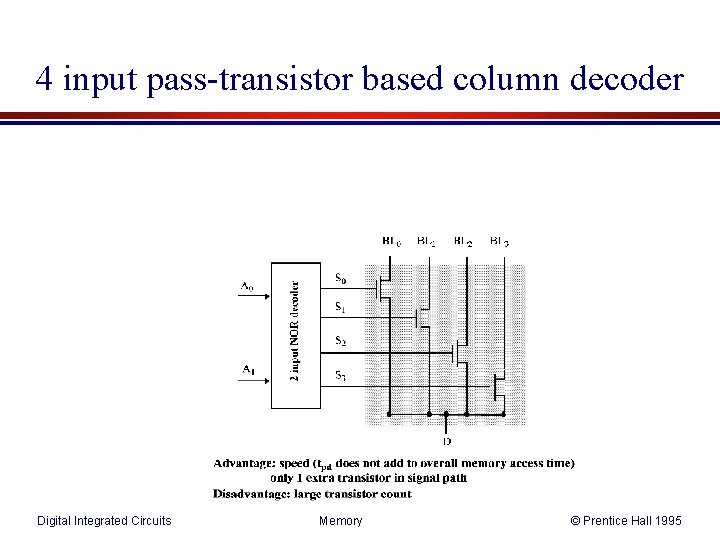

4 input pass-transistor based column decoder Digital Integrated Circuits Memory © Prentice Hall 1995

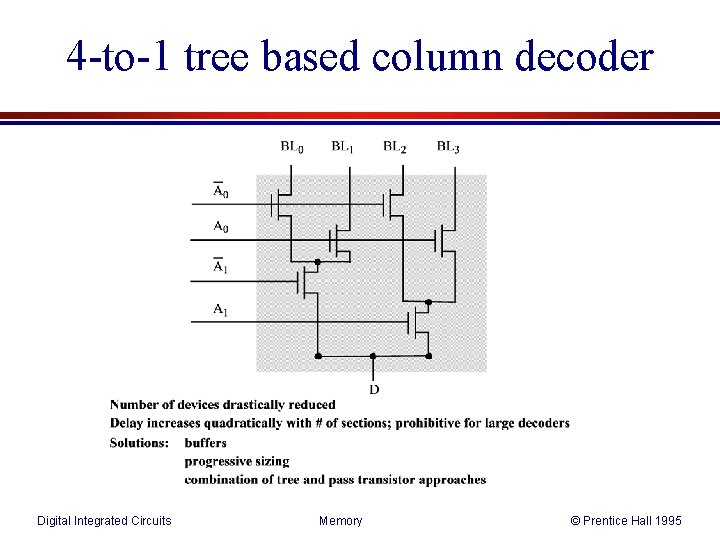

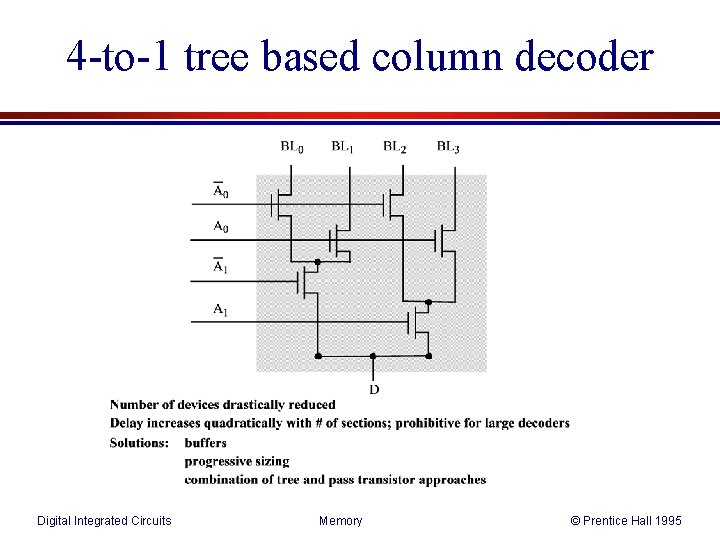

4 -to-1 tree based column decoder Digital Integrated Circuits Memory © Prentice Hall 1995

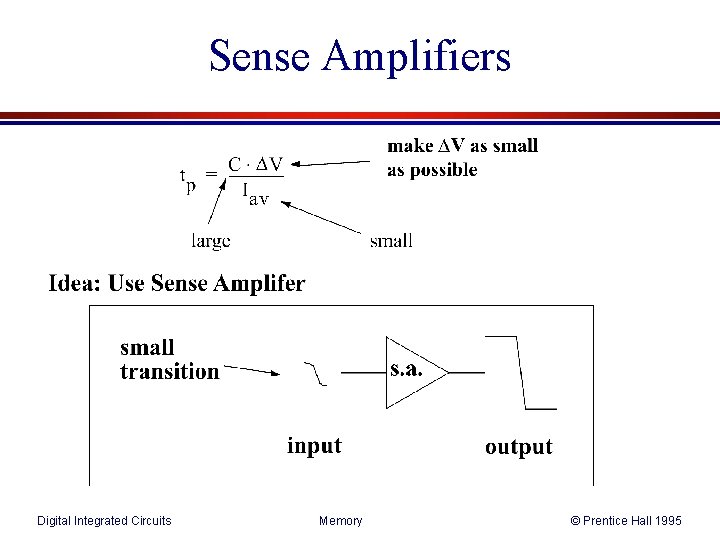

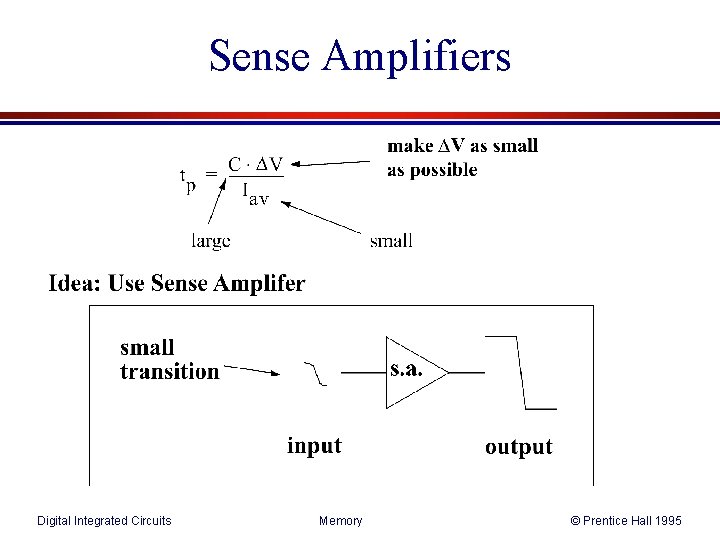

Sense Amplifiers Digital Integrated Circuits Memory © Prentice Hall 1995

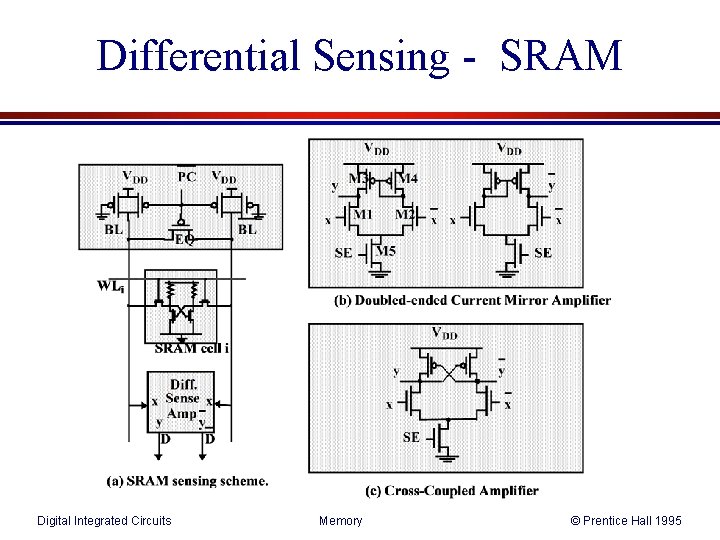

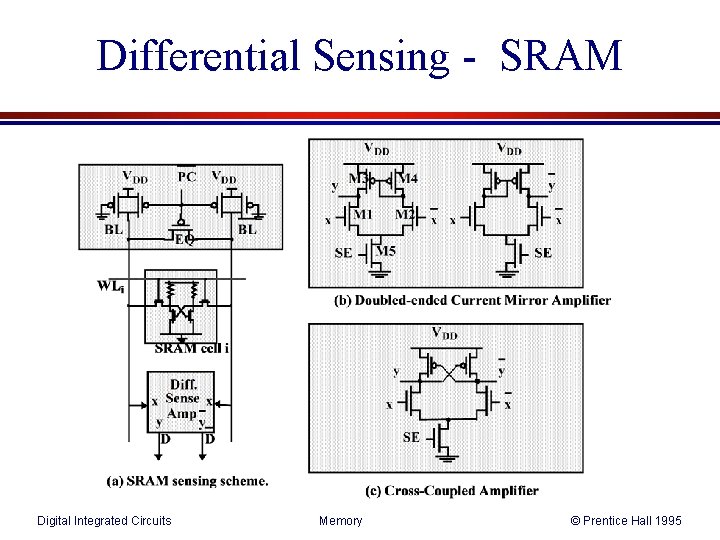

Differential Sensing - SRAM Digital Integrated Circuits Memory © Prentice Hall 1995

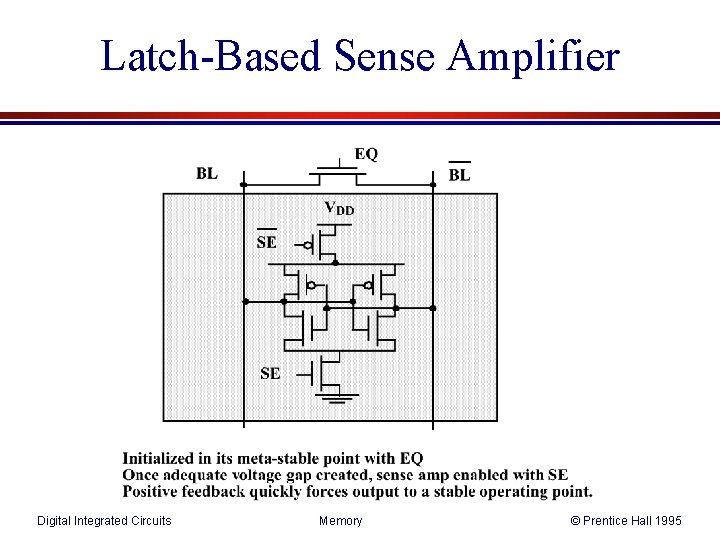

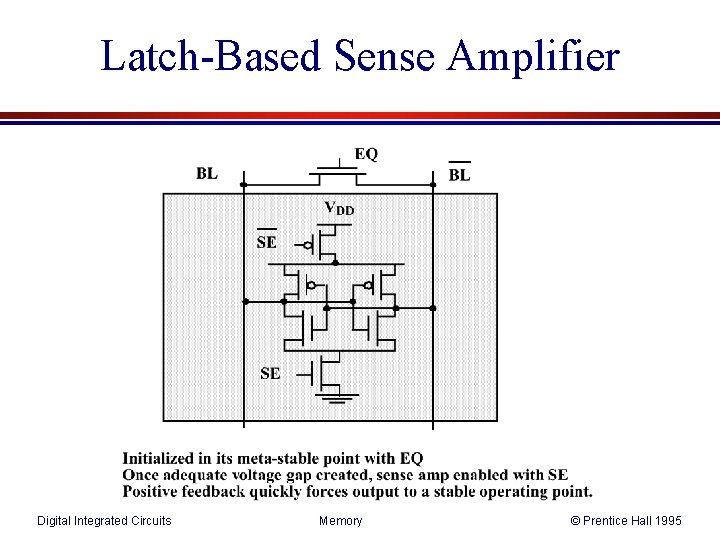

Latch-Based Sense Amplifier Digital Integrated Circuits Memory © Prentice Hall 1995

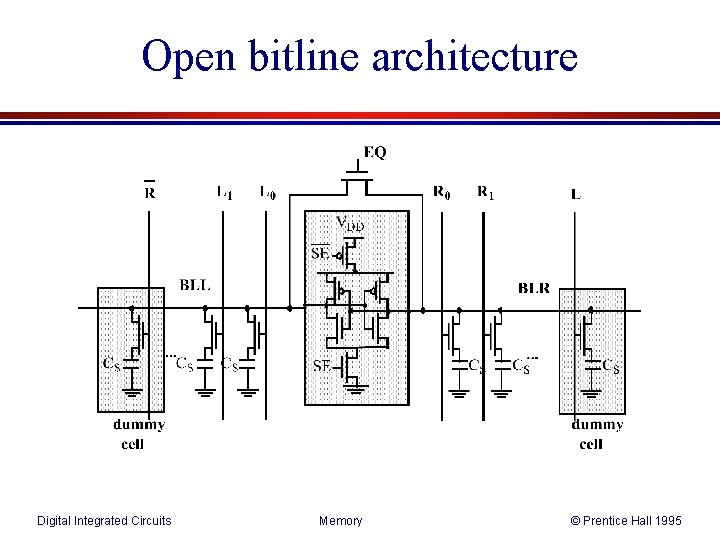

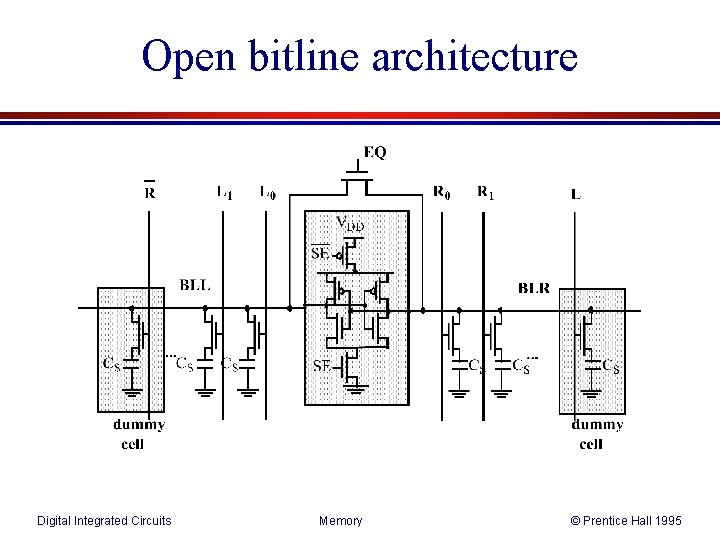

Open bitline architecture Digital Integrated Circuits Memory © Prentice Hall 1995

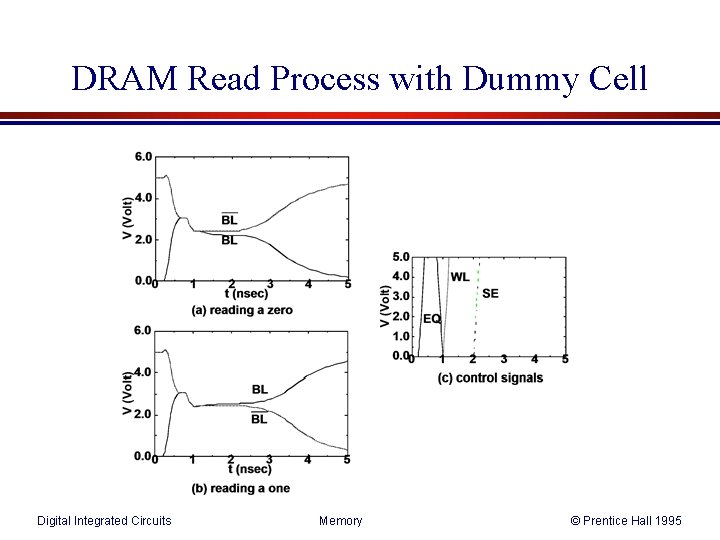

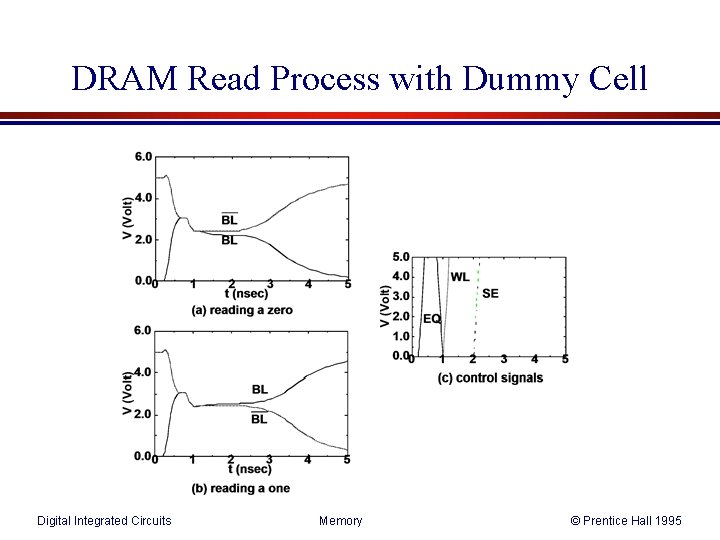

DRAM Read Process with Dummy Cell Digital Integrated Circuits Memory © Prentice Hall 1995

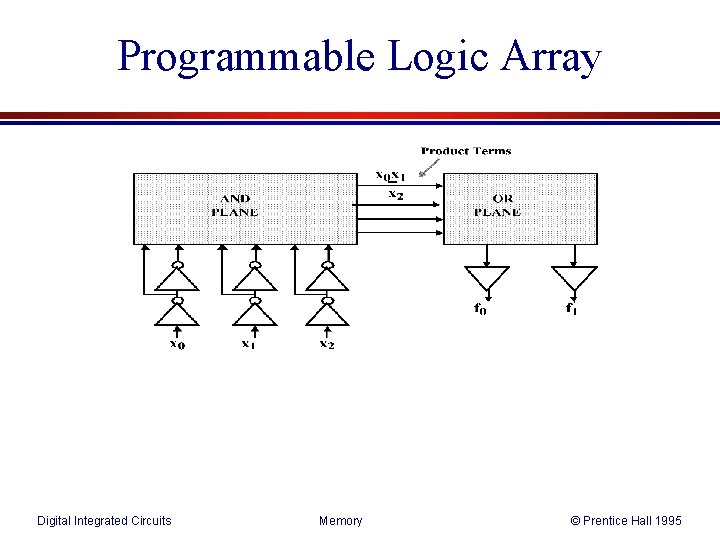

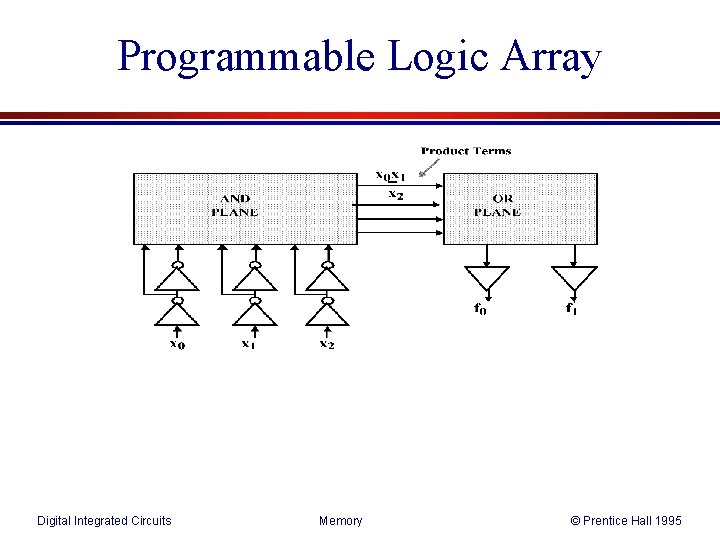

Programmable Logic Array Digital Integrated Circuits Memory © Prentice Hall 1995

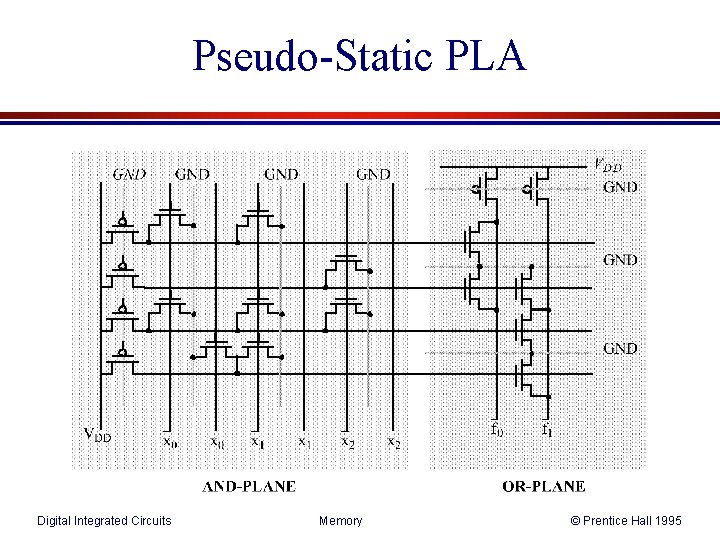

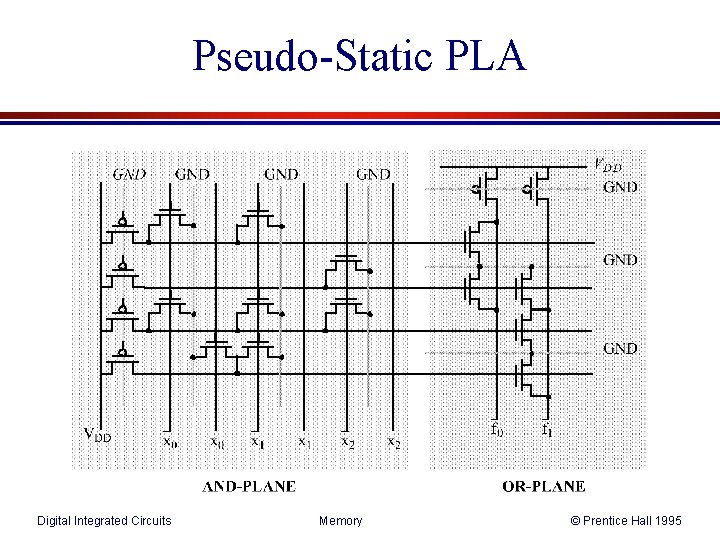

Pseudo-Static PLA Digital Integrated Circuits Memory © Prentice Hall 1995

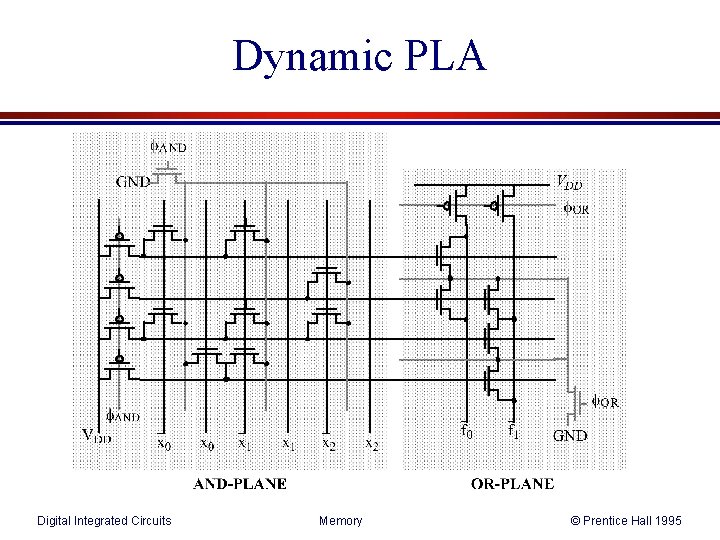

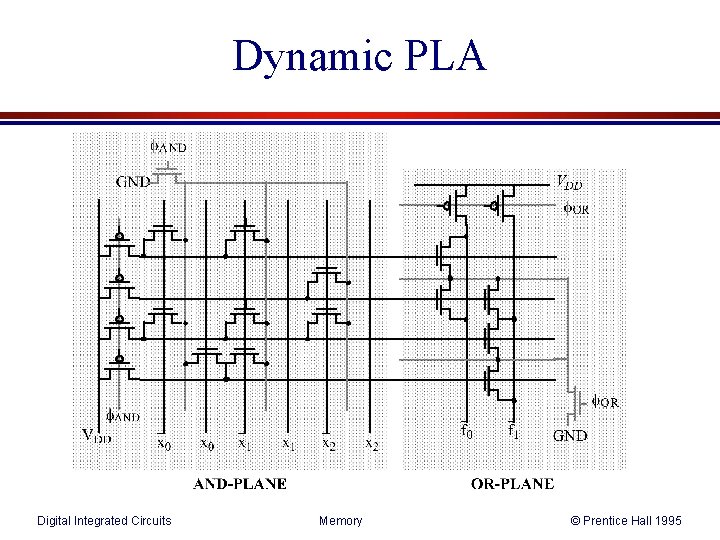

Dynamic PLA Digital Integrated Circuits Memory © Prentice Hall 1995

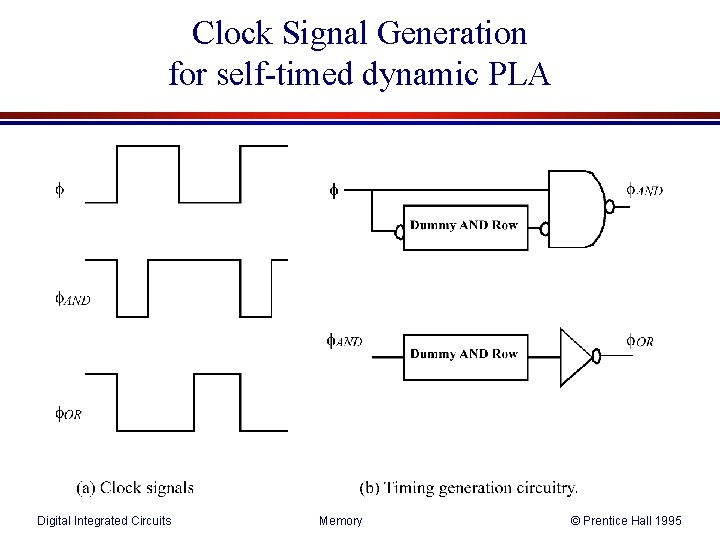

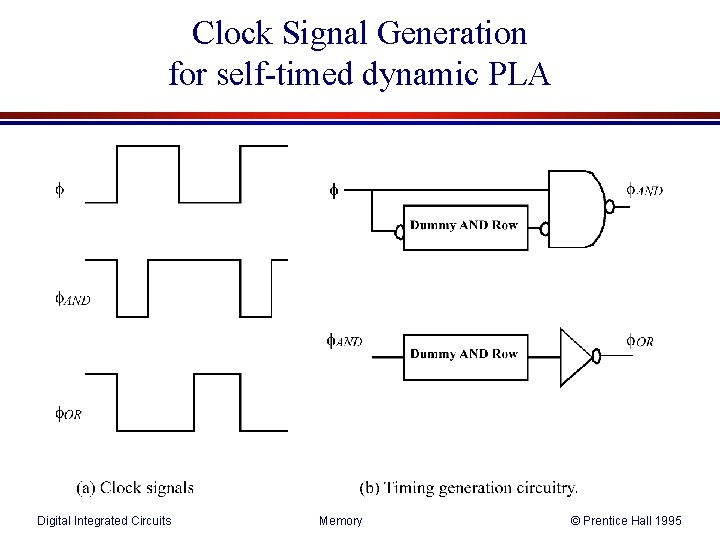

Clock Signal Generation for self-timed dynamic PLA Digital Integrated Circuits Memory © Prentice Hall 1995

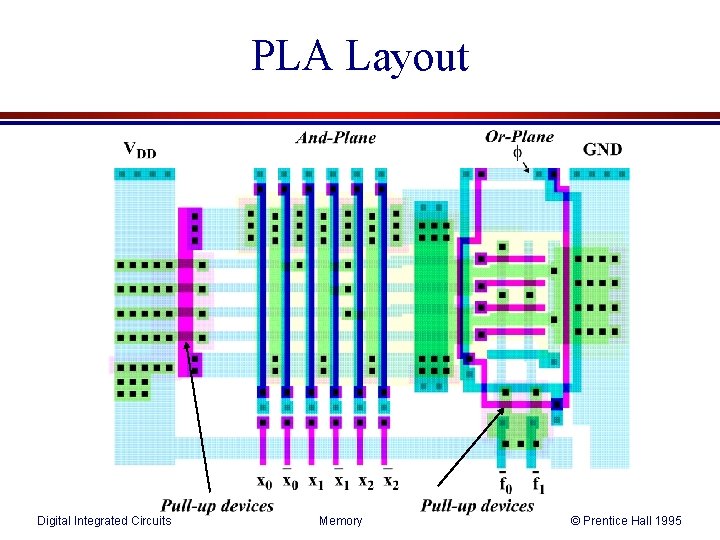

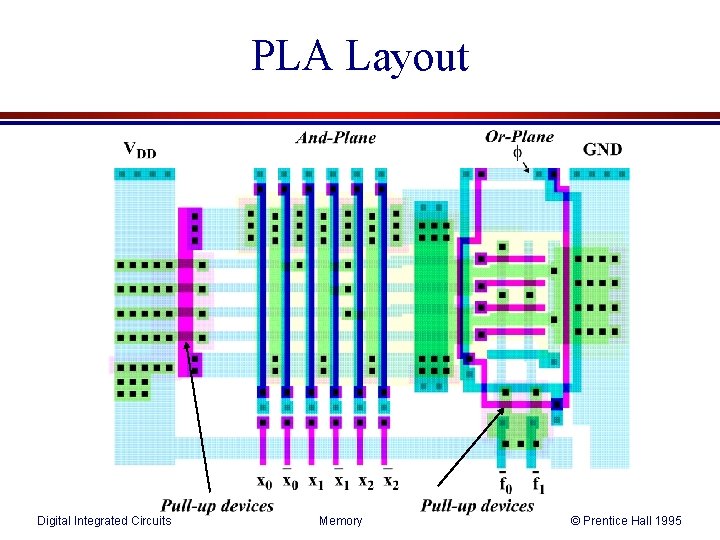

PLA Layout Digital Integrated Circuits Memory © Prentice Hall 1995

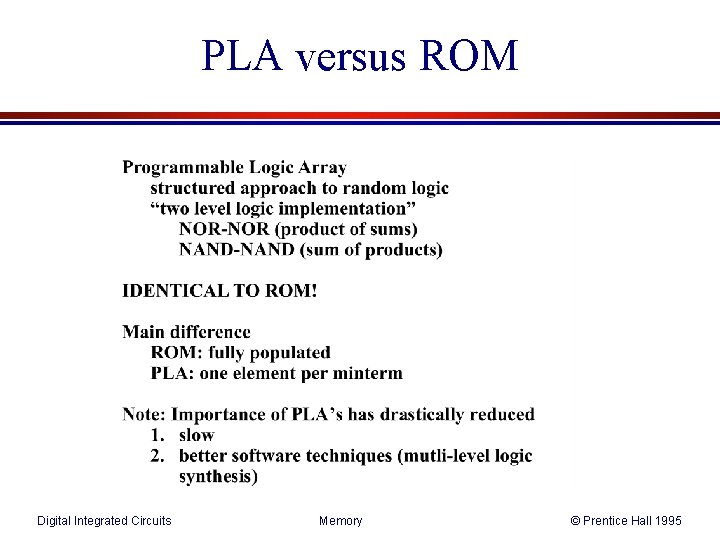

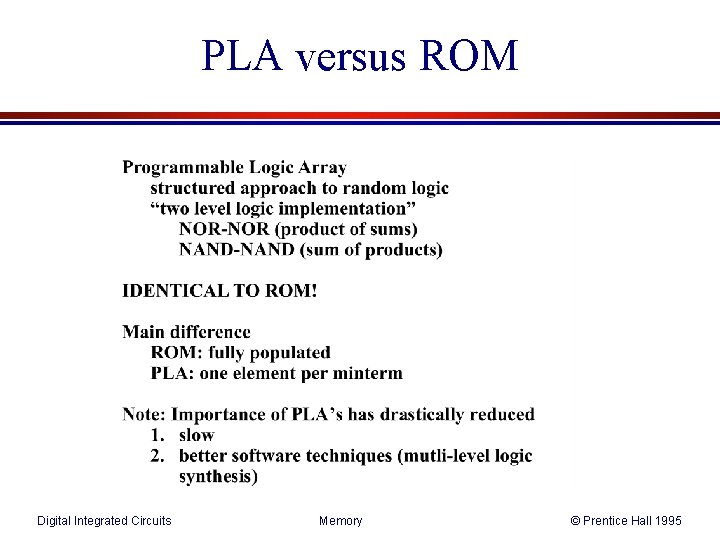

PLA versus ROM Digital Integrated Circuits Memory © Prentice Hall 1995

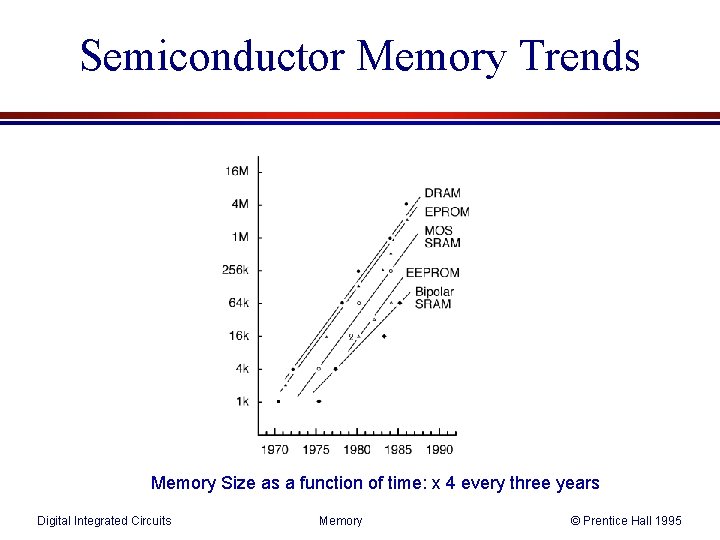

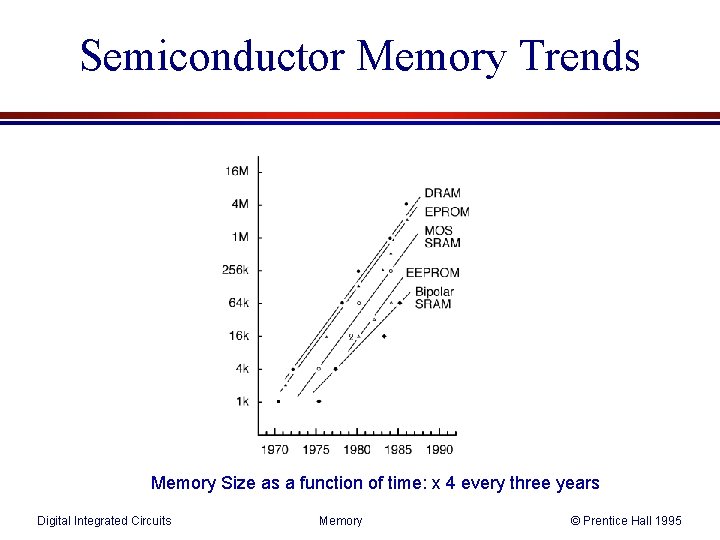

Semiconductor Memory Trends Memory Size as a function of time: x 4 every three years Digital Integrated Circuits Memory © Prentice Hall 1995

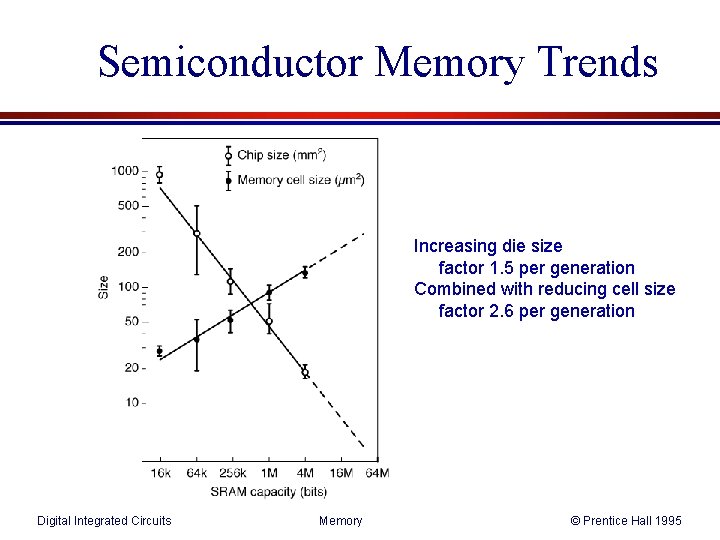

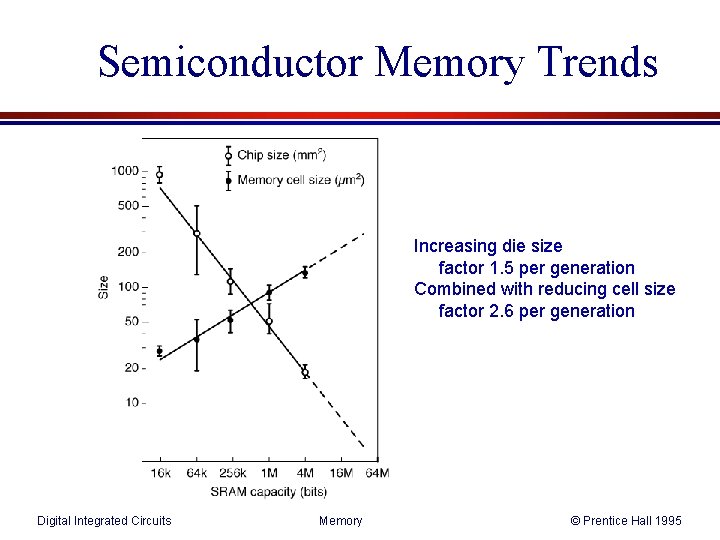

Semiconductor Memory Trends Increasing die size factor 1. 5 per generation Combined with reducing cell size factor 2. 6 per generation Digital Integrated Circuits Memory © Prentice Hall 1995

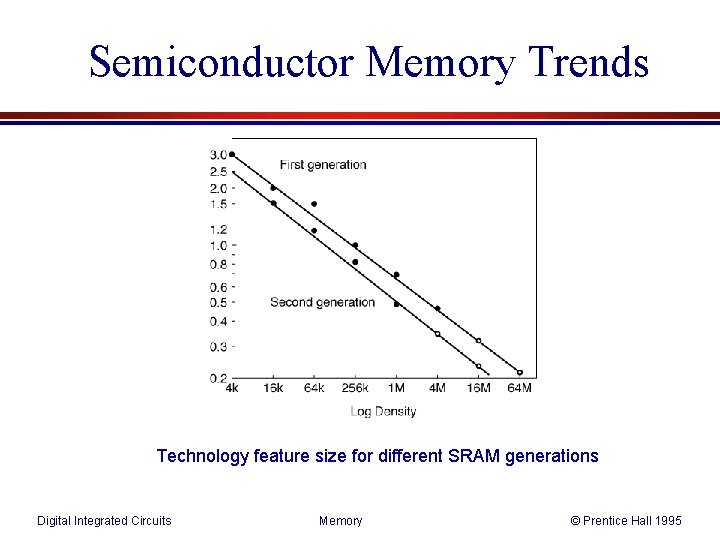

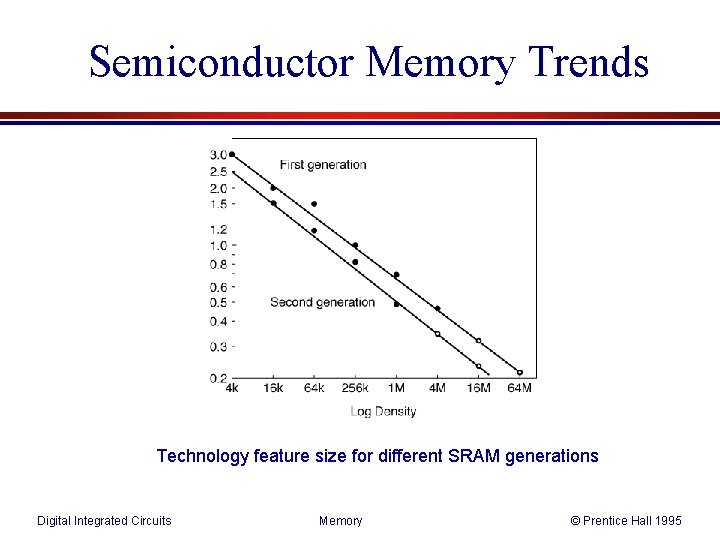

Semiconductor Memory Trends Technology feature size for different SRAM generations Digital Integrated Circuits Memory © Prentice Hall 1995