SelfTimed Systems Mitch Thornton Timing complexity growing in

- Slides: 18

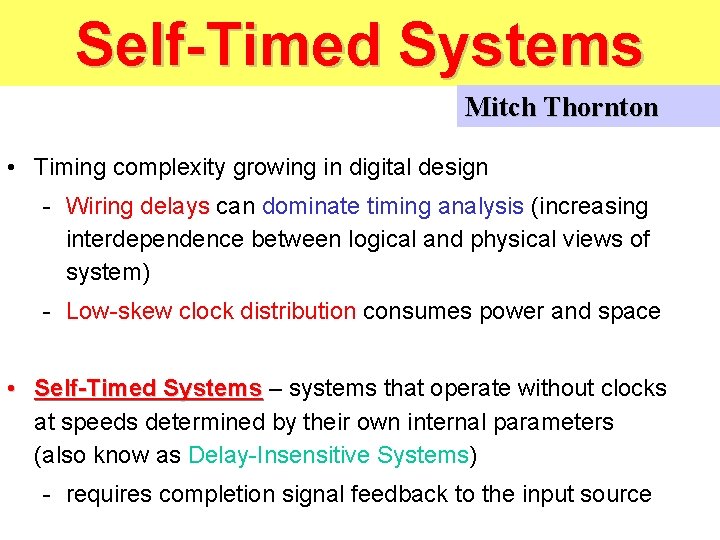

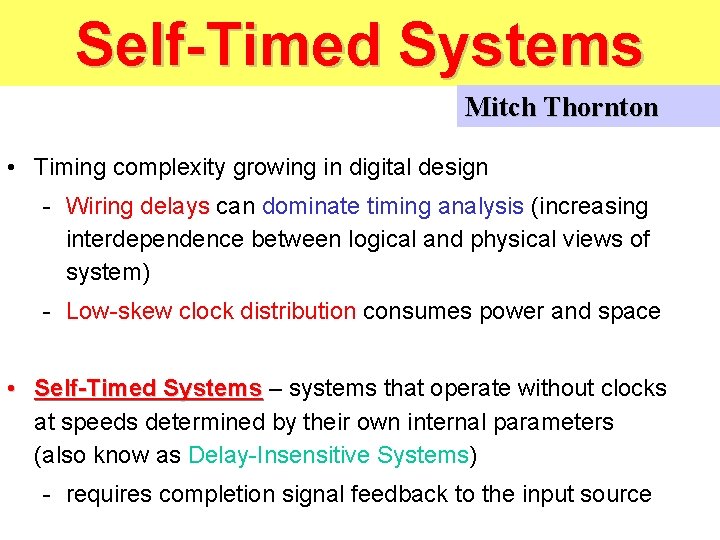

Self-Timed Systems Mitch Thornton • Timing complexity growing in digital design - Wiring delays can dominate timing analysis (increasing interdependence between logical and physical views of system) - Low-skew clock distribution consumes power and space • Self-Timed Systems – systems that operate without clocks at speeds determined by their own internal parameters (also know as Delay-Insensitive Systems) - requires completion signal feedback to the input source

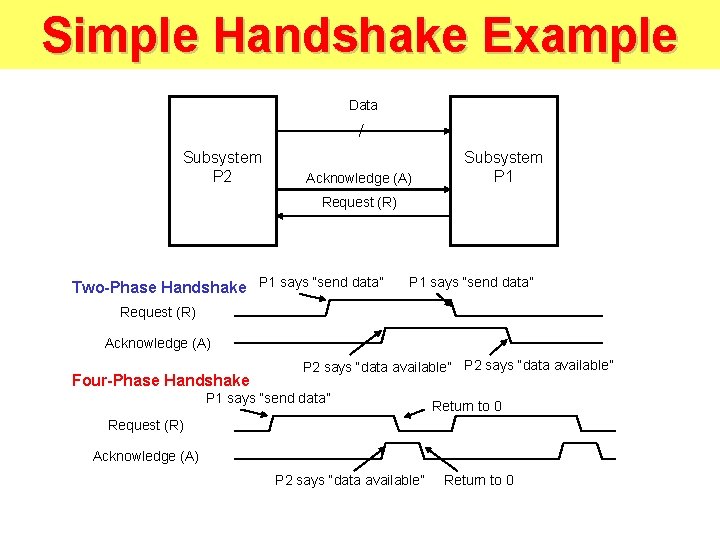

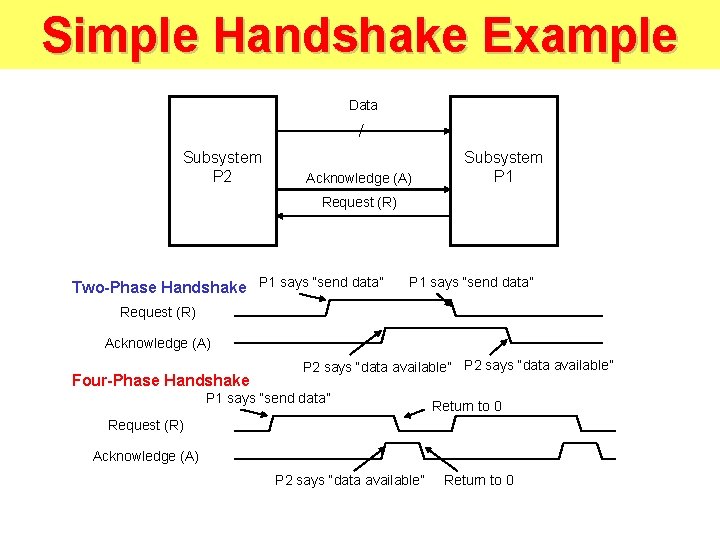

Simple Handshake Example Data Subsystem P 2 Acknowledge (A) Subsystem P 1 Request (R) Two-Phase Handshake P 1 says “send data” Request (R) Acknowledge (A) Four-Phase Handshake P 2 says “data available” P 1 says “send data” Return to 0 Request (R) Acknowledge (A) P 2 says “data available” Return to 0

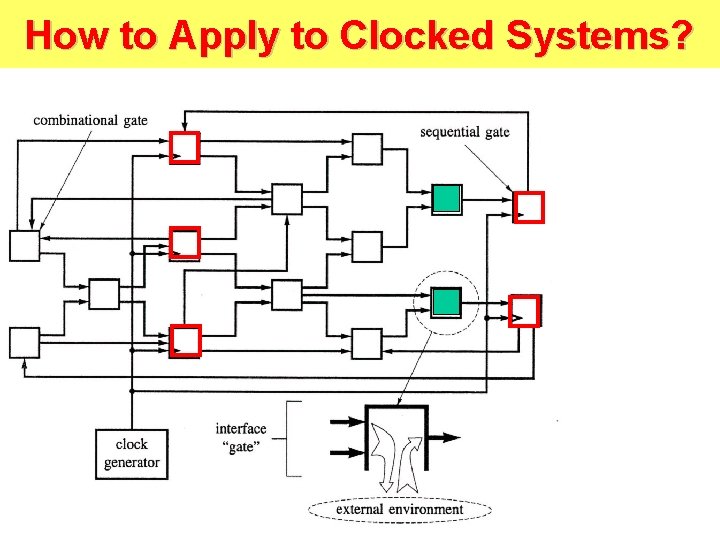

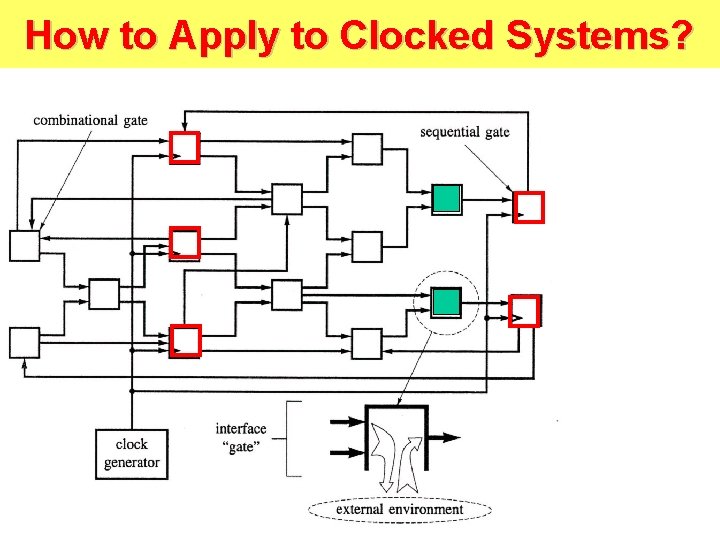

How to Apply to Clocked Systems?

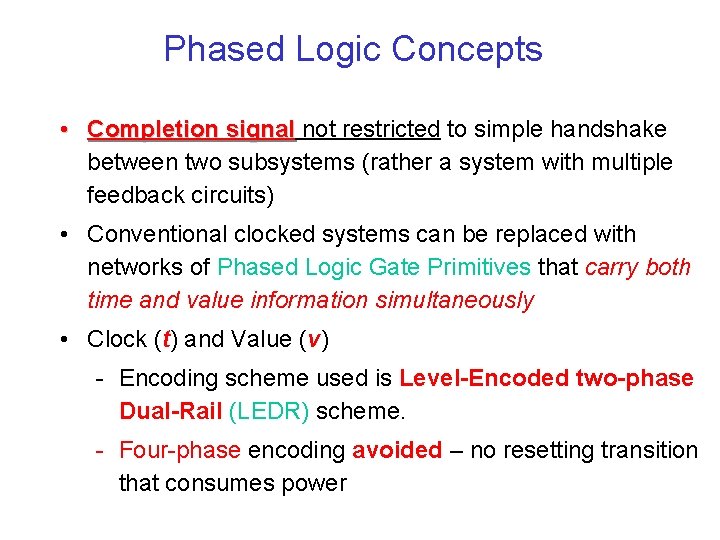

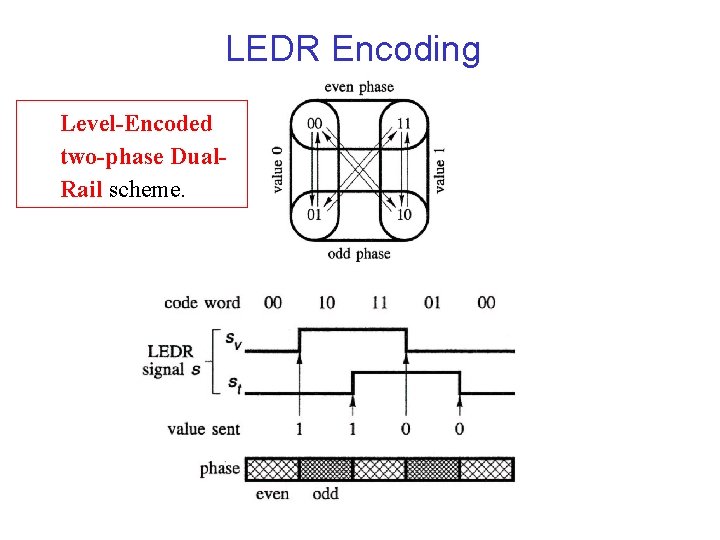

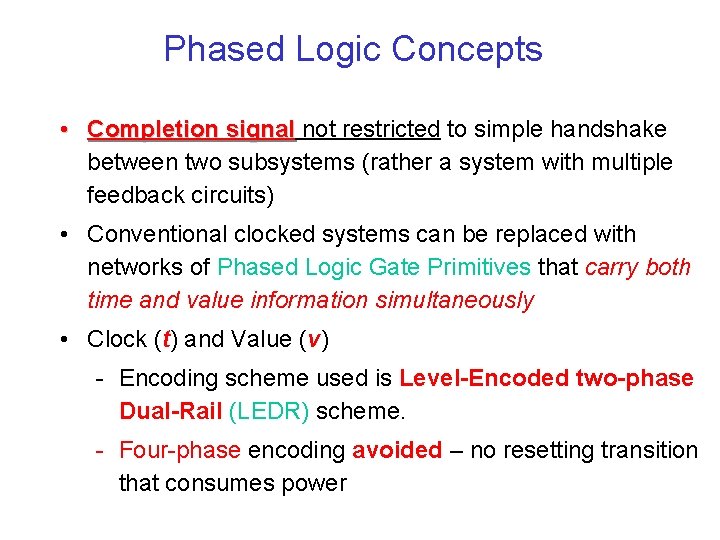

Phased Logic Concepts • Completion signal not restricted to simple handshake between two subsystems (rather a system with multiple feedback circuits) • Conventional clocked systems can be replaced with networks of Phased Logic Gate Primitives that carry both time and value information simultaneously • Clock (t) and Value (v) - Encoding scheme used is Level-Encoded two-phase Dual-Rail (LEDR) scheme. - Four-phase encoding avoided – no resetting transition that consumes power

LEDR Encoding Level-Encoded two-phase Dual. Rail scheme.

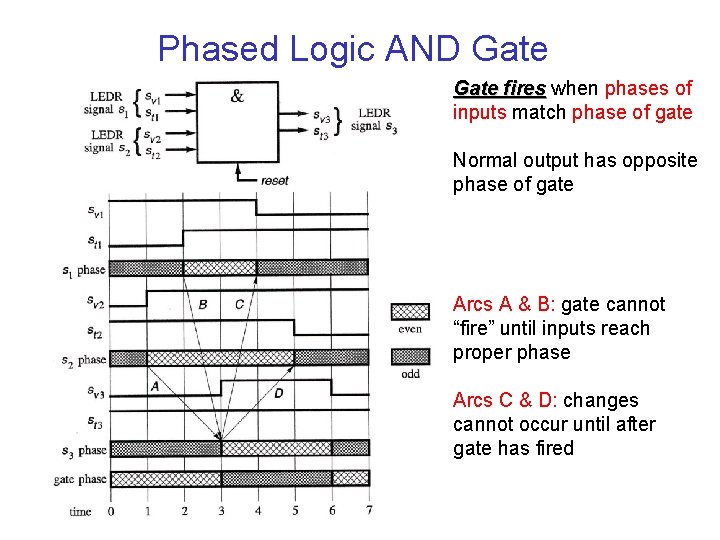

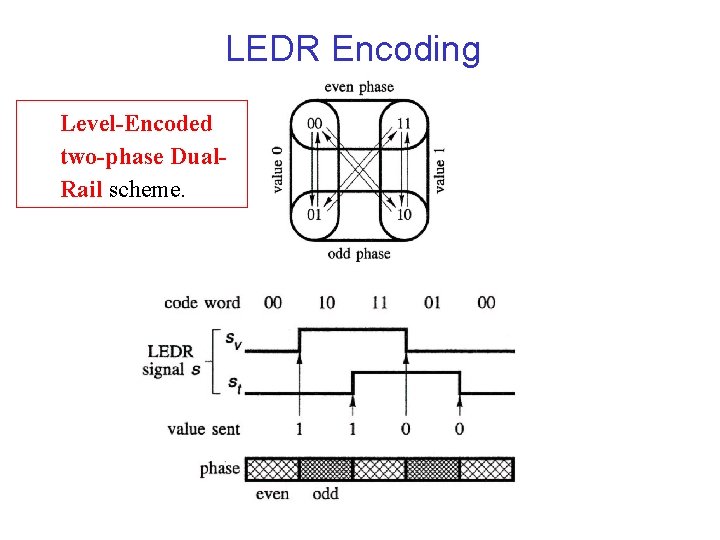

Phased Logic AND Gate fires when phases of inputs match phase of gate Normal output has opposite phase of gate Arcs A & B: gate cannot “fire” until inputs reach proper phase Arcs C & D: changes cannot occur until after gate has fired

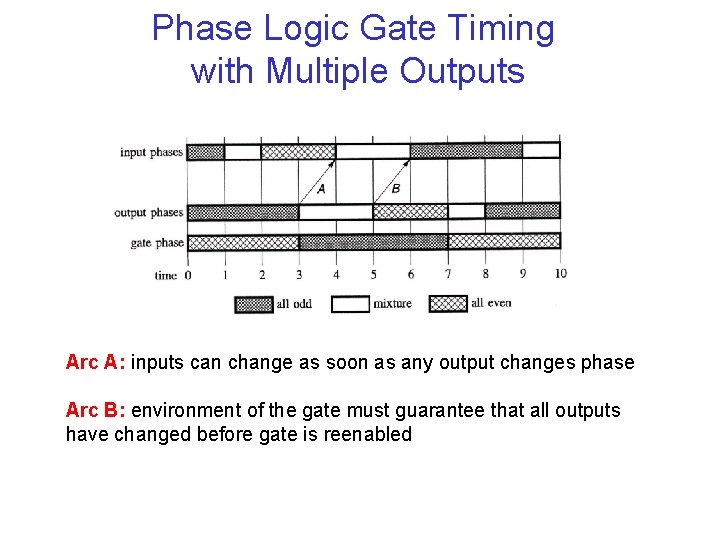

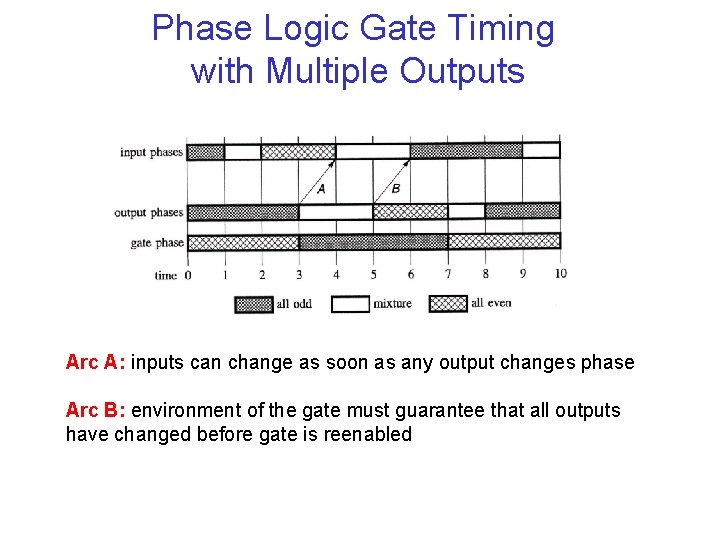

Phase Logic Gate Timing with Multiple Outputs Arc A: inputs can change as soon as any output changes phase Arc B: environment of the gate must guarantee that all outputs have changed before gate is reenabled

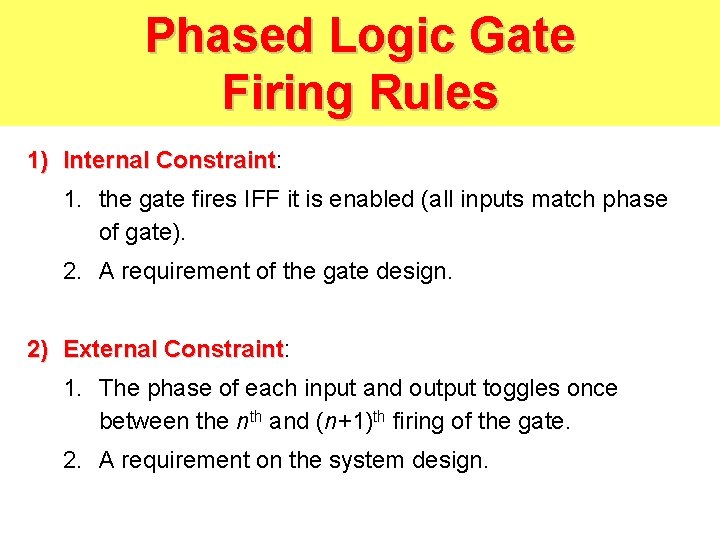

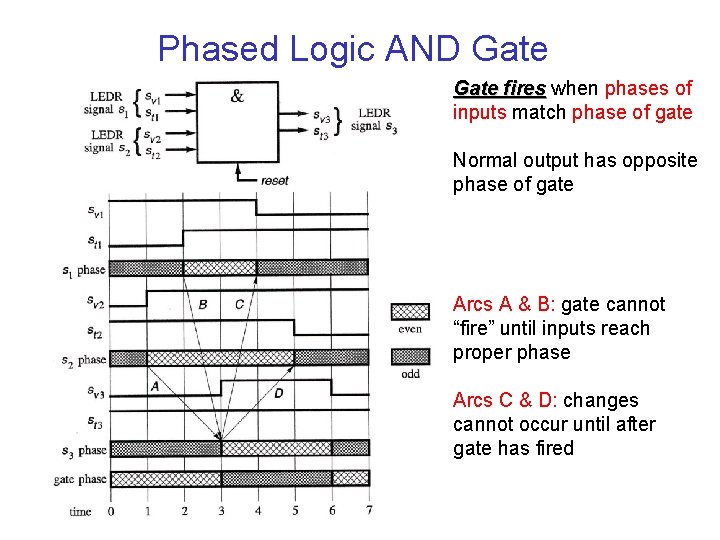

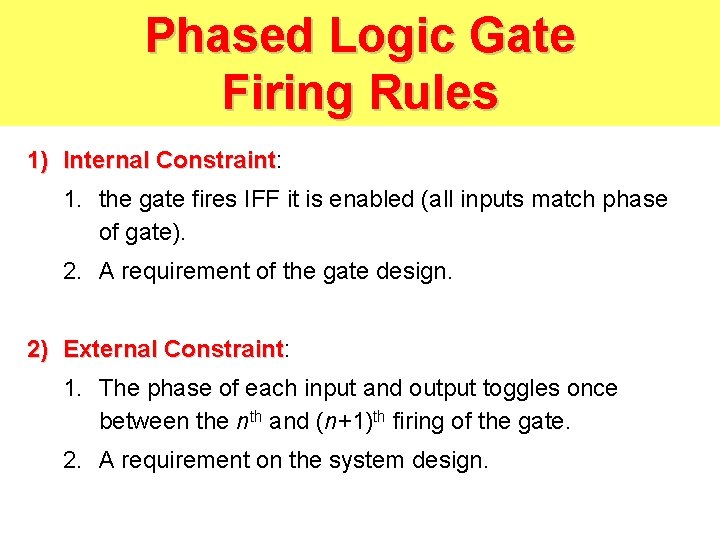

Phased Logic Gate Firing Rules 1) Internal Constraint: Constraint 1. the gate fires IFF it is enabled (all inputs match phase of gate). 2. A requirement of the gate design. 2) External Constraint: Constraint 1. The phase of each input and output toggles once between the nth and (n+1)th firing of the gate. 2. A requirement on the system design.

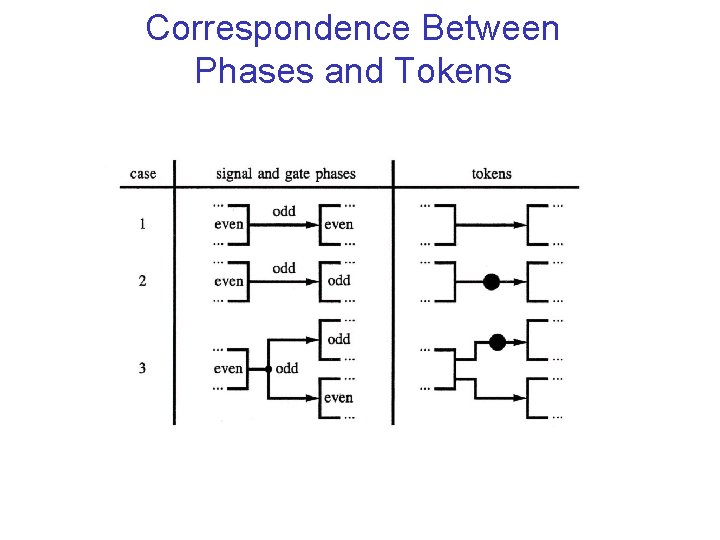

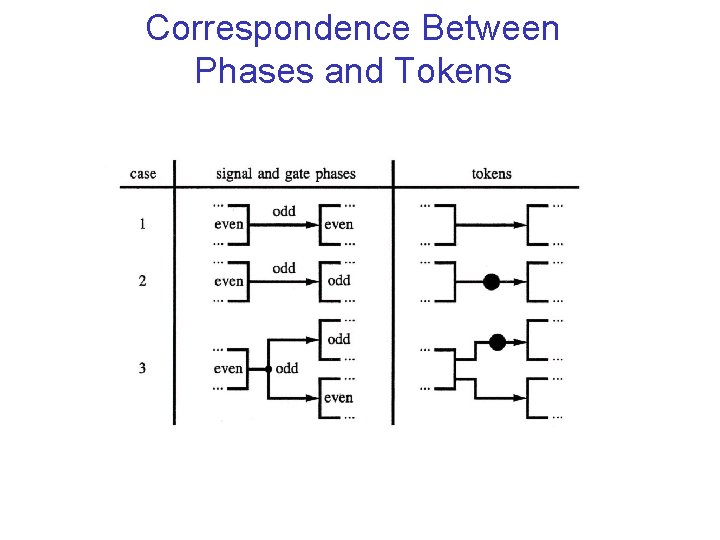

Correspondence Between Phases and Tokens

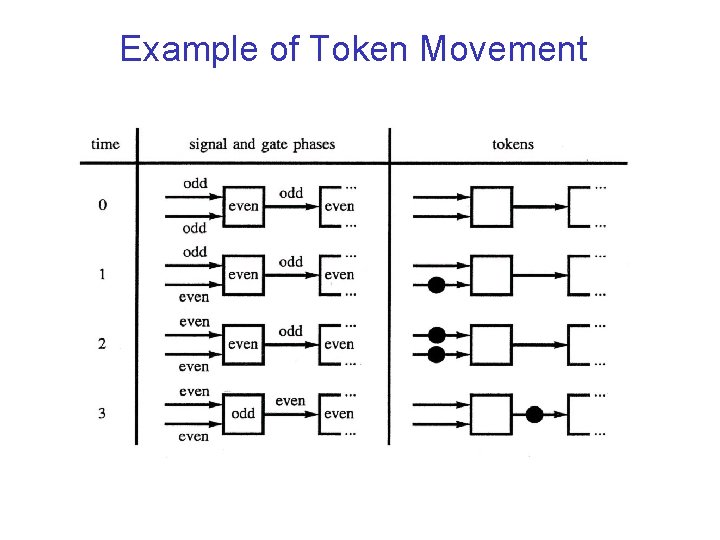

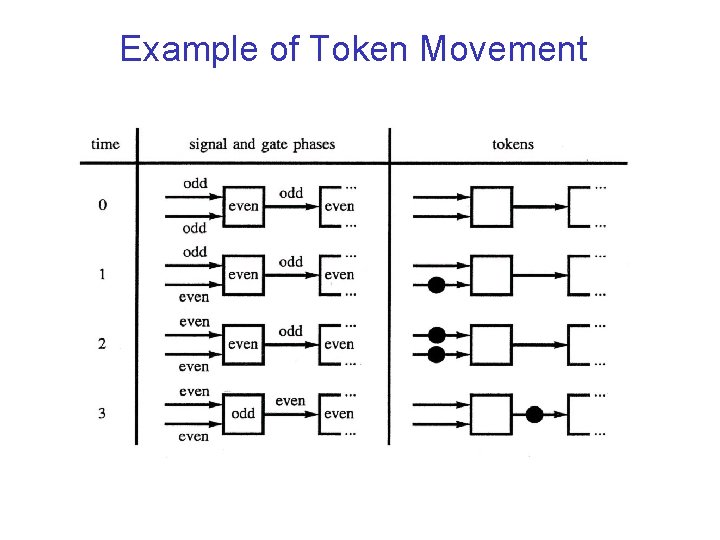

Example of Token Movement

Initial Token Markings

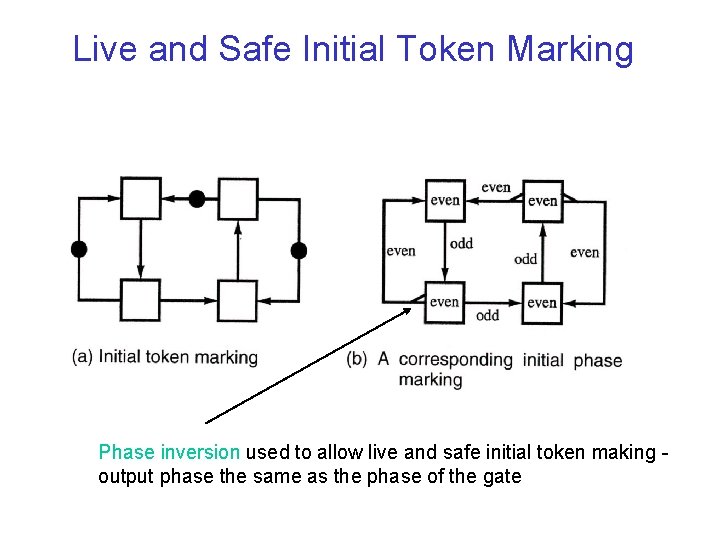

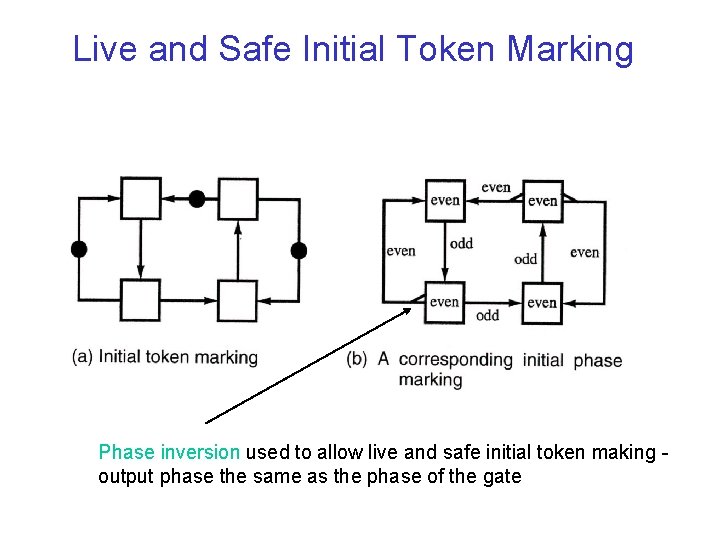

Live and Safe Initial Token Marking Phase inversion used to allow live and safe initial token making output phase the same as the phase of the gate

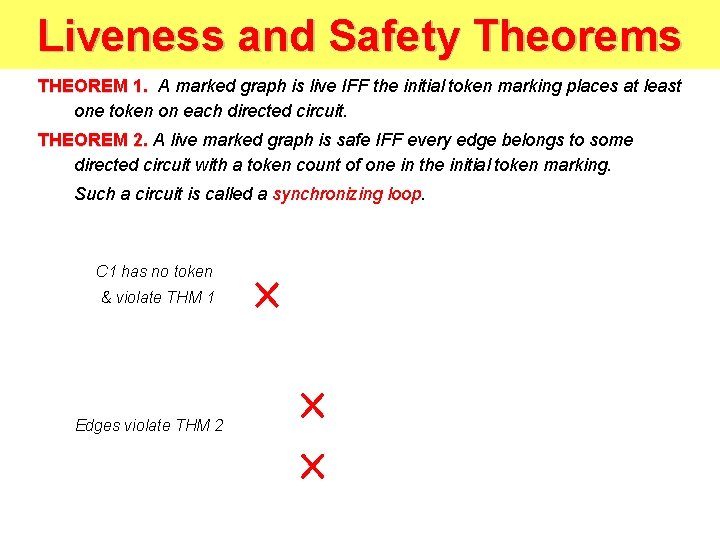

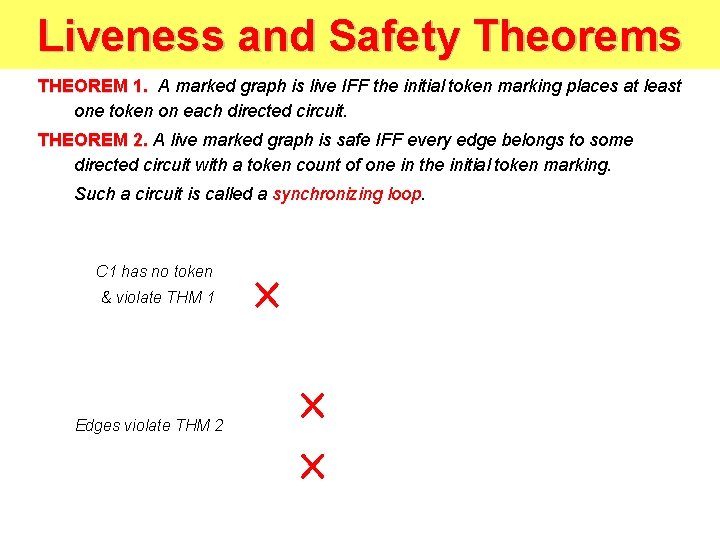

Liveness and Safety Theorems THEOREM 1. A marked graph is live IFF the initial token marking places at least one token on each directed circuit. THEOREM 2. A live marked graph is safe IFF every edge belongs to some directed circuit with a token count of one in the initial token marking. Such a circuit is called a synchronizing loop. C 1 has no token & violate THM 1 Edges violate THM 2

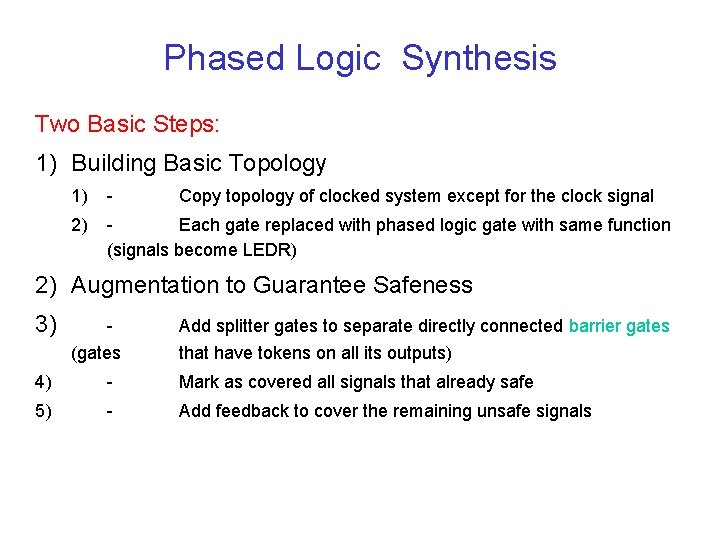

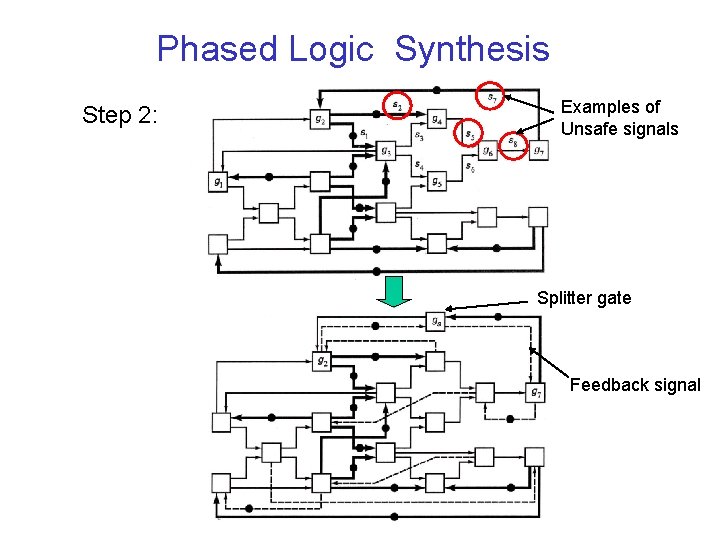

Phased Logic Synthesis Two Basic Steps: 1) Building Basic Topology 1) - 2) Each gate replaced with phased logic gate with same function (signals become LEDR) Copy topology of clocked system except for the clock signal 2) Augmentation to Guarantee Safeness 3) (gates Add splitter gates to separate directly connected barrier gates that have tokens on all its outputs) 4) - Mark as covered all signals that already safe 5) - Add feedback to cover the remaining unsafe signals

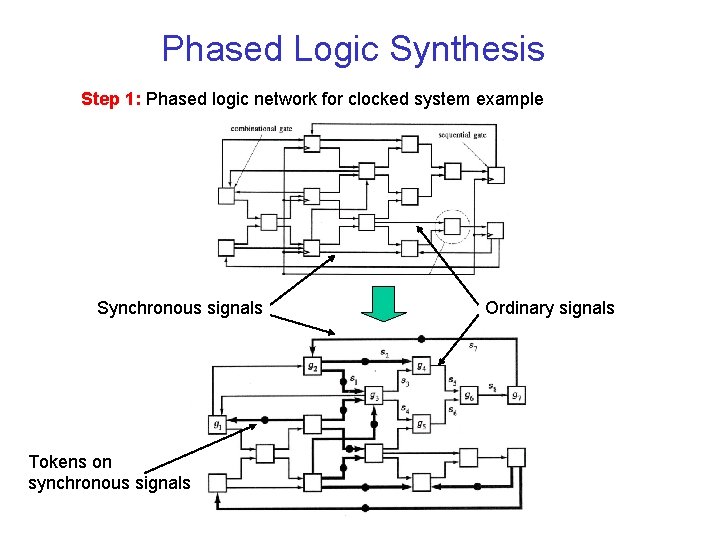

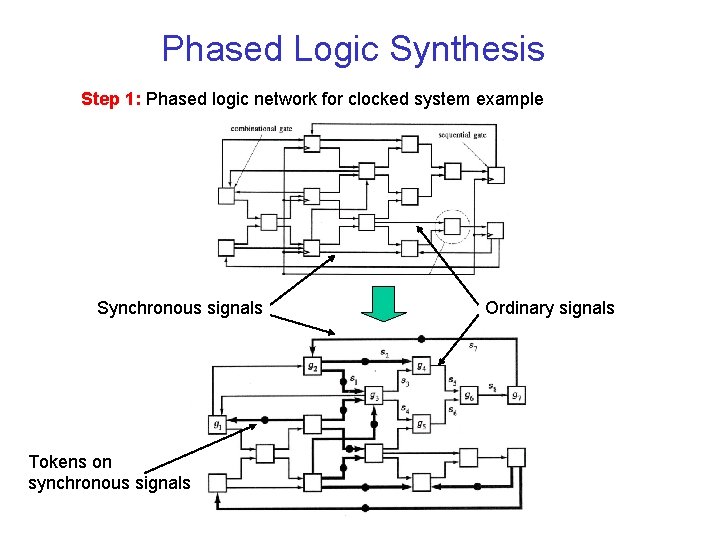

Phased Logic Synthesis Step 1: Phased logic network for clocked system example Synchronous signals Tokens on synchronous signals Ordinary signals

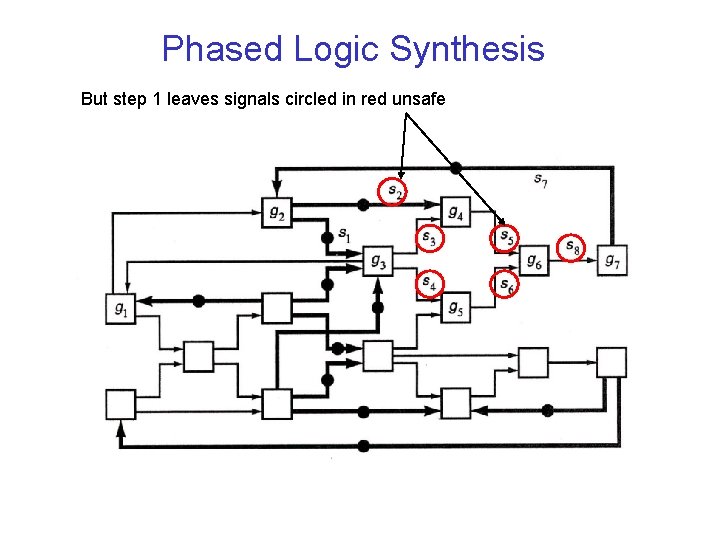

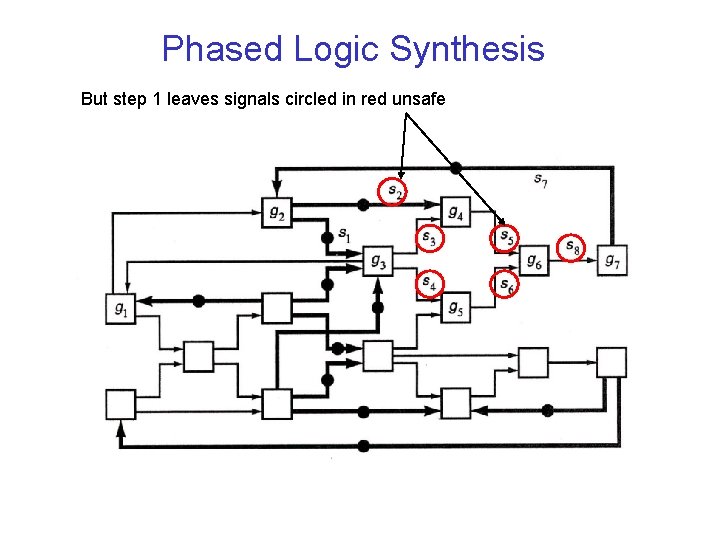

Phased Logic Synthesis But step 1 leaves signals circled in red unsafe

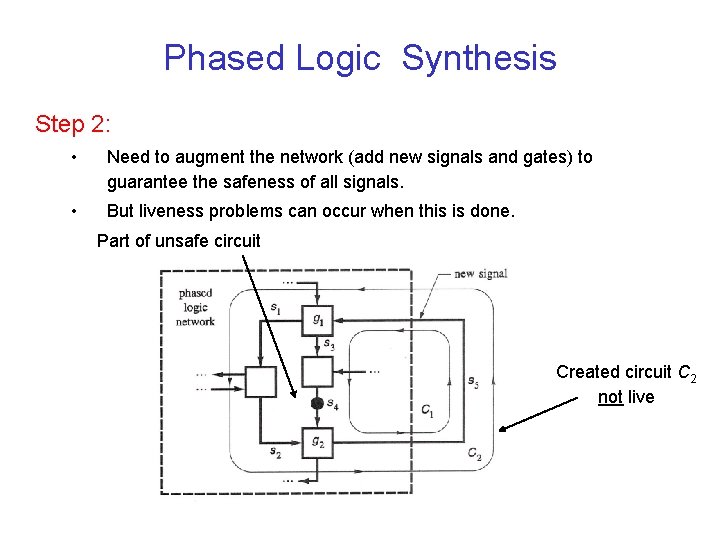

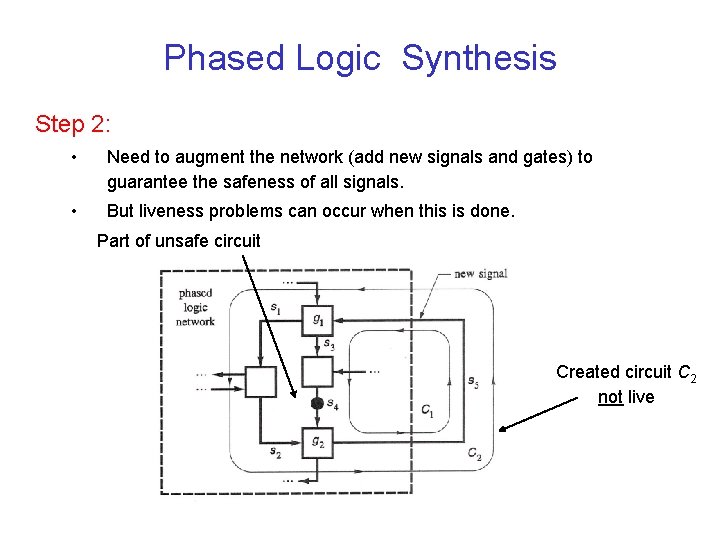

Phased Logic Synthesis Step 2: • Need to augment the network (add new signals and gates) to guarantee the safeness of all signals. • But liveness problems can occur when this is done. Part of unsafe circuit Created circuit C 2 not live

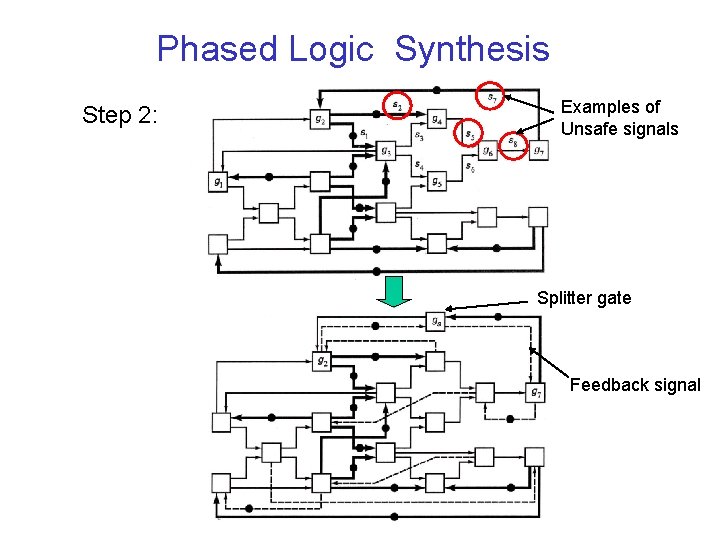

Phased Logic Synthesis Step 2: Examples of Unsafe signals Splitter gate Feedback signal