Selected information on Altera FPGAs and Software n

- Slides: 31

Selected information on Altera FPGAs and Software n They have very good University program n Donated 4 boards to PSU for free n Help with projects © 2001 Altera Corporation ()

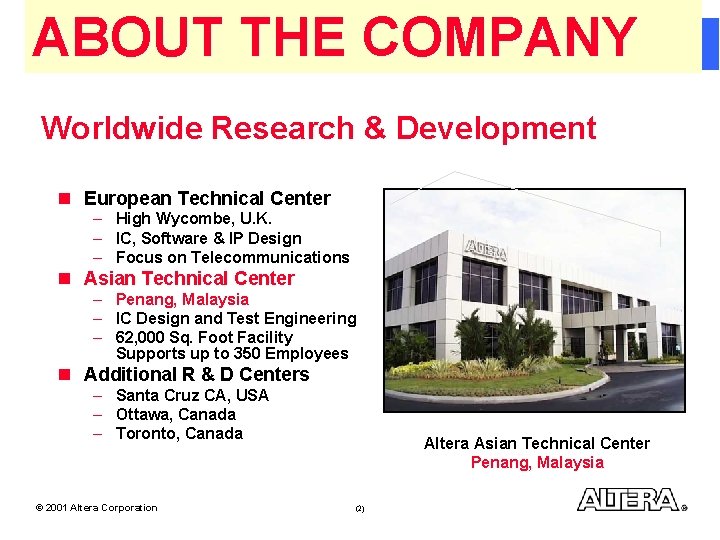

ABOUT THE COMPANY Worldwide Research & Development n European Technical Center – High Wycombe, U. K. – IC, Software & IP Design – Focus on Telecommunications n Asian Technical Center – Penang, Malaysia – IC Design and Test Engineering – 62, 000 Sq. Foot Facility Supports up to 350 Employees n Additional R & D Centers – Santa Cruz CA, USA – Ottawa, Canada – Toronto, Canada © 2001 Altera Corporation Altera Asian Technical Center Penang, Malaysia (2)

Worldwide Manufacturing Capacity n World-Class Wafer Foundries – Sharp & TSMC – Multiple Foundries in Asia and North America – Ensures Supply Continuity n State-of-the-Art Development n Partnership with TSMC – 0. 42 -µ, 0. 30 -µ, 0. 22 -µ and 0. 18 -µ Processes Released to Production – 0. 15 -µ and 0. 13 -µ Processes with Copper Interconnect – 12 inch Wafer Development Underway © 2001 Altera Corporation (3)

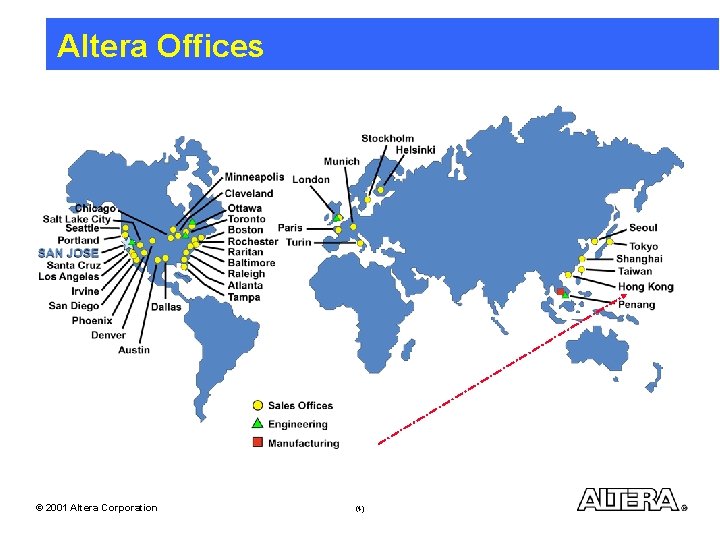

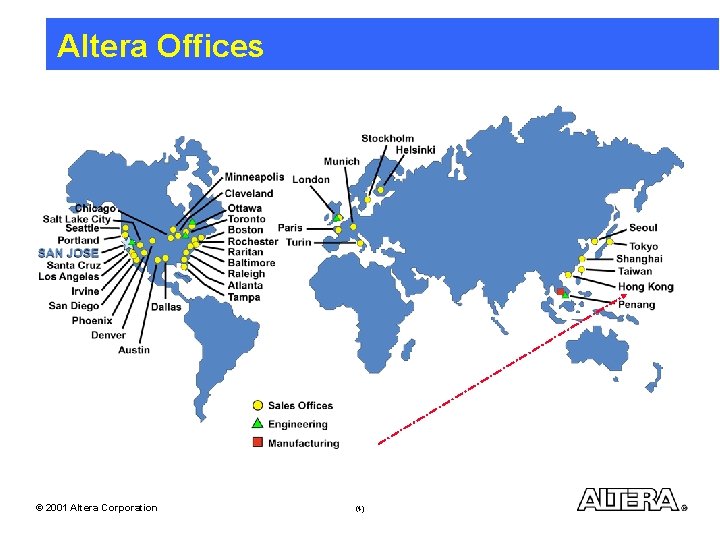

Altera Offices © 2001 Altera Corporation (4)

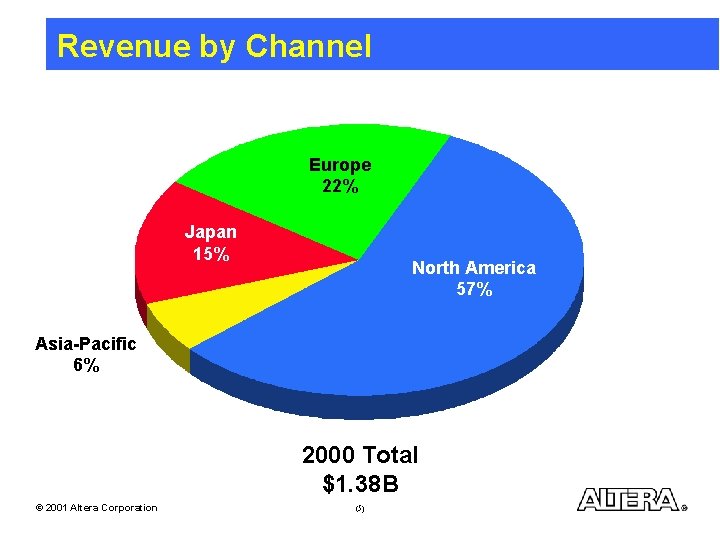

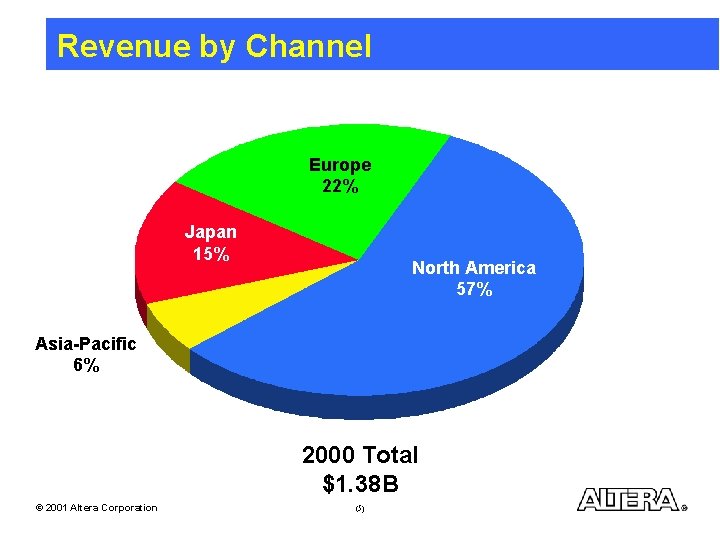

Revenue by Channel Europe 22% Japan 15% North America 57% Asia-Pacific 6% 2000 Total $1. 38 B © 2001 Altera Corporation (5)

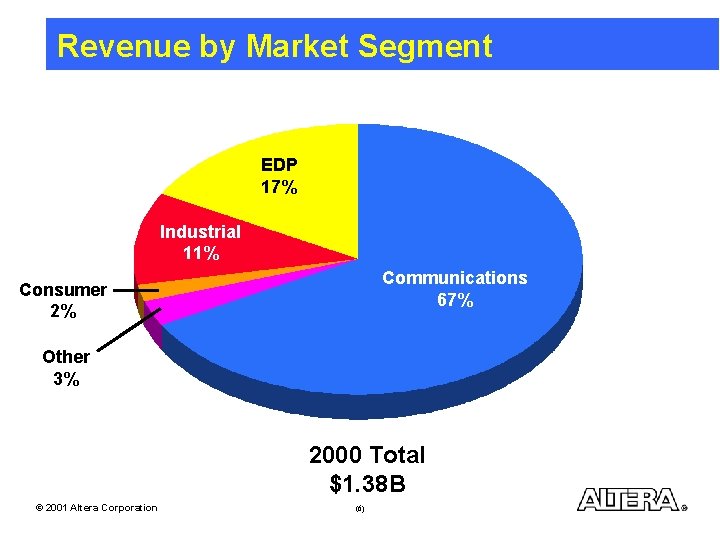

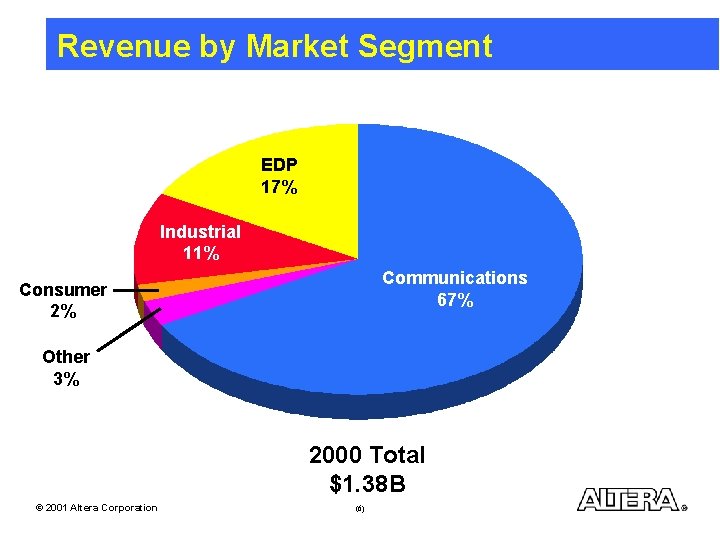

Revenue by Market Segment EDP 17% Industrial 11% Communications 67% Consumer 2% Other 3% 2000 Total $1. 38 B © 2001 Altera Corporation (6)

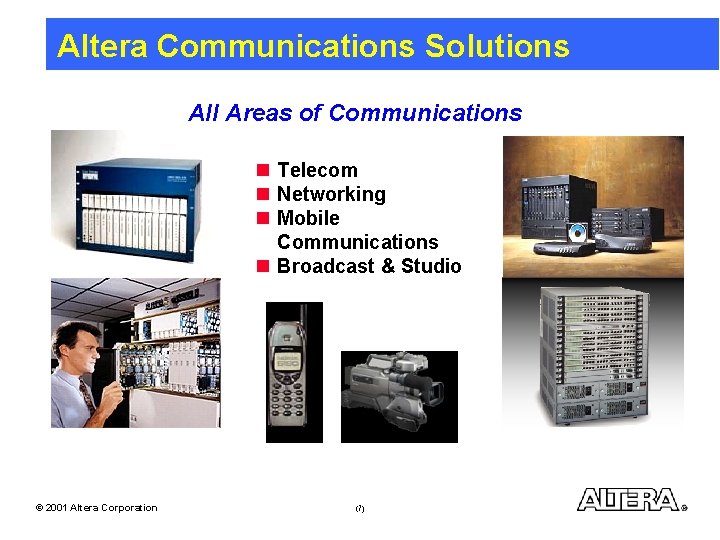

Altera Communications Solutions All Areas of Communications n Telecom n Networking n Mobile Communications n Broadcast & Studio © 2001 Altera Corporation (7)

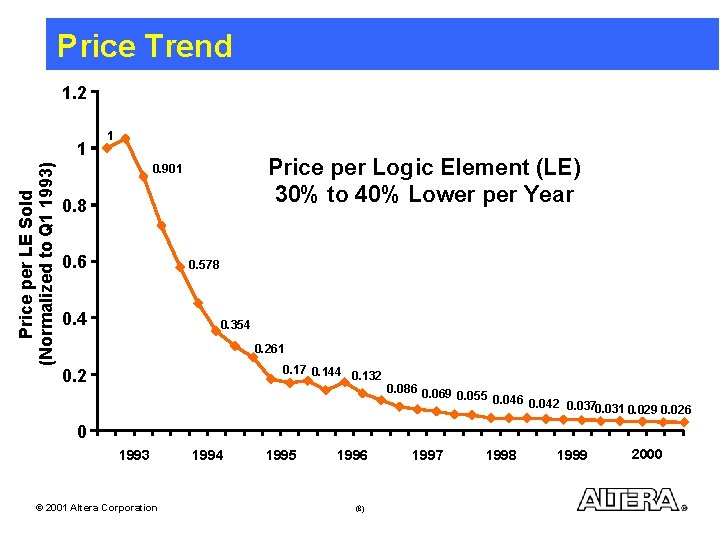

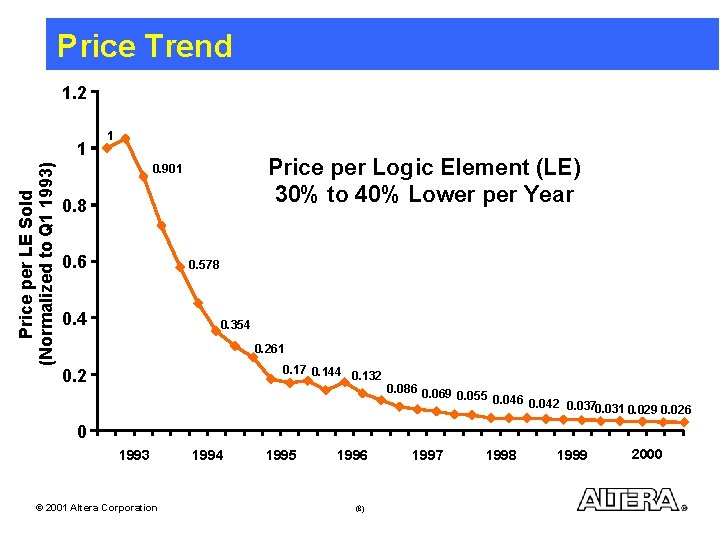

Price Trend 1. 2 Price per LE Sold (Normalized to Q 1 1993) 1 1 Price per Logic Element (LE) 30% to 40% Lower per Year 0. 901 0. 8 0. 6 0. 578 0. 4 0. 354 0. 261 0. 17 0. 144 0. 132 0. 086 0. 069 0. 055 0. 046 0. 042 0. 0370. 031 0. 029 0. 026 0 1993 © 2001 Altera Corporation 1994 1995 1996 (8) 1997 1998 1999 2000

Some of Altera’s FPGA architectures © 2001 Altera Corporation (9)

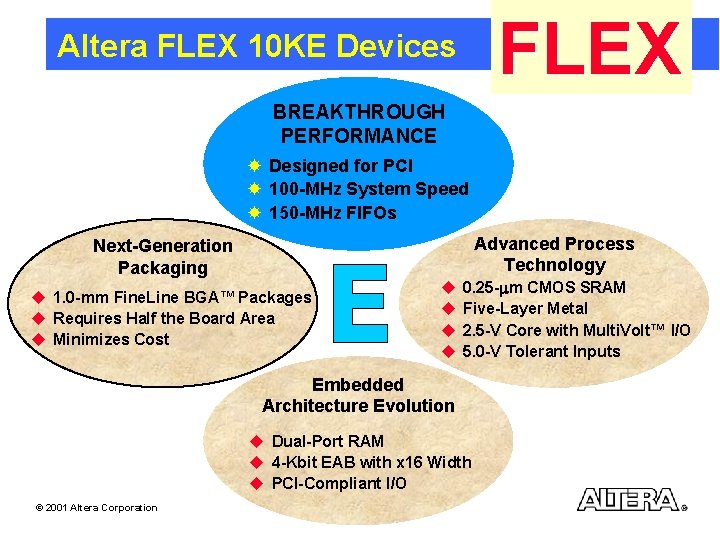

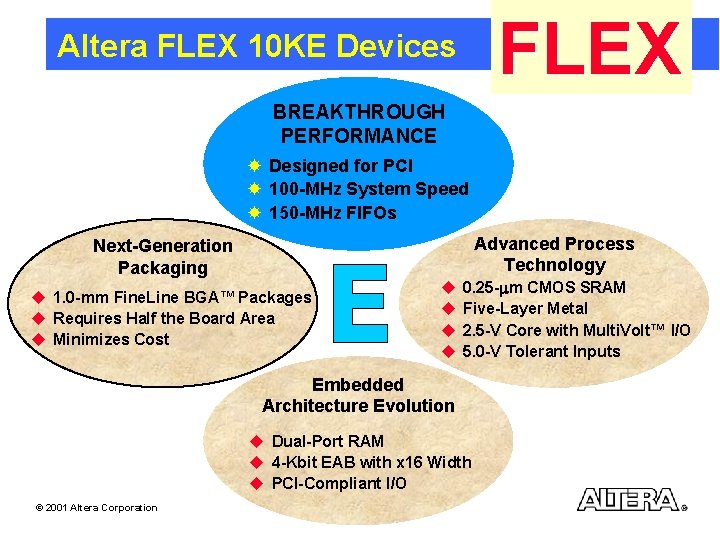

FLEX Altera FLEX 10 KE Devices BREAKTHROUGH PERFORMANCE Designed for PCI 100 -MHz System Speed 150 -MHz FIFOs Advanced Process Technology Next-Generation Packaging u u u 1. 0 -mm Fine. Line BGA™ Packages u Requires Half the Board Area u Minimizes Cost 0. 25 -mm CMOS SRAM Five-Layer Metal 2. 5 -V Core with Multi. Volt™ I/O 5. 0 -V Tolerant Inputs Embedded Architecture Evolution u Dual-Port RAM u 4 -Kbit EAB with x 16 Width u PCI-Compliant I/O © 2001 Altera Corporation (10)

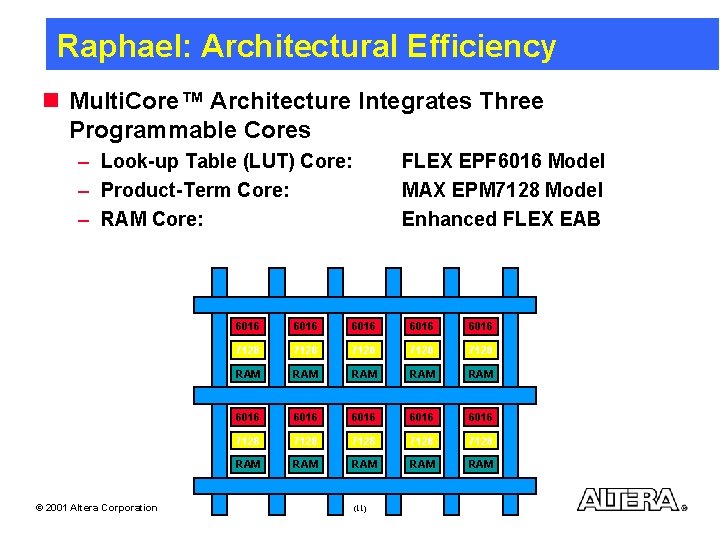

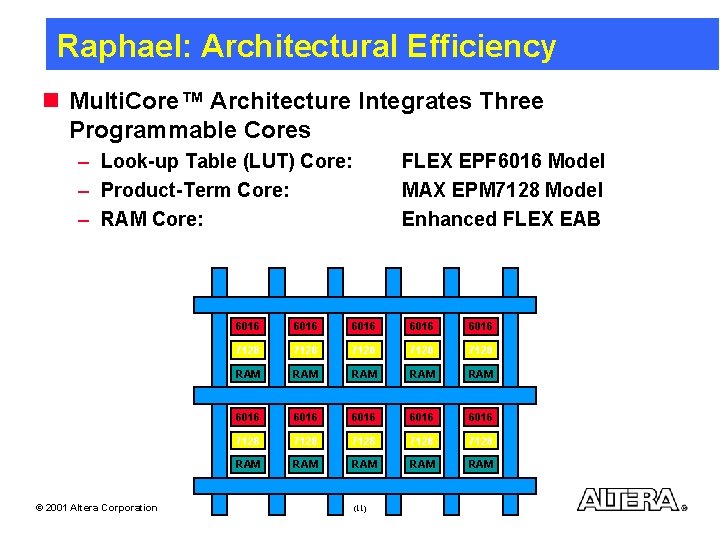

Raphael: Architectural Efficiency n Multi. Core™ Architecture Integrates Three Programmable Cores – Look-up Table (LUT) Core: – Product-Term Core: – RAM Core: © 2001 Altera Corporation FLEX EPF 6016 Model MAX EPM 7128 Model Enhanced FLEX EAB 6016 6016 6016 7128 7128 7128 RAM RAM RAM (11)

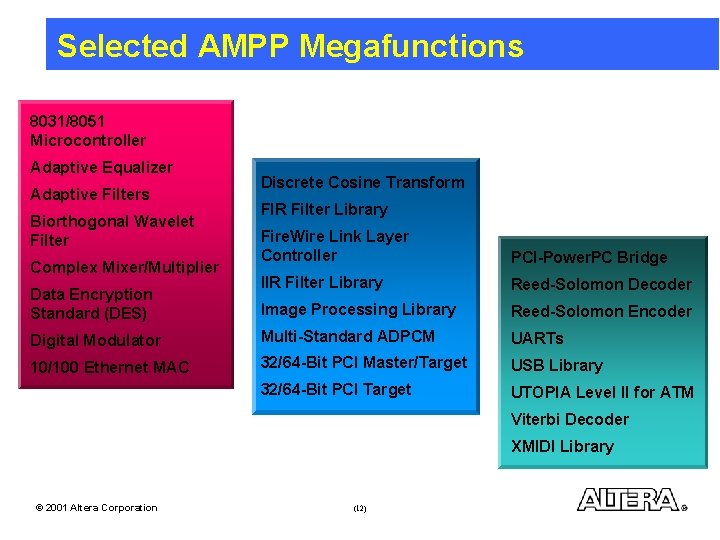

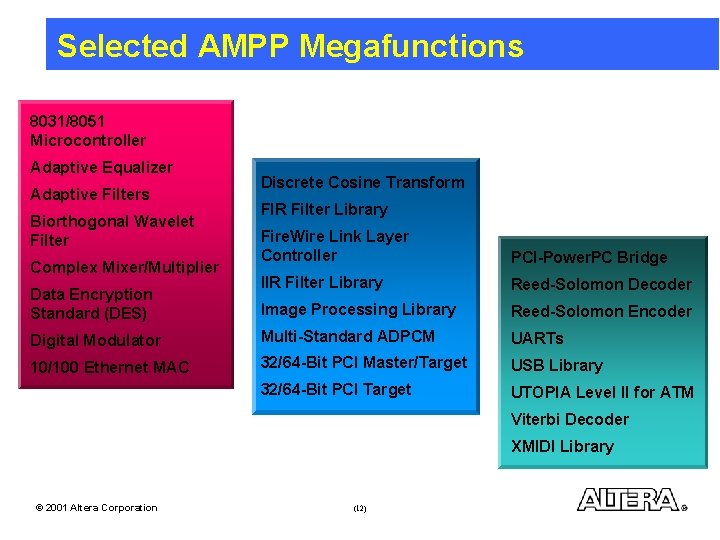

Selected AMPP Megafunctions 8031/8051 Microcontroller Adaptive Equalizer Adaptive Filters Biorthogonal Wavelet Filter Discrete Cosine Transform FIR Filter Library Fire. Wire Link Layer Controller PCI-Power. PC Bridge IIR Filter Library Reed-Solomon Decoder Image Processing Library Reed-Solomon Encoder Digital Modulator Multi-Standard ADPCM UARTs 10/100 Ethernet MAC 32/64 -Bit PCI Master/Target USB Library 32/64 -Bit PCI Target UTOPIA Level II for ATM Complex Mixer/Multiplier Data Encryption Standard (DES) Viterbi Decoder XMIDI Library © 2001 Altera Corporation (12)

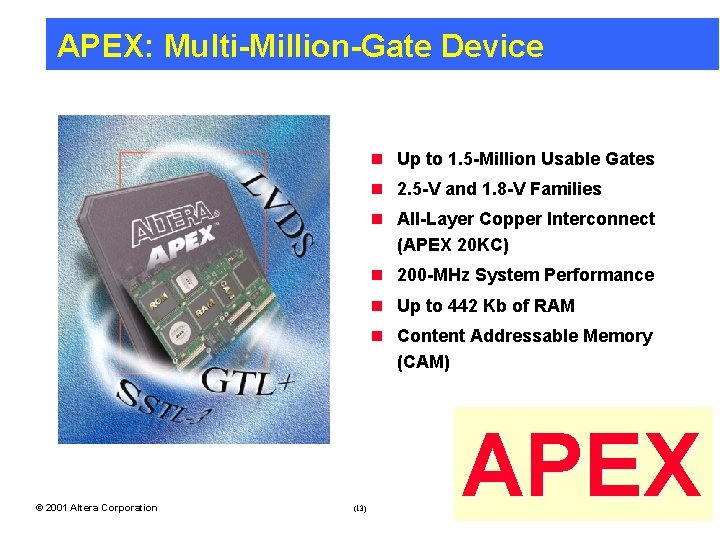

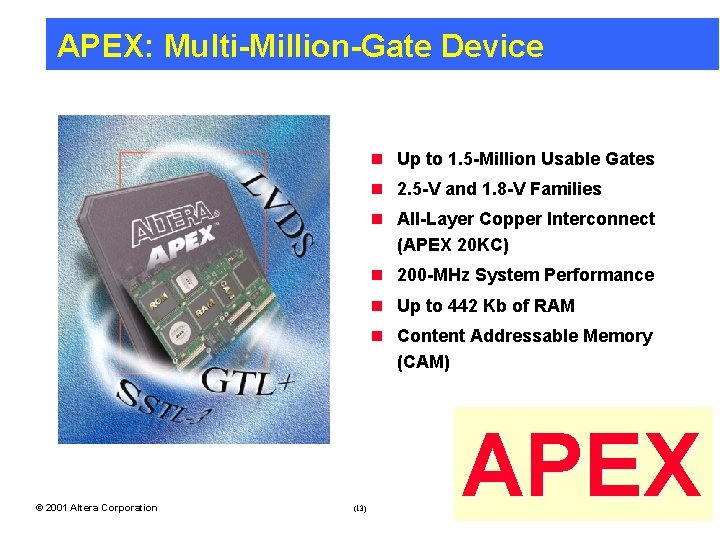

APEX: Multi-Million-Gate Device n Up to 1. 5 -Million Usable Gates n 2. 5 -V and 1. 8 -V Families n All-Layer Copper Interconnect (APEX 20 KC) n 200 -MHz System Performance n Up to 442 Kb of RAM n Content Addressable Memory (CAM) © 2001 Altera Corporation (13) APEX

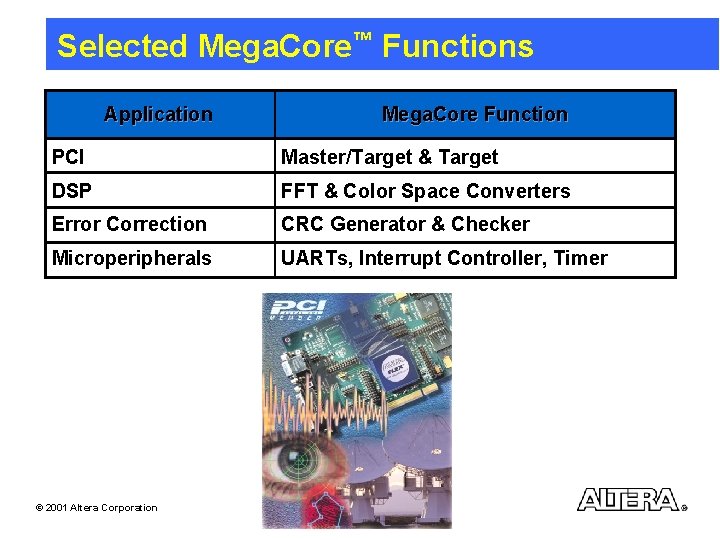

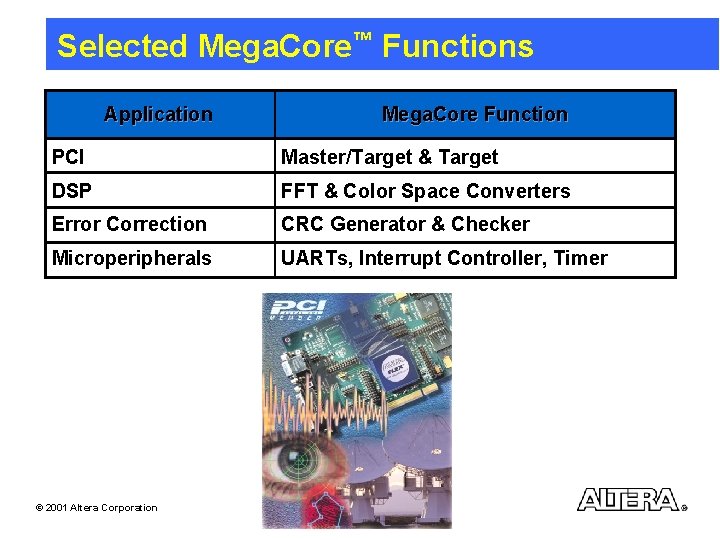

Selected Mega. Core™ Functions Application Mega. Core Function PCI Master/Target & Target DSP FFT & Color Space Converters Error Correction CRC Generator & Checker Microperipherals UARTs, Interrupt Controller, Timer © 2001 Altera Corporation (14)

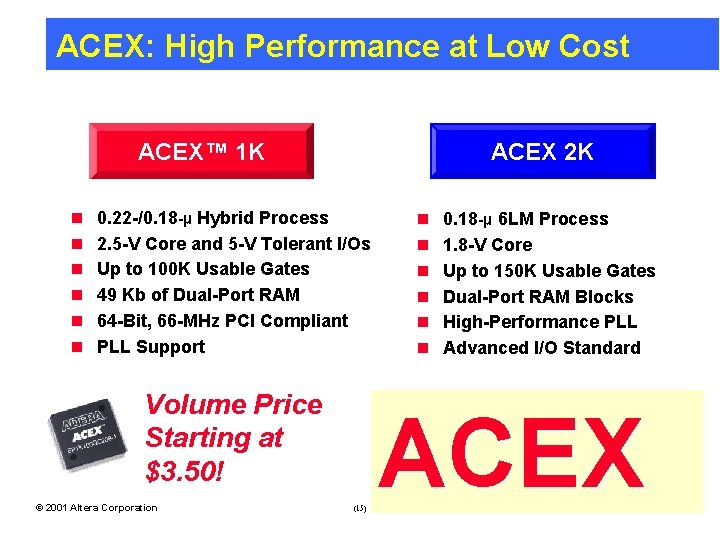

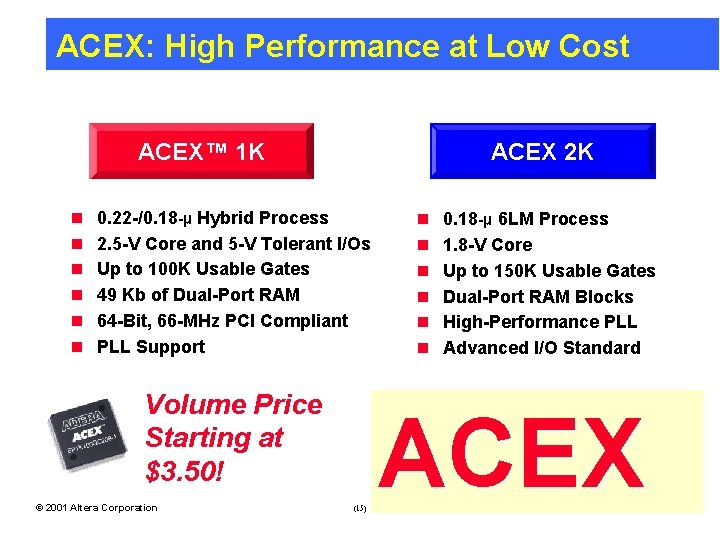

ACEX: High Performance at Low Cost ACEX™ 1 K n n n ACEX 2 K 0. 22 -/0. 18 -µ Hybrid Process 2. 5 -V Core and 5 -V Tolerant I/Os Up to 100 K Usable Gates 49 Kb of Dual-Port RAM 64 -Bit, 66 -MHz PCI Compliant PLL Support Volume Price Starting at $3. 50! © 2001 Altera Corporation (15) n n n 0. 18 -µ 6 LM Process 1. 8 -V Core Up to 150 K Usable Gates Dual-Port RAM Blocks High-Performance PLL Advanced I/O Standard ACEX

Development tools © 2001 Altera Corporation (16)

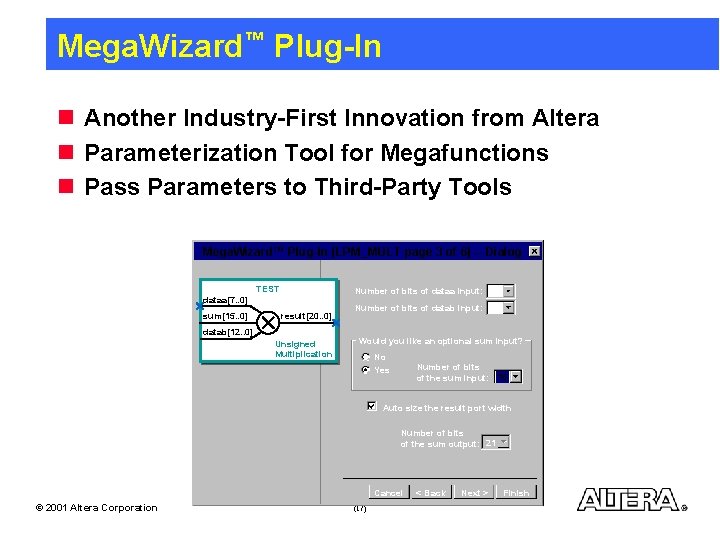

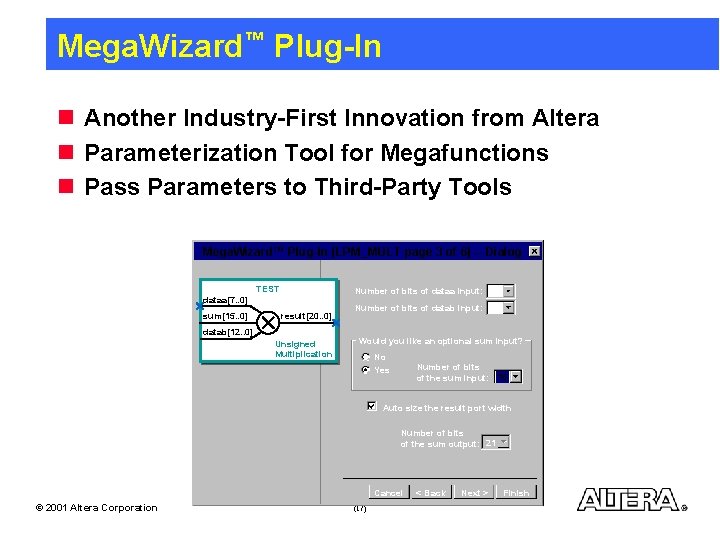

Mega. Wizard™ Plug-In n Another Industry-First Innovation from Altera n Parameterization Tool for Megafunctions n Pass Parameters to Third-Party Tools Mega. Wizard™ Plug-In [LPM_MULT page 3 of 6] -- Dialog TEST Number of bits of dataa input: dataa[7. . 0] sum[15. . 0] result[20. . 0] datab[12. . 0] Unsigned Multiplication 8 Number of bits of datab input: 13 Would you like an optional sum input? No Yes Number of bits of the sum input: 16 Auto size the result port width Number of bits of the sum output: 21 Cancel © 2001 Altera Corporation (17) < Back Next > Finish

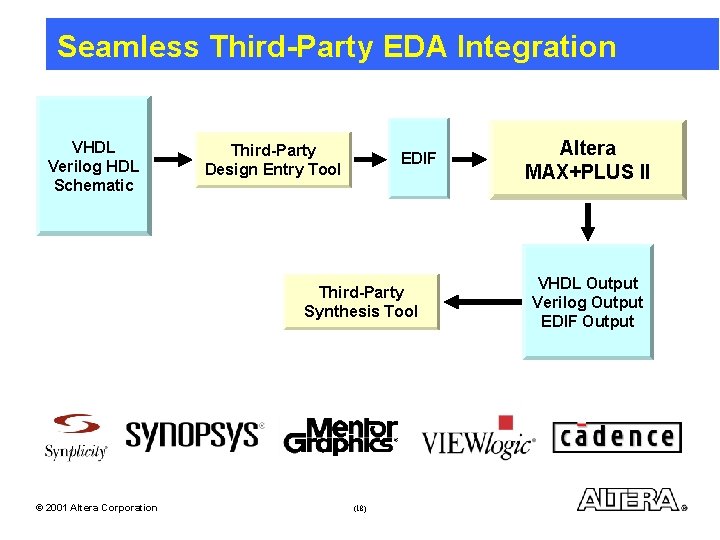

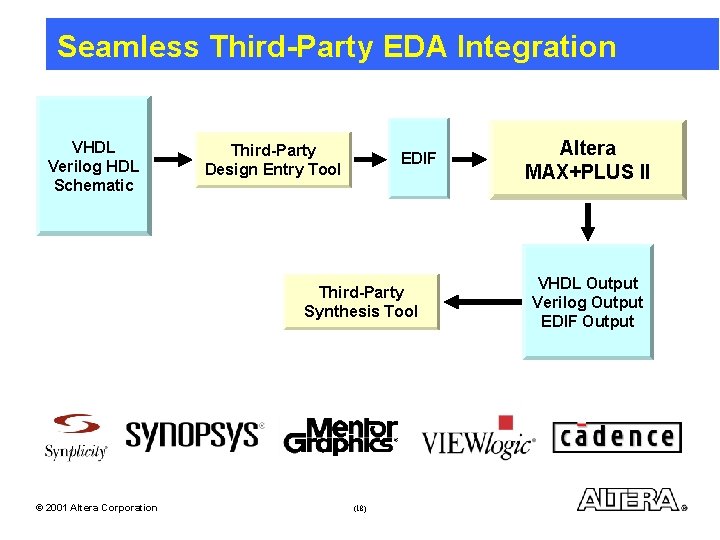

Seamless Third-Party EDA Integration VHDL Verilog HDL Schematic Third-Party Design Entry Tool EDIF Third-Party Synthesis Tool © 2001 Altera Corporation (18) Altera MAX+PLUS II VHDL Output Verilog Output EDIF Output

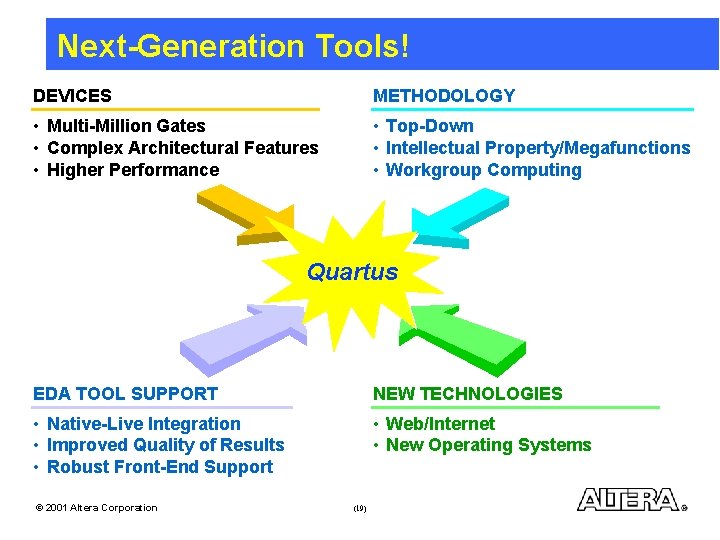

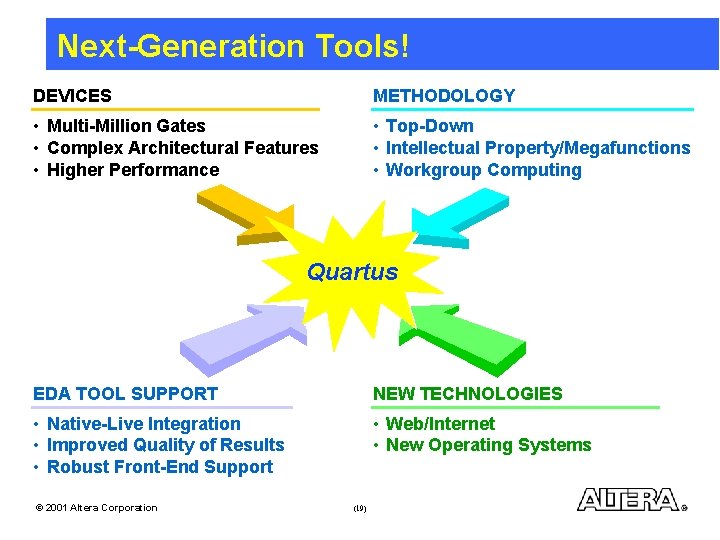

Next-Generation Tools! DEVICES METHODOLOGY • Multi-Million Gates • Complex Architectural Features • Higher Performance • Top-Down • Intellectual Property/Megafunctions • Workgroup Computing Quartus EDA TOOL SUPPORT NEW TECHNOLOGIES • Native-Live Integration • Improved Quality of Results • Robust Front-End Support • Web/Internet • New Operating Systems © 2001 Altera Corporation (19)

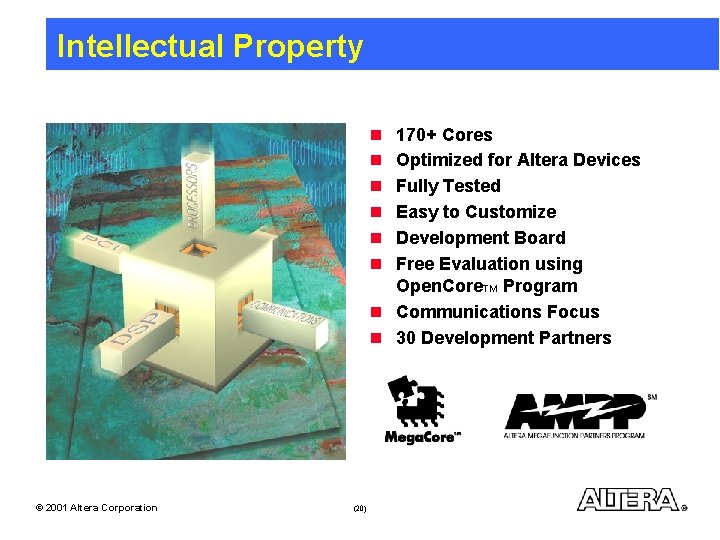

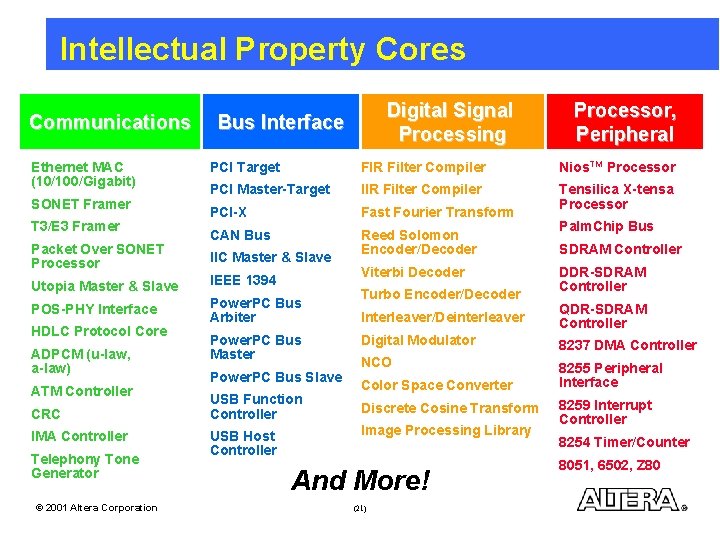

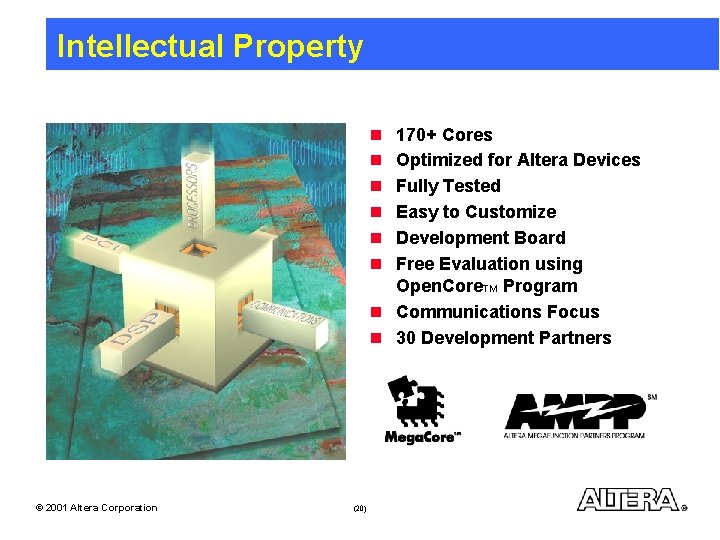

Intellectual Property n n n 170+ Cores Optimized for Altera Devices Fully Tested Easy to Customize Development Board Free Evaluation using Open. Core. TM Program n Communications Focus n 30 Development Partners © 2001 Altera Corporation (20)

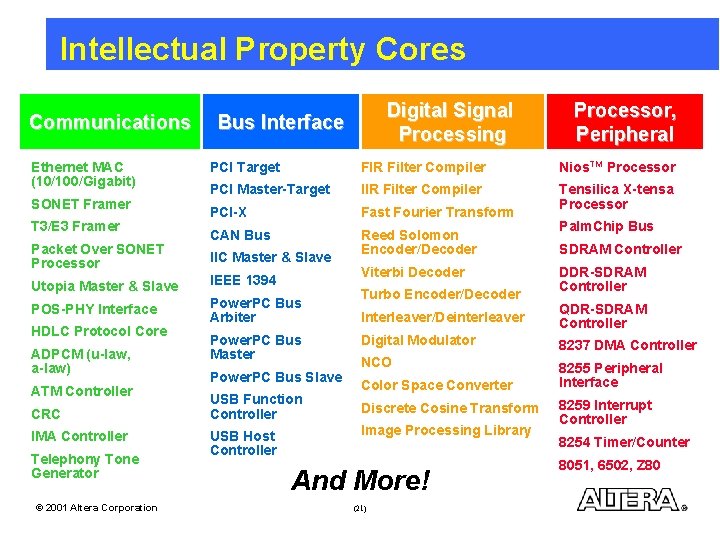

Intellectual Property Cores Communications Ethernet MAC (10/100/Gigabit) SONET Framer T 3/E 3 Framer Packet Over SONET Processor FIR Filter Compiler Nios. TM Processor PCI Master-Target IIR Filter Compiler PCI-X Fast Fourier Transform Tensilica X-tensa Processor CAN Bus Reed Solomon Encoder/Decoder IIC Master & Slave IEEE 1394 POS-PHY Interface Power. PC Bus Arbiter ADPCM (u-law, a-law) ATM Controller CRC IMA Controller Telephony Tone Generator © 2001 Altera Corporation Processor, Peripheral PCI Target Utopia Master & Slave HDLC Protocol Core Digital Signal Processing Bus Interface Power. PC Bus Master Power. PC Bus Slave USB Function Controller USB Host Controller Viterbi Decoder Turbo Encoder/Decoder Palm. Chip Bus SDRAM Controller DDR-SDRAM Controller Interleaver/Deinterleaver QDR-SDRAM Controller Digital Modulator 8237 DMA Controller NCO 8255 Peripheral Interface Color Space Converter Discrete Cosine Transform Image Processing Library And More! (21) 8259 Interrupt Controller 8254 Timer/Counter 8051, 6502, Z 80

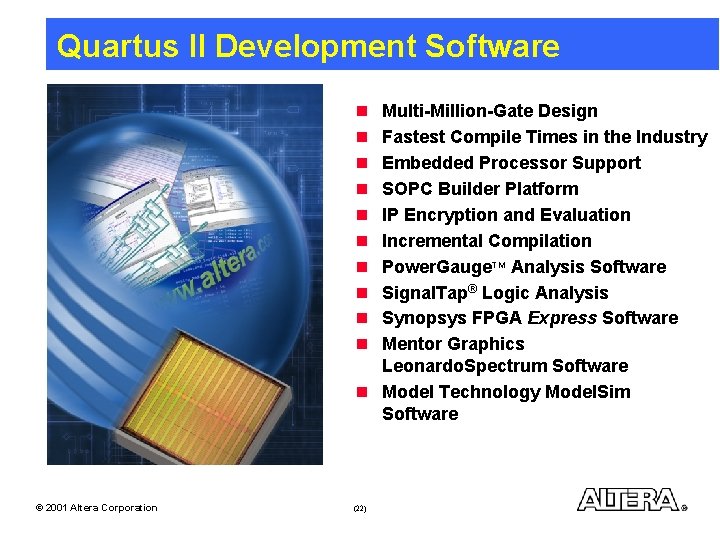

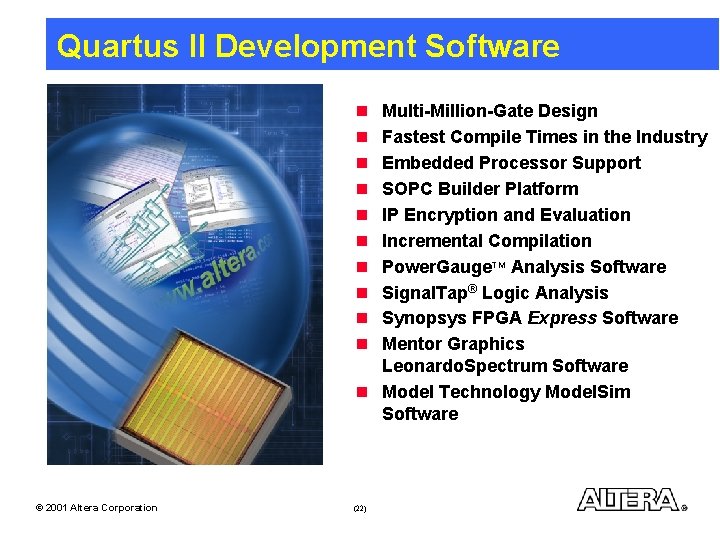

Quartus II Development Software n n n n n Multi-Million-Gate Design Fastest Compile Times in the Industry Embedded Processor Support SOPC Builder Platform IP Encryption and Evaluation Incremental Compilation Power. Gauge. TM Analysis Software Signal. Tap® Logic Analysis Synopsys FPGA Express Software Mentor Graphics Leonardo. Spectrum Software n Model Technology Model. Sim Software © 2001 Altera Corporation (22)

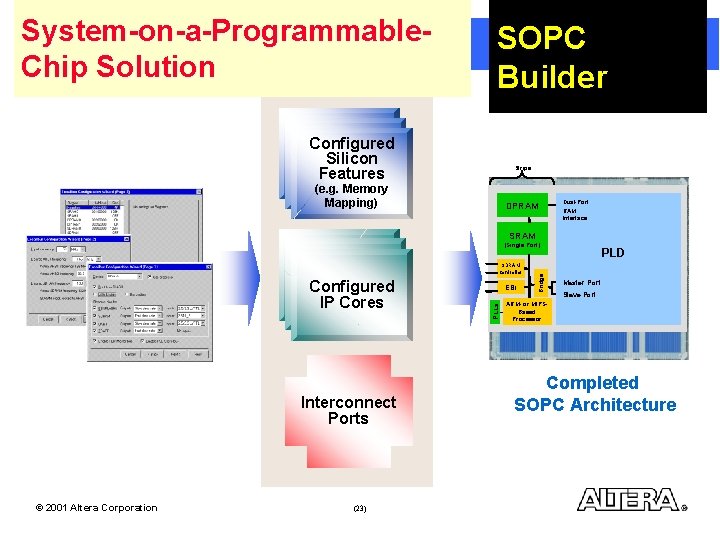

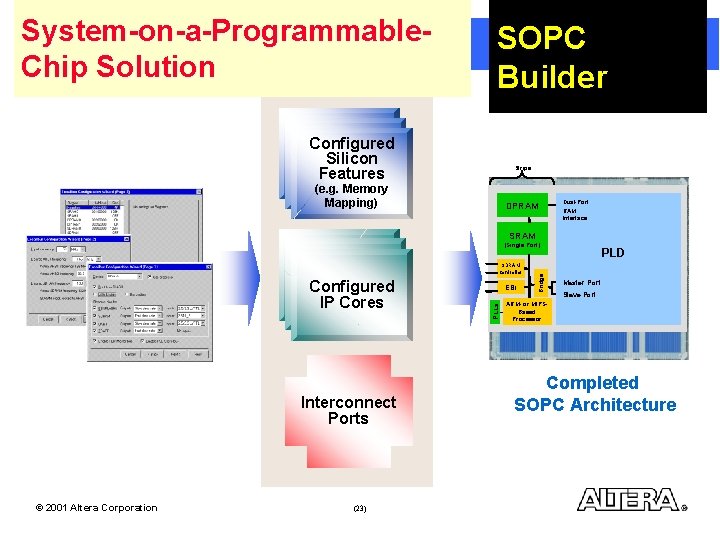

System-on-a-Programmable. Chip Solution SOPC Builder Configured Silicon Features Stripe (e. g. Memory Mapping) DPRAM Dual-Port RAM Interface SRAM Interconnect Ports © 2001 Altera Corporation (23) SDRAM Controller Flash Interface EBI PLLs Configured IP Cores SDRAM Interface Bridge (Single Port) PLD Master Port Slave Port ARM- or MIPSBased Processor Completed SOPC Architecture

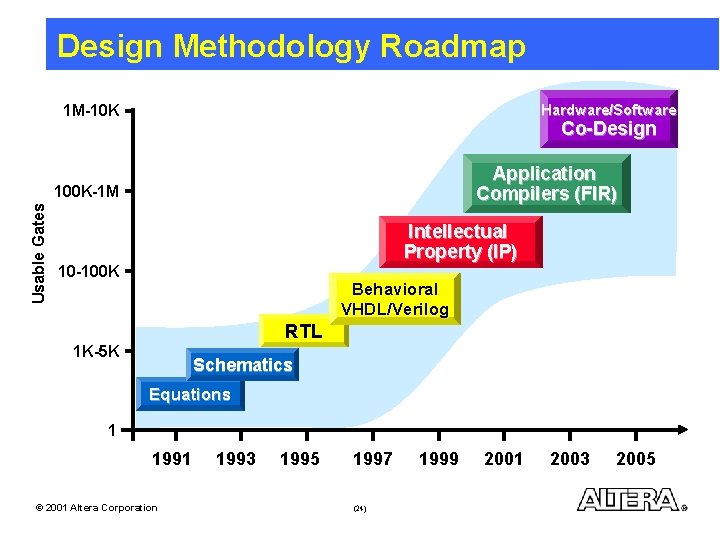

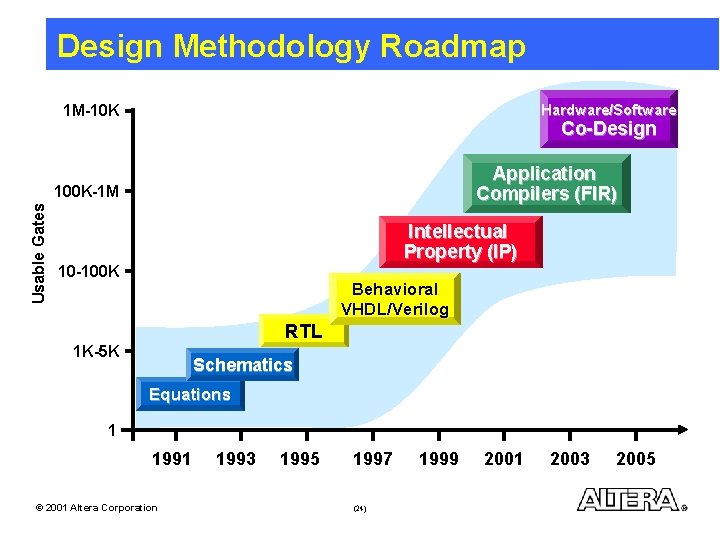

Design Methodology Roadmap Hardware/Software 1 M-10 K Co-Design Application Compilers (FIR) Usable Gates 100 K-1 M Intellectual Property (IP) 10 -100 K Behavioral VHDL/Verilog RTL 1 K-5 K Schematics Equations 1 1991 © 2001 Altera Corporation 1993 1995 1997 (24) 1999 2001 2003 2005

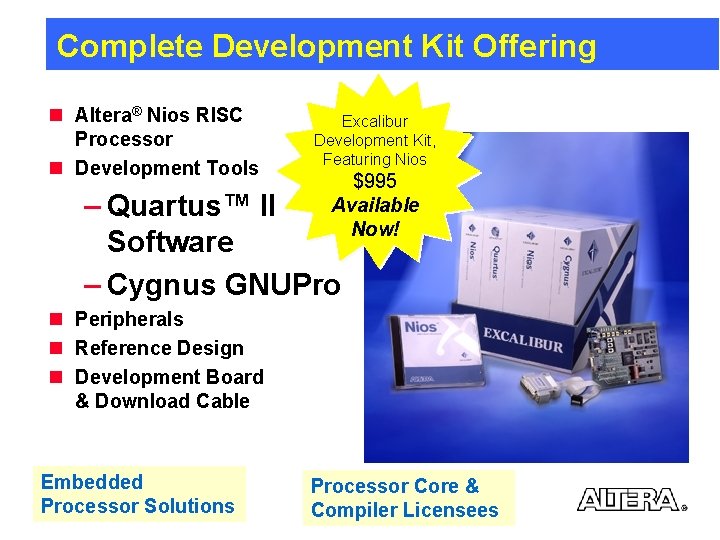

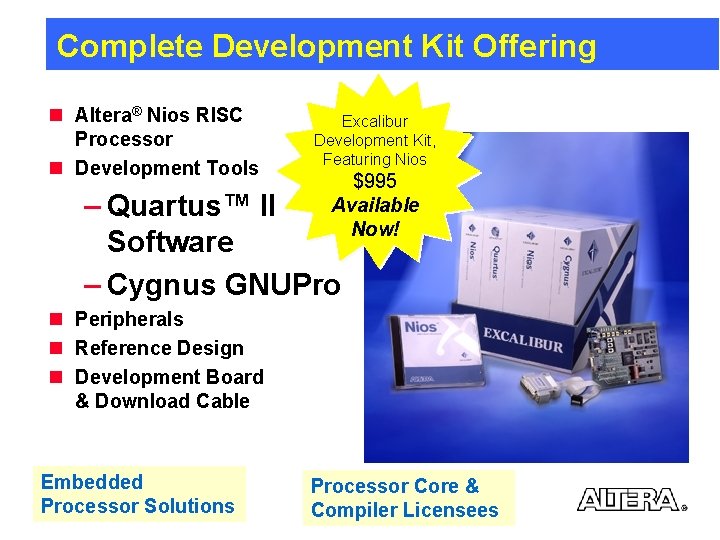

Complete Development Kit Offering n Altera® Nios RISC Processor n Development Tools Excalibur Development Kit, Featuring Nios $995 Available Now! – Quartus™ II Software – Cygnus GNUPro n Peripherals n Reference Design n Development Board & Download Cable Embedded ©Processor 2001 Altera Corporation Solutions Processor Core & Compiler Licensees (25)

Future Developments © 2001 Altera Corporation (26)

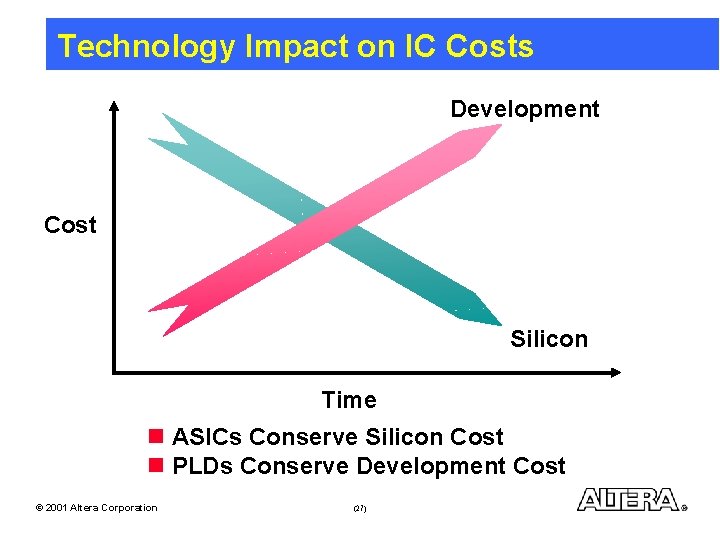

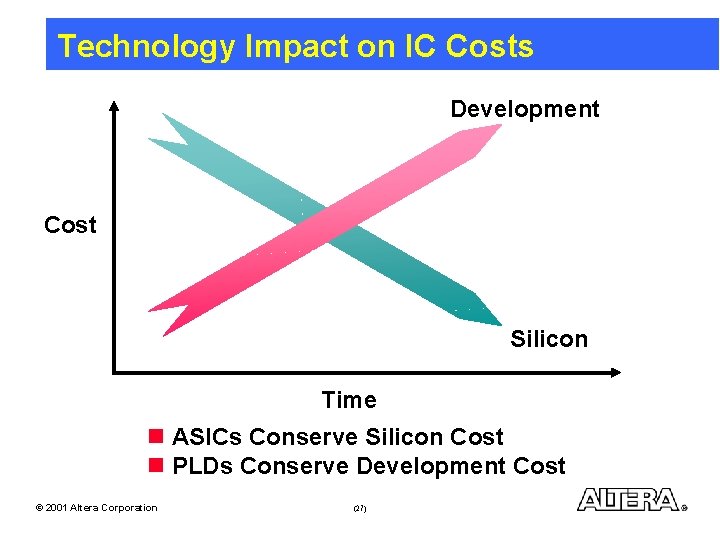

Technology Impact on IC Costs Development Cost Silicon Time n ASICs Conserve Silicon Cost n PLDs Conserve Development Cost © 2001 Altera Corporation (27)

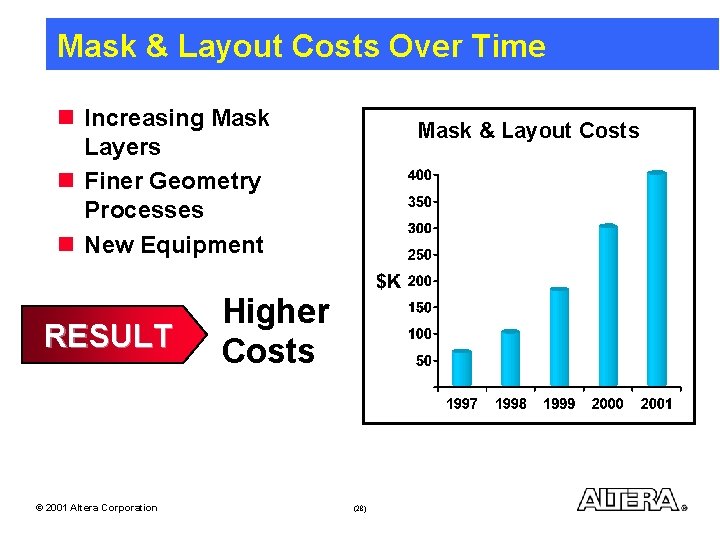

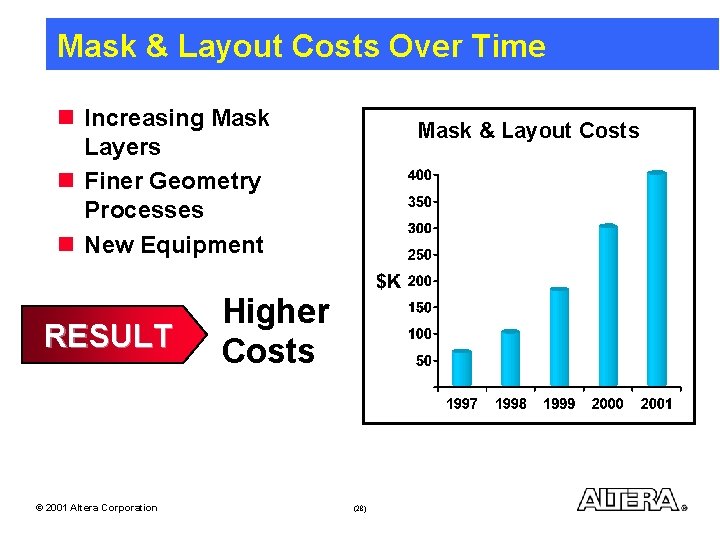

Mask & Layout Costs Over Time n Increasing Mask Layers n Finer Geometry Processes n New Equipment RESULT © 2001 Altera Corporation Mask & Layout Costs Higher Costs (28)

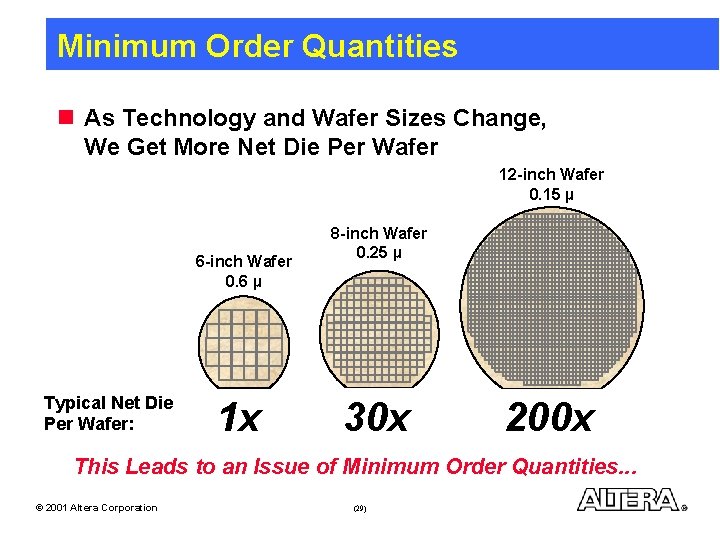

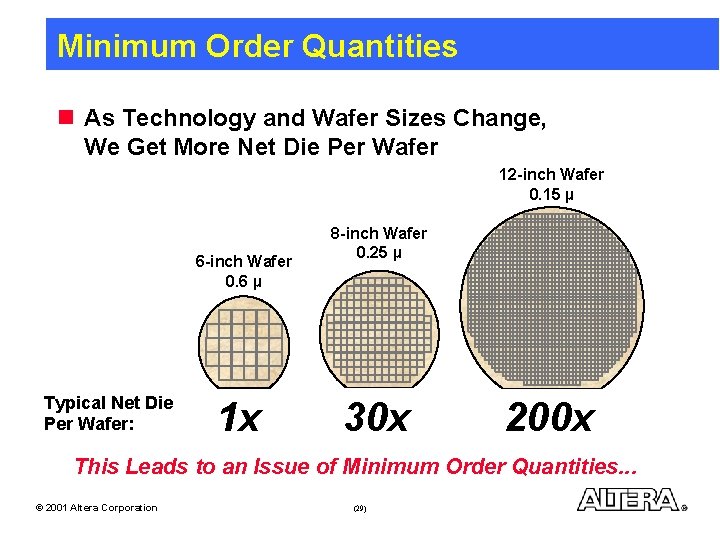

Minimum Order Quantities n As Technology and Wafer Sizes Change, We Get More Net Die Per Wafer 12 -inch Wafer 0. 15 µ 6 -inch Wafer 0. 6 µ Typical Net Die Per Wafer: 1 x 8 -inch Wafer 0. 25 µ 30 x 200 x This Leads to an Issue of Minimum Order Quantities. . . © 2001 Altera Corporation (29)

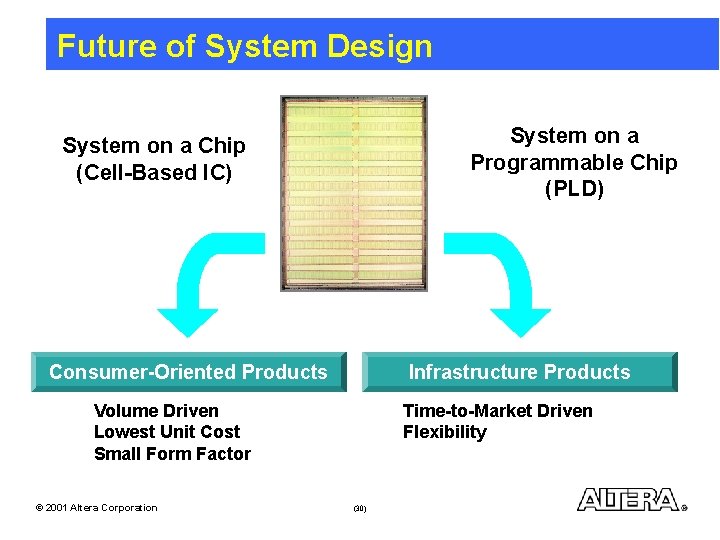

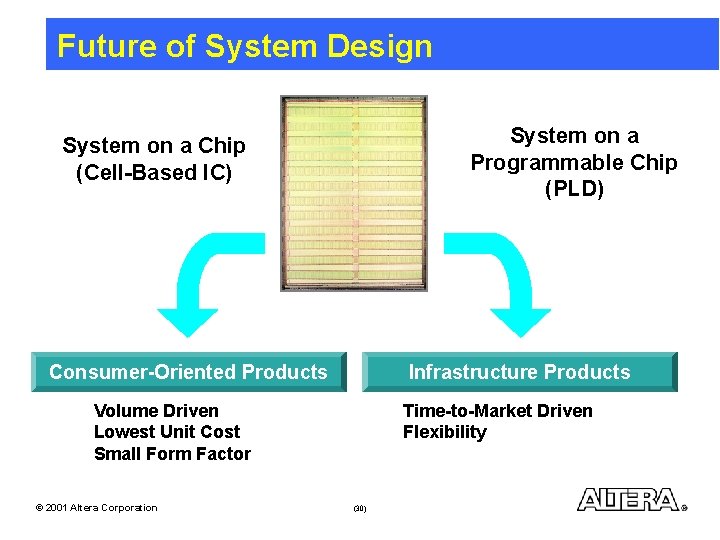

Future of System Design System on a Programmable Chip (PLD) System on a Chip (Cell-Based IC) Consumer-Oriented Products Infrastructure Products Volume Driven Lowest Unit Cost Small Form Factor © 2001 Altera Corporation Time-to-Market Driven Flexibility (30)

Souces: Altera Corporation David Greenfield, Sr. Product Marketing Manager, Development Tools © 2001 Altera Corporation ()