Sector Logic Implementation for the ATLAS Endcap Level1

- Slides: 20

Sector Logic Implementation for the ATLAS Endcap Level-1 Muon Trigger R. Ichimiya (Kobe university) • • • Contents ATLAS Level-1 Trigger system Endcap Muon Trigger system Sector Logic Design Prototype Test Results Summary 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 1

ATLAS Trigger and DAQ system ATLAS Trigger & DAQ System Level-1 Trigger System 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 2

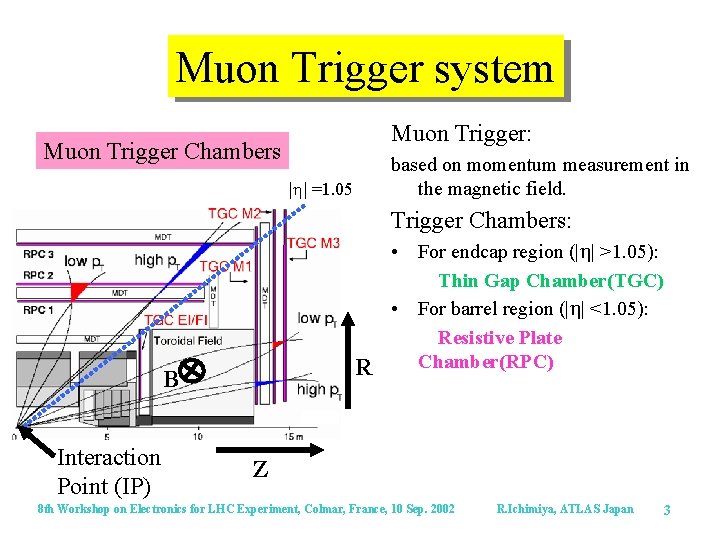

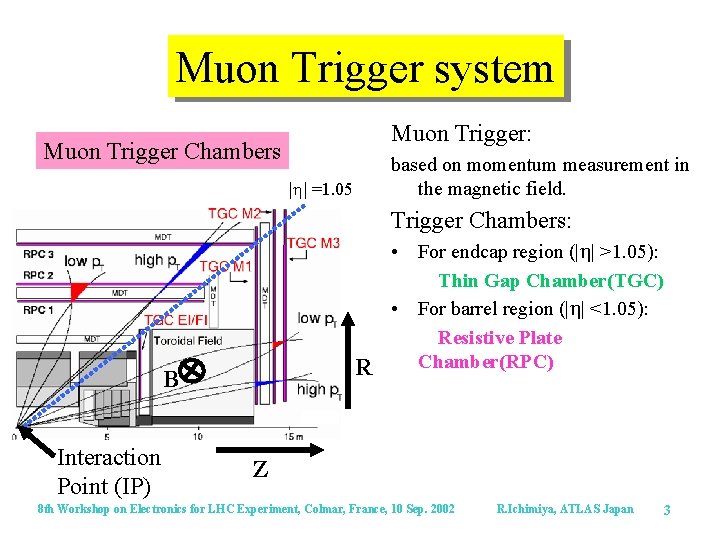

Muon Trigger system Muon Trigger: Muon Trigger Chambers |h| =1. 05 based on momentum measurement in the magnetic field. Trigger Chambers: • For endcap region (|h| >1. 05): Thin Gap Chamber(TGC) • For barrel region (|h| <1. 05): Resistive Plate Chamber(RPC) R B Interaction Point (IP) Z 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 3

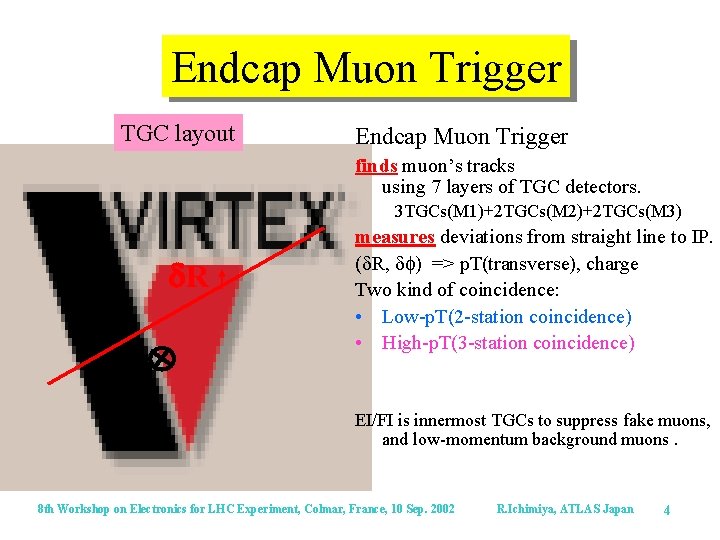

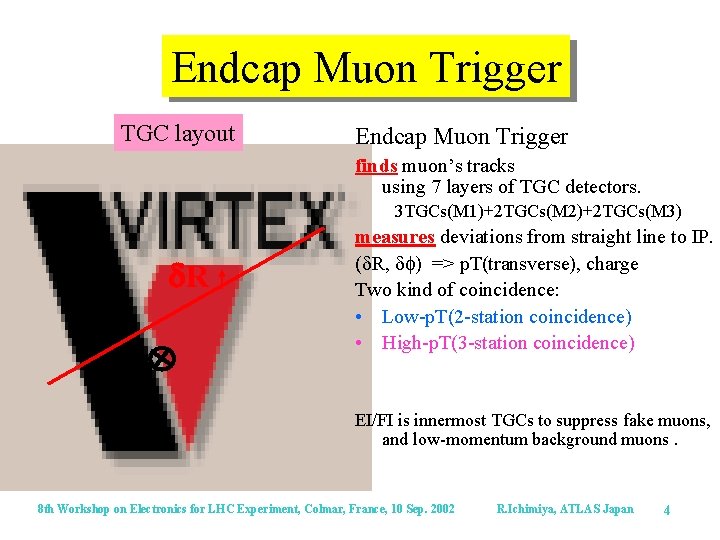

Endcap Muon Trigger TGC layout Endcap Muon Trigger finds muon’s tracks using 7 layers of TGC detectors. 3 TGCs(M 1)+2 TGCs(M 2)+2 TGCs(M 3) d. R B measures deviations from straight line to IP. (d. R, df) => p. T(transverse), charge Two kind of coincidence: • Low-p. T(2 -station coincidence) • High-p. T(3 -station coincidence) EI/FI is innermost TGCs to suppress fake muons, and low-momentum background muons. 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 4

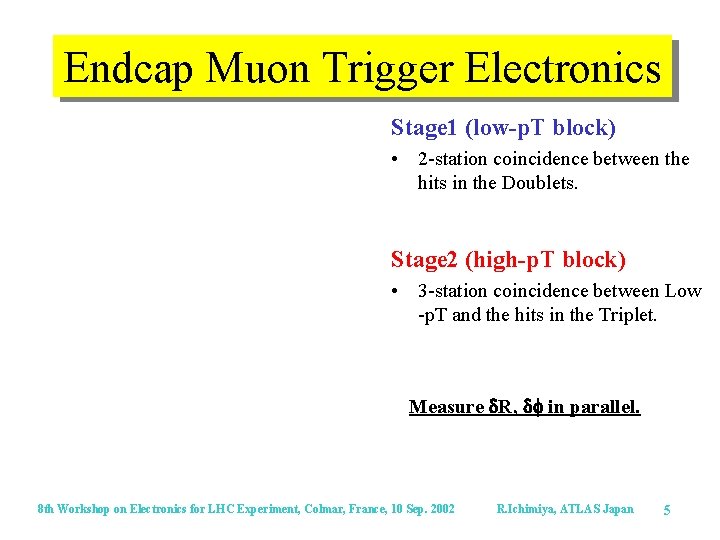

Endcap Muon Trigger Electronics Stage 1 (low-p. T block) • 2 -station coincidence between the hits in the Doublets. Stage 2 (high-p. T block) • 3 -station coincidence between Low -p. T and the hits in the Triplet. Measure d. R, df in parallel. 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 5

Endcap Muon Trigger Electronics Stage 3 (Sector Logic) combines R- and f-informaton from high-p. T coincidence. 1. 2. 3. Reconstruct 3 -dimensional muon tracks. tag with its p. T value of 6 levels by using d. R and df. choose 2 highest p. T tracks. 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 6

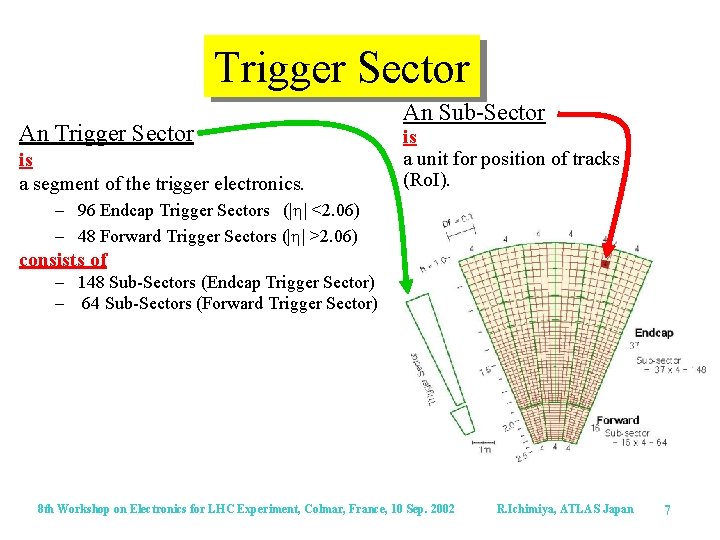

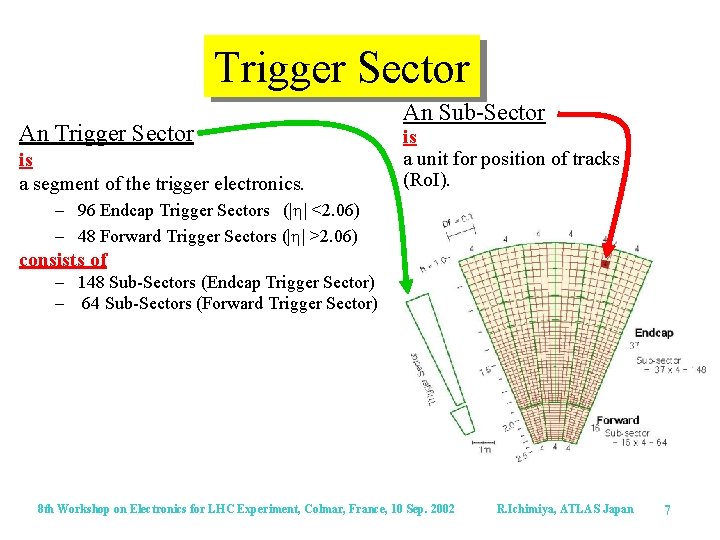

Trigger Sector An Trigger Sector is a segment of the trigger electronics. An Sub-Sector is a unit for position of tracks (Ro. I). – 96 Endcap Trigger Sectors (|h| <2. 06) – 48 Forward Trigger Sectors (|h| >2. 06) consists of – 148 Sub-Sectors (Endcap Trigger Sector) – 64 Sub-Sectors (Forward Trigger Sector) 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 7

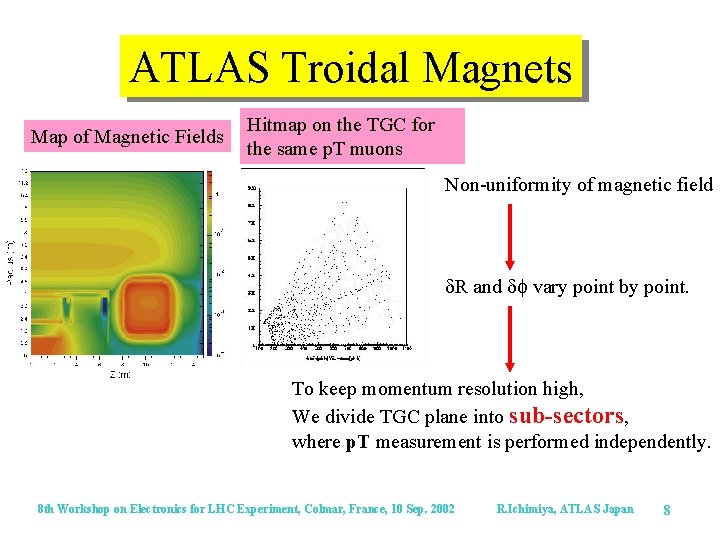

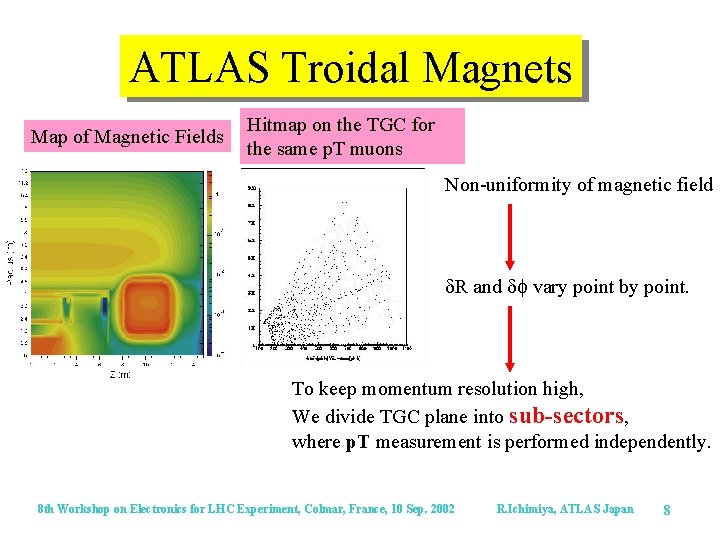

ATLAS Troidal Magnets Map of Magnetic Fields Hitmap on the TGC for the same p. T muons Non-uniformity of magnetic field d. R and df vary point by point. To keep momentum resolution high, We divide TGC plane into sub-sectors, where p. T measurement is performed independently. 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 8

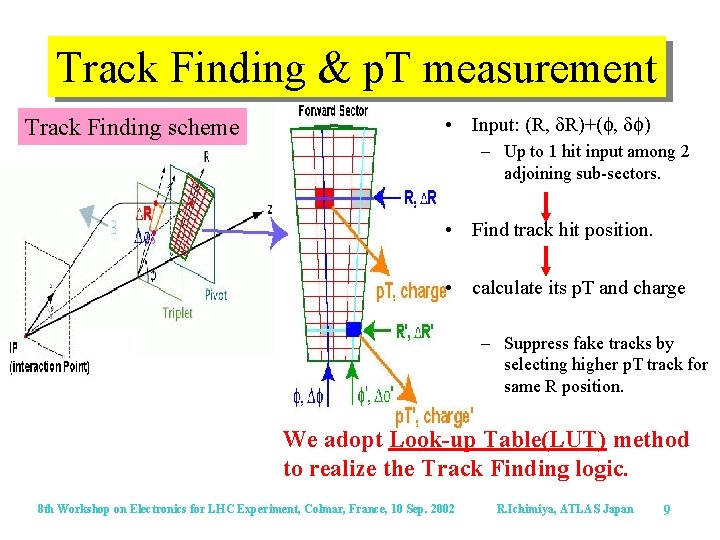

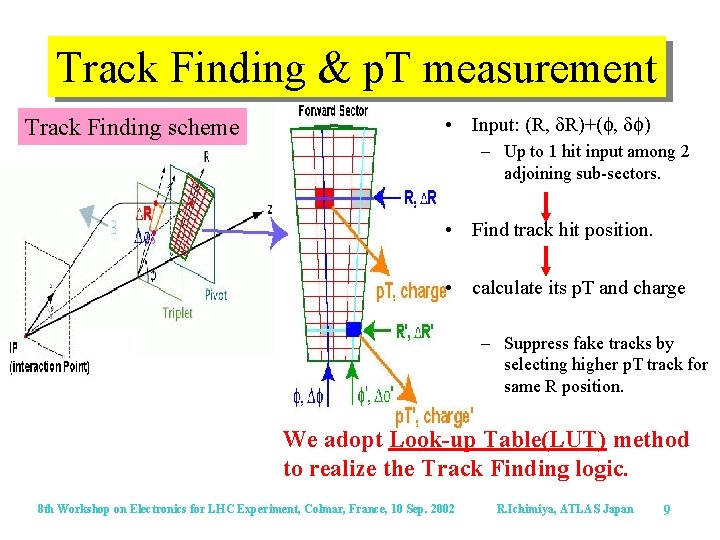

Track Finding & p. T measurement Track Finding scheme • Input: (R, d. R)+(f, df) – Up to 1 hit input among 2 adjoining sub-sectors. • Find track hit position. • calculate its p. T and charge – Suppress fake tracks by selecting higher p. T track for same R position. We adopt Look-up Table(LUT) method to realize the Track Finding logic. 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 9

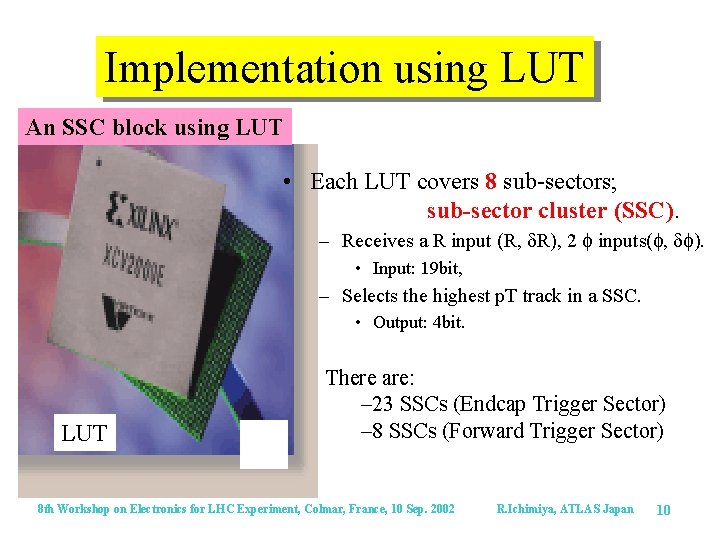

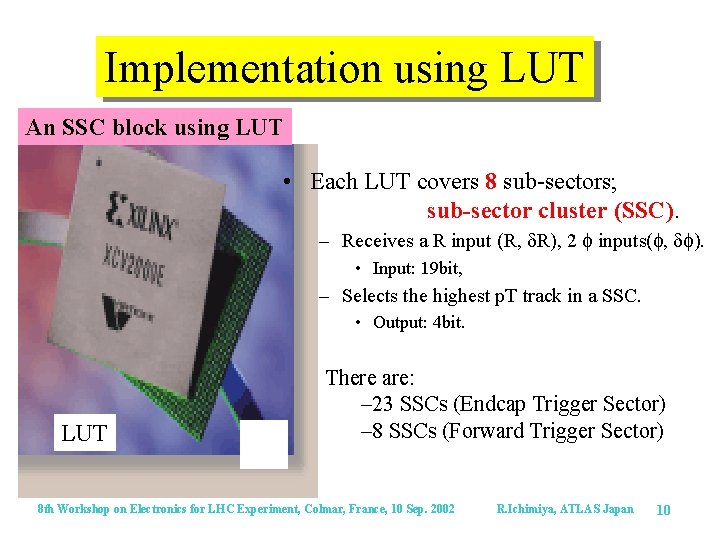

Implementation using LUT An SSC block using LUT • Each LUT covers 8 sub-sectors; sub-sector cluster (SSC). – Receives a R input (R, d. R), 2 f inputs(f, df). • Input: 19 bit, – Selects the highest p. T track in a SSC. • Output: 4 bit. LUT There are: – 23 SSCs (Endcap Trigger Sector) – 8 SSCs (Forward Trigger Sector) 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 10

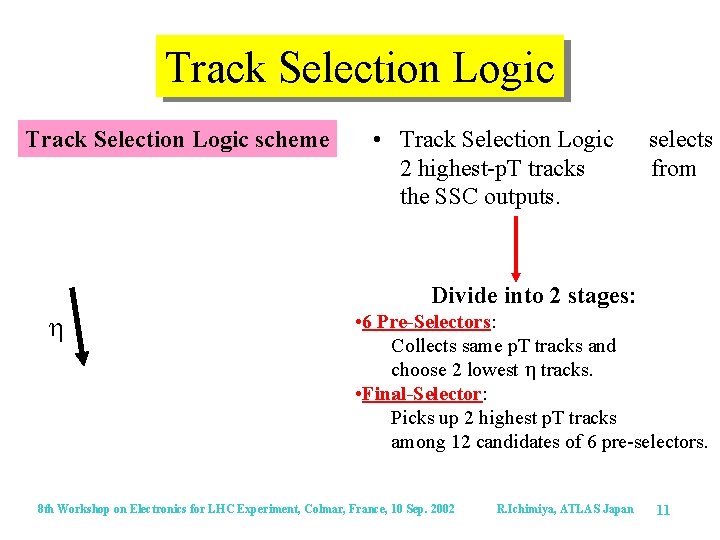

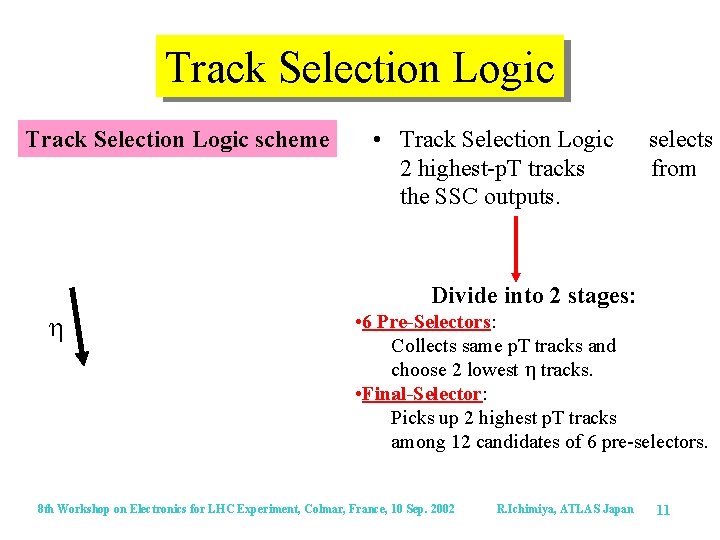

Track Selection Logic scheme h • Track Selection Logic 2 highest-p. T tracks the SSC outputs. selects from Divide into 2 stages: • 6 Pre-Selectors: Collects same p. T tracks and choose 2 lowest h tracks. • Final-Selector: Picks up 2 highest p. T tracks among 12 candidates of 6 pre-selectors. 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 11

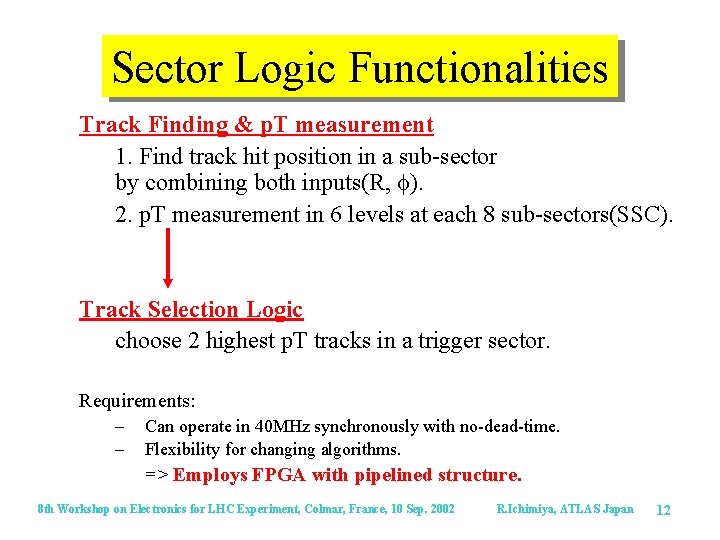

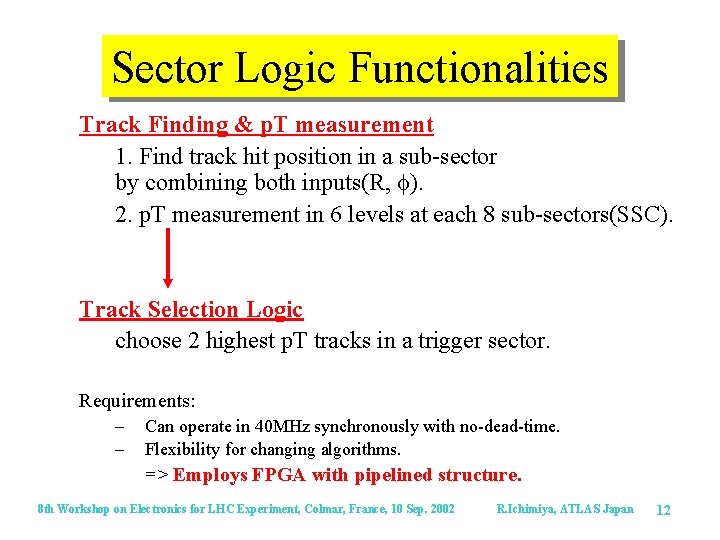

Sector Logic Functionalities Track Finding & p. T measurement 1. Find track hit position in a sub-sector by combining both inputs(R, f). 2. p. T measurement in 6 levels at each 8 sub-sectors(SSC). Track Selection Logic choose 2 highest p. T tracks in a trigger sector. Requirements: – – Can operate in 40 MHz synchronously with no-dead-time. Flexibility for changing algorithms. => Employs FPGA with pipelined structure. 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 12

Prototype-0: FPGA(Virtex-EM) • Device Choice – Large SRAM embedded type FPGA is required to hold many big LUTs. – Xilinx Virtex-EM series (XCV 405 E) • Block. RAM™ 560 Kbit – synchronous SRAM – 4 Kbit x 160 • (cf. 82 Kbit in XCV 400 E as same gate size) • Merits – Can access the LUT very fast. (access speed: 2. 46 ns) – Reduce number of chips and wiring in PCB board. – (!) Needs 1 additional clock cycle to access the Block. RAM™. (Because, the Block. RAM™ is the synchronous SRAM. ) 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 13

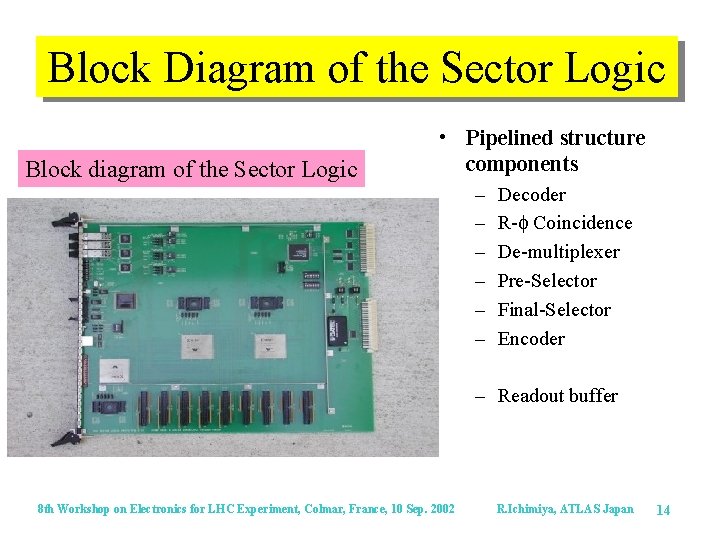

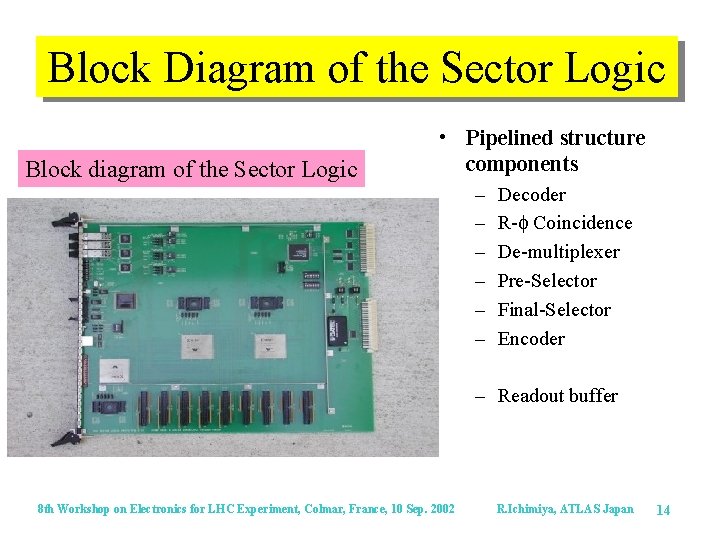

Block Diagram of the Sector Logic Block diagram of the Sector Logic • Pipelined structure components – – – Decoder R-f Coincidence De-multiplexer Pre-Selector Final-Selector Encoder – Readout buffer 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 14

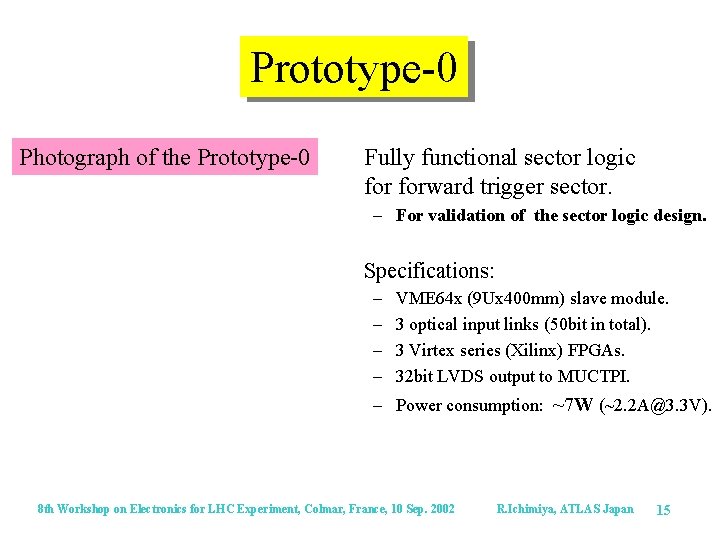

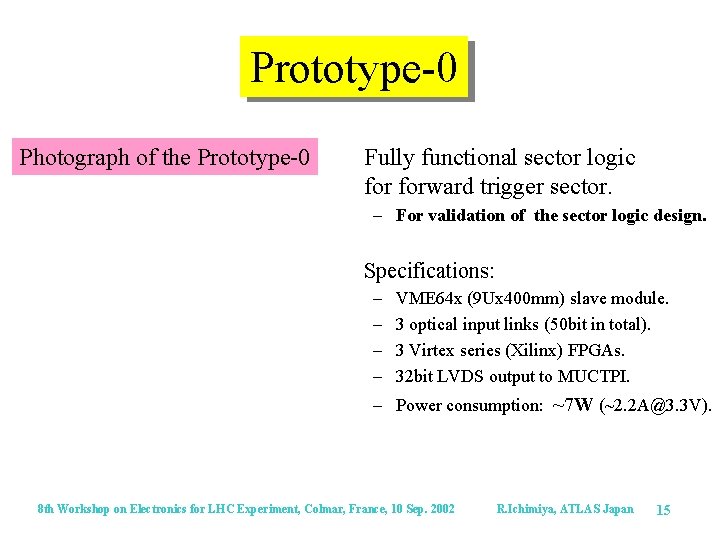

Prototype-0 Photograph of the Prototype-0 Fully functional sector logic forward trigger sector. – For validation of the sector logic design. Specifications: – – VME 64 x (9 Ux 400 mm) slave module. 3 optical input links (50 bit in total). 3 Virtex series (Xilinx) FPGAs. 32 bit LVDS output to MUCTPI. – Power consumption: ~7 W (~2. 2 A@3. 3 V). 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 15

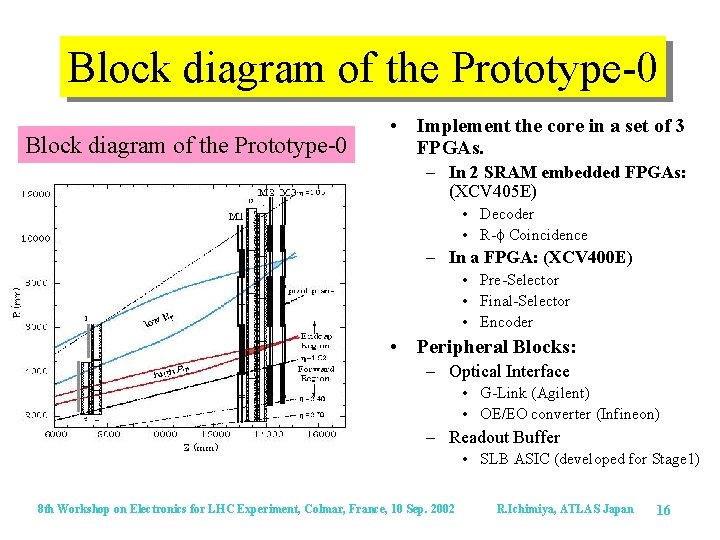

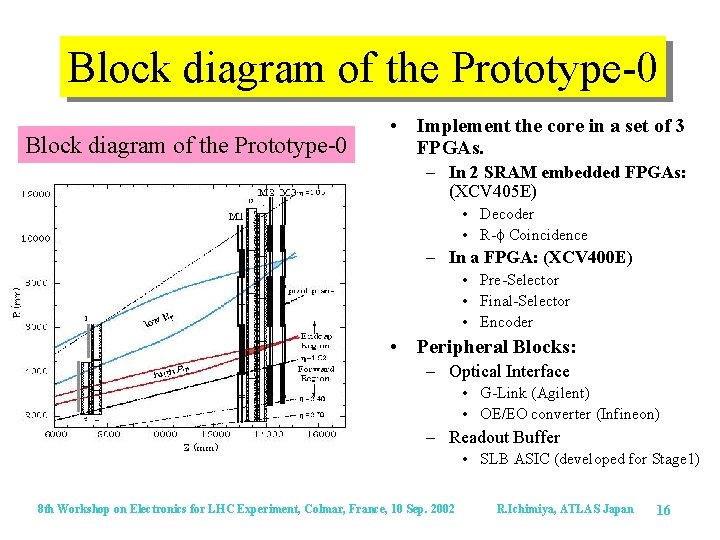

Block diagram of the Prototype-0 • Implement the core in a set of 3 FPGAs. – In 2 SRAM embedded FPGAs: (XCV 405 E) • Decoder • R-f Coincidence – In a FPGA: (XCV 400 E) • Pre-Selector • Final-Selector • Encoder • Peripheral Blocks: – Optical Interface • G-Link (Agilent) • OE/EO converter (Infineon) – Readout Buffer • SLB ASIC (developed for Stage 1) 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 16

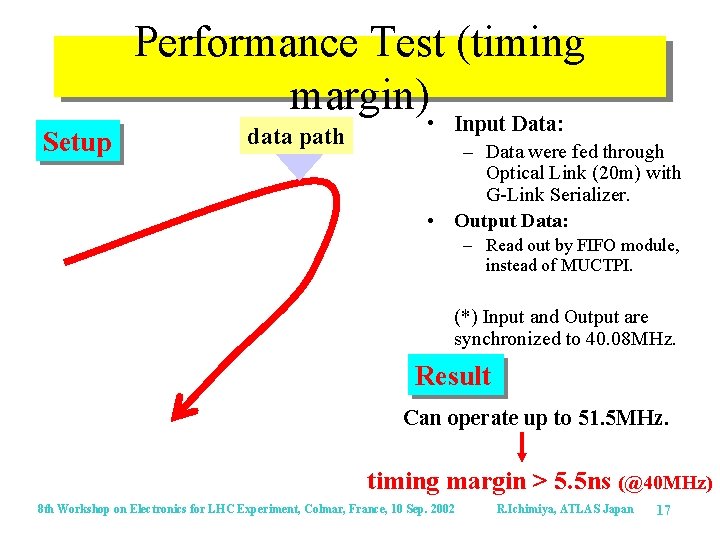

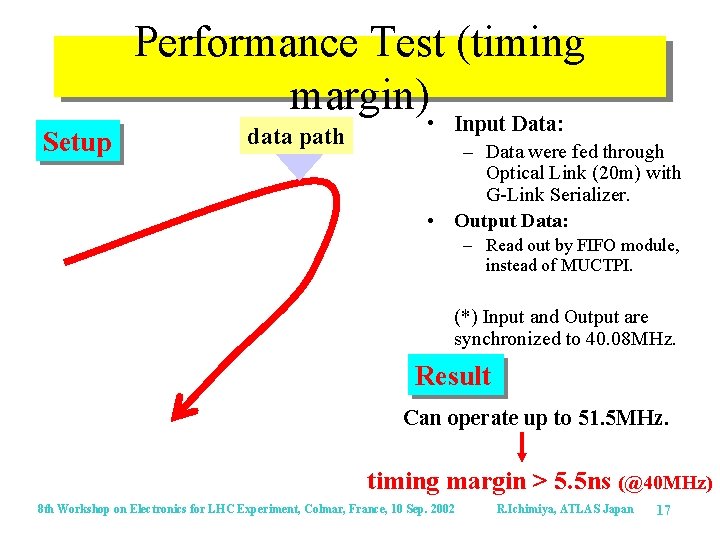

Performance Test (timing margin) Setup data path • Input Data: – Data were fed through Optical Link (20 m) with G-Link Serializer. • Output Data: – Read out by FIFO module, instead of MUCTPI. (*) Input and Output are synchronized to 40. 08 MHz. Result Can operate up to 51. 5 MHz. timing margin > 5. 5 ns (@40 MHz) 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 17

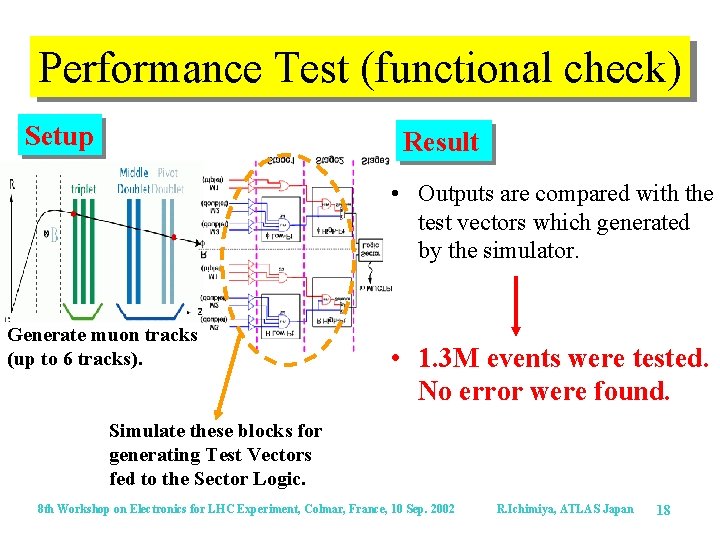

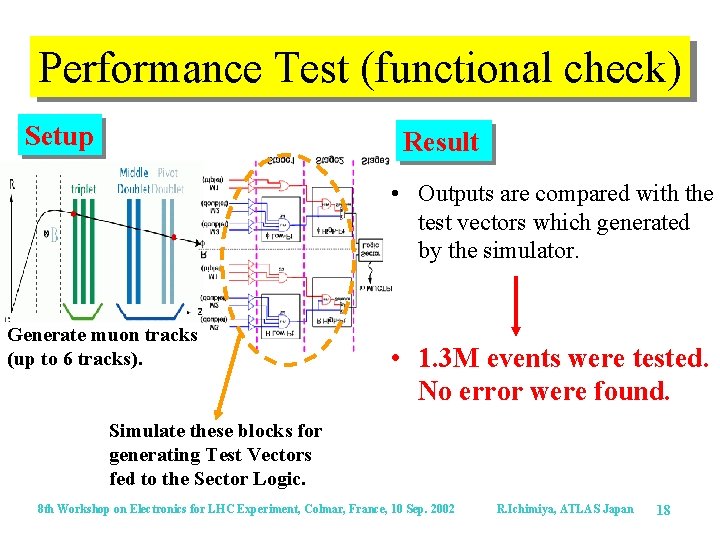

Performance Test (functional check) Setup Result • Outputs are compared with the test vectors which generated by the simulator. Generate muon tracks (up to 6 tracks). • 1. 3 M events were tested. No error were found. Simulate these blocks for generating Test Vectors fed to the Sector Logic. 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 18

Integration Test with the MUCTPI Setup • SL was configured as an PPG. • TTCvi was used for clock source (40. 08 MHz), Trigger(L 1 A) for MIOCT. Result Error rate: <10 -9 /bit. 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 19

Summary • Designed the Sector Logic for endcap muon trigger. – The core is R-f coincidence and Track Selection Logic. – SRAM embedded FPGA for the LUT of R-f coincidence. – Pipelined structure. • Fabricated and Tested fully functional Sector Logic Prototype. – – FPGA based design. It worked up to 51. 5 MHz; 5. 5 ns margin @40 MHz. No error with 1. 3 M input patterns. Verified the data transmission from the Sector Logic to the MUCTPI. The design and the prototype implementation satisfies requirements for the endcap muon Sector Logic. 8 th Workshop on Electronics for LHC Experiment, Colmar, France, 10 Sep. 2002 R. Ichimiya, ATLAS Japan 20