Section 6 Digital Combinational Circuits VLSI DesignEEE 453

Section 6 Digital Combinational Circuits VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili

CMOS Circuits n Combinational » Static » Dynamic n Sequential » Static » Dynamic VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 2

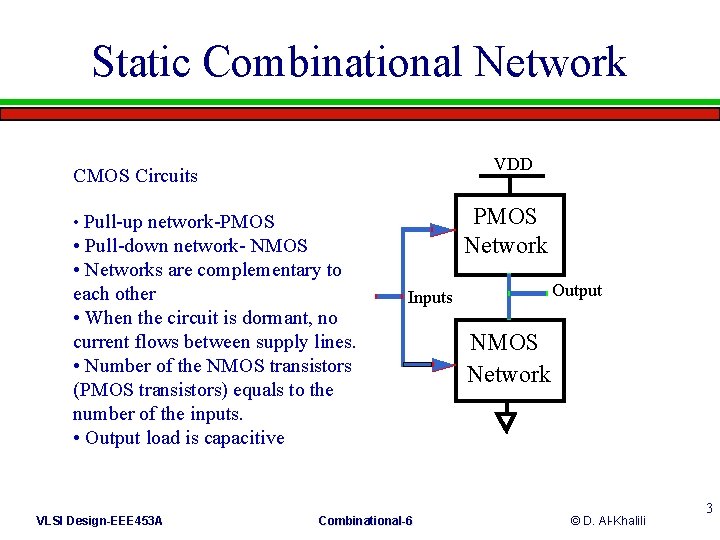

Static Combinational Network VDD CMOS Circuits PMOS Network • Pull-up network-PMOS • Pull-down network- NMOS • Networks are complementary to each other • When the circuit is dormant, no current flows between supply lines. • Number of the NMOS transistors (PMOS transistors) equals to the number of the inputs. • Output load is capacitive VLSI Design-EEE 453 A Output Inputs Combinational-6 NMOS Network © D. Al-Khalili 3

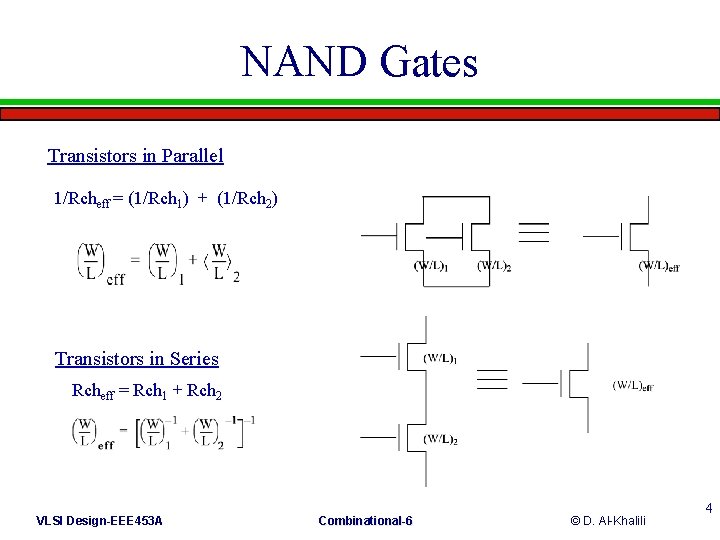

NAND Gates Transistors in Parallel 1/Rcheff = (1/Rch 1) + (1/Rch 2) Transistors in Series Rcheff = Rch 1 + Rch 2 VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 4

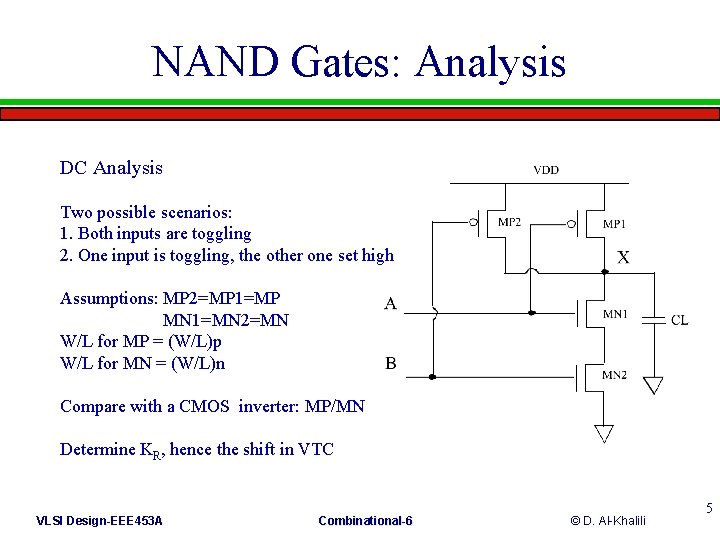

NAND Gates: Analysis DC Analysis Two possible scenarios: 1. Both inputs are toggling 2. One input is toggling, the other one set high Assumptions: MP 2=MP 1=MP MN 1=MN 2=MN W/L for MP = (W/L)p W/L for MN = (W/L)n Compare with a CMOS inverter: MP/MN Determine KR, hence the shift in VTC VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 5

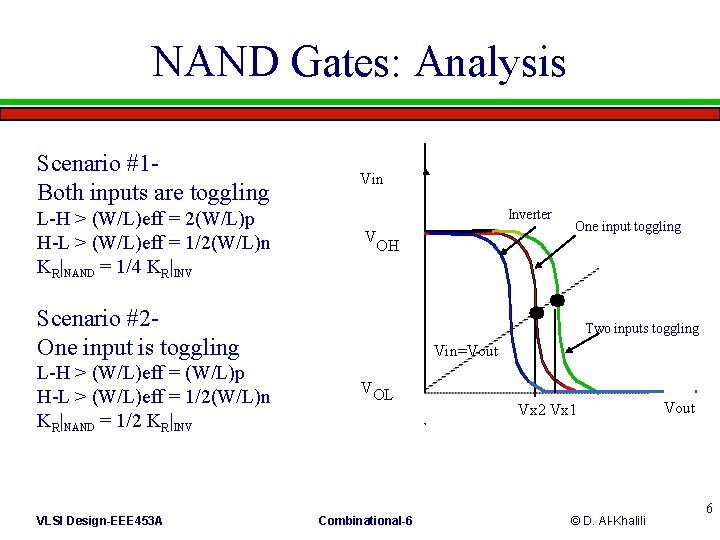

NAND Gates: Analysis Scenario #1 Both inputs are toggling L-H > (W/L)eff = 2(W/L)p H-L > (W/L)eff = 1/2(W/L)n KR|NAND = 1/4 KR|INV Vin Inverter V OH Scenario #2 One input is toggling L-H > (W/L)eff = (W/L)p H-L > (W/L)eff = 1/2(W/L)n KR|NAND = 1/2 KR|INV VLSI Design-EEE 453 A One input toggling Two inputs toggling Vin=Vout VOL Combinational-6 Vx 2 Vx 1 © D. Al-Khalili Vout 6

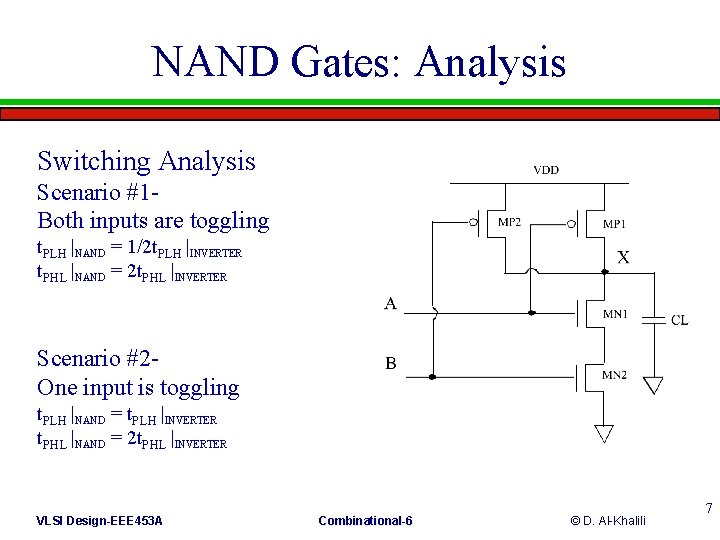

NAND Gates: Analysis Switching Analysis Scenario #1 Both inputs are toggling t. PLH |NAND = 1/2 t. PLH |INVERTER t. PHL |NAND = 2 t. PHL |INVERTER Scenario #2 One input is toggling t. PLH |NAND = t. PLH |INVERTER t. PHL |NAND = 2 t. PHL |INVERTER VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 7

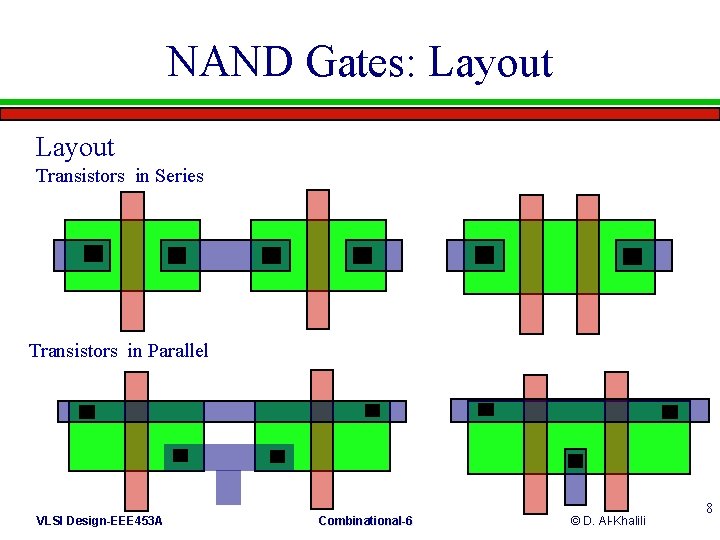

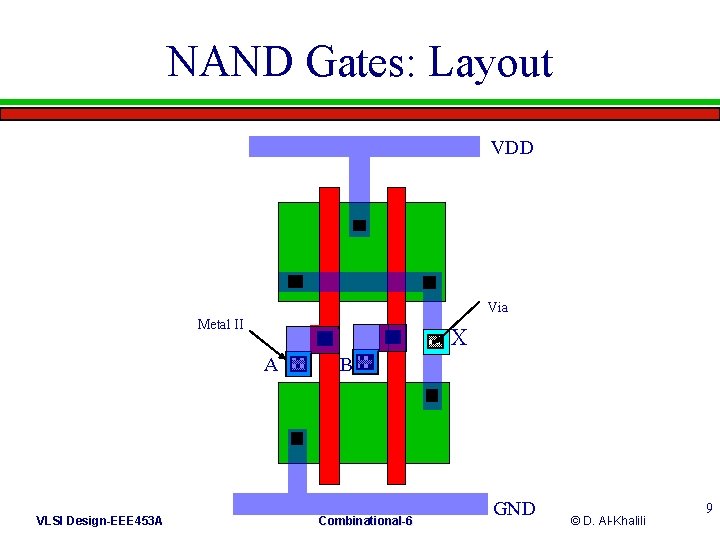

NAND Gates: Layout Transistors in Series Transistors in Parallel VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 8

NAND Gates: Layout VDD Via Metal II X A VLSI Design-EEE 453 A B Combinational-6 GND © D. Al-Khalili 9

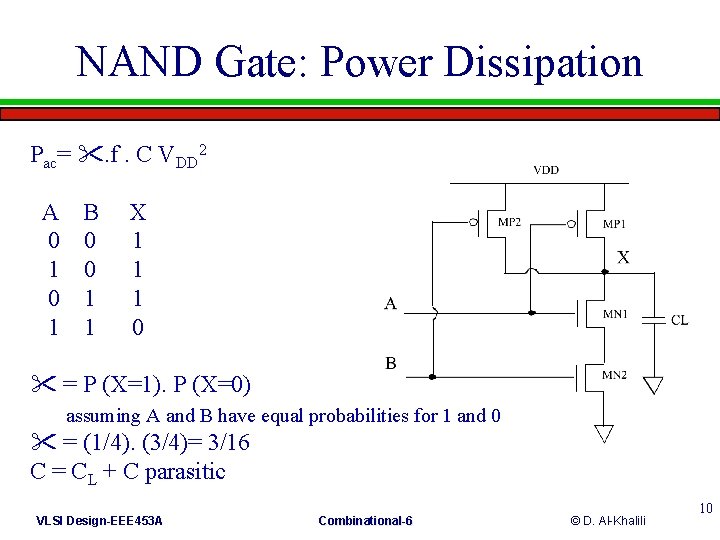

NAND Gate: Power Dissipation Pac= . f. C VDD 2 A B 0 0 1 1 1 X 1 1 1 0 = P (X=1). P (X=0) assuming A and B have equal probabilities for 1 and 0 = (1/4). (3/4)= 3/16 C = CL + C parasitic VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 10

AND Gate: Layout 1. Draw the schematic 2. Do the stick diagram 3. Optimize stick diagram 4. Generate Layout VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 11

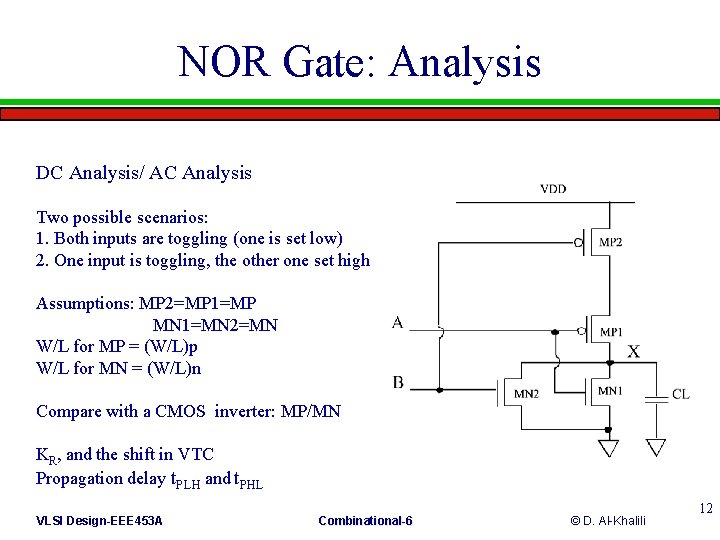

NOR Gate: Analysis DC Analysis/ AC Analysis Two possible scenarios: 1. Both inputs are toggling (one is set low) 2. One input is toggling, the other one set high Assumptions: MP 2=MP 1=MP MN 1=MN 2=MN W/L for MP = (W/L)p W/L for MN = (W/L)n Compare with a CMOS inverter: MP/MN KR, and the shift in VTC Propagation delay t. PLH and t. PHL VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 12

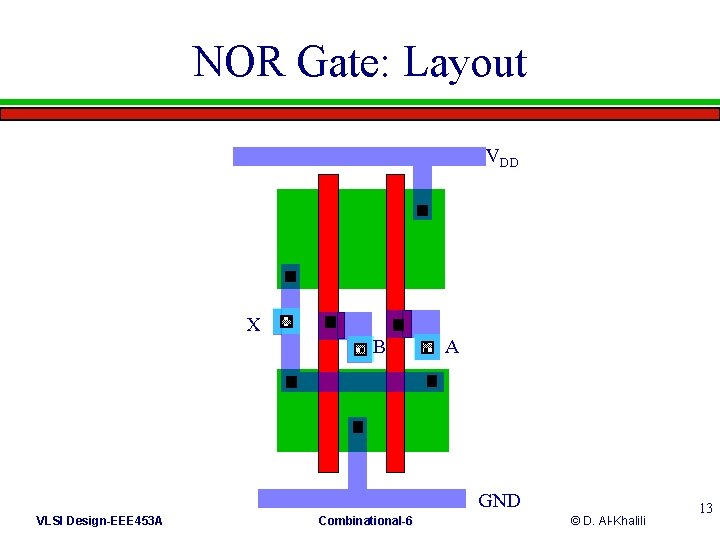

NOR Gate: Layout VDD X B A GND VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 13

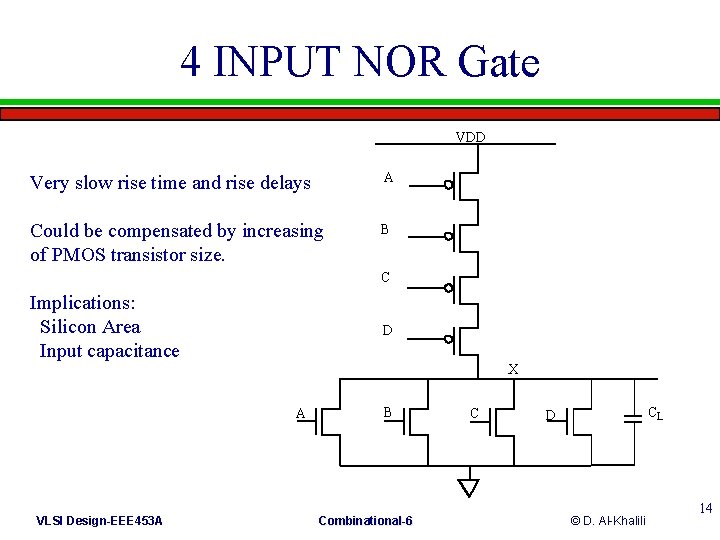

4 INPUT NOR Gate VDD Very slow rise time and rise delays A Could be compensated by increasing of PMOS transistor size. B C Implications: Silicon Area Input capacitance D X A VLSI Design-EEE 453 A B Combinational-6 C CL D © D. Al-Khalili 14

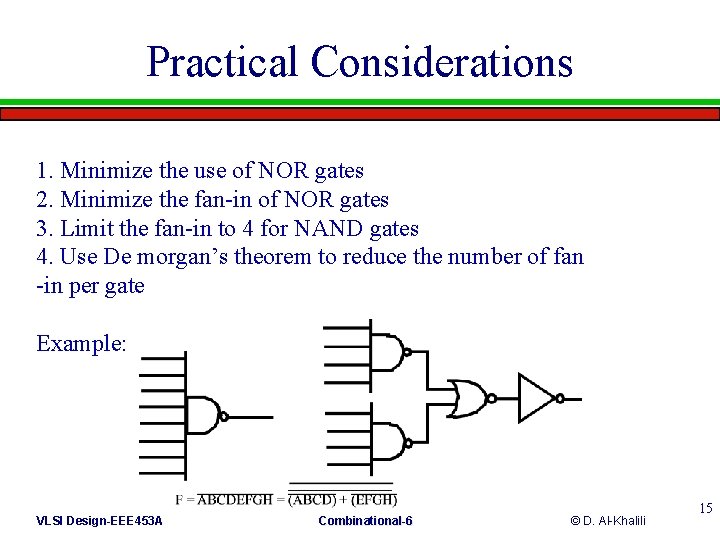

Practical Considerations 1. Minimize the use of NOR gates 2. Minimize the fan-in of NOR gates 3. Limit the fan-in to 4 for NAND gates 4. Use De morgan’s theorem to reduce the number of fan -in per gate Example: VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 15

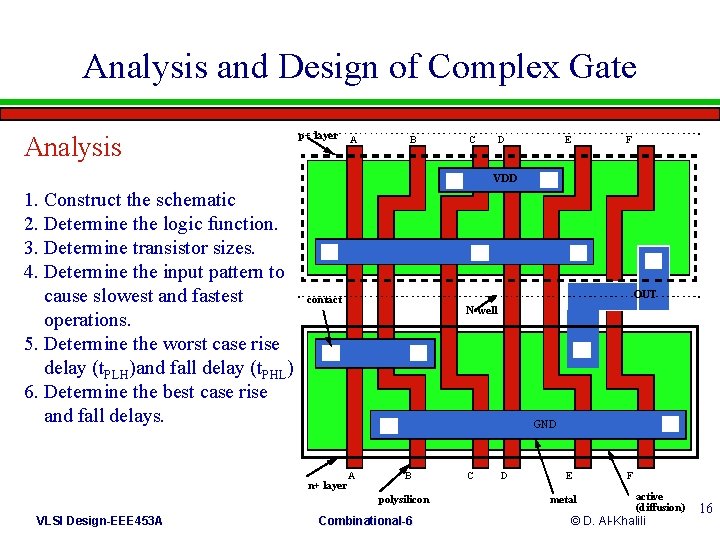

Analysis and Design of Complex Gate Analysis p+ layer A B C D E F VDD 1. Construct the schematic 2. Determine the logic function. 3. Determine transistor sizes. 4. Determine the input pattern to cause slowest and fastest operations. 5. Determine the worst case rise delay (t. PLH)and fall delay (t. PHL) 6. Determine the best case rise and fall delays. OUT contact N-well GND n+ layer A B polysilicon VLSI Design-EEE 453 A Combinational-6 C D E metal F active (diffusion) © D. Al-Khalili 16

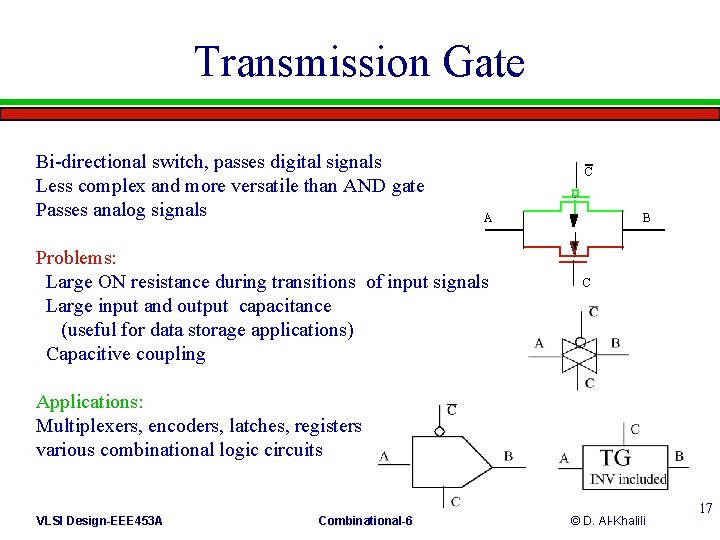

Transmission Gate Bi-directional switch, passes digital signals Less complex and more versatile than AND gate Passes analog signals C A Problems: Large ON resistance during transitions of input signals Large input and output capacitance (useful for data storage applications) Capacitive coupling B C Applications: Multiplexers, encoders, latches, registers various combinational logic circuits VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 17

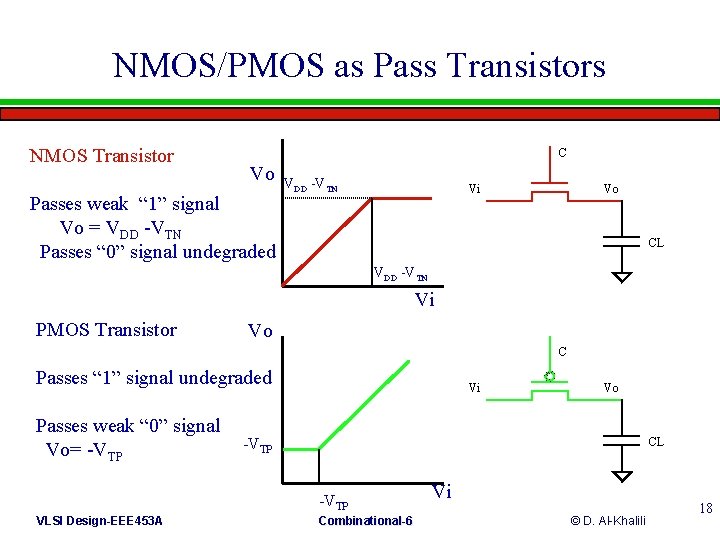

NMOS/PMOS as Pass Transistors NMOS Transistor C Vo Passes weak “ 1” signal Vo = VDD -VTN Passes “ 0” signal undegraded VDD -VTN Vi Vo CL VDD -VTN Vi PMOS Transistor Vo C Passes “ 1” signal undegraded Passes weak “ 0” signal Vo= -VTP Vi -VTP CL -VTP VLSI Design-EEE 453 A Vo Combinational-6 Vi © D. Al-Khalili 18

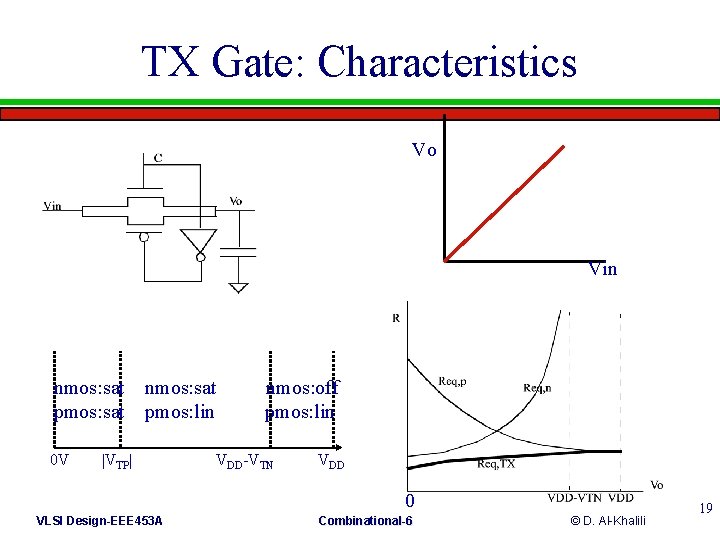

TX Gate: Characteristics Vo Vin nmos: sat pmos: sat 0 V nmos: sat pmos: lin |VTP| nmos: off pmos: lin VDD-VTN VDD 0 VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 19

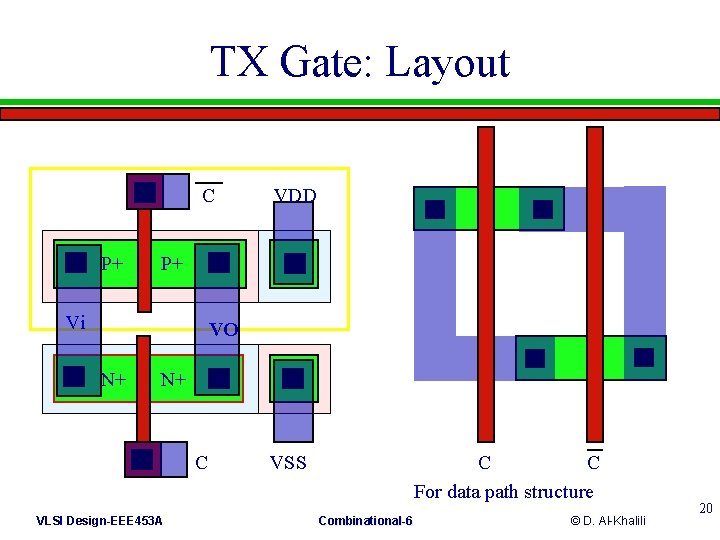

TX Gate: Layout C P+ VDD P+ Vi VO N+ N+ C VLSI Design-EEE 453 A VSS C C For data path structure Combinational-6 © D. Al-Khalili 20

TX Gate: Applications Exclusive OR 12 Transistors 8 Transistors Multiplexers Realization of Combinational Logic Functions VLSI Design-EEE 453 A Combinational-6 © D. Al-Khalili 21

- Slides: 21