Section 4 Fabrication and Layout Digital IC DesignATEC

Section 4 Fabrication and Layout Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 1

Fabrication- CMOS Process The Starting Material Preparation 1. Produce Metallurgical Grade Silicon (MGS) Si. O 2 (sand) + C in Arc Furnace Si- liquid 98% pure 2. Produce Electronic Grade Silicon (EGS) HCl + Si (MGS) Successive purification by distillation Chemical Vapor Deposition (CVD) Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 2

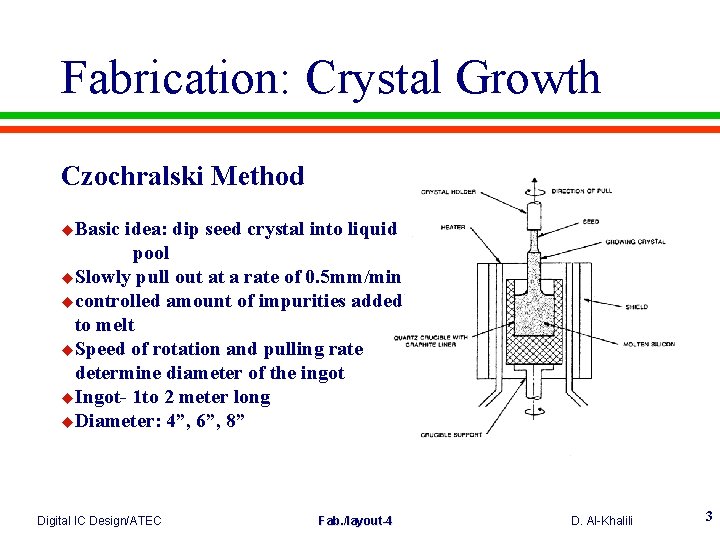

Fabrication: Crystal Growth Czochralski Method u. Basic idea: dip seed crystal into liquid pool u. Slowly pull out at a rate of 0. 5 mm/min ucontrolled amount of impurities added to melt u. Speed of rotation and pulling rate determine diameter of the ingot u. Ingot- 1 to 2 meter long u. Diameter: 4”, 6”, 8” Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 3

Fabrication: Wafering u Finish ingot to precise diameter u Mill “ flats” u Cut wafers by diamond saw: Typical thickness 0. 5 mm u Polish to give optically flat surface Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 4

Fabrication: Oxidation Quartz Tube u Silicon Dioxide has several uses: - mask against implant Pump or diffusion - device isolation - gate oxide - isolation between layers Wafers O 2 or Water Vapor Quartz Carrier u Si. O 2 could be thermally generated u or through CVD Resistance Heater u Oxidation consumes silicon u Wet or dry oxidation Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 5

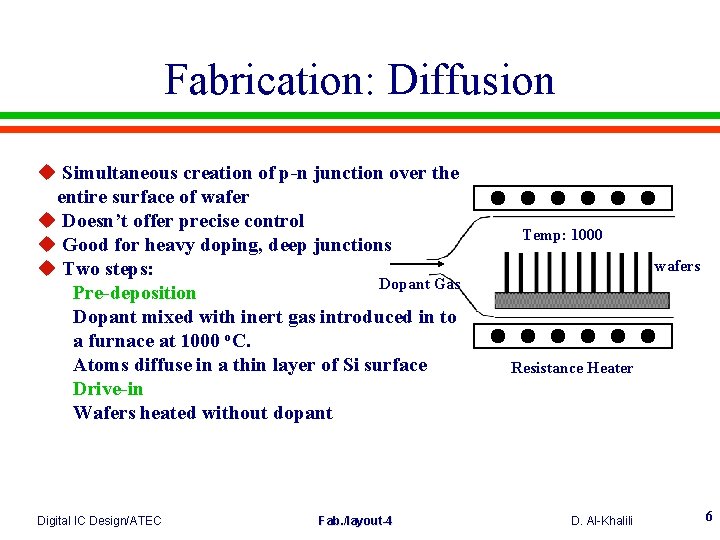

Fabrication: Diffusion u Simultaneous creation of p-n junction over the entire surface of wafer u Doesn’t offer precise control u Good for heavy doping, deep junctions u Two steps: Dopant Gas Pre-deposition Dopant mixed with inert gas introduced in to a furnace at 1000 o. C. Atoms diffuse in a thin layer of Si surface Drive-in Wafers heated without dopant Digital IC Design/ATEC Fab. /layout-4 Temp: 1000 wafers Resistance Heater D. Al-Khalili 6

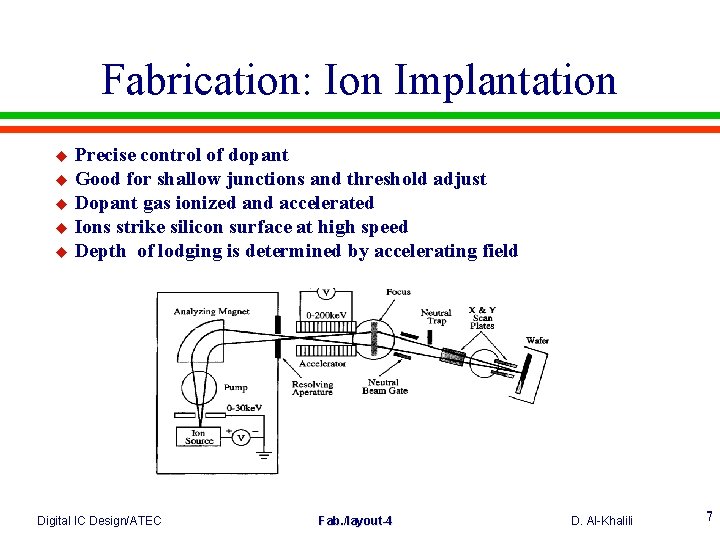

Fabrication: Ion Implantation Precise control of dopant u Good for shallow junctions and threshold adjust u Dopant gas ionized and accelerated u Ions strike silicon surface at high speed u Depth of lodging is determined by accelerating field u Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 7

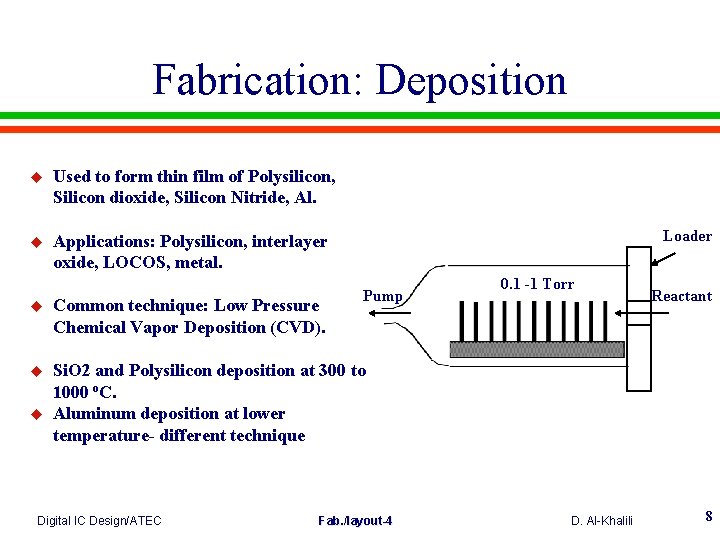

Fabrication: Deposition u Used to form thin film of Polysilicon, Silicon dioxide, Silicon Nitride, Al. u Applications: Polysilicon, interlayer oxide, LOCOS, metal. Loader Pump u Common technique: Low Pressure Chemical Vapor Deposition (CVD). u Si. O 2 and Polysilicon deposition at 300 to 1000 o. C. Aluminum deposition at lower temperature- different technique u Digital IC Design/ATEC Fab. /layout-4 0. 1 -1 Torr D. Al-Khalili Reactant 8

Fabrication: Metallization u Standard material is Aluminum u Low contact resistance to p-type and n-type u When deposited on Si. O 2, Al 2 O 3 is formed: good adhesive u All wafer covered with Al u Deposition techniques: Vacuum Evaporation Electron Beam Evaporation RF Sputtering u Other materials used in conjunction with or replacement to Al Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 9

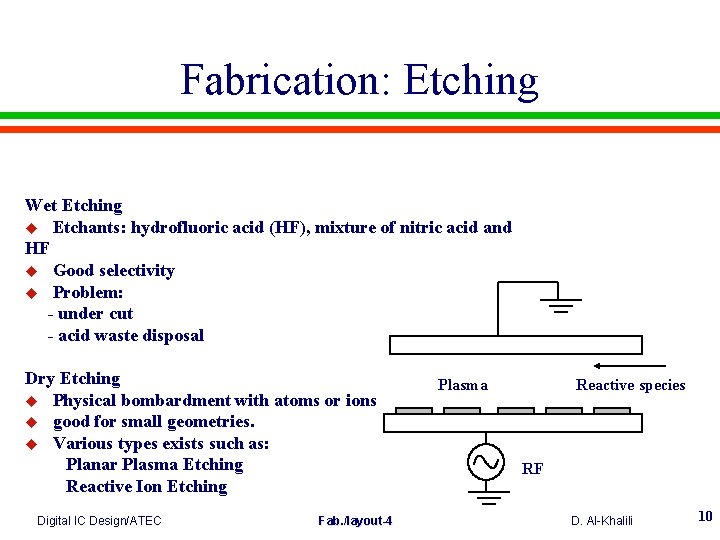

Fabrication: Etching Wet Etching u Etchants: hydrofluoric acid (HF), mixture of nitric acid and HF u Good selectivity u Problem: - under cut - acid waste disposal Dry Etching u Physical bombardment with atoms or ions u good for small geometries. u Various types exists such as: Planar Plasma Etching Reactive Ion Etching Digital IC Design/ATEC Fab. /layout-4 Plasma Reactive species RF D. Al-Khalili 10

Fabrication: Lithography Mask making u Most critical part of lithography is conversion from layout to master mask u Masking plate has opaque geometrical shapes corresponding to the area on the wafer surface where certain photochemical reactions have to be prevented or taken place. u Masks uses photographic emulsion or hard surface u Two types: dark field or clear field u Maskmaking: optical or e-beam Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 11

Lithography: Mask making Optical Mask Technique 1. Prepare Reticle Use projection like system: -Precise movable stage -Aperture of precisely rectangular size and angular orientation -Computer controlled UV light source directed to photographic plate After flashing, plate is developed yielding reticle Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 12

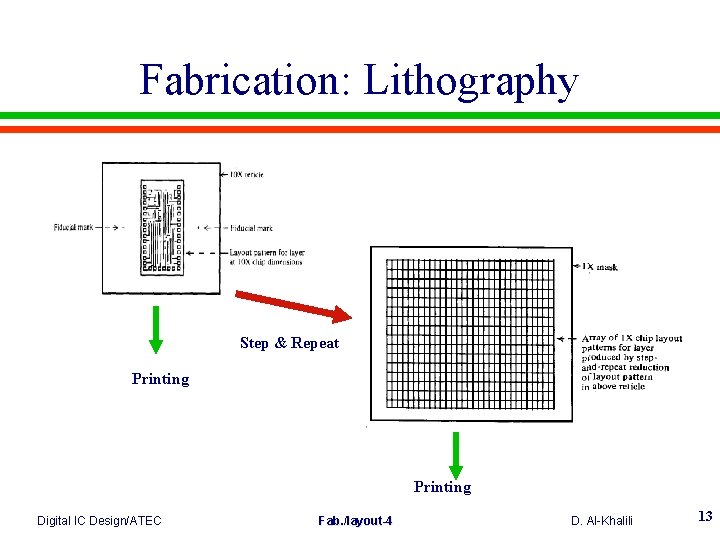

Fabrication: Lithography Step & Repeat Printing Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 13

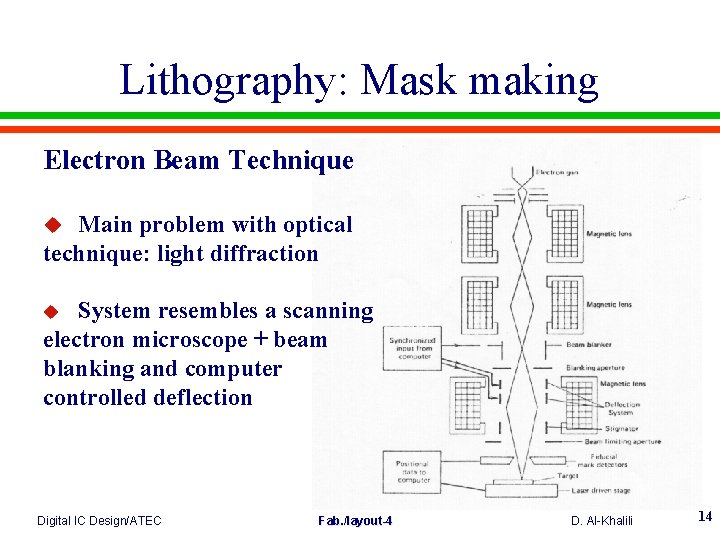

Lithography: Mask making Electron Beam Technique u Main problem with optical technique: light diffraction System resembles a scanning electron microscope + beam blanking and computer controlled deflection u Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 14

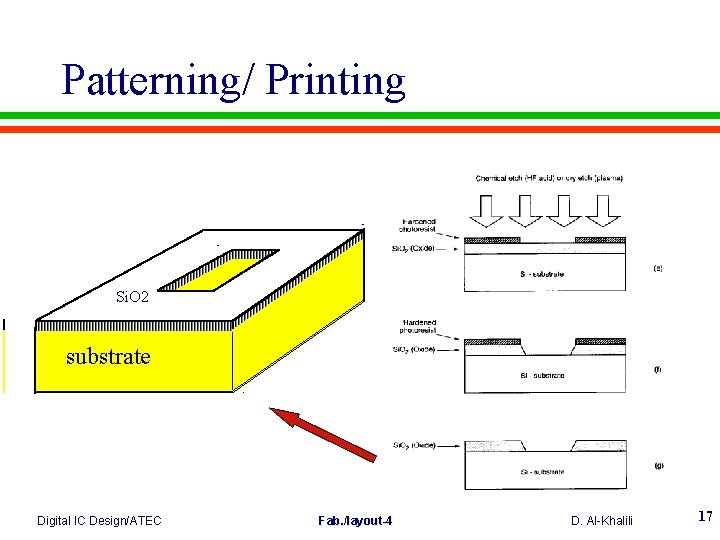

Patterning/ Printing Process of transferring mask features to surface of the silicon wafer. u Optical or Electron-beam u Photo-resist material (negative or positive): synthetic rubber or polymer upon exposure to light becomes insoluble ( negative ) or volatile (positive) u Developer: typically organic solvant-e. g. Xylen u u A common step in many processes is the creation and selective removal of Silicon Dioxide Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 15

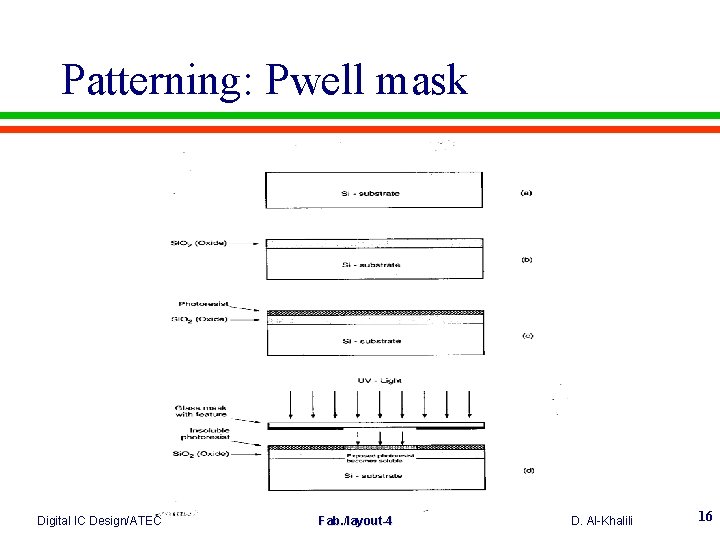

Patterning: Pwell mask Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 16

Patterning/ Printing Si. O 2 substrate Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 17

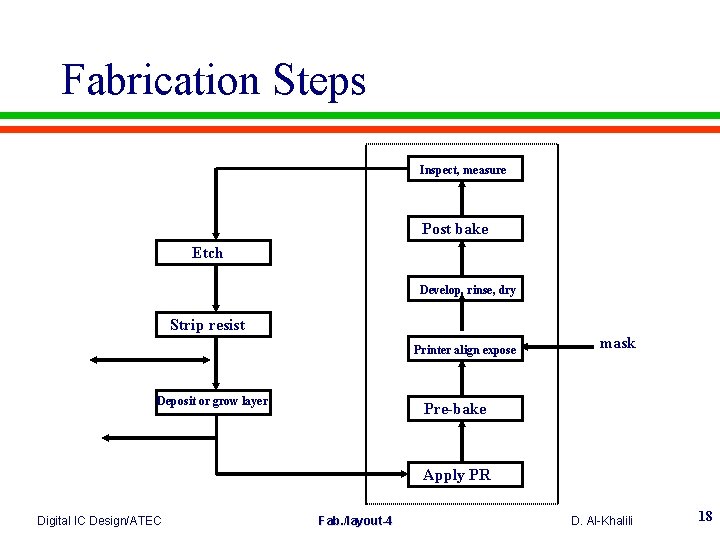

Fabrication Steps Inspect, measure Post bake Etch Develop, rinse, dry Strip resist Printer align expose Deposit or grow layer mask Pre-bake Apply PR Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 18

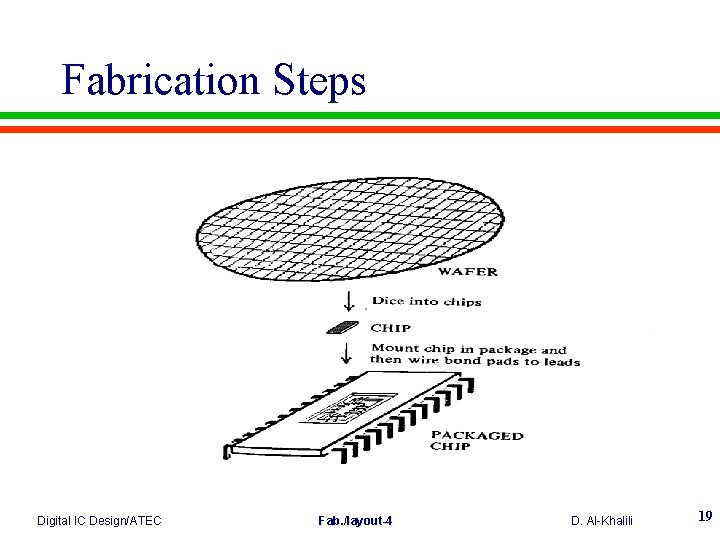

Fabrication Steps Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 19

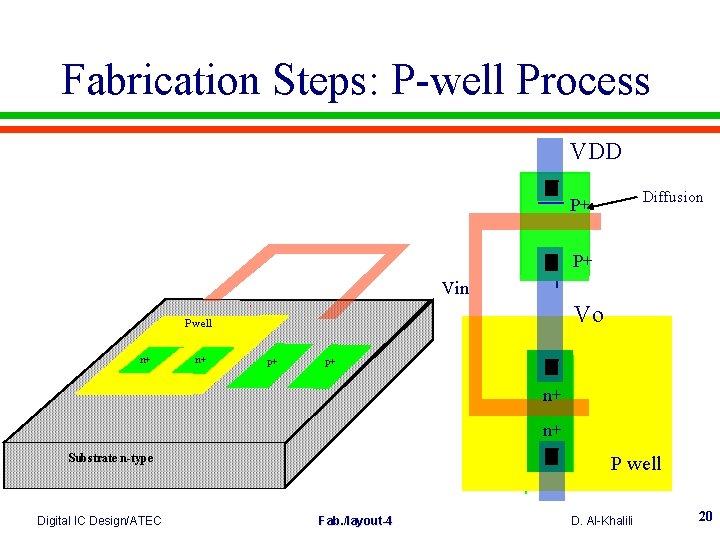

Fabrication Steps: P-well Process VDD Diffusion P+ P+ Vin Vo P well n+ n+ p+ p+ n+ n+ Substrate n-type Digital IC Design/ATEC P well Fab. /layout-4 D. Al-Khalili 20

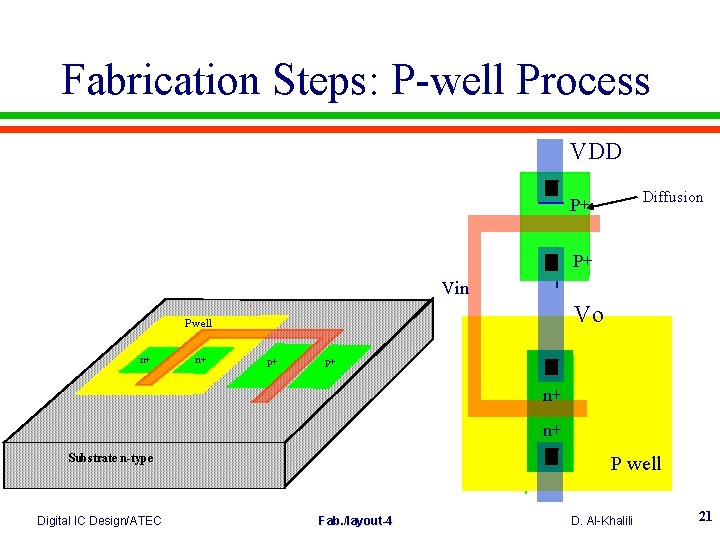

Fabrication Steps: P-well Process VDD Diffusion P+ P+ Vin Vo P well n+ n+ p+ p+ n+ n+ Substrate n-type Digital IC Design/ATEC P well Fab. /layout-4 D. Al-Khalili 21

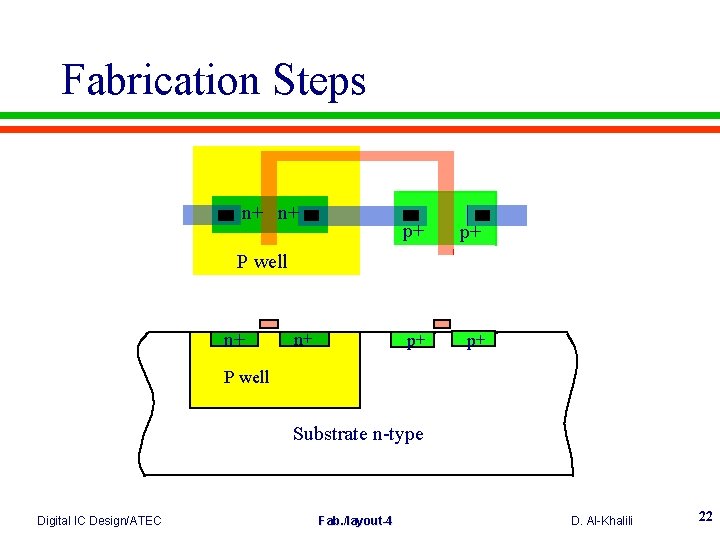

Fabrication Steps n+ n+ p+ p+ P well n+ n+ P well Substrate n-type Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 22

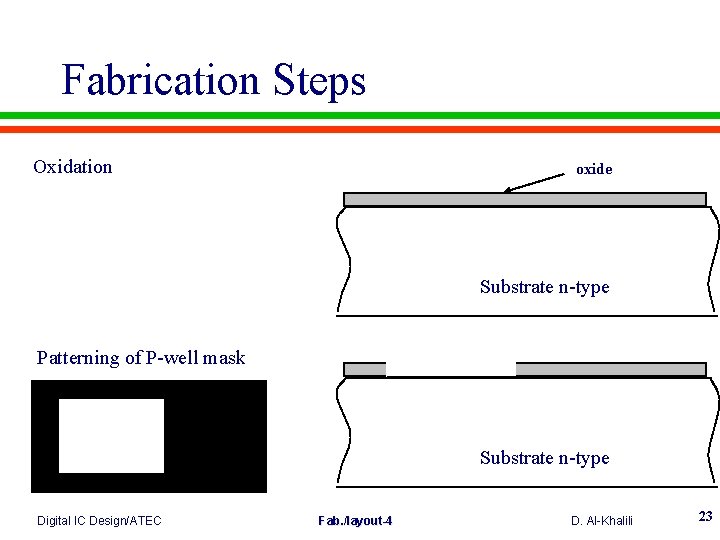

Fabrication Steps Oxidation oxide Substrate n-type Patterning of P-well mask Substrate n-type Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 23

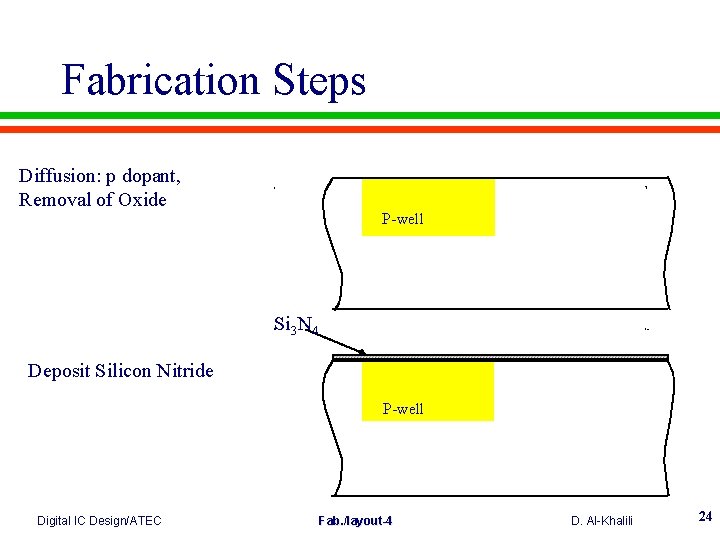

Fabrication Steps Diffusion: p dopant, Removal of Oxide P-well Si 3 N 4 Deposit Silicon Nitride P-well Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 24

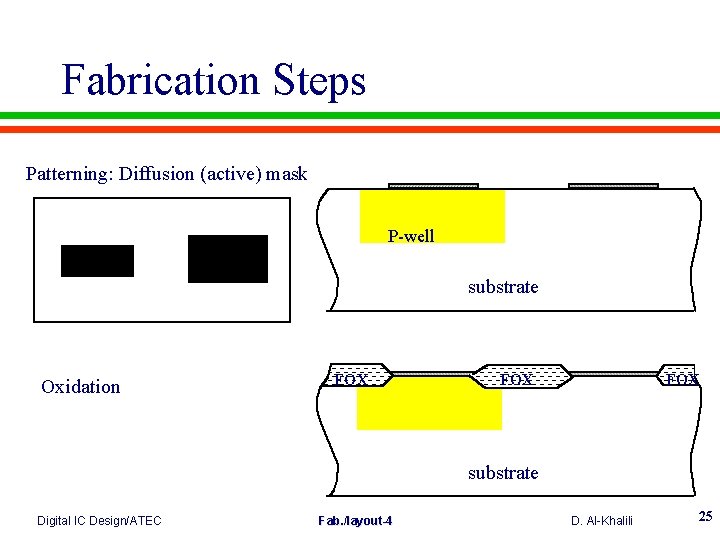

Fabrication Steps Patterning: Diffusion (active) mask P-well substrate Oxidation FOX FOX substrate Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 25

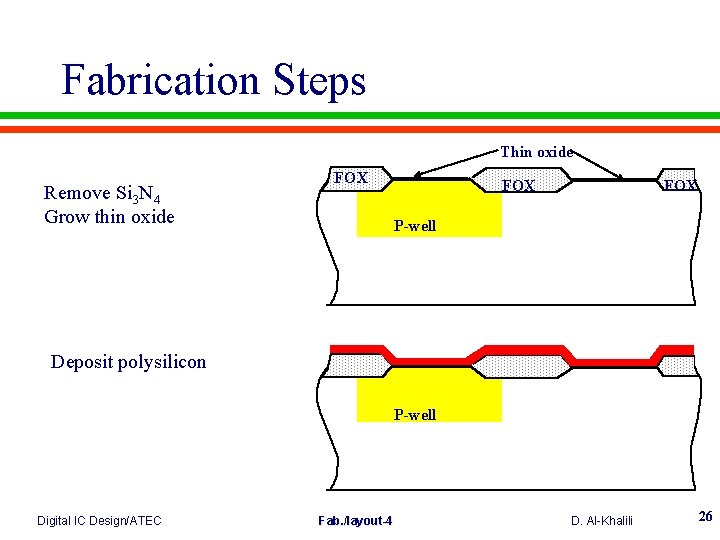

Fabrication Steps Thin oxide Remove Si 3 N 4 Grow thin oxide FOX FOX P-well Deposit polysilicon P-well Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 26

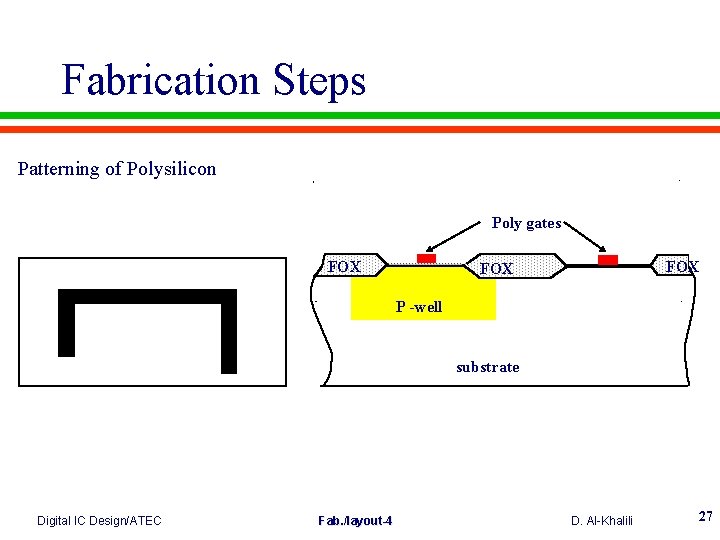

Fabrication Steps Patterning of Polysilicon Poly gates FOX FOX P -well substrate Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 27

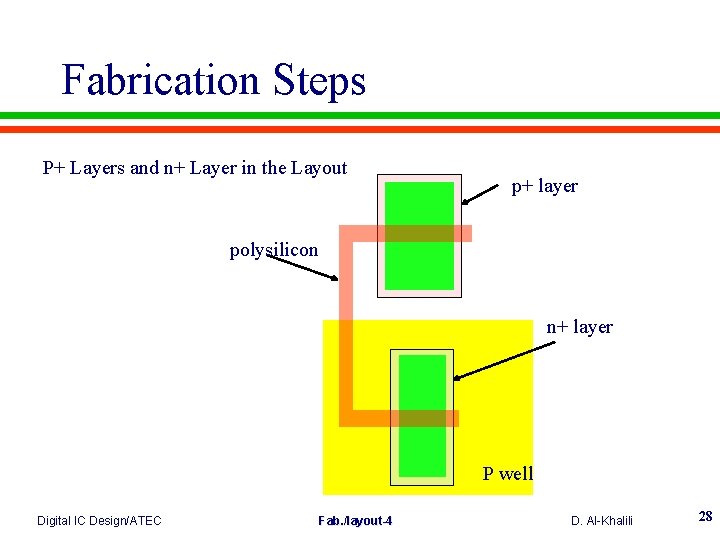

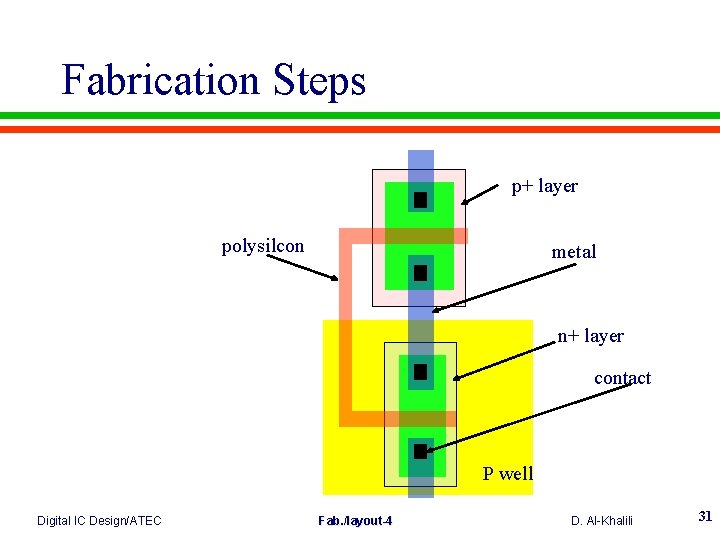

Fabrication Steps P+ Layers and n+ Layer in the Layout p+ layer polysilicon n+ layer P well Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 28

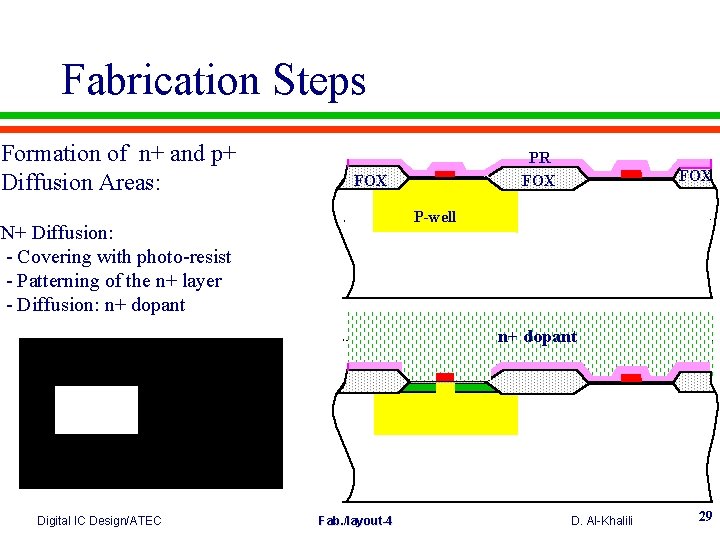

Fabrication Steps Formation of n+ and p+ Diffusion Areas: PR FOX FOX P-well N+ Diffusion: - Covering with photo-resist - Patterning of the n+ layer - Diffusion: n+ dopant Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 29

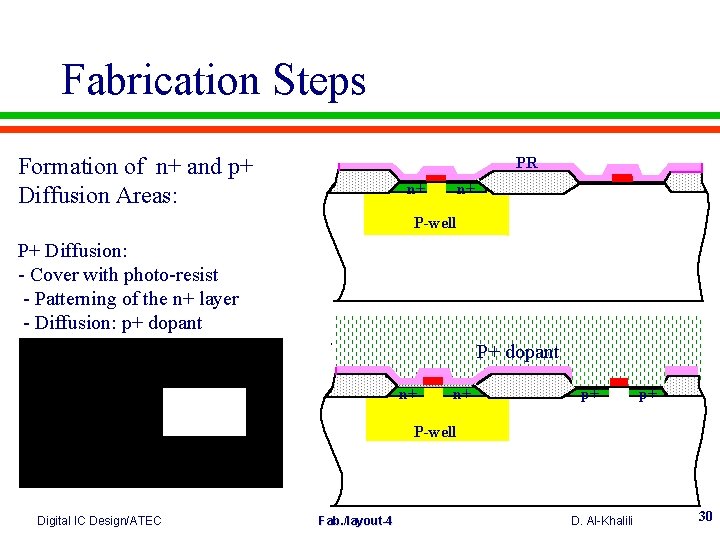

Fabrication Steps Formation of n+ and p+ Diffusion Areas: PR n+ n+ P-well P+ Diffusion: - Cover with photo-resist - Patterning of the n+ layer - Diffusion: p+ dopant P+ dopant n+ n+ p+ p+ P-well Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 30

Fabrication Steps p+ layer polysilcon metal n+ layer contact P well Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 31

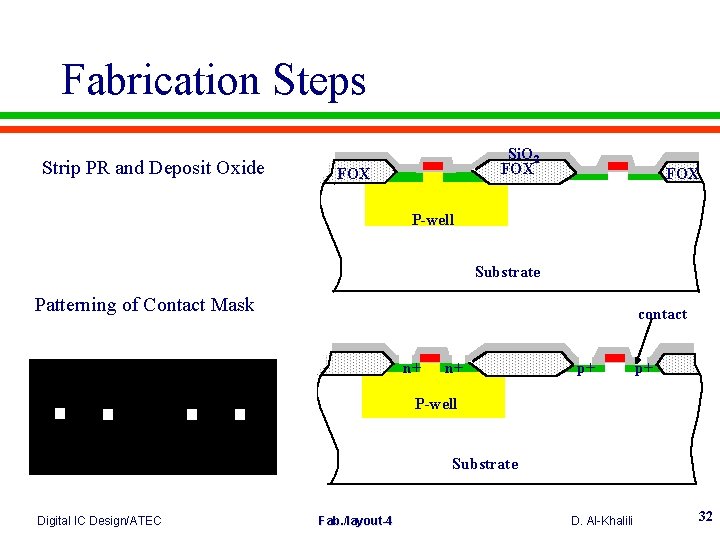

Fabrication Steps Strip PR and Deposit Oxide Si. O 2 FOX FOX P-well Substrate Patterning of Contact Mask contact n+ n+ p+ p+ P-well Substrate Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 32

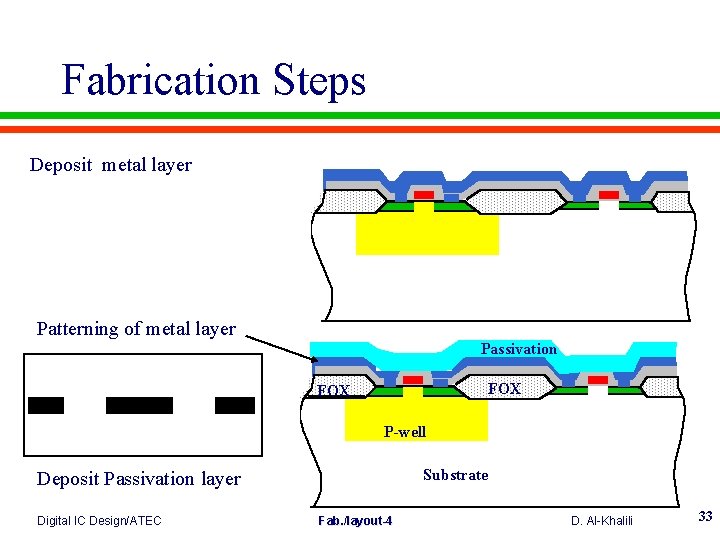

Fabrication Steps Deposit metal layer Patterning of metal layer Passivation FOX P-well Substrate Deposit Passivation layer Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 33

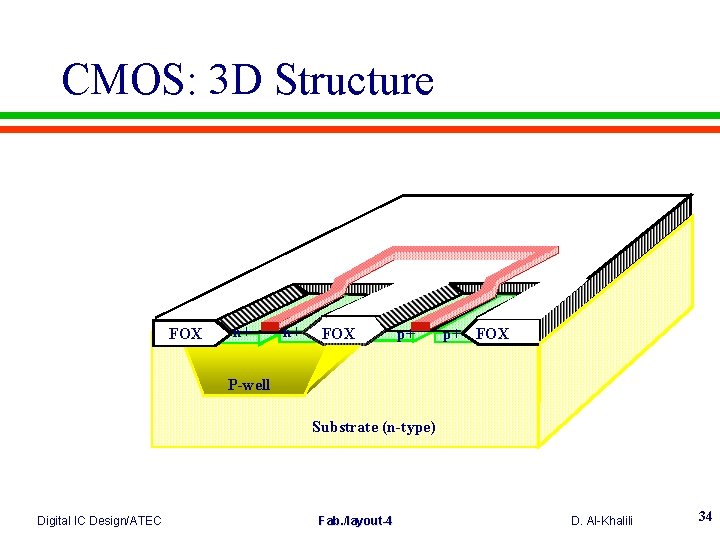

CMOS: 3 D Structure FOX n+ n+ FOX p+ p+ FOX P-well Substrate (n-type) Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 34

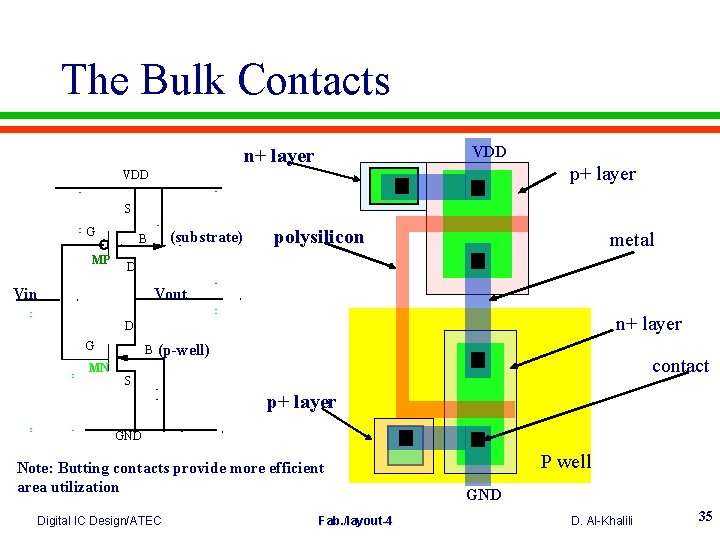

The Bulk Contacts VDD n+ layer p+ layer VDD S G MP (substrate) B polysilicon metal D Vin Vout n+ layer D G MN B (p-well) contact S p+ layer GND Note: Butting contacts provide more efficient area utilization Digital IC Design/ATEC Fab. /layout-4 P well GND D. Al-Khalili 35

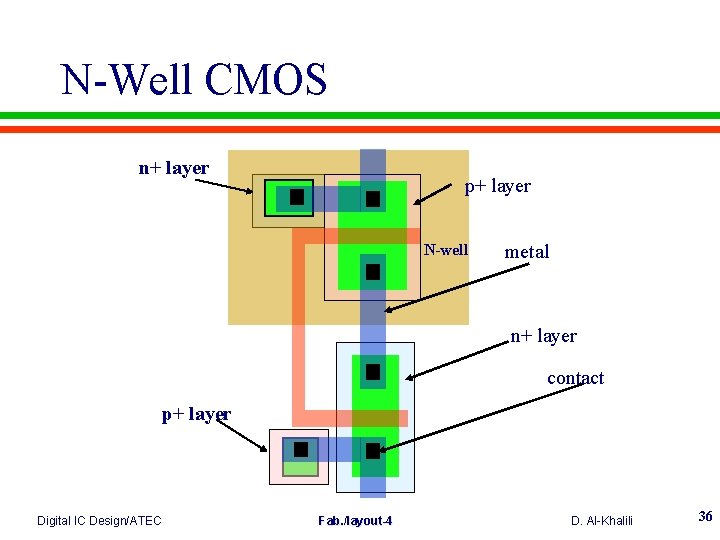

N-Well CMOS n+ layer p+ layer N-well metal n+ layer contact p+ layer Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 36

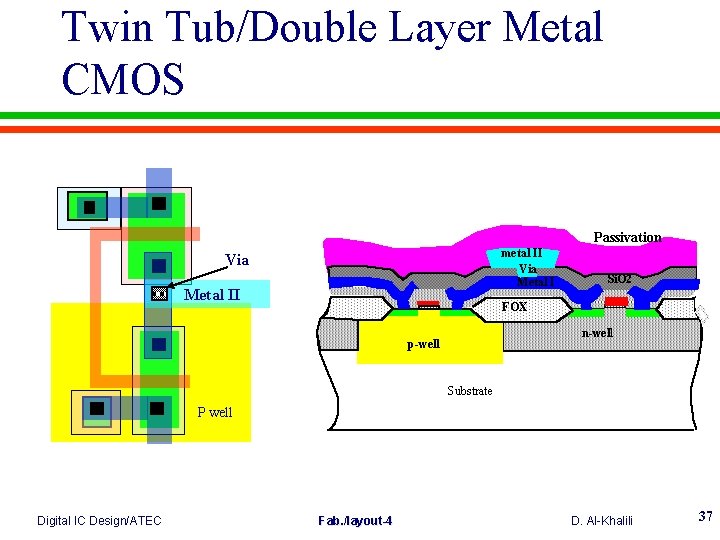

Twin Tub/Double Layer Metal CMOS Passivation metal II Via Metal II Si. O 2 FOX n-well p-well Substrate P well Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 37

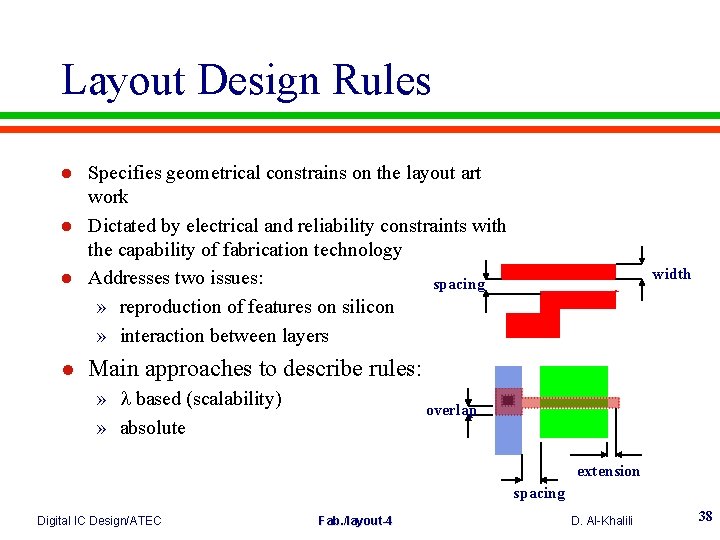

Layout Design Rules l l Specifies geometrical constrains on the layout art work Dictated by electrical and reliability constraints with the capability of fabrication technology Addresses two issues: spacing » reproduction of features on silicon » interaction between layers width Main approaches to describe rules: » based (scalability) » absolute overlap extension spacing Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 38

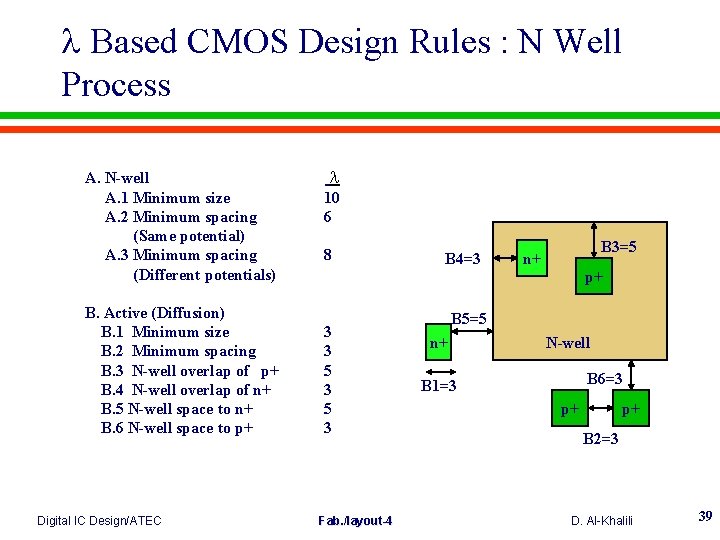

Based CMOS Design Rules : N Well Process A. N-well A. 1 Minimum size A. 2 Minimum spacing (Same potential) A. 3 Minimum spacing (Different potentials) B. Active (Diffusion) B. 1 Minimum size B. 2 Minimum spacing B. 3 N-well overlap of p+ B. 4 N-well overlap of n+ B. 5 N-well space to n+ B. 6 N-well space to p+ Digital IC Design/ATEC 10 6 8 B 4=3 B 3=5 n+ p+ 3 3 5 3 Fab. /layout-4 B 5=5 n+ N-well B 6=3 B 1=3 p+ p+ B 2=3 D. Al-Khalili 39

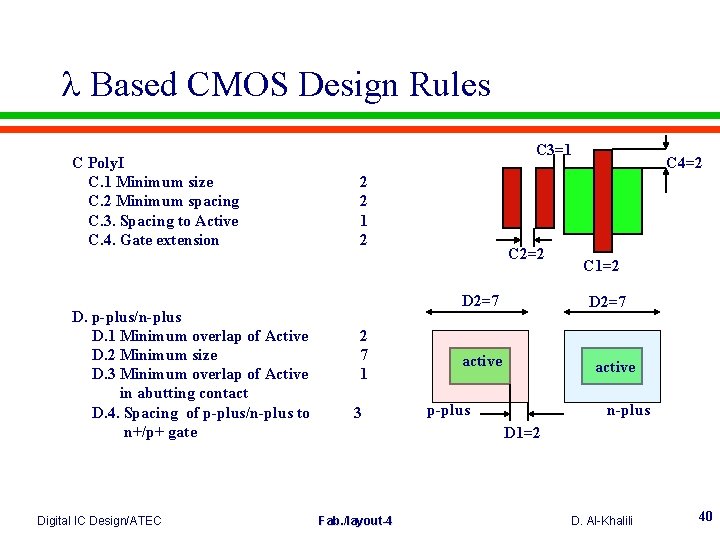

Based CMOS Design Rules C Poly. I C. 1 Minimum size C. 2 Minimum spacing C. 3. Spacing to Active C. 4. Gate extension D. p-plus/n-plus D. 1 Minimum overlap of Active D. 2 Minimum size D. 3 Minimum overlap of Active in abutting contact D. 4. Spacing of p-plus/n-plus to n+/p+ gate Digital IC Design/ATEC C 3=1 2 2 1 2 C 2=2 D 2=7 2 7 1 3 C 4=2 C 1=2 D 2=7 active p-plus n-plus D 1=2 Fab. /layout-4 D. Al-Khalili 40

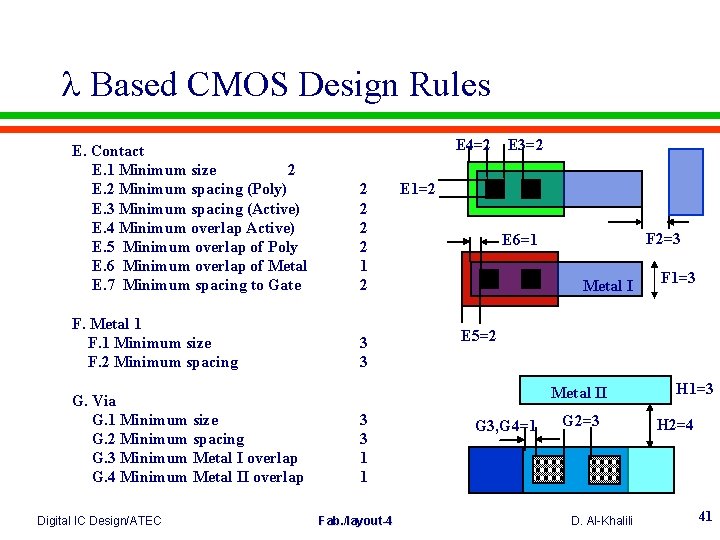

Based CMOS Design Rules E 4=2 E. Contact E. 1 Minimum size 2 E. 2 Minimum spacing (Poly) E. 3 Minimum spacing (Active) E. 4 Minimum overlap Active) E. 5 Minimum overlap of Poly E. 6 Minimum overlap of Metal E. 7 Minimum spacing to Gate 2 2 1 2 F. Metal 1 F. 1 Minimum size F. 2 Minimum spacing 3 3 G. Via G. 1 Minimum size G. 2 Minimum spacing G. 3 Minimum Metal I overlap G. 4 Minimum Metal II overlap Digital IC Design/ATEC E 3=2 E 1=2 F 2=3 E 6=1 Metal I E 5=2 Metal II 3 3 1 1 Fab. /layout-4 F 1=3 G 3, G 4=1 G 2=3 D. Al-Khalili H 1=3 H 2=4 41

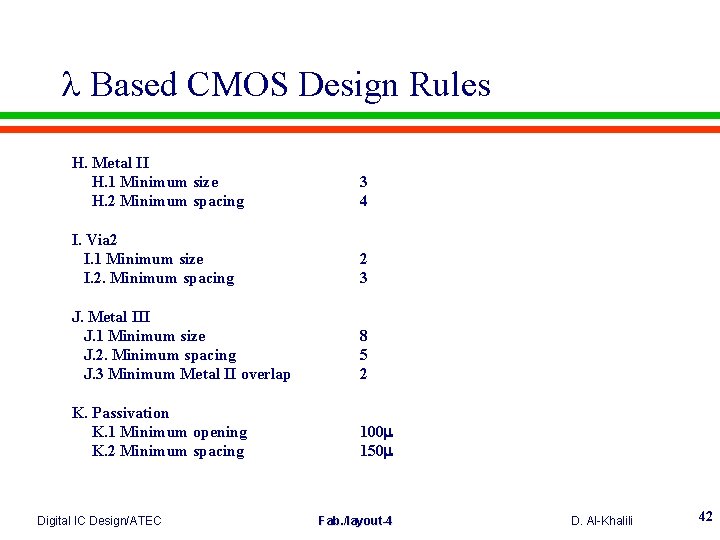

Based CMOS Design Rules H. Metal II H. 1 Minimum size H. 2 Minimum spacing 3 4 I. Via 2 I. 1 Minimum size I. 2. Minimum spacing 2 3 J. Metal III J. 1 Minimum size J. 2. Minimum spacing J. 3 Minimum Metal II overlap 8 5 2 K. Passivation K. 1 Minimum opening K. 2 Minimum spacing 100 m 150 m Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 42

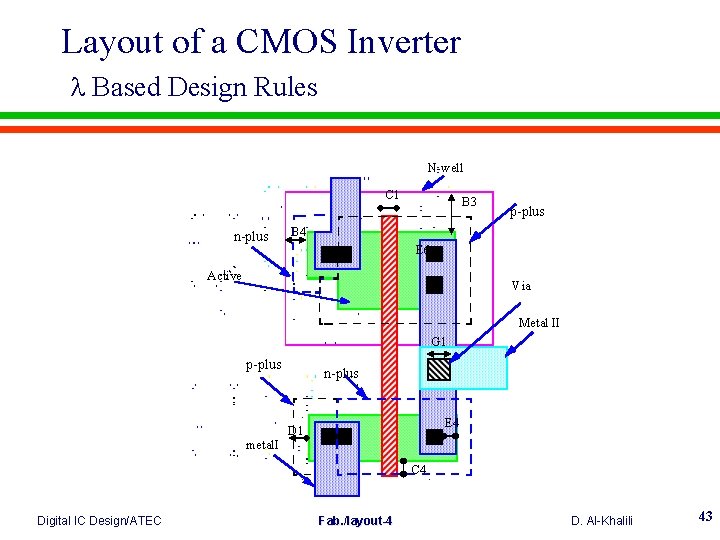

Layout of a CMOS Inverter Based Design Rules N-well C 1 n-plus B 3 p-plus B 4 E 6 Active Via Metal II G 1 p-plus metal. I n-plus E 4 D 1 C 4 Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 43

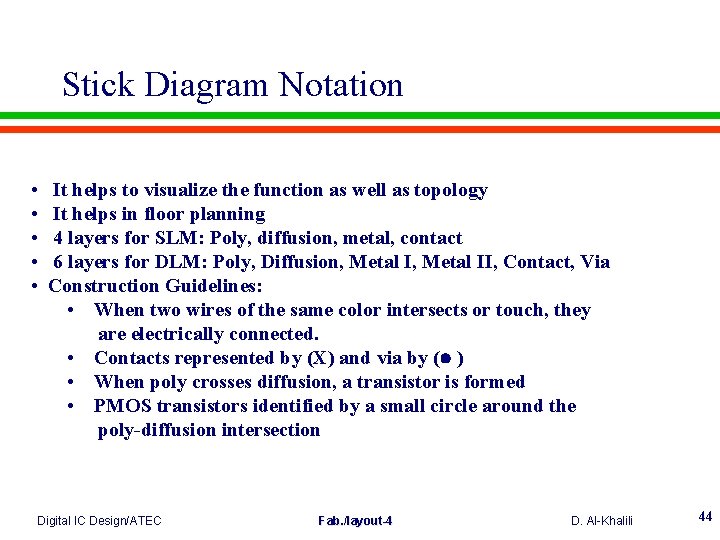

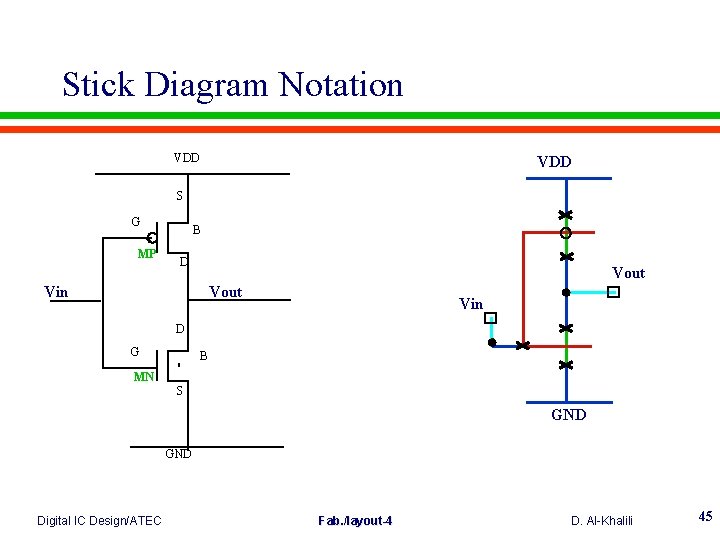

Stick Diagram Notation • • • It helps to visualize the function as well as topology It helps in floor planning 4 layers for SLM: Poly, diffusion, metal, contact 6 layers for DLM: Poly, Diffusion, Metal II, Contact, Via Construction Guidelines: • When two wires of the same color intersects or touch, they are electrically connected. • Contacts represented by (X) and via by ( ) • When poly crosses diffusion, a transistor is formed • PMOS transistors identified by a small circle around the poly-diffusion intersection Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 44

Stick Diagram Notation VDD S G MP B D Vout Vin D G B MN S GND Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 45

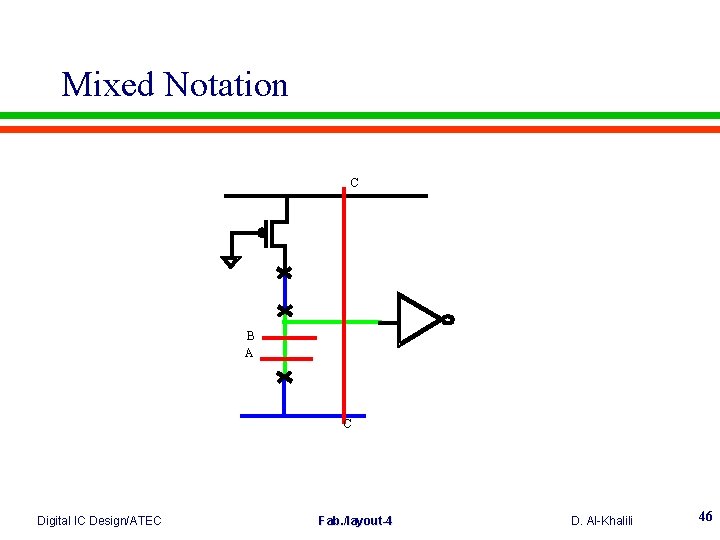

Mixed Notation C B A C Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 46

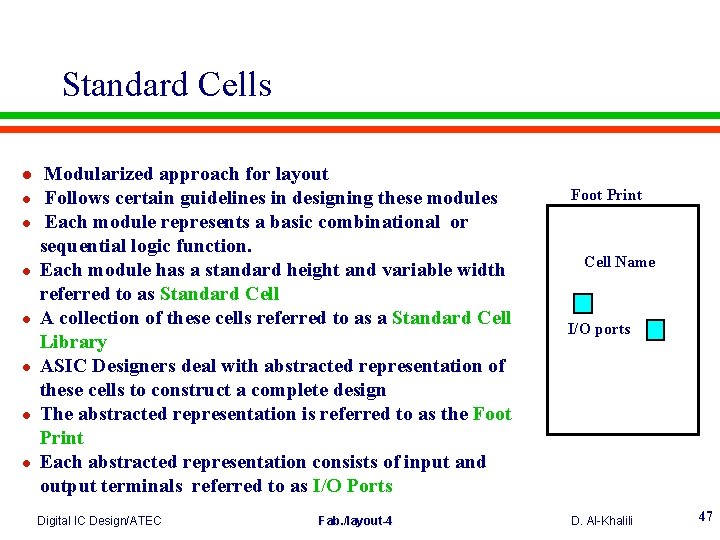

Standard Cells l l l l Modularized approach for layout Follows certain guidelines in designing these modules Each module represents a basic combinational or sequential logic function. Each module has a standard height and variable width referred to as Standard Cell A collection of these cells referred to as a Standard Cell Library ASIC Designers deal with abstracted representation of these cells to construct a complete design The abstracted representation is referred to as the Foot Print Each abstracted representation consists of input and output terminals referred to as I/O Ports I/O ports Digital IC Design/ATEC D. Al-Khalili Fab. /layout-4 Foot Print Cell Name 47

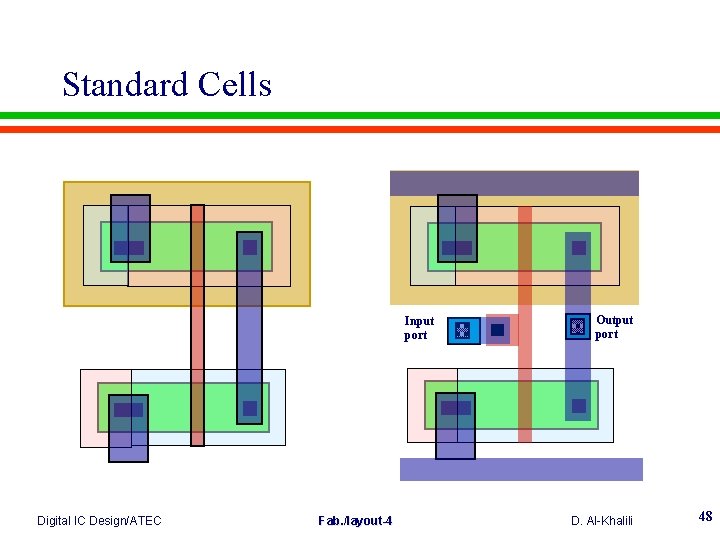

Standard Cells Input port Digital IC Design/ATEC Fab. /layout-4 Output port D. Al-Khalili 48

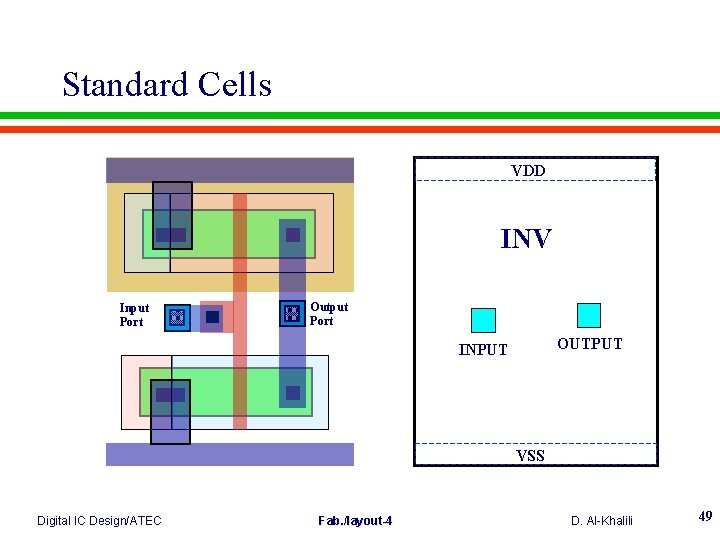

Standard Cells VDD INV Input Port Output Port OUTPUT INPUT VSS Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 49

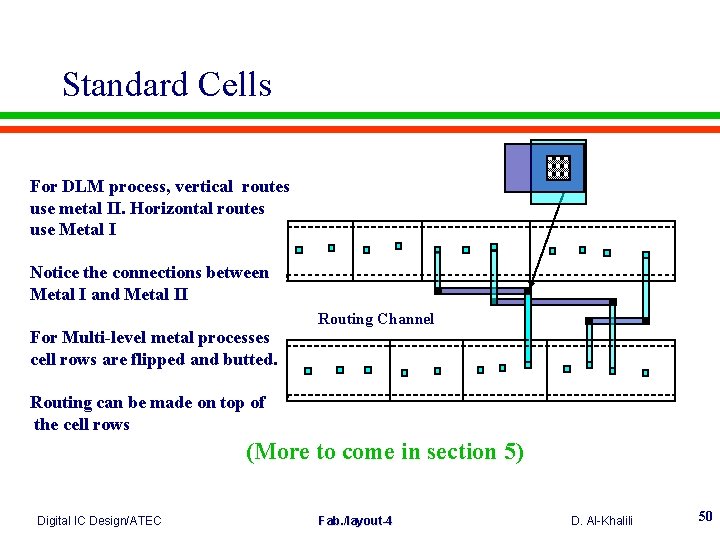

Standard Cells For DLM process, vertical routes use metal II. Horizontal routes use Metal I Notice the connections between Metal I and Metal II For Multi-level metal processes cell rows are flipped and butted. Routing Channel Routing can be made on top of the cell rows (More to come in section 5) Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 50

Yield Analysis Yield is defined as : Number of Good chips on wafer Total Number of chips X 100% Influenced by Defect density Chip area Design rule lithography dimensions Number of mask levels Defects Crystal defects film deposition and growth defects photo-resist imperfections Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 51

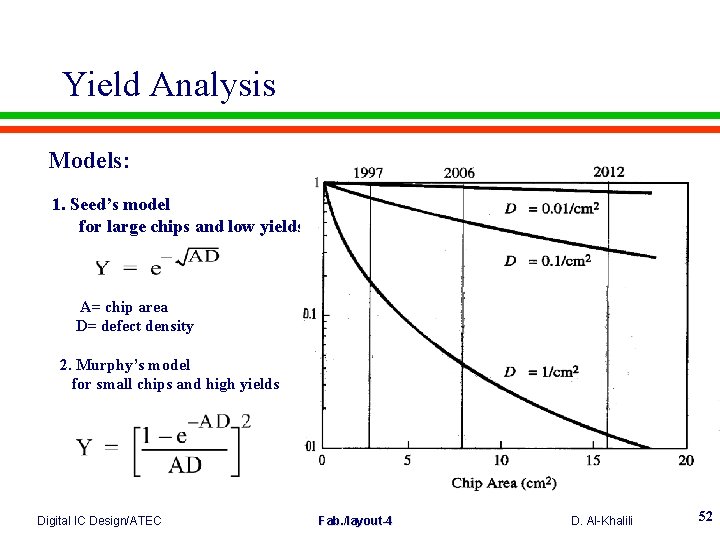

Yield Analysis Models: 1. Seed’s model for large chips and low yields A= chip area D= defect density 2. Murphy’s model for small chips and high yields Digital IC Design/ATEC Fab. /layout-4 D. Al-Khalili 52

- Slides: 52