SDRAM Memory Controller z Static RAM Technology y

- Slides: 21

SDRAM Memory Controller z Static RAM Technology y 6 T Memory Cell y Memory Access Timing z Dynamic RAM Technology y 1 T Memory Cell y Memory Access Timing CS 150 - Spring 2007 – Lec #10: Memory Controller - 1

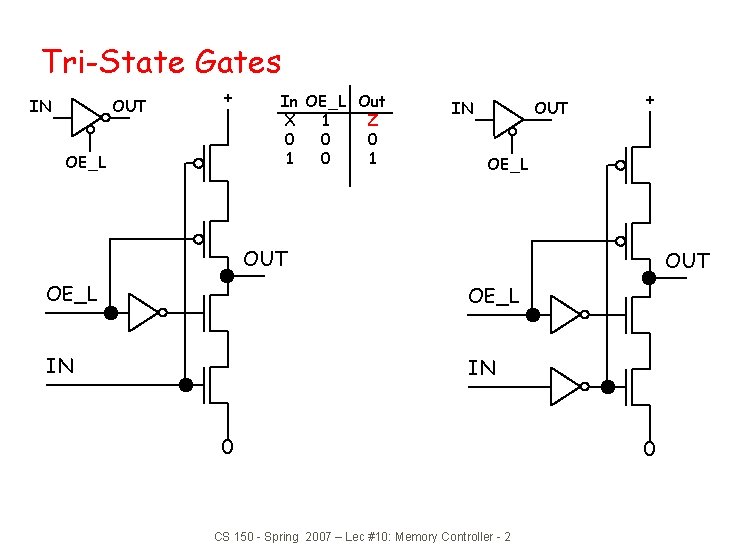

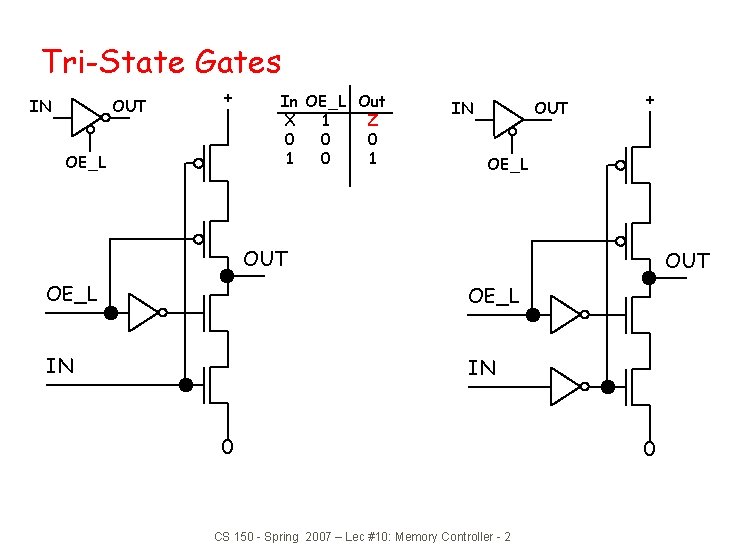

Tri-State Gates IN OUT + OE_L In OE_L Out X 1 Z 0 0 0 1 IN OUT + OE_L OUT OE_L IN IN 0 CS 150 - Spring 2007 – Lec #10: Memory Controller - 2 0

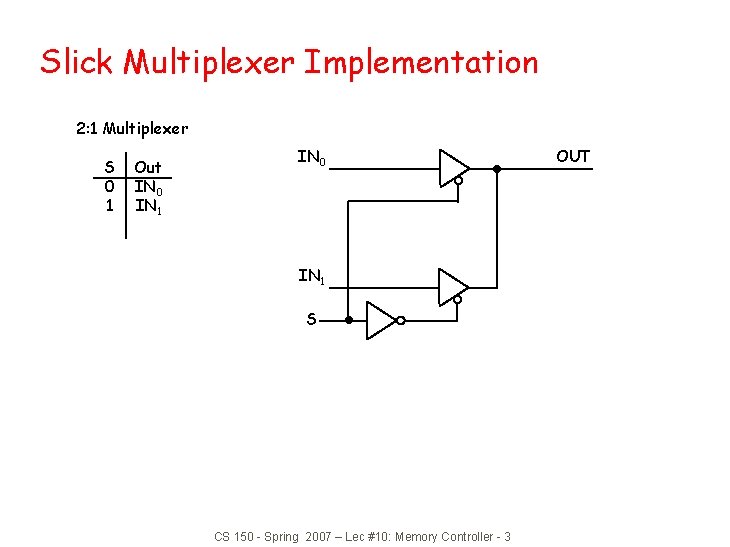

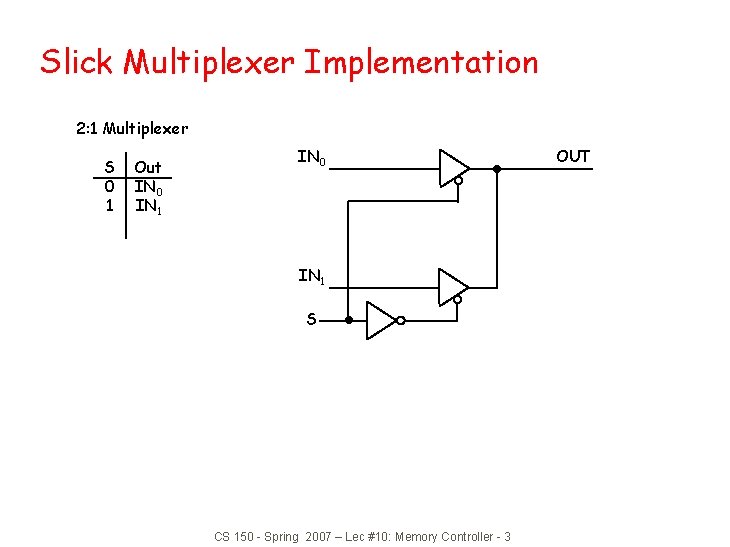

Slick Multiplexer Implementation 2: 1 Multiplexer S 0 1 Out IN 0 IN 1 S CS 150 - Spring 2007 – Lec #10: Memory Controller - 3 OUT

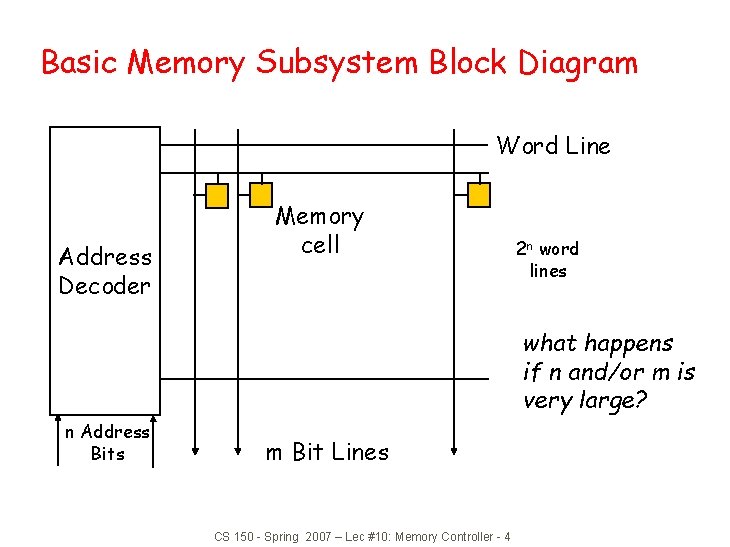

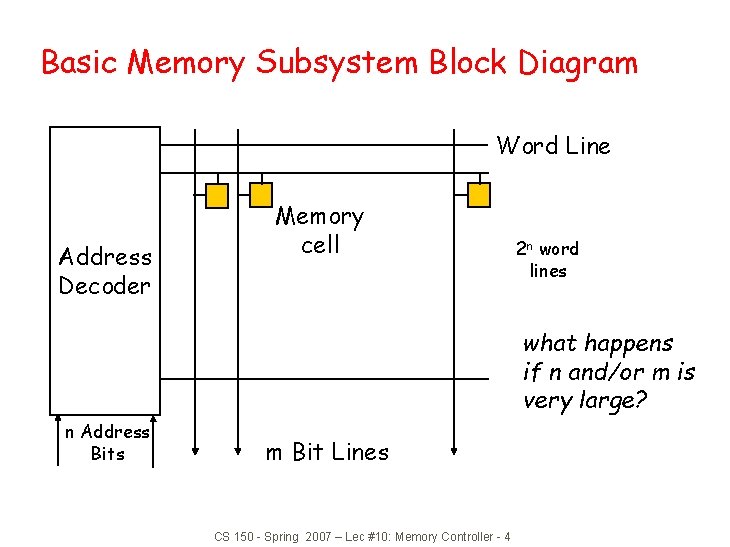

Basic Memory Subsystem Block Diagram Word Line Address Decoder Memory cell 2 n word lines what happens if n and/or m is very large? n Address Bits m Bit Lines CS 150 - Spring 2007 – Lec #10: Memory Controller - 4

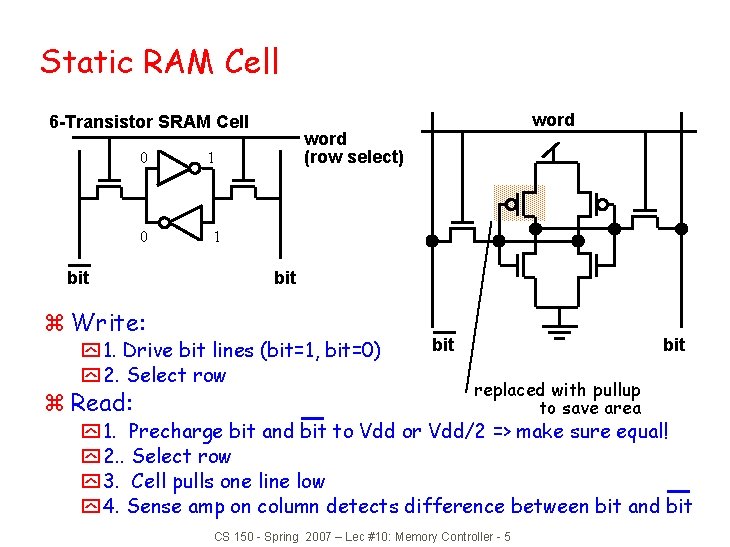

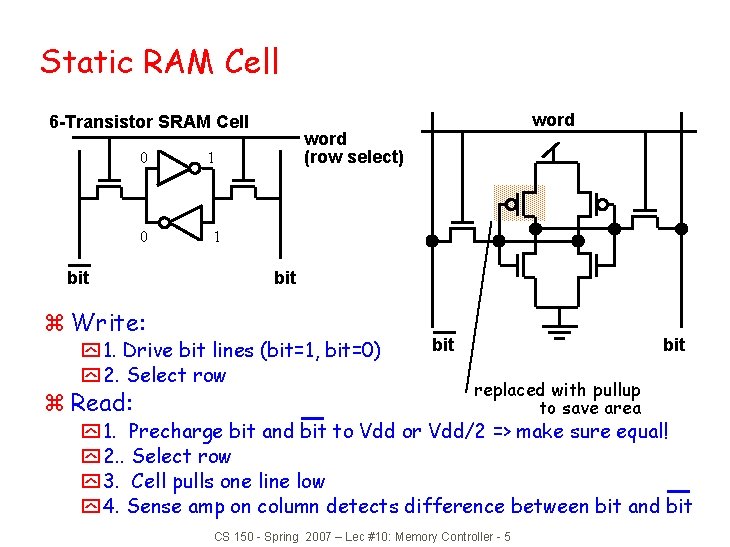

Static RAM Cell 6 -Transistor SRAM Cell 0 0 bit z Write: word (row select) 1 1 bit y 1. Drive bit lines (bit=1, bit=0) y 2. Select row z Read: word bit replaced with pullup to save area y 1. Precharge bit and bit to Vdd or Vdd/2 => make sure equal! y 2. . Select row y 3. Cell pulls one line low y 4. Sense amp on column detects difference between bit and bit CS 150 - Spring 2007 – Lec #10: Memory Controller - 5

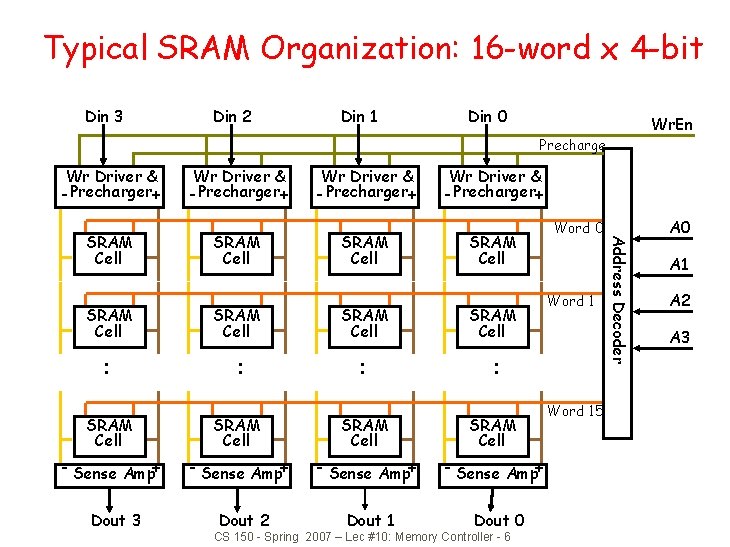

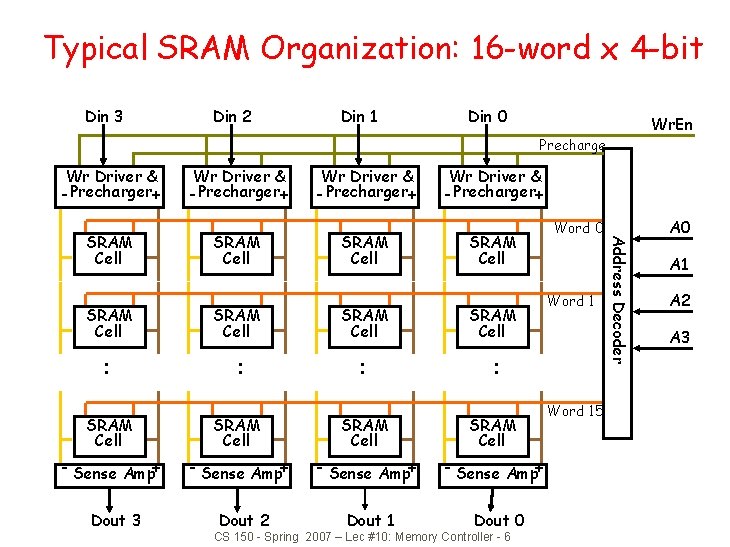

Typical SRAM Organization: 16 -word x 4 -bit Din 3 Din 2 Din 1 Din 0 Wr. En Precharge Wr Driver & - Precharger+ SRAM Cell SRAM Cell : : SRAM Cell - Sense Amp+ Dout 3 Dout 2 Dout 1 Dout 0 CS 150 - Spring 2007 – Lec #10: Memory Controller - 6 Word 0 Word 15 Address Decoder SRAM Cell Wr Driver & - Precharger+ A 0 A 1 A 2 A 3

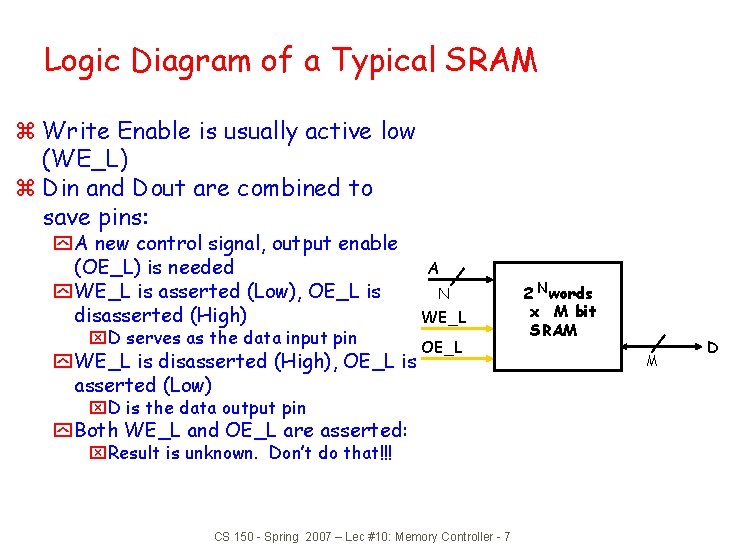

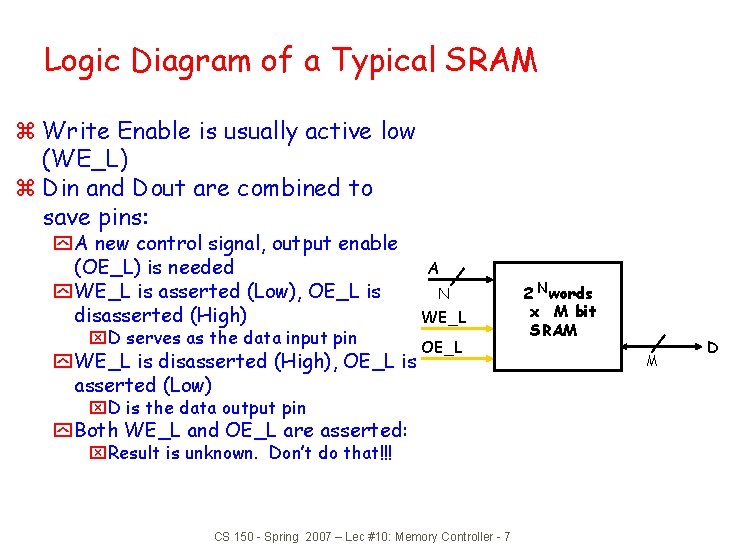

Logic Diagram of a Typical SRAM z Write Enable is usually active low (WE_L) z Din and Dout are combined to save pins: y A new control signal, output enable (OE_L) is needed y WE_L is asserted (Low), OE_L is disasserted (High) x. D serves as the data input pin y WE_L is disasserted (High), OE_L is asserted (Low) A N WE_L OE_L x. D is the data output pin y Both WE_L and OE_L are asserted: x. Result is unknown. Don’t do that!!! CS 150 - Spring 2007 – Lec #10: Memory Controller - 7 2 N words x M bit SRAM M D

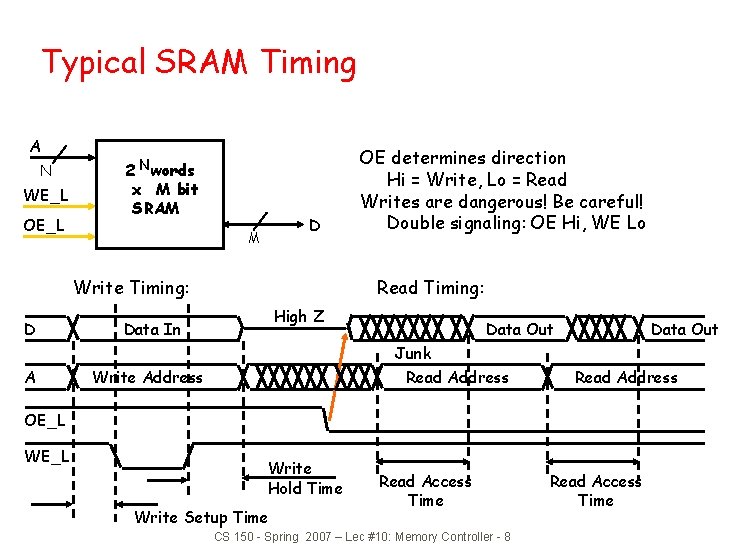

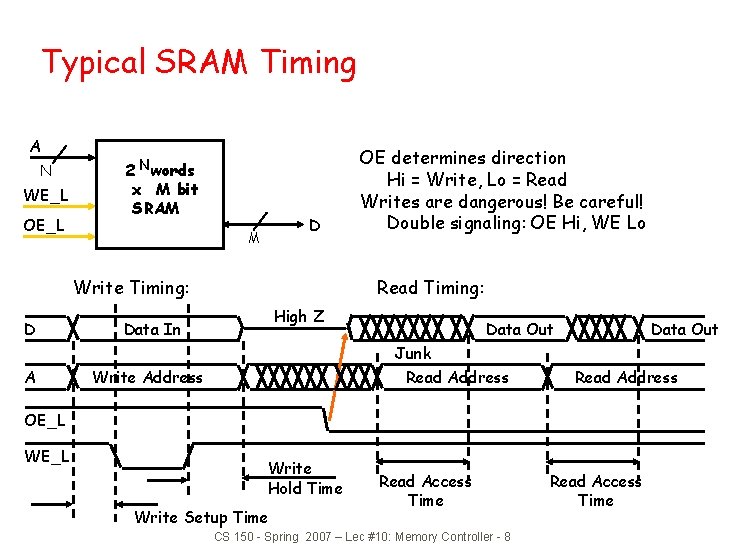

Typical SRAM Timing A N WE_L OE_L 2 N words x M bit SRAM D M Write Timing: D OE determines direction Hi = Write, Lo = Read Writes are dangerous! Be careful! Double signaling: OE Hi, WE Lo Read Timing: High Z Data In Data Out Junk A Write Address Read Address OE_L Write Hold Time Write Setup Time Read Access Time CS 150 - Spring 2007 – Lec #10: Memory Controller - 8 Read Access Time

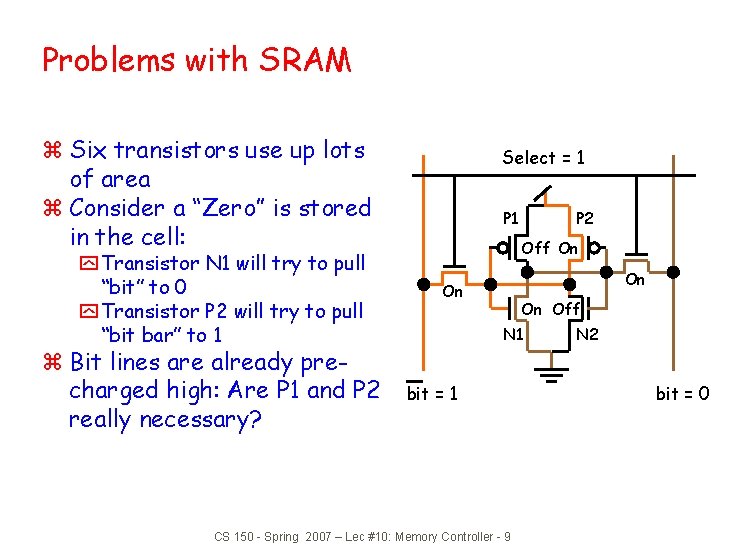

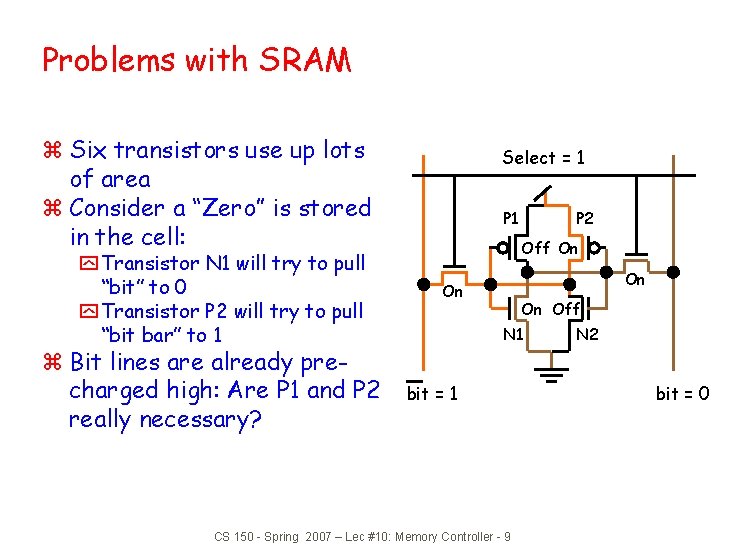

Problems with SRAM z Six transistors use up lots of area z Consider a “Zero” is stored in the cell: y Transistor N 1 will try to pull “bit” to 0 y Transistor P 2 will try to pull “bit bar” to 1 z Bit lines are already precharged high: Are P 1 and P 2 really necessary? Select = 1 P 2 Off On On Off N 1 bit = 1 CS 150 - Spring 2007 – Lec #10: Memory Controller - 9 N 2 bit = 0

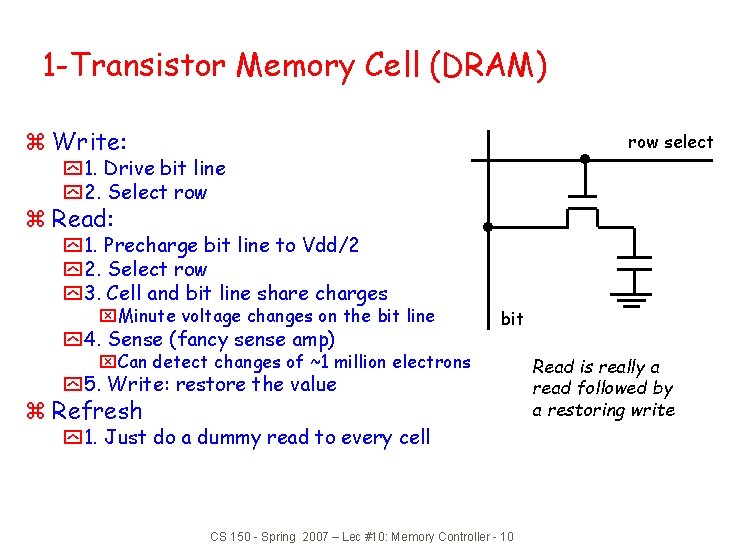

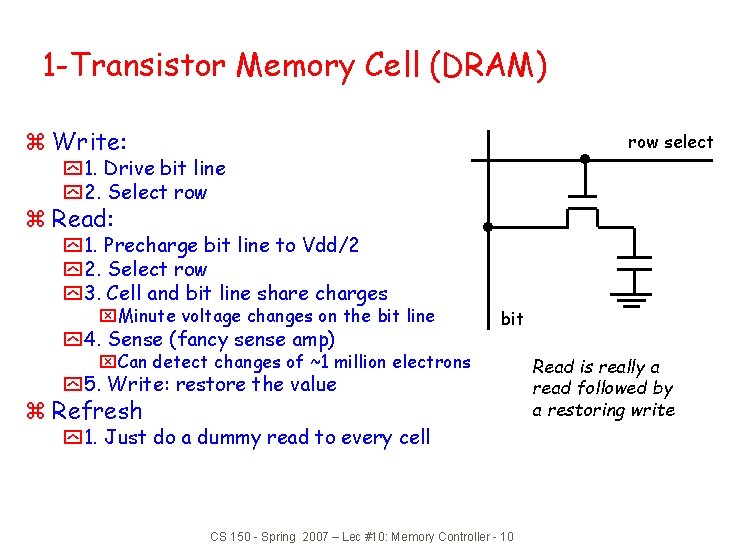

1 -Transistor Memory Cell (DRAM) z Write: row select y 1. Drive bit line y 2. Select row z Read: y 1. Precharge bit line to Vdd/2 y 2. Select row y 3. Cell and bit line share charges x. Minute voltage changes on the bit line y 4. Sense (fancy sense amp) bit x. Can detect changes of ~1 million electrons y 5. Write: restore the value z Refresh y 1. Just do a dummy read to every cell CS 150 - Spring 2007 – Lec #10: Memory Controller - 10 Read is really a read followed by a restoring write

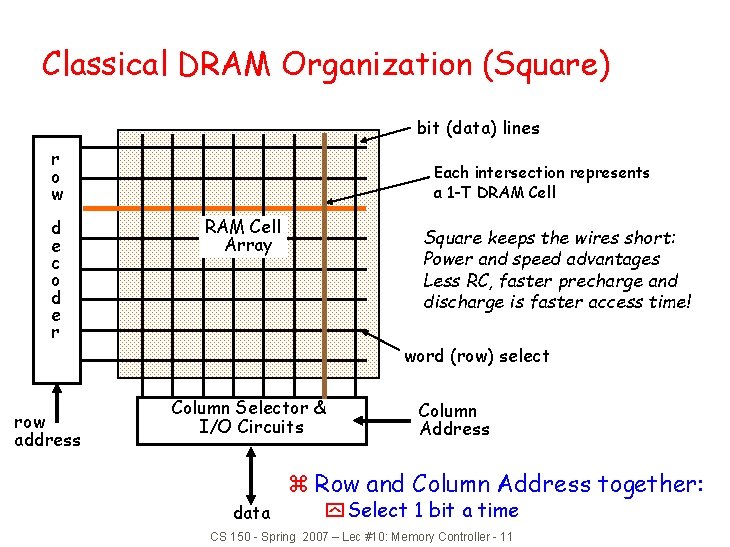

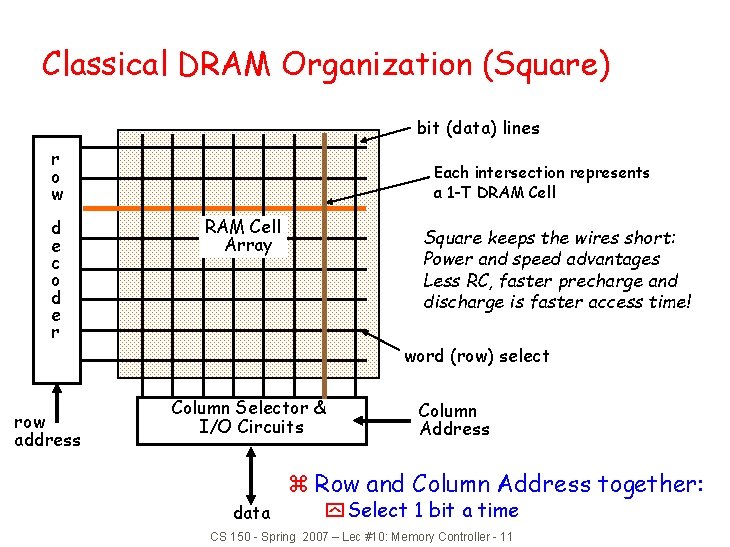

Classical DRAM Organization (Square) bit (data) lines r o w d e c o d e r row address Each intersection represents a 1 -T DRAM Cell Array Square keeps the wires short: Power and speed advantages Less RC, faster precharge and discharge is faster access time! word (row) select Column Selector & I/O Circuits data Column Address z Row and Column Address together: y Select 1 bit a time CS 150 - Spring 2007 – Lec #10: Memory Controller - 11

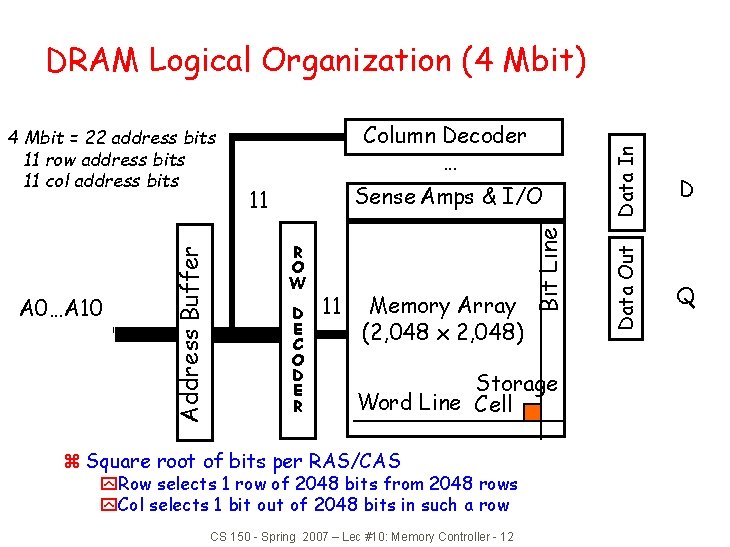

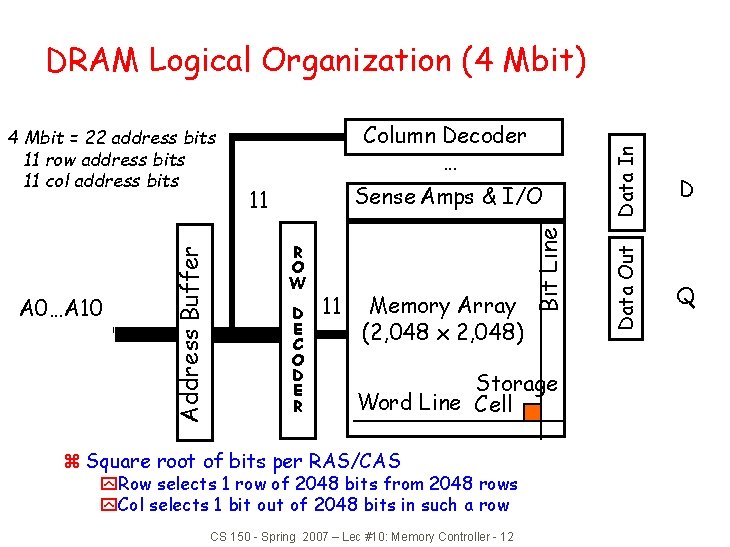

Sense Amps & I/O 11 R O W D E C O D E R 11 Memory Array (2, 048 x 2, 048) Storage Word Line Cell z Square root of bits per RAS/CAS y. Row selects 1 row of 2048 bits from 2048 rows y. Col selects 1 bit out of 2048 bits in such a row CS 150 - Spring 2007 – Lec #10: Memory Controller - 12 Data In Column Decoder … Bit Line A 0…A 10 Address Buffer 4 Mbit = 22 address bits 11 row address bits 11 col address bits D Data Out DRAM Logical Organization (4 Mbit) Q

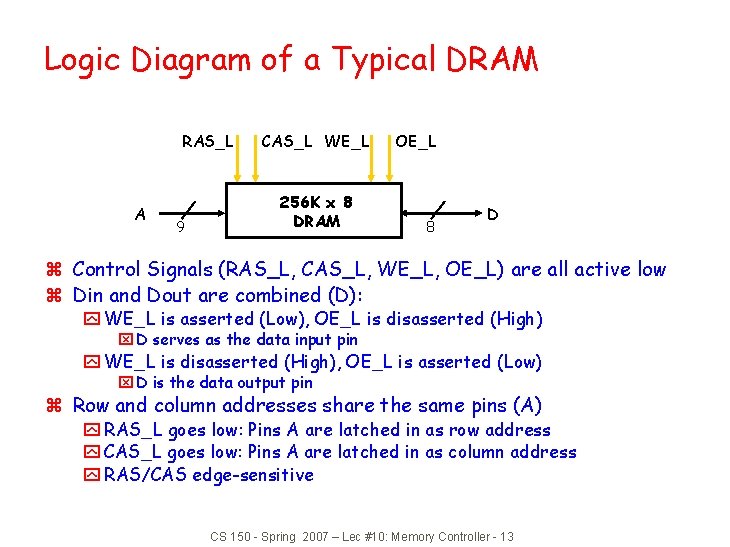

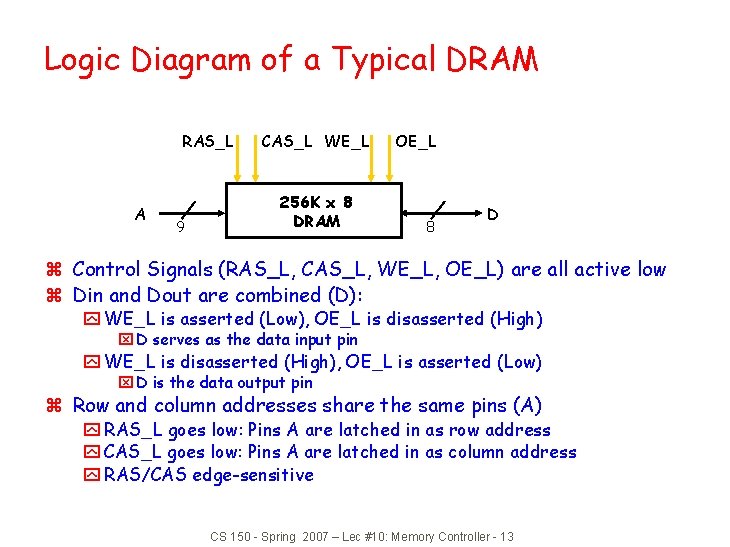

Logic Diagram of a Typical DRAM RAS_L A 9 CAS_L WE_L 256 K x 8 DRAM OE_L 8 D z Control Signals (RAS_L, CAS_L, WE_L, OE_L) are all active low z Din and Dout are combined (D): y WE_L is asserted (Low), OE_L is disasserted (High) x D serves as the data input pin y WE_L is disasserted (High), OE_L is asserted (Low) x D is the data output pin z Row and column addresses share the same pins (A) y RAS_L goes low: Pins A are latched in as row address y CAS_L goes low: Pins A are latched in as column address y RAS/CAS edge-sensitive CS 150 - Spring 2007 – Lec #10: Memory Controller - 13

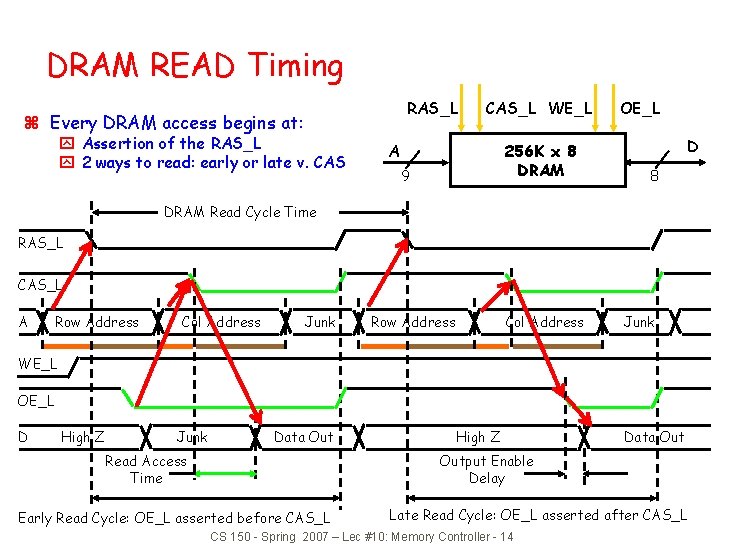

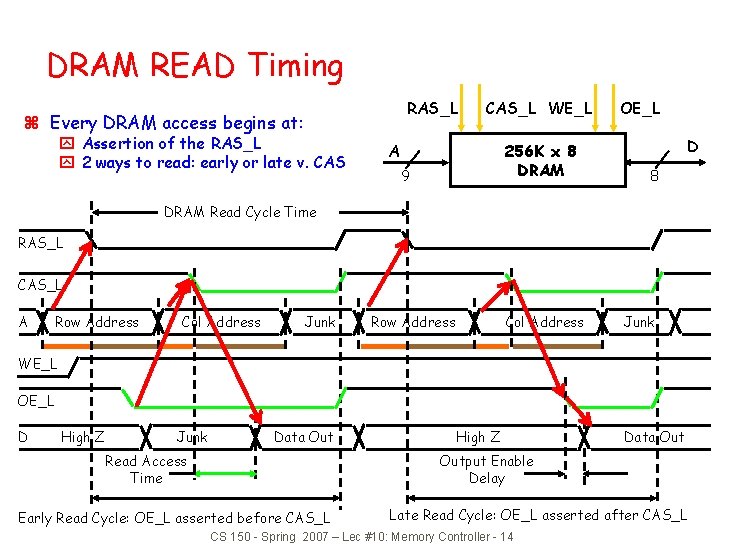

DRAM READ Timing RAS_L z Every DRAM access begins at: y Assertion of the RAS_L y 2 ways to read: early or late v. CAS_L WE_L A 256 K x 8 DRAM 9 OE_L D 8 DRAM Read Cycle Time RAS_L CAS_L A Row Address Col Address Junk WE_L OE_L D High Z Junk Data Out Read Access Time High Z Data Output Enable Delay Early Read Cycle: OE_L asserted before CAS_L Late Read Cycle: OE_L asserted after CAS_L CS 150 - Spring 2007 – Lec #10: Memory Controller - 14

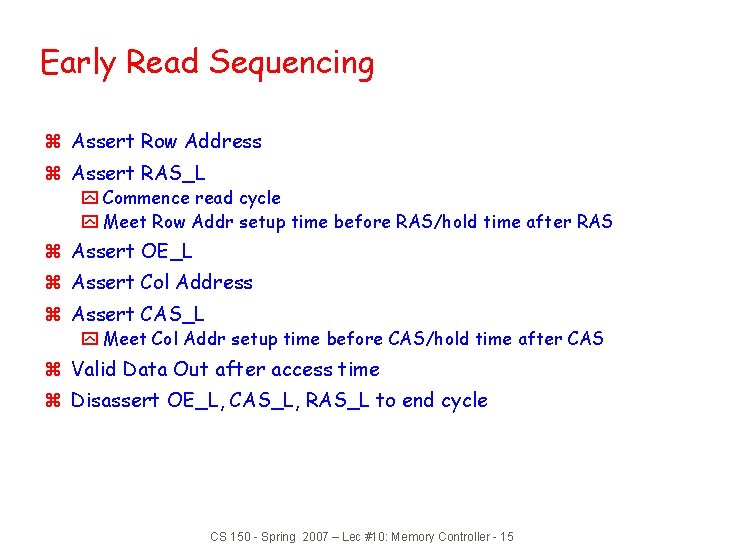

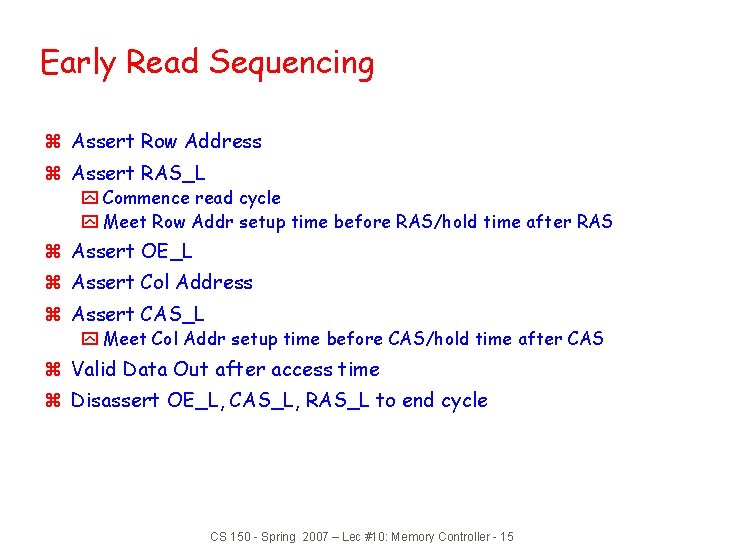

Early Read Sequencing z Assert Row Address z Assert RAS_L y Commence read cycle y Meet Row Addr setup time before RAS/hold time after RAS z Assert OE_L z Assert Col Address z Assert CAS_L y Meet Col Addr setup time before CAS/hold time after CAS z Valid Data Out after access time z Disassert OE_L, CAS_L, RAS_L to end cycle CS 150 - Spring 2007 – Lec #10: Memory Controller - 15

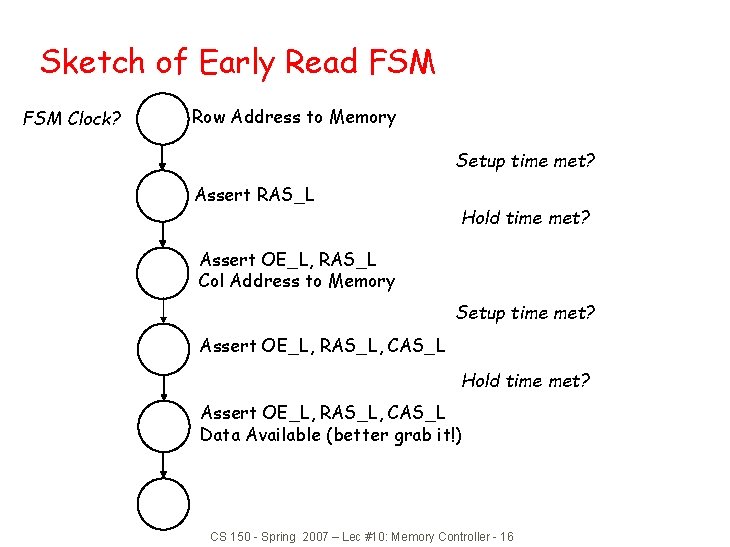

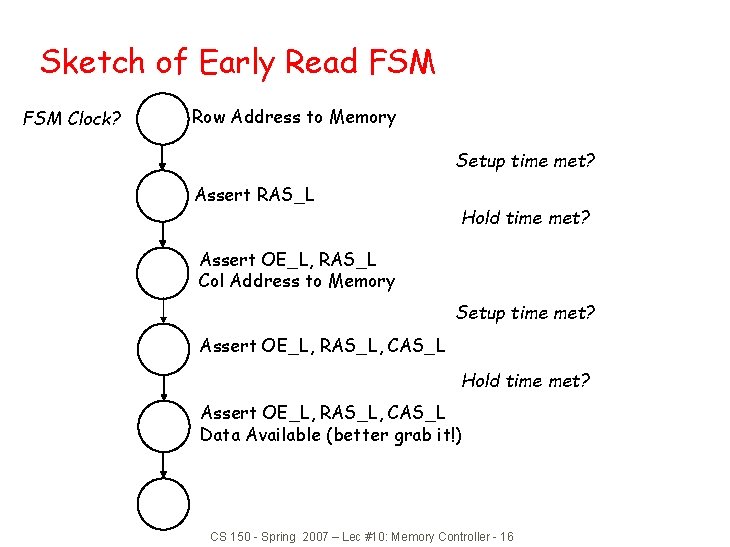

Sketch of Early Read FSM Clock? Row Address to Memory Setup time met? Assert RAS_L Hold time met? Assert OE_L, RAS_L Col Address to Memory Setup time met? Assert OE_L, RAS_L, CAS_L Hold time met? Assert OE_L, RAS_L, CAS_L Data Available (better grab it!) CS 150 - Spring 2007 – Lec #10: Memory Controller - 16

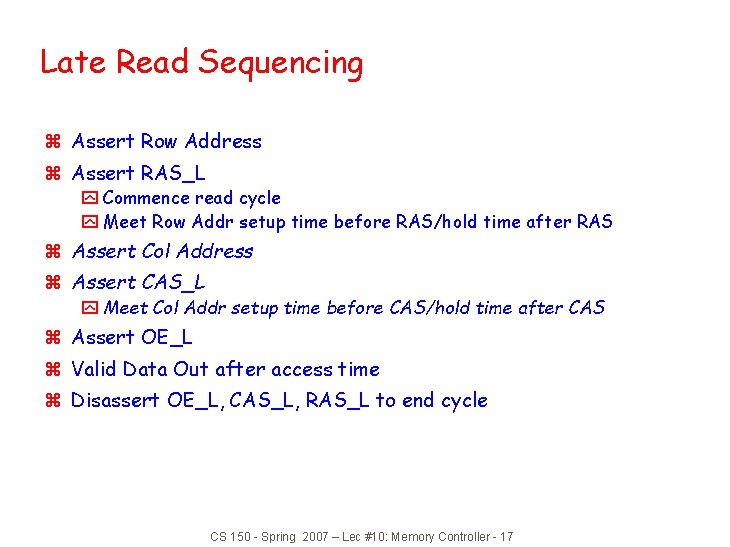

Late Read Sequencing z Assert Row Address z Assert RAS_L y Commence read cycle y Meet Row Addr setup time before RAS/hold time after RAS z Assert Col Address z Assert CAS_L y Meet Col Addr setup time before CAS/hold time after CAS z Assert OE_L z Valid Data Out after access time z Disassert OE_L, CAS_L, RAS_L to end cycle CS 150 - Spring 2007 – Lec #10: Memory Controller - 17

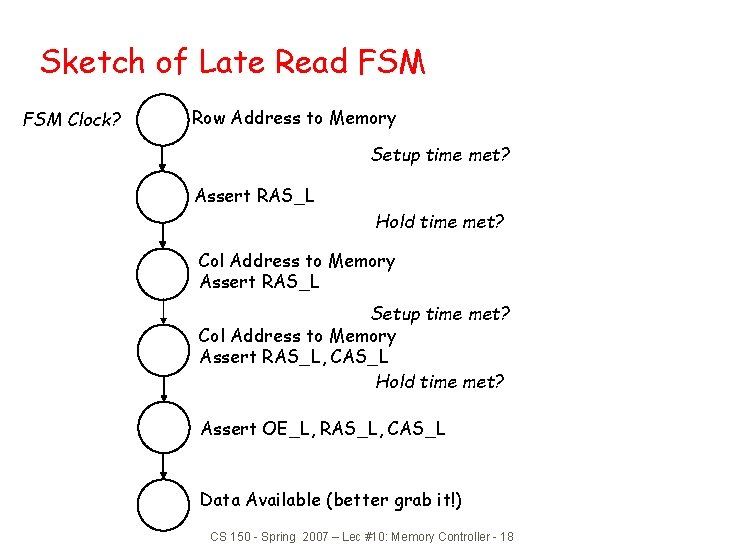

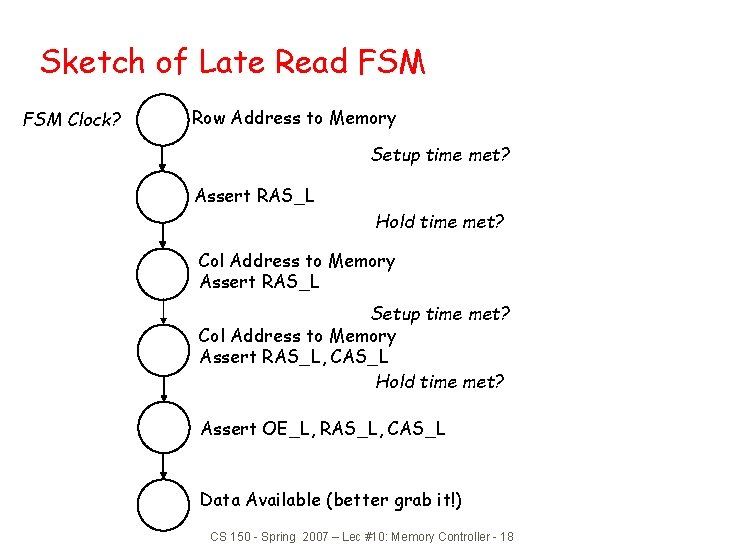

Sketch of Late Read FSM Clock? Row Address to Memory Setup time met? Assert RAS_L Hold time met? Col Address to Memory Assert RAS_L Setup time met? Col Address to Memory Assert RAS_L, CAS_L Hold time met? Assert OE_L, RAS_L, CAS_L Data Available (better grab it!) CS 150 - Spring 2007 – Lec #10: Memory Controller - 18

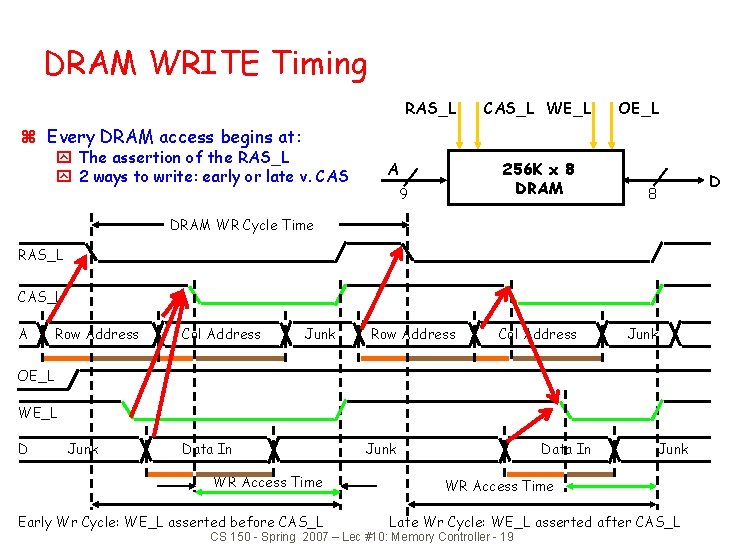

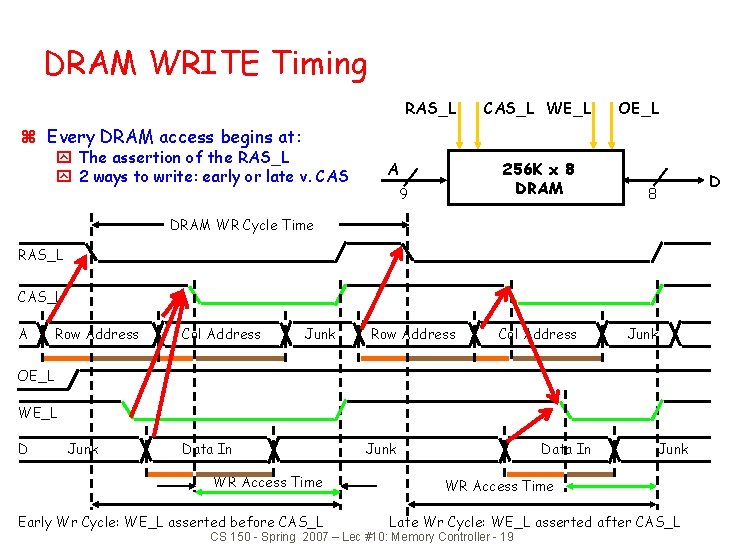

DRAM WRITE Timing RAS_L CAS_L WE_L OE_L z Every DRAM access begins at: y The assertion of the RAS_L y 2 ways to write: early or late v. CAS A 9 256 K x 8 DRAM 8 Col Address Junk D DRAM WR Cycle Time RAS_L CAS_L A Row Address Col Address Junk Row Address OE_L WE_L D Junk Data In WR Access Time Early Wr Cycle: WE_L asserted before CAS_L Junk Data In Junk WR Access Time Late Wr Cycle: WE_L asserted after CAS_L CS 150 - Spring 2007 – Lec #10: Memory Controller - 19

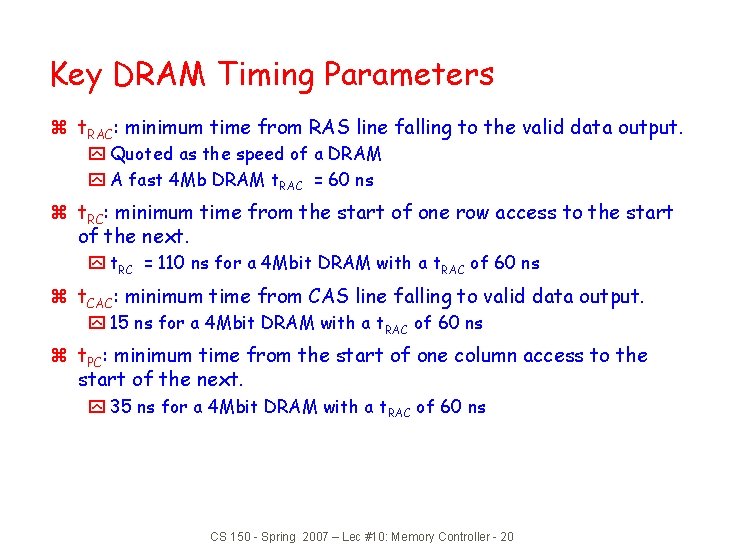

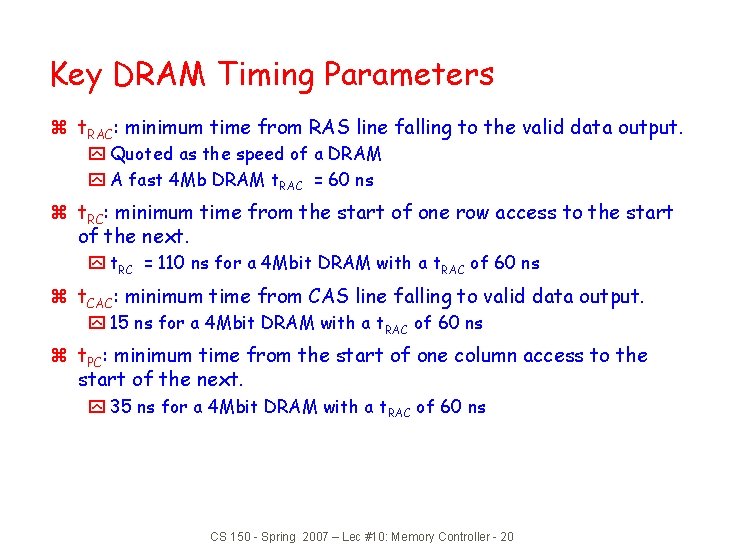

Key DRAM Timing Parameters z t. RAC: minimum time from RAS line falling to the valid data output. y Quoted as the speed of a DRAM y A fast 4 Mb DRAM t. RAC = 60 ns z t. RC: minimum time from the start of one row access to the start of the next. y t. RC = 110 ns for a 4 Mbit DRAM with a t. RAC of 60 ns z t. CAC: minimum time from CAS line falling to valid data output. y 15 ns for a 4 Mbit DRAM with a t. RAC of 60 ns z t. PC: minimum time from the start of one column access to the start of the next. y 35 ns for a 4 Mbit DRAM with a t. RAC of 60 ns CS 150 - Spring 2007 – Lec #10: Memory Controller - 20

SDRAM Memory Controller z Static RAM Technology y 6 T Memory Cell y Memory Access Timing z Dynamic RAM Technology y 1 T Memory Cell y Memory Access Timing CS 150 - Spring 2007 – Lec #10: Memory Controller - 22