Scoreboard CDC 6600 Registers FP Mult FP Divide

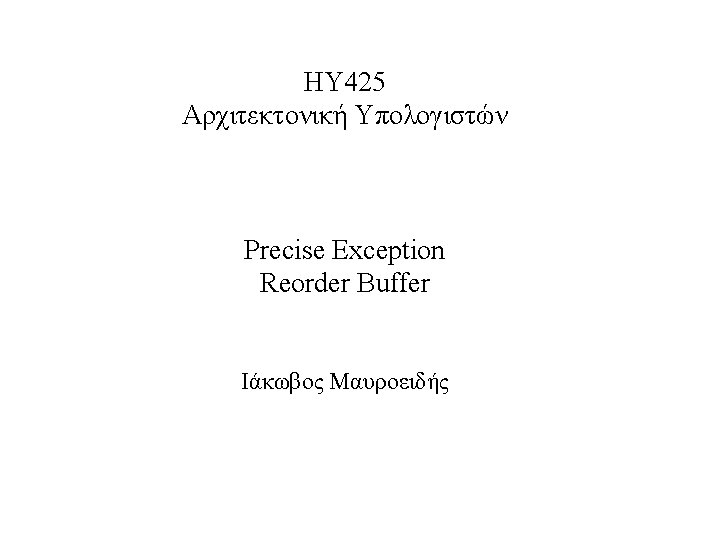

Αρχιτεκτονική Scoreboard (CDC 6600) Registers FP Mult FP Divide FP Add Integer SCOREBOARD Functional Units FP Mult Memory

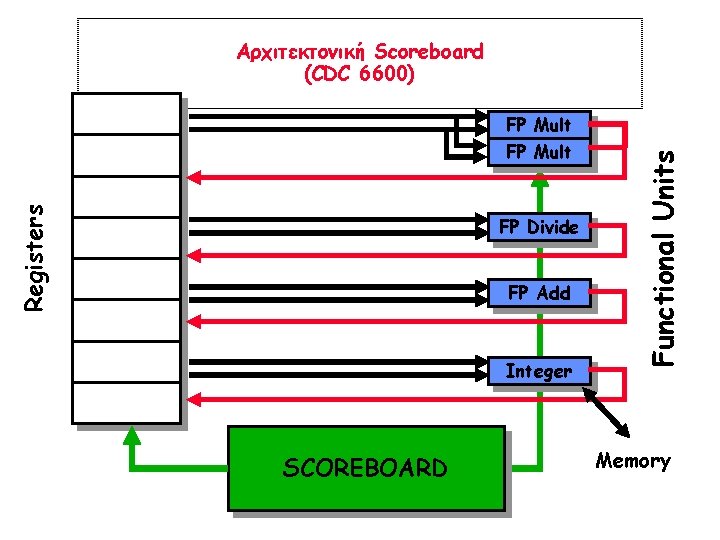

Tomasulo Organization FP Registers From Mem FP Op Queue Load Buffers Load 1 Load 2 Load 3 Load 4 Load 5 Load 6 Store Buffers Add 1 Add 2 Add 3 Mult 1 Mult 2 FP adders Reservation Stations To Mem FP multipliers Common Data Bus (CDB)

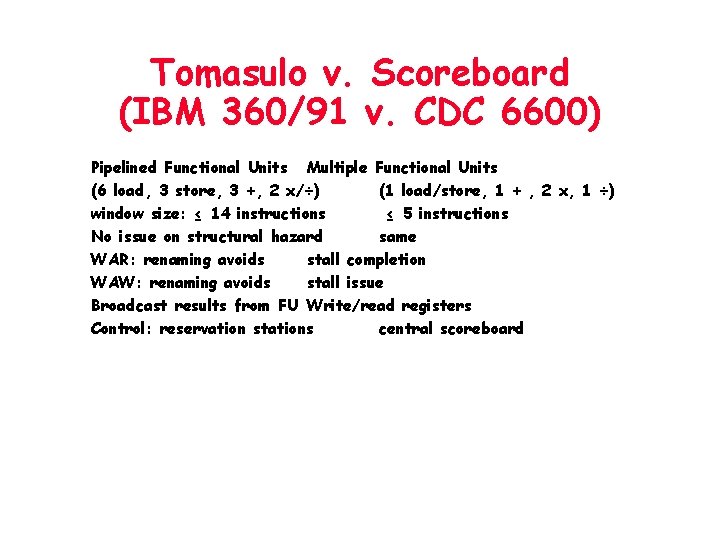

Tomasulo v. Scoreboard (IBM 360/91 v. CDC 6600) Pipelined Functional Units Multiple Functional Units (6 load, 3 store, 3 +, 2 x/÷) (1 load/store, 1 + , 2 x, 1 ÷) window size: ≤ 14 instructions ≤ 5 instructions No issue on structural hazard same WAR: renaming avoids stall completion WAW: renaming avoids stall issue Broadcast results from FU Write/read registers Control: reservation stations central scoreboard

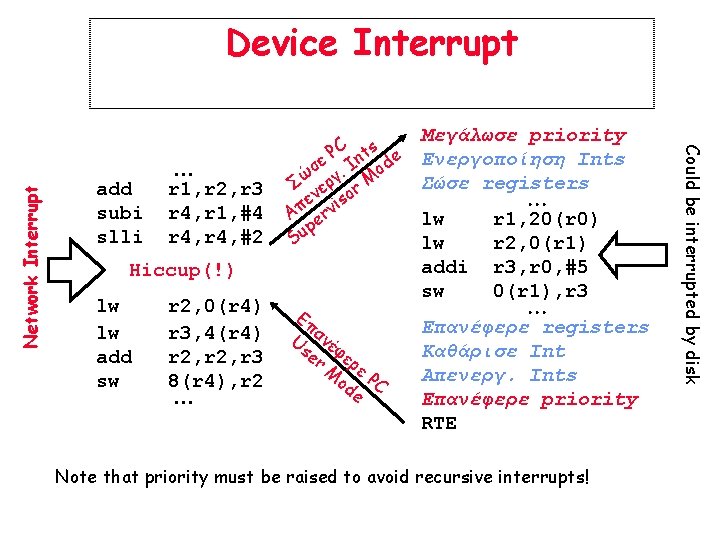

add subi slli r 1, r 2, r 3 r 4, r 1, #4 r 4, #2 PC nts e ε σ. I od ώ Σ εργ r M εν iso π Α erv p Su Hiccup(!) lw lw add sw r 2, 0(r 4) r 3, 4(r 4) r 2, r 3 8(r 4), r 2 Επ Us ανέ er φερ M εP od C e Μεγάλωσε priority Ενεργοποίηση Ints Σώσε registers lw r 1, 20(r 0) lw r 2, 0(r 1) addi r 3, r 0, #5 sw 0(r 1), r 3 Επανέφερε registers Καθάρισε Int Απενεργ. Ints Επανέφερε priority RTE Note that priority must be raised to avoid recursive interrupts! Could be interrupted by disk Network Interrupt Device Interrupt

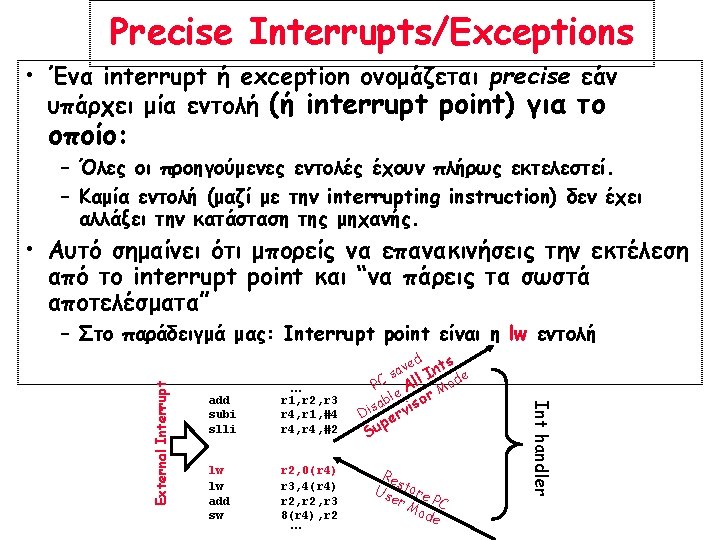

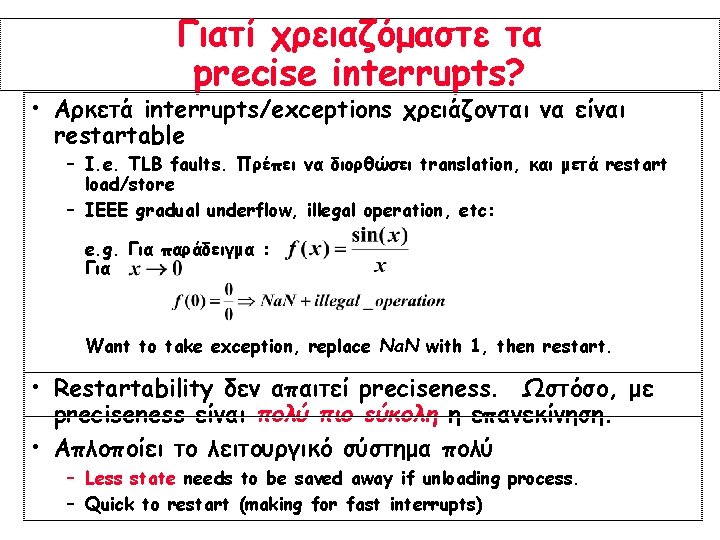

Precise interrupt point απαιτεί πολλάπλα PCs όταν υπάρχουν delayed branches addi r 4, r 3, #4 sub r 1, r 2, r 3 r 1, there PC: bne r 2, r 3, r 5 PC+4: and <other insts> addi r 4, r 3, #4 sub r 1, r 2, r 3 PC: bne r 1, there r 2, r 3, r 5 PC+4: and <other insts> Interrupt point described as <PC, PC+4> Interrupt point described as: <PC+4, there> (branch was taken) or <PC+4, PC+8> (branch was not taken)

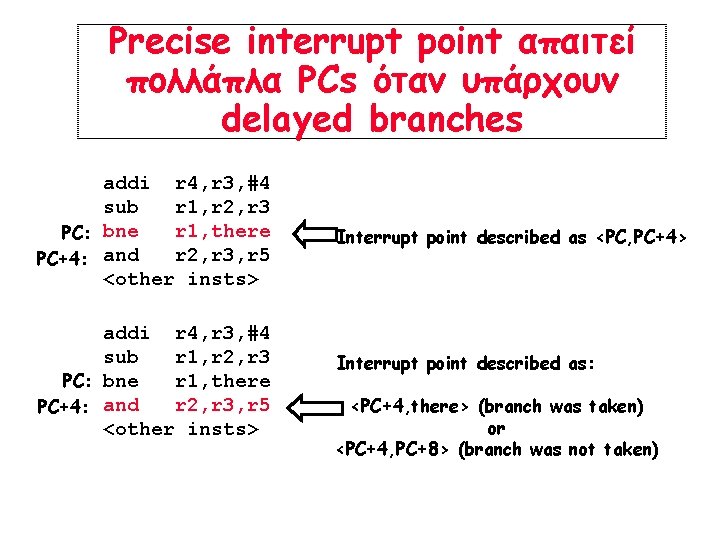

Γιατί χρειαζόμαστε τα precise interrupts? • Αρκετά interrupts/exceptions χρειάζονται να είναι restartable – I. e. TLB faults. Πρέπει να διορθώσει translation, και μετά restart load/store – IEEE gradual underflow, illegal operation, etc: e. g. Για παράδειγμα : Για Want to take exception, replace Na. N with 1, then restart. • Restartability δεν απαιτεί preciseness. Ωστόσο, με preciseness είναι πολύ πιο εύκολη η επανεκίνηση. • Απλοποίει το λειτουργικό σύστημα πολύ – Less state needs to be saved away if unloading process. – Quick to restart (making for fast interrupts)

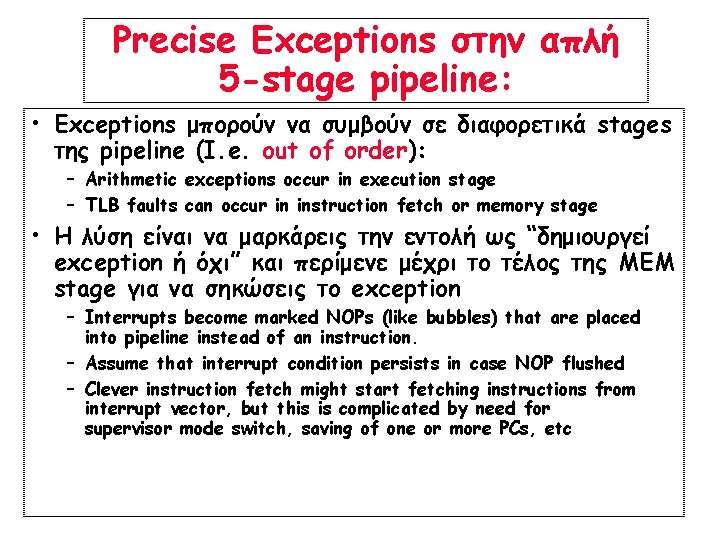

Precise Exceptions στην απλή 5 -stage pipeline: • Exceptions μπορούν να συμβούν σε διαφορετικά stages της pipeline (I. e. out of order): – Arithmetic exceptions occur in execution stage – TLB faults can occur in instruction fetch or memory stage • Η λύση είναι να μαρκάρεις την εντολή ως “δημιουργεί exception ή όχι” και περίμενε μέχρι το τέλος της MEM stage για να σηκώσεις το exception – Interrupts become marked NOPs (like bubbles) that are placed into pipeline instead of an instruction. – Assume that interrupt condition persists in case NOP flushed – Clever instruction fetch might start fetching instructions from interrupt vector, but this is complicated by need for supervisor mode switch, saving of one or more PCs, etc

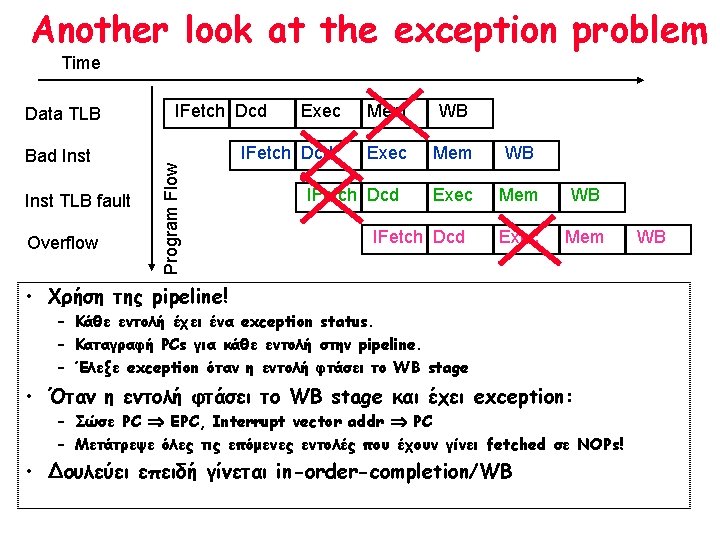

Another look at the exception problem Time Bad Inst TLB fault Overflow IFetch Dcd Exec IFetch Dcd Program Flow Data TLB Mem WB Exec Mem IFetch Dcd • Χρήση της pipeline! – Κάθε εντολή έχει ένα exception status. – Καταγραφή PCs για κάθε εντολή στην pipeline. – Έλεξε exception όταν η εντολή φτάσει το WB stage • Όταν η εντολή φτάσει το WB stage και έχει exception: – Σώσε PC EPC, Interrupt vector addr PC – Μετάτρεψε όλες τις επόμενες εντολές που έχουν γίνει fetched σε NOPs! • Δουλεύει επειδή γίνεται in-order-completion/WB WB

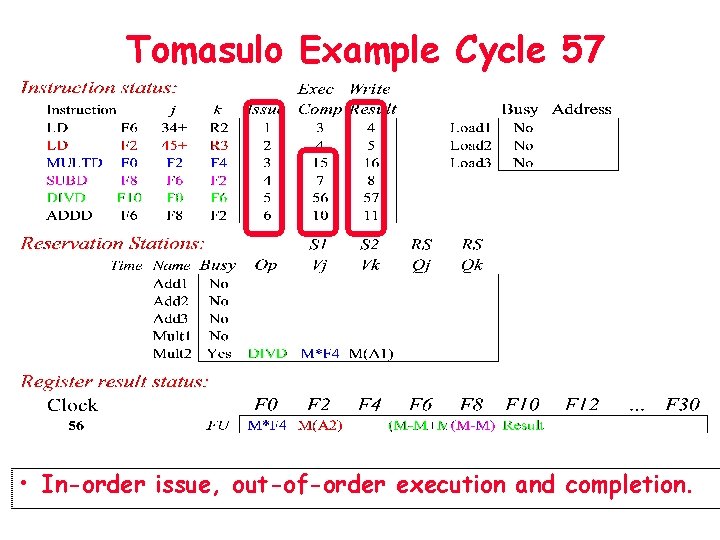

Tomasulo Example Cycle 57 • In-order issue, out-of-order execution and completion.

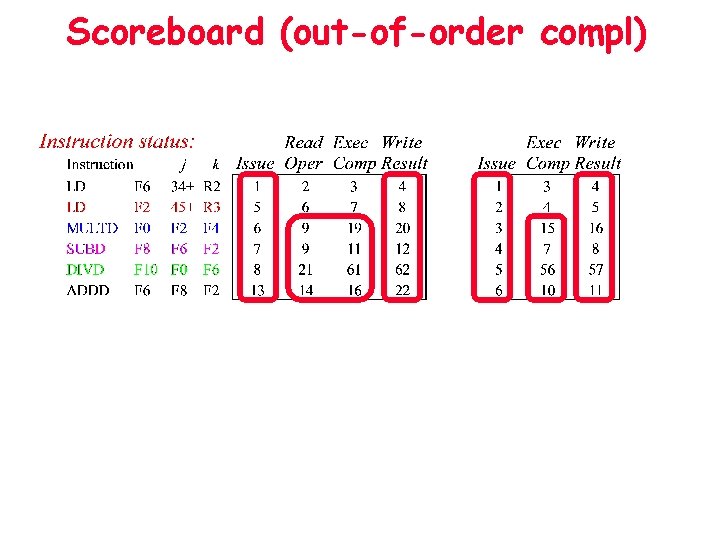

Scoreboard (out-of-order compl)

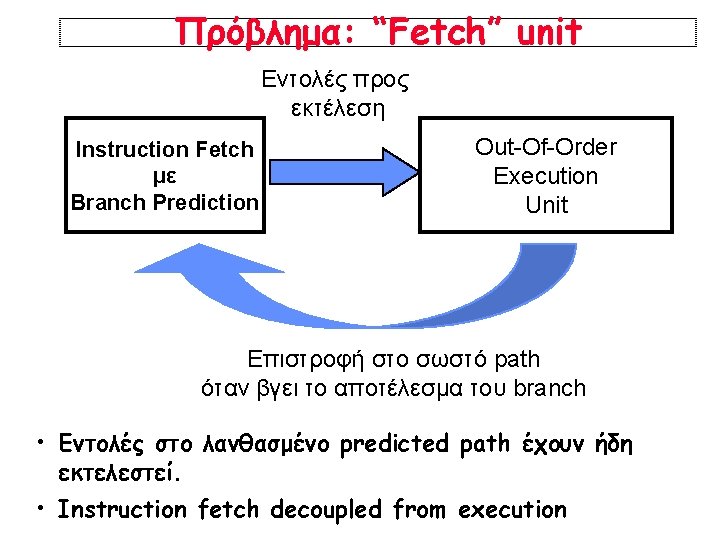

Πρόβλημα: “Fetch” unit Εντολές προς εκτέλεση Instruction Fetch με Branch Prediction Out-Of-Order Execution Unit Επιστροφή στο σωστό path όταν βγει το αποτέλεσμα του branch • Εντολές στο λανθασμένο predicted path έχουν ήδη εκτελεστεί. • Instruction fetch decoupled from execution

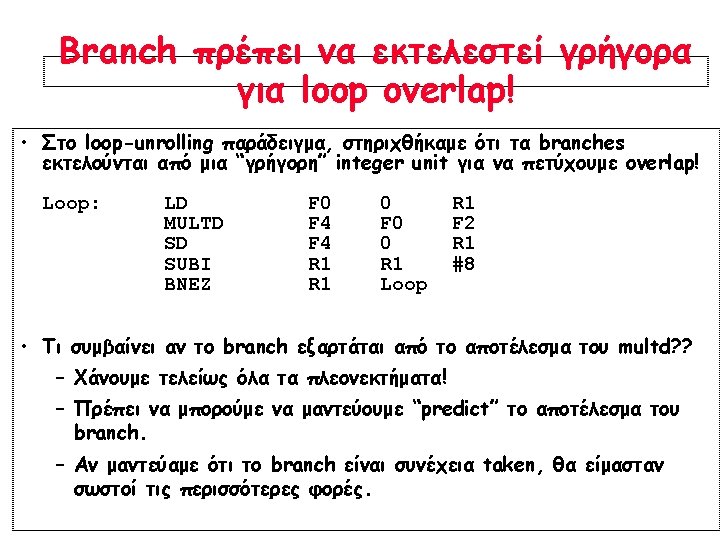

Prediction: Branches, Dependencies, Data • Η πρόβλεψη είναι απαραίτητη για καλή απόδοση. • Θα μελετήσουμε πώς προβλέπονται branches σε άλλα μαθήματα. Μοντέρνες αρχιτεκτονικές τώρα προβλέπουν τα πάντα : data dependencies, actual data, and results of groups of instructions: • Γιατί δουλεύει η πρόβλεψη? – Underlying algorithm has regularities. – Data that is being operated on has regularities. – Instruction sequence has redundancies that are artifacts of way that humans/compilers think about problems.

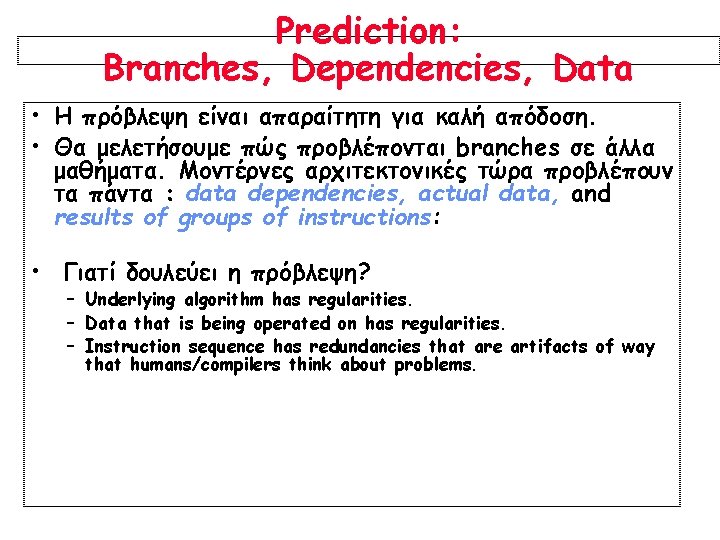

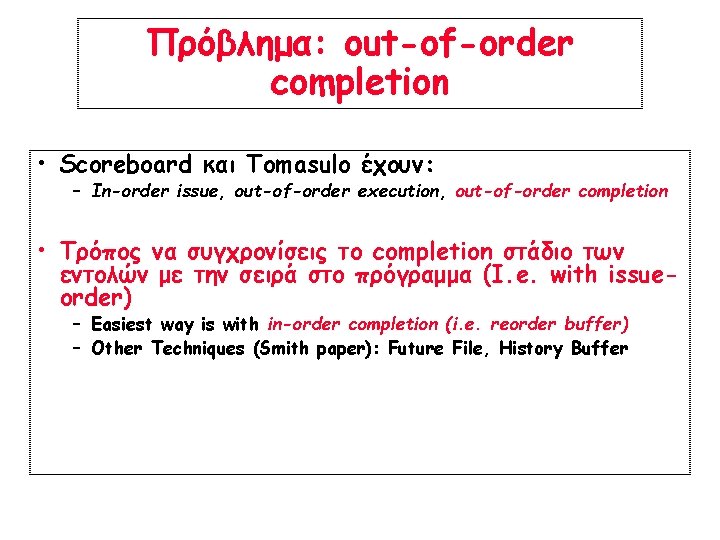

Πρόβλημα: out-of-order completion • Scoreboard και Tomasulo έχουν: – In-order issue, out-of-order execution, out-of-order completion • Τρόπος να συγχρονίσεις το completion στάδιο των εντολών με την σειρά στο πρόγραμμα (I. e. with issueorder) – Easiest way is with in-order completion (i. e. reorder buffer) – Other Techniques (Smith paper): Future File, History Buffer

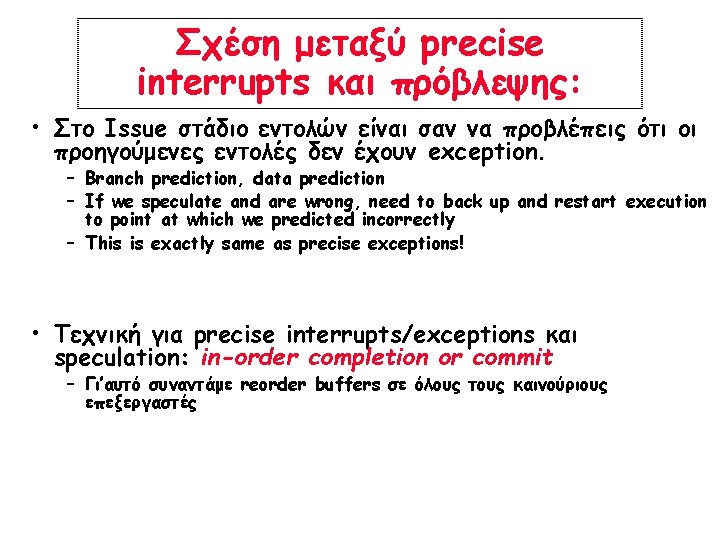

Σχέση μεταξύ precise interrupts και πρόβλεψης: • Στο Ιssue στάδιο εντολών είναι σαν να προβλέπεις ότι οι προηγούμενες εντολές δεν έχουν exception. – Branch prediction, data prediction – If we speculate and are wrong, need to back up and restart execution to point at which we predicted incorrectly – This is exactly same as precise exceptions! • Τεχνική για precise interrupts/exceptions και speculation: in-order completion or commit – Γι’αυτό συναντάμε reorder buffers σε όλους τους καινούριους επεξεργαστές

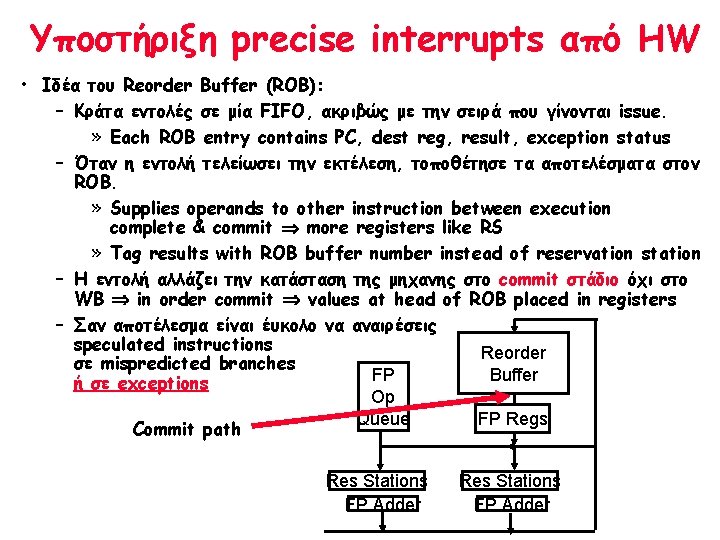

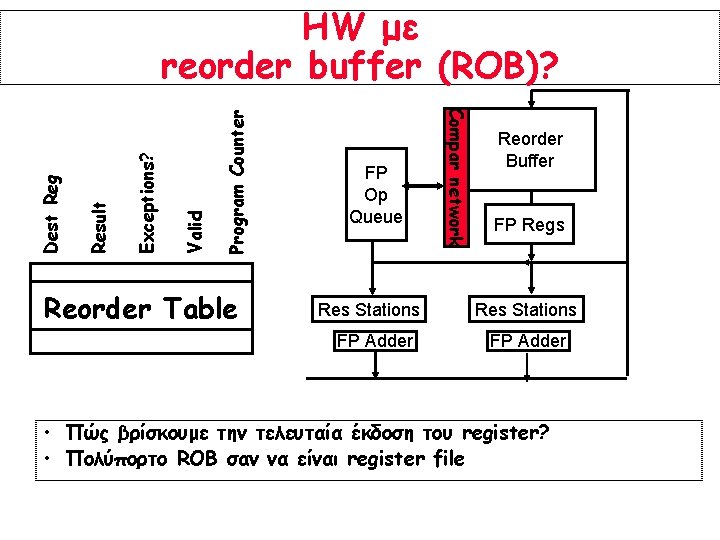

Υποστήριξη precise interrupts από HW • Ιδέα του Reorder Buffer (ROB): – Κράτα εντολές σε μία FIFO, ακριβώς με την σειρά που γίνονται issue. » Each ROB entry contains PC, dest reg, result, exception status – Όταν η εντολή τελείωσει την εκτέλεση, τοποθέτησε τα αποτελέσματα στον ROB. » Supplies operands to other instruction between execution complete & commit more registers like RS » Tag results with ROB buffer number instead of reservation station – Η εντολή αλλάζει την κατάσταση της μηχανης στο commit στάδιο όχι στο WB in order commit values at head of ROB placed in registers – Σαν αποτέλεσμα είναι έυκολο να αναιρέσεις speculated instructions Reorder σε mispredicted branches Buffer FP ή σε exceptions Op Queue FP Regs Commit path Res Stations FP Adder

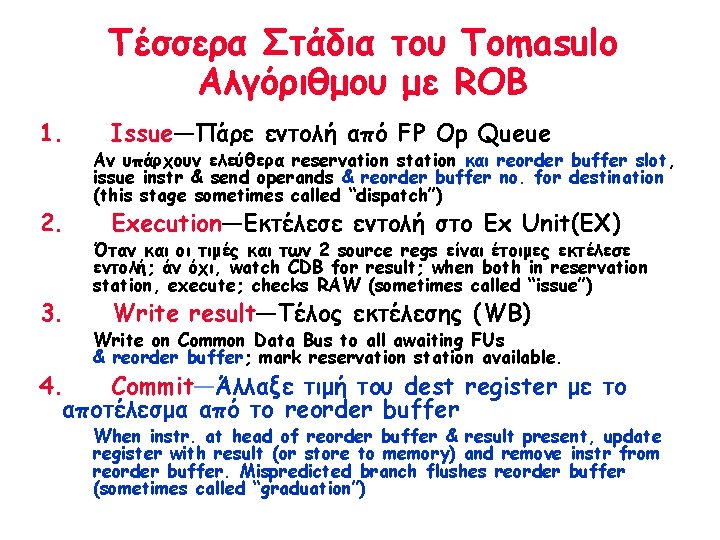

Τέσσερα Στάδια του Tomasulo Αλγόριθμου με ROB 1. 2. 3. Issue—Πάρε εντολή από FP Op Queue Αν υπάρχουν ελεύθερα reservation station και reorder buffer slot, issue instr & send operands & reorder buffer no. for destination (this stage sometimes called “dispatch”) Execution—Εκτέλεσε εντολή στο Ex Unit(EX) Όταν και οι τιμές και των 2 source regs είναι έτοιμες εκτέλεσε εντολή; άν όχι, watch CDB for result; when both in reservation station, execute; checks RAW (sometimes called “issue”) Write result—Τέλος εκτέλεσης (WB) Write on Common Data Bus to all awaiting FUs & reorder buffer; mark reservation station available. 4. Commit—Άλλαξε τιμή του dest register με το αποτέλεσμα από το reorder buffer When instr. at head of reorder buffer & result present, update register with result (or store to memory) and remove instr from reorder buffer. Mispredicted branch flushes reorder buffer (sometimes called “graduation”)

Program Counter Valid Exceptions? Result Reorder Table FP Op Queue Res Stations FP Adder Compar network Dest Reg HW με reorder buffer (ROB)? Reorder Buffer FP Regs Res Stations FP Adder • Πώς βρίσκουμε την τελευταία έκδοση του register? • Πολύπορτο ROB σαν να είναι register file

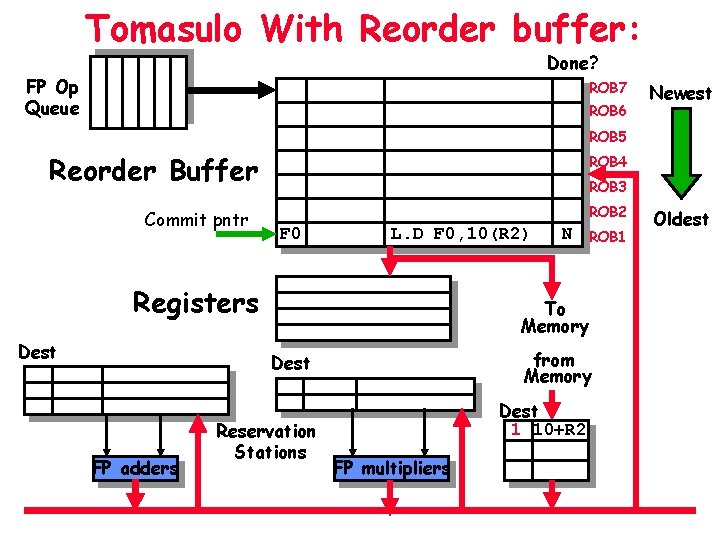

Tomasulo With Reorder buffer: Done? FP Op Queue ROB 7 ROB 6 Newest ROB 5 Reorder Buffer Commit pntr ROB 4 ROB 3 ROB 2 F 0 L. D F 0, 10(R 2) Registers Dest ROB 1 To Memory from Memory Dest FP adders N Reservation Stations Dest 1 10+R 2 FP multipliers Oldest

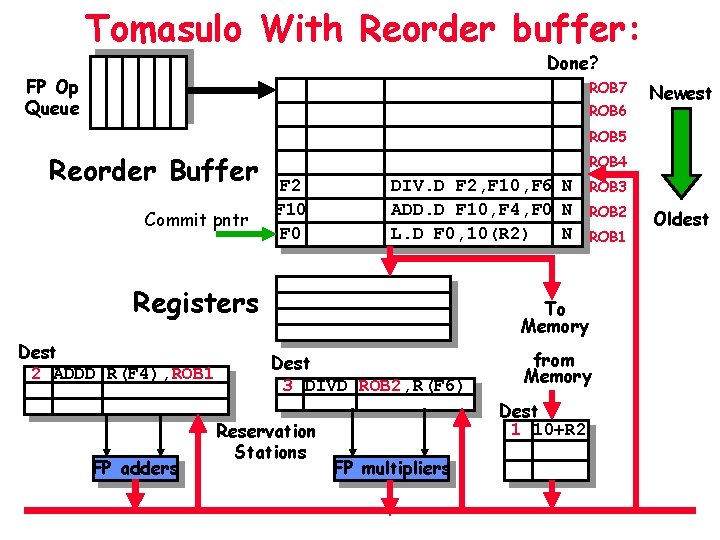

Tomasulo With Reorder buffer: Done? FP Op Queue ROB 7 ROB 6 Newest ROB 5 Reorder Buffer Commit pntr ROB 4 F 2 F 10 F 0 DIV. D F 2, F 10, F 6 N ADD. D F 10, F 4, F 0 N L. D F 0, 10(R 2) N Registers Dest 2 ADDD R(F 4), ROB 1 FP adders ROB 3 ROB 2 ROB 1 To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations from Memory Dest 1 10+R 2 FP multipliers Oldest

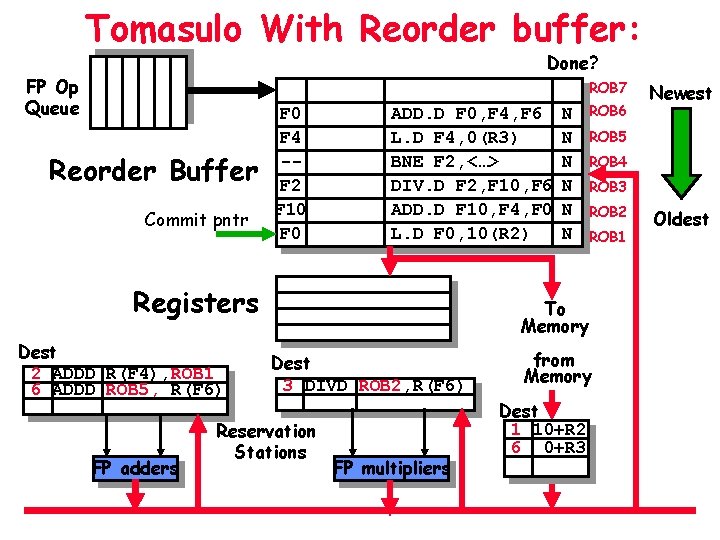

Tomasulo With Reorder buffer: Done? FP Op Queue ROB 7 Reorder Buffer Commit pntr F 0 F 4 -F 2 F 10 F 0 ADD. D F 0, F 4, F 6 L. D F 4, 0(R 3) BNE F 2, <…> DIV. D F 2, F 10, F 6 ADD. D F 10, F 4, F 0 L. D F 0, 10(R 2) Registers Dest 2 ADDD R(F 4), ROB 1 6 ADDD ROB 5, R(F 6) FP adders N N N ROB 6 ROB 5 ROB 4 ROB 3 ROB 2 ROB 1 To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations FP multipliers from Memory Dest 1 10+R 2 6 0+R 3 Newest Oldest

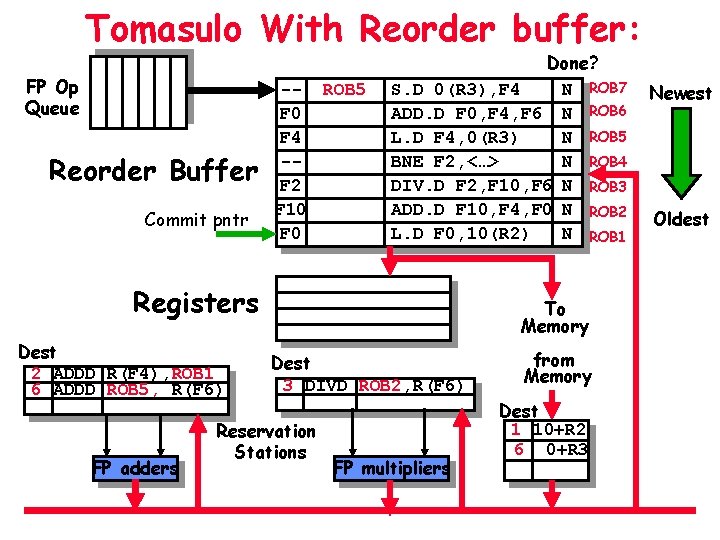

Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer Commit pntr -- ROB 5 F 0 F 4 -F 2 F 10 F 0 Done? S. D 0(R 3), F 4 N ROB 7 ADD. D F 0, F 4, F 6 N ROB 6 L. D F 4, 0(R 3) N ROB 5 BNE F 2, <…> N ROB 4 DIV. D F 2, F 10, F 6 N ROB 3 ADD. D F 10, F 4, F 0 N ROB 2 L. D F 0, 10(R 2) N ROB 1 Registers Dest 2 ADDD R(F 4), ROB 1 6 ADDD ROB 5, R(F 6) FP adders To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations FP multipliers from Memory Dest 1 10+R 2 6 0+R 3 Newest Oldest

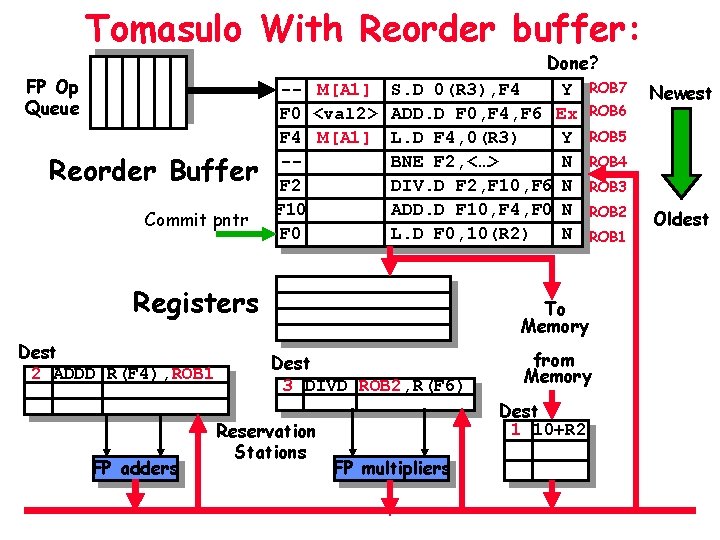

Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer Commit pntr Done? -- M[Α 1] S. D 0(R 3), F 4 Y ROB 7 F 0 <val 2> ADD. D F 0, F 4, F 6 Ex ROB 6 F 4 M[Α 1] L. D F 4, 0(R 3) Y ROB 5 -BNE F 2, <…> N ROB 4 F 2 DIV. D F 2, F 10, F 6 N ROB 3 F 10 ADD. D F 10, F 4, F 0 N ROB 2 F 0 L. D F 0, 10(R 2) N ROB 1 Registers Dest 2 ADDD R(F 4), ROB 1 FP adders To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations from Memory Dest 1 10+R 2 FP multipliers Newest Oldest

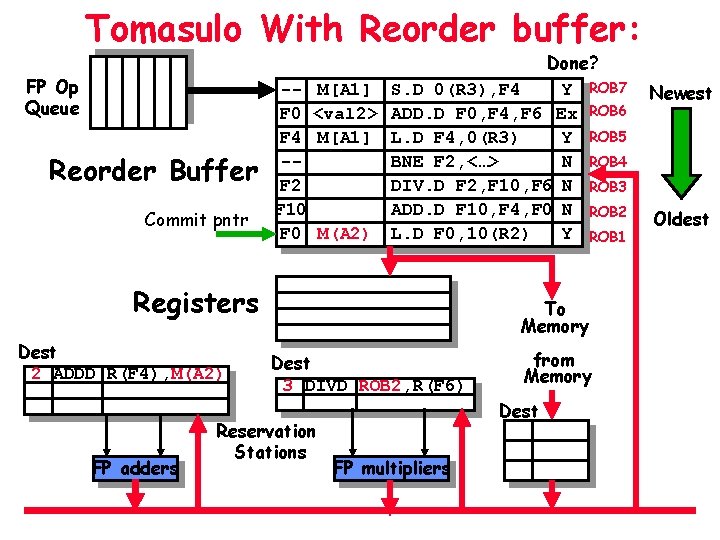

Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer Commit pntr Done? -- M[Α 1] S. D 0(R 3), F 4 Y ROB 7 F 0 <val 2> ADD. D F 0, F 4, F 6 Ex ROB 6 F 4 M[Α 1] L. D F 4, 0(R 3) Y ROB 5 -BNE F 2, <…> N ROB 4 F 2 DIV. D F 2, F 10, F 6 N ROB 3 F 10 ADD. D F 10, F 4, F 0 N ROB 2 F 0 Μ(Α 2) L. D F 0, 10(R 2) Υ ROB 1 Registers Dest 2 ADDD R(F 4), Μ(Α 2) FP adders To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations from Memory Dest FP multipliers Newest Oldest

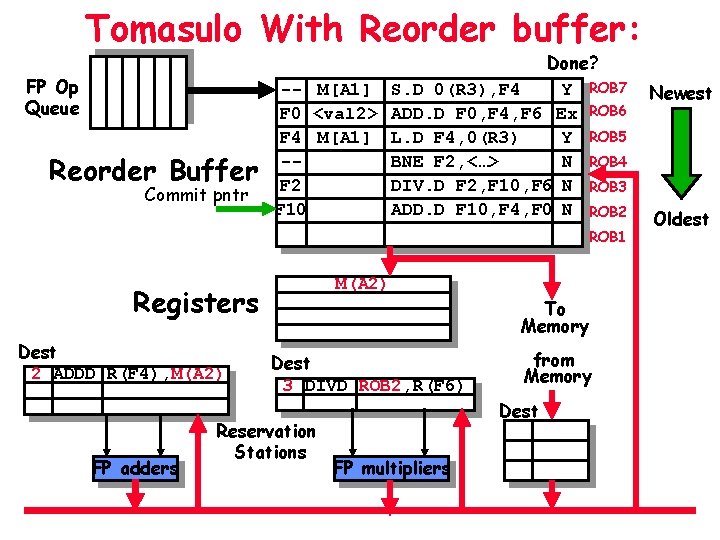

Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer Commit pntr Done? -- M[Α 1] S. D 0(R 3), F 4 Y ROB 7 F 0 <val 2> ADD. D F 0, F 4, F 6 Ex ROB 6 F 4 M[Α 1] L. D F 4, 0(R 3) Y ROB 5 -BNE F 2, <…> N ROB 4 F 2 DIV. D F 2, F 10, F 6 N ROB 3 F 10 ADD. D F 10, F 4, F 0 N ROB 2 ROB 1 Μ(Α 2) Registers Dest 2 ADDD R(F 4), Μ(Α 2) FP adders To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations from Memory Dest FP multipliers Newest Oldest

![Tomasulo With Reorder buffer: FP Op Queue Commit pntr Done? -- M[Α 1] S. Tomasulo With Reorder buffer: FP Op Queue Commit pntr Done? -- M[Α 1] S.](http://slidetodoc.com/presentation_image_h/1c5888f3f73861d0bf5ec424be15ed35/image-28.jpg)

Tomasulo With Reorder buffer: FP Op Queue Commit pntr Done? -- M[Α 1] S. D 0(R 3), F 4 Y ROB 7 F 0 <val 2> ADD. D F 0, F 4, F 6 Ex ROB 6 Newest ROB 5 Reorder Buffer ROB 4 ROB 3 ROB 2 ROB 1 Registers Dest To Memory from Memory Dest FP adders Reservation Stations Dest FP multipliers Oldest

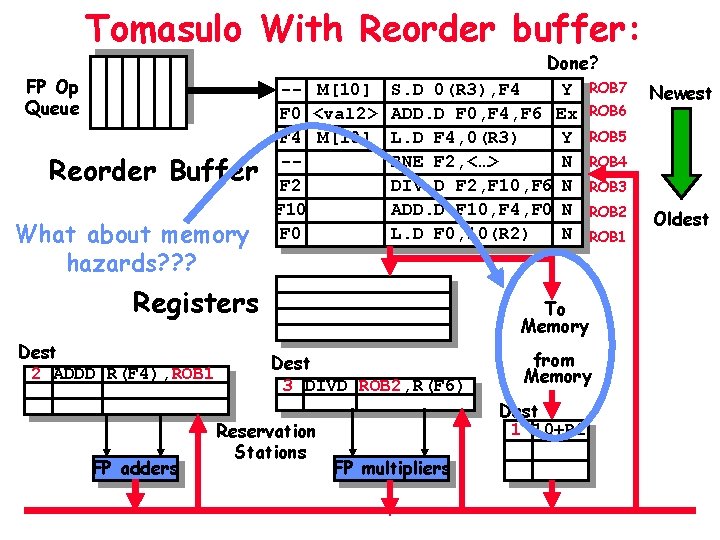

Tomasulo With Reorder buffer: FP Op Queue Reorder Buffer What about memory hazards? ? ? Done? -- M[10] S. D 0(R 3), F 4 Y ROB 7 F 0 <val 2> ADD. D F 0, F 4, F 6 Ex ROB 6 F 4 M[10] L. D F 4, 0(R 3) Y ROB 5 -BNE F 2, <…> N ROB 4 F 2 DIV. D F 2, F 10, F 6 N ROB 3 F 10 ADD. D F 10, F 4, F 0 N ROB 2 F 0 L. D F 0, 10(R 2) N ROB 1 Registers Dest 2 ADDD R(F 4), ROB 1 FP adders To Memory Dest 3 DIVD ROB 2, R(F 6) Reservation Stations from Memory Dest 1 10+R 2 FP multipliers Newest Oldest

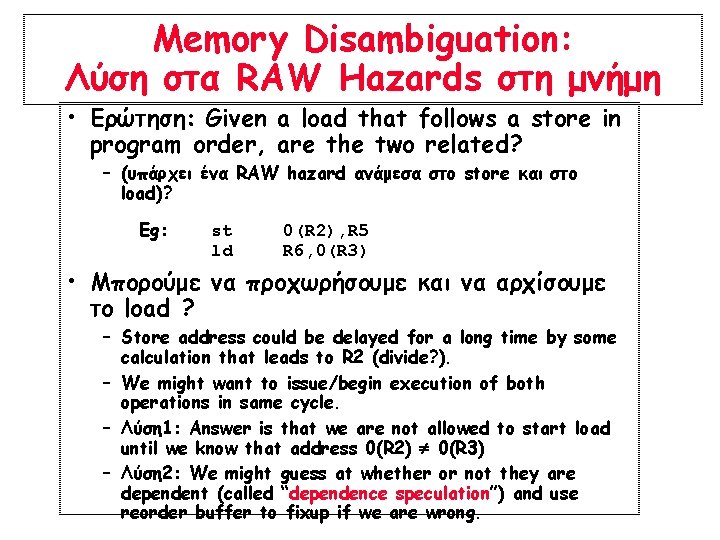

Memory Disambiguation: Λύση στα RAW Hazards στη μνήμη • Ερώτηση: Given a load that follows a store in program order, are the two related? – (υπάρχει ένα RAW hazard ανάμεσα στο store και στο load)? Eg: st ld 0(R 2), R 5 R 6, 0(R 3) • Μπορούμε να προχωρήσουμε και να αρχίσουμε το load ? – Store address could be delayed for a long time by some calculation that leads to R 2 (divide? ). – We might want to issue/begin execution of both operations in same cycle. – Λύση 1: Answer is that we are not allowed to start load until we know that address 0(R 2) 0(R 3) – Λύση 2: We might guess at whether or not they are dependent (called “dependence speculation”) and use reorder buffer to fixup if we are wrong.

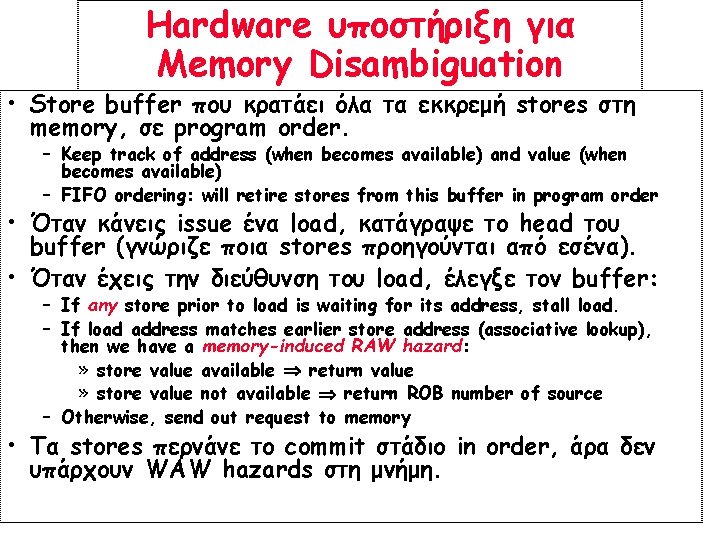

Hardware υποστήριξη για Memory Disambiguation • Store buffer που κρατάει όλα τα εκκρεμή stores στη memory, σε program order. – Keep track of address (when becomes available) and value (when becomes available) – FIFO ordering: will retire stores from this buffer in program order • Όταν κάνεις issue ένα load, κατάγραψε το head του buffer (γνώριζε ποια stores προηγούνται από εσένα). • Όταν έχεις την διεύθυνση του load, έλεγξε τον buffer: – If any store prior to load is waiting for its address, stall load. – If load address matches earlier store address (associative lookup), then we have a memory-induced RAW hazard: » store value available return value » store value not available return ROB number of source – Otherwise, send out request to memory • Τα stores περνάνε το commit στάδιο in order, άρα δεν υπάρχουν WAW hazards στη μνήμη.

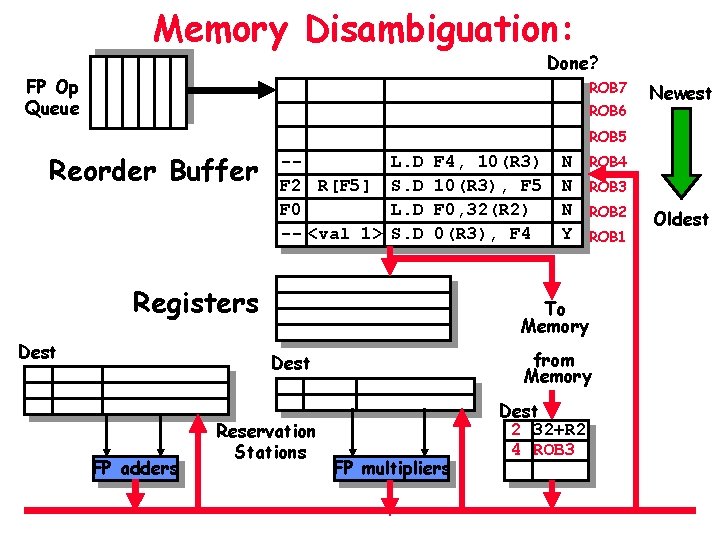

Memory Disambiguation: Done? FP Op Queue ROB 7 ROB 6 Newest ROB 5 Reorder Buffer -F 2 R[F 5] F 0 -- <val 1> L. D S. D F 4, 10(R 3), F 5 F 0, 32(R 2) 0(R 3), F 4 Registers Dest ROB 4 ROB 3 ROB 2 ROB 1 To Memory from Memory Dest FP adders N N N Y Reservation Stations FP multipliers Dest 2 32+R 2 4 ROB 3 Oldest

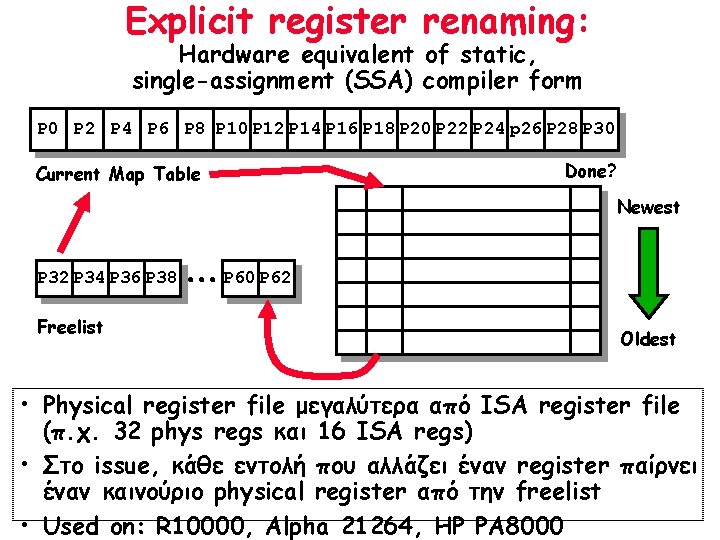

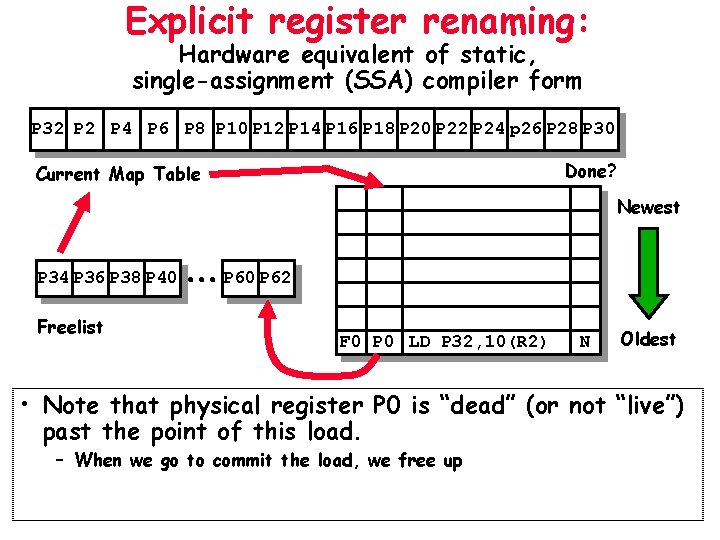

Explicit register renaming: Hardware equivalent of static, single-assignment (SSA) compiler form P 0 P 2 P 4 P 6 P 8 P 10 P 12 P 14 P 16 P 18 P 20 P 22 P 24 p 26 P 28 P 30 Current Map Table Done? Newest P 32 P 34 P 36 P 38 Freelist P 60 P 62 Oldest • Physical register file μεγαλύτερα από ISA register file (π. χ. 32 phys regs και 16 ISA regs) • Στο issue, κάθε εντολή που αλλάζει έναν register παίρνει έναν καινούριο physical register από την freelist • Used on: R 10000, Alpha 21264, HP PA 8000

Explicit register renaming: Hardware equivalent of static, single-assignment (SSA) compiler form P 32 P 4 P 6 P 8 P 10 P 12 P 14 P 16 P 18 P 20 P 22 P 24 p 26 P 28 P 30 Done? Current Map Table Newest P 34 P 36 P 38 P 40 Freelist P 60 P 62 F 0 P 0 LD P 32, 10(R 2) N Oldest • Note that physical register P 0 is “dead” (or not “live”) past the point of this load. – When we go to commit the load, we free up

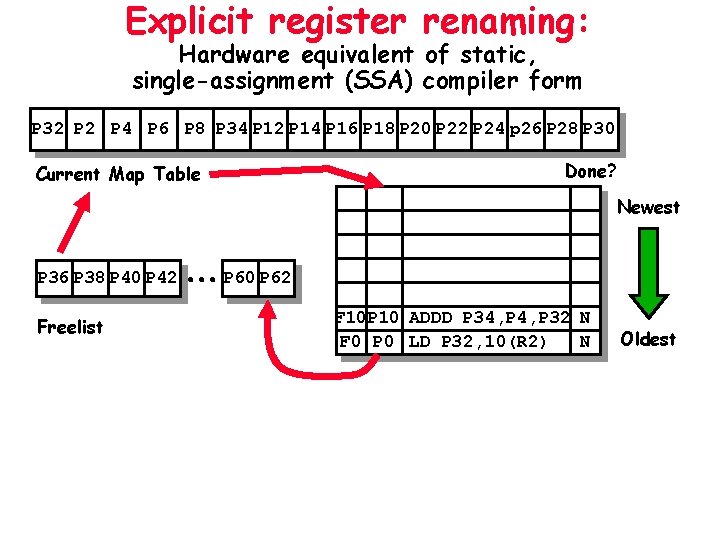

Explicit register renaming: Hardware equivalent of static, single-assignment (SSA) compiler form P 32 P 4 P 6 P 8 P 34 P 12 P 14 P 16 P 18 P 20 P 22 P 24 p 26 P 28 P 30 Current Map Table Done? Newest P 36 P 38 P 40 P 42 Freelist P 60 P 62 F 10 P 10 ADDD P 34, P 32 N F 0 P 0 LD P 32, 10(R 2) N Oldest

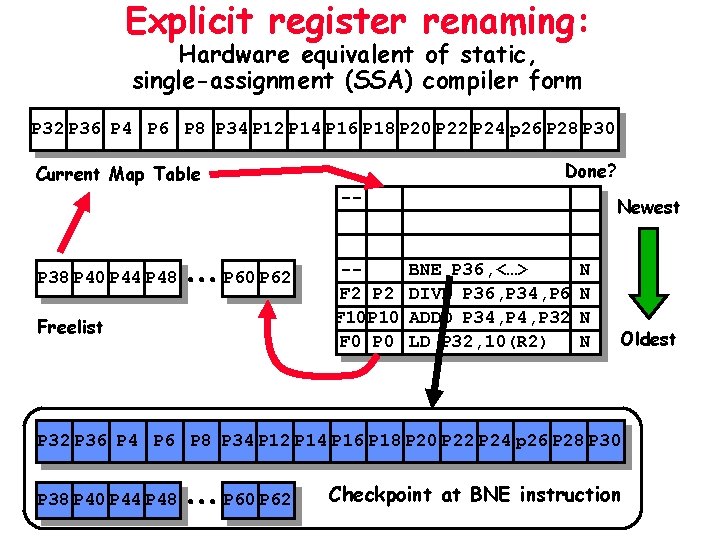

Explicit register renaming: Hardware equivalent of static, single-assignment (SSA) compiler form P 32 P 36 P 4 P 6 P 8 P 34 P 12 P 14 P 16 P 18 P 20 P 22 P 24 p 26 P 28 P 30 Done? Current Map Table -- P 38 P 40 P 44 P 48 P 60 P 62 Freelist -F 2 P 2 F 10 P 10 F 0 P 0 Newest BNE P 36, <…> DIVD P 36, P 34, P 6 ADDD P 34, P 32 LD P 32, 10(R 2) N N Oldest P 32 P 36 P 4 P 6 P 8 P 34 P 12 P 14 P 16 P 18 P 20 P 22 P 24 p 26 P 28 P 30 P 38 P 40 P 44 P 48 P 60 P 62 Checkpoint at BNE instruction

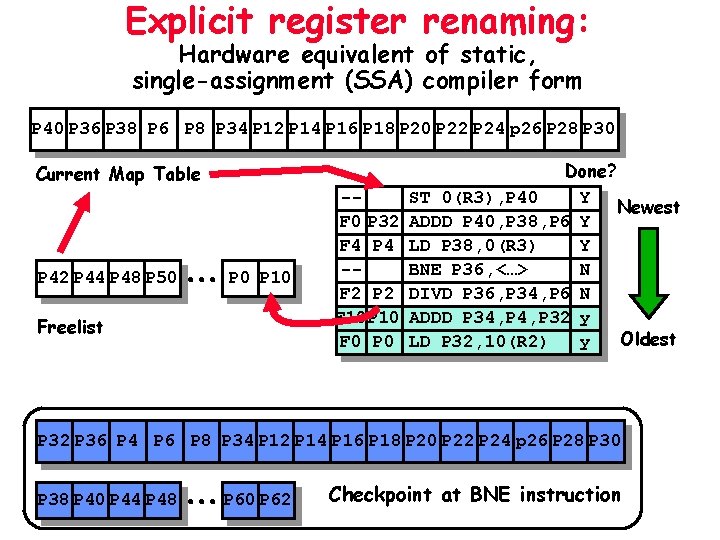

Explicit register renaming: Hardware equivalent of static, single-assignment (SSA) compiler form P 40 P 36 P 38 P 6 P 8 P 34 P 12 P 14 P 16 P 18 P 20 P 22 P 24 p 26 P 28 P 30 Current Map Table P 42 P 44 P 48 P 50 P 10 Freelist -F 0 P 32 F 4 P 4 -F 2 P 2 F 10 P 10 F 0 P 0 Done? ST 0(R 3), P 40 Y Newest ADDD P 40, P 38, P 6 Y LD P 38, 0(R 3) Y BNE P 36, <…> N DIVD P 36, P 34, P 6 N ADDD P 34, P 32 y Oldest LD P 32, 10(R 2) y P 32 P 36 P 4 P 6 P 8 P 34 P 12 P 14 P 16 P 18 P 20 P 22 P 24 p 26 P 28 P 30 P 38 P 40 P 44 P 48 P 60 P 62 Checkpoint at BNE instruction

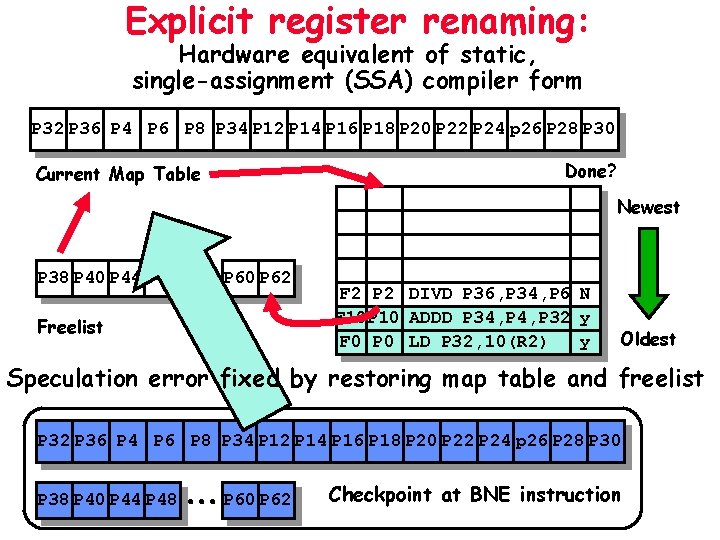

Explicit register renaming: Hardware equivalent of static, single-assignment (SSA) compiler form P 32 P 36 P 4 P 6 P 8 P 34 P 12 P 14 P 16 P 18 P 20 P 22 P 24 p 26 P 28 P 30 Current Map Table Done? Newest P 38 P 40 P 44 P 48 P 60 P 62 Freelist F 2 P 2 DIVD P 36, P 34, P 6 N F 10 P 10 ADDD P 34, P 32 y F 0 P 0 LD P 32, 10(R 2) y Oldest Speculation error fixed by restoring map table and freelist P 32 P 36 P 4 P 6 P 8 P 34 P 12 P 14 P 16 P 18 P 20 P 22 P 24 p 26 P 28 P 30 P 38 P 40 P 44 P 48 P 60 P 62 Checkpoint at BNE instruction

- Slides: 38