School of Engineering Heute ARM Befehlsstze ARM Instruction

School of Engineering Heute: - ARM Befehlssätze - ARM Instruction Pipeline - Branches & Bedingte Befehle

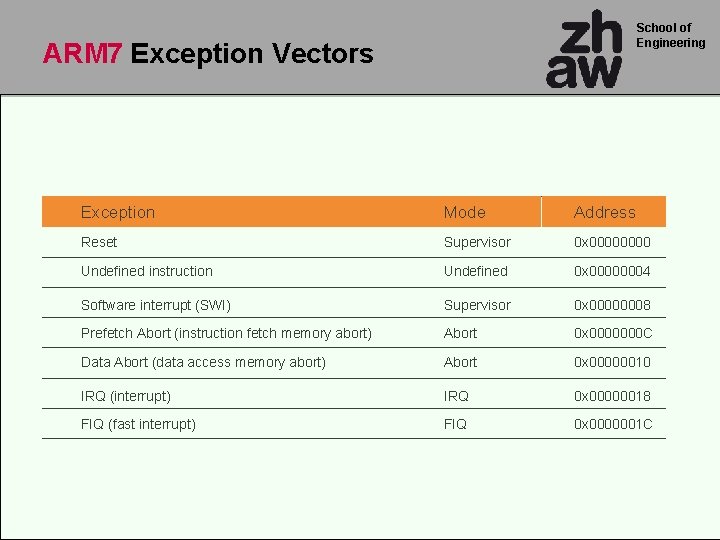

School of Engineering ARM 7 Exception Vectors Exception Mode Address Reset Supervisor 0 x 0000 Undefined instruction Undefined 0 x 00000004 Software interrupt (SWI) Supervisor 0 x 00000008 Prefetch Abort (instruction fetch memory abort) Abort 0 x 0000000 C Data Abort (data access memory abort) Abort 0 x 00000010 IRQ (interrupt) IRQ 0 x 00000018 FIQ (fast interrupt) FIQ 0 x 0000001 C

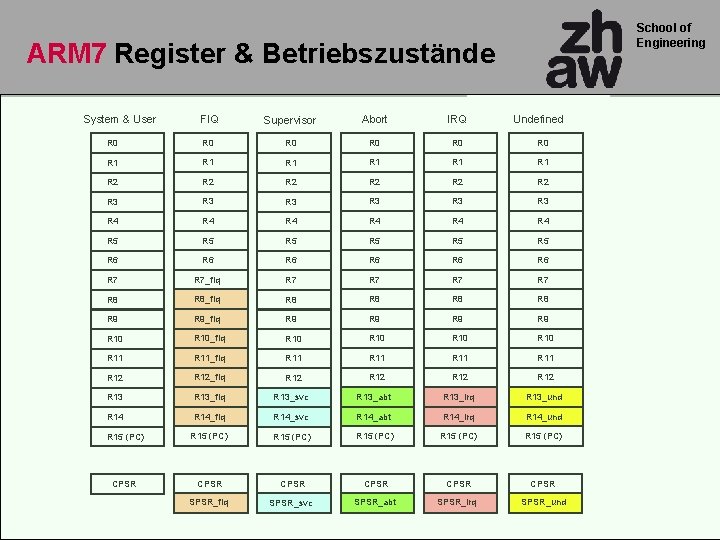

School of Engineering ARM 7 Register & Betriebszustände System & User FIQ Supervisor Abort IRQ Undefined R 0 R 0 R 0 R 1 R 1 R 1 R 2 R 2 R 2 R 3 R 3 R 3 R 4 R 4 R 4 R 5 R 5 R 5 R 6 R 6 R 6 R 7_fiq R 7 R 7 R 8_fiq R 8 R 8 R 9_fiq R 9 R 9 R 10_fiq R 10 R 11_fiq R 11 R 12_fiq R 12 R 13_fiq R 13_svc R 13_abt R 13_irq R 13_und R 14_fiq R 14_svc R 14_abt R 14_irq R 14_und R 15 (PC) R 15 (PC) CPSR CPSR SPSR_fiq SPSR_svc SPSR_abt SPSR_irq SPSR_und

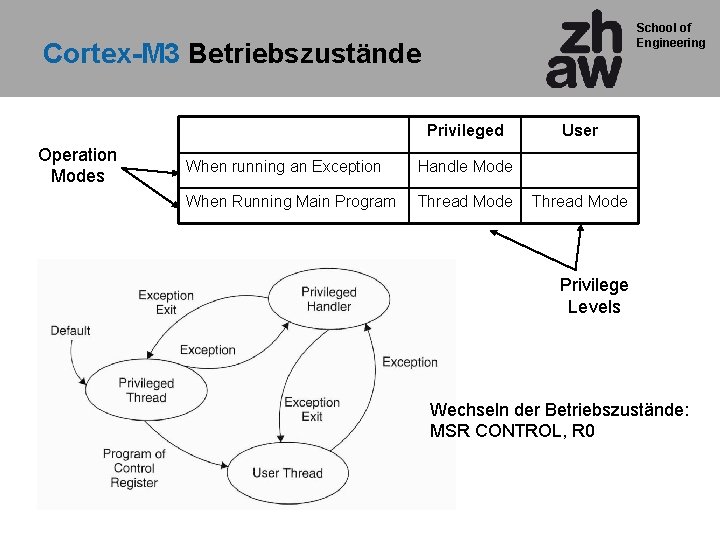

School of Engineering Cortex-M 3 Betriebszustände Privileged Operation Modes When running an Exception Handle Mode When Running Main Program Thread Mode User Thread Mode Privilege Levels Wechseln der Betriebszustände: MSR CONTROL, R 0

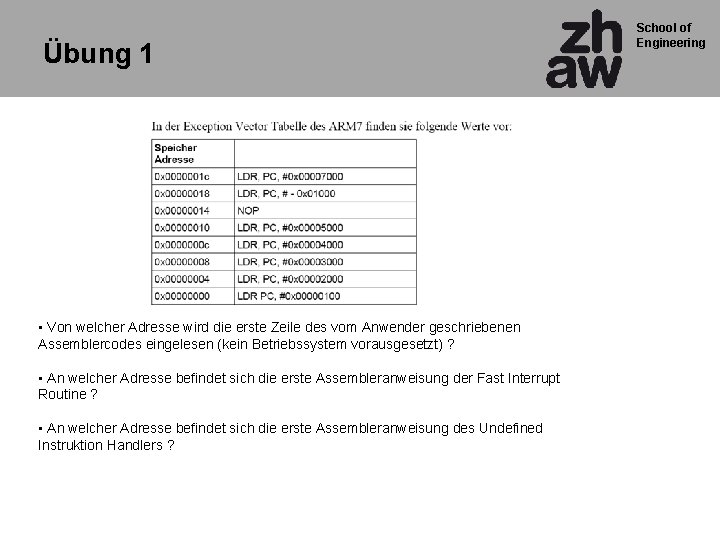

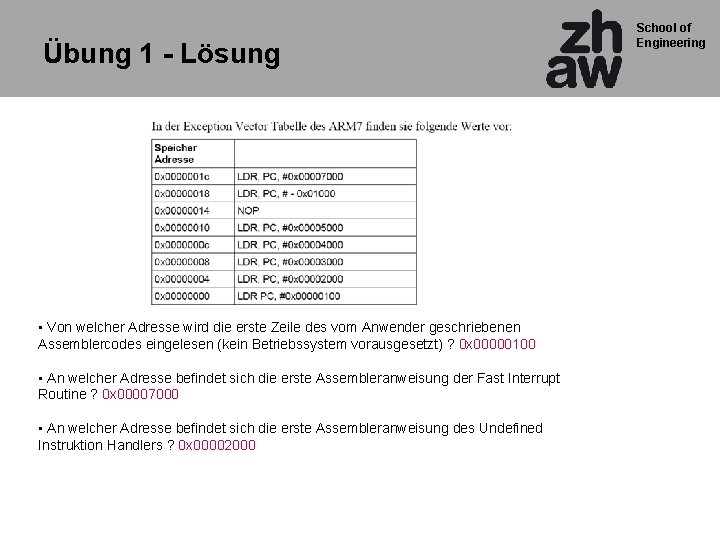

Übung 1 • Von welcher Adresse wird die erste Zeile des vom Anwender geschriebenen Assemblercodes eingelesen (kein Betriebssystem vorausgesetzt) ? • An welcher Adresse befindet sich die erste Assembleranweisung der Fast Interrupt Routine ? • An welcher Adresse befindet sich die erste Assembleranweisung des Undefined Instruktion Handlers ? School of Engineering

Übung 1 - Lösung • Von welcher Adresse wird die erste Zeile des vom Anwender geschriebenen Assemblercodes eingelesen (kein Betriebssystem vorausgesetzt) ? 0 x 00000100 • An welcher Adresse befindet sich die erste Assembleranweisung der Fast Interrupt Routine ? 0 x 00007000 • An welcher Adresse befindet sich die erste Assembleranweisung des Undefined Instruktion Handlers ? 0 x 00002000 School of Engineering

School of Engineering ARM Befehlssätze

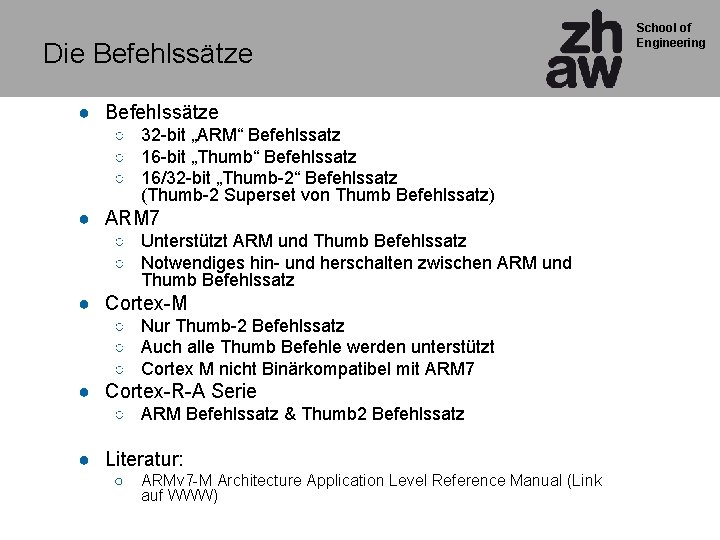

Die Befehlssätze ● Befehlssätze ○ 32 -bit „ARM“ Befehlssatz ○ 16 -bit „Thumb“ Befehlssatz ○ 16/32 -bit „Thumb-2“ Befehlssatz (Thumb-2 Superset von Thumb Befehlssatz) ● ARM 7 ○ Unterstützt ARM und Thumb Befehlssatz ○ Notwendiges hin- und herschalten zwischen ARM und Thumb Befehlssatz ● Cortex-M ○ Nur Thumb-2 Befehlssatz ○ Auch alle Thumb Befehle werden unterstützt ○ Cortex M nicht Binärkompatibel mit ARM 7 ● Cortex-R-A Serie ○ ARM Befehlssatz & Thumb 2 Befehlssatz ● Literatur: ○ ARMv 7 -M Architecture Application Level Reference Manual (Link auf WWW) School of Engineering

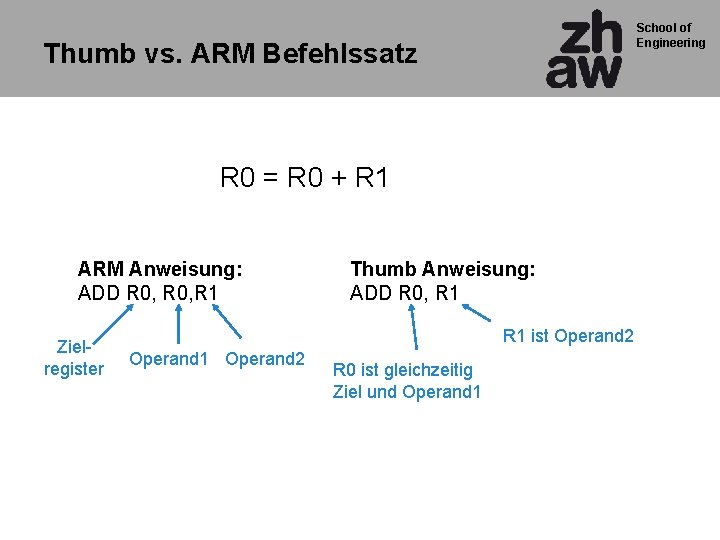

School of Engineering Thumb vs. ARM Befehlssatz R 0 = R 0 + R 1 ARM Anweisung: ADD R 0, R 1 Zielregister Thumb Anweisung: ADD R 0, R 1 ist Operand 2 Operand 1 Operand 2 R 0 ist gleichzeitig Ziel und Operand 1

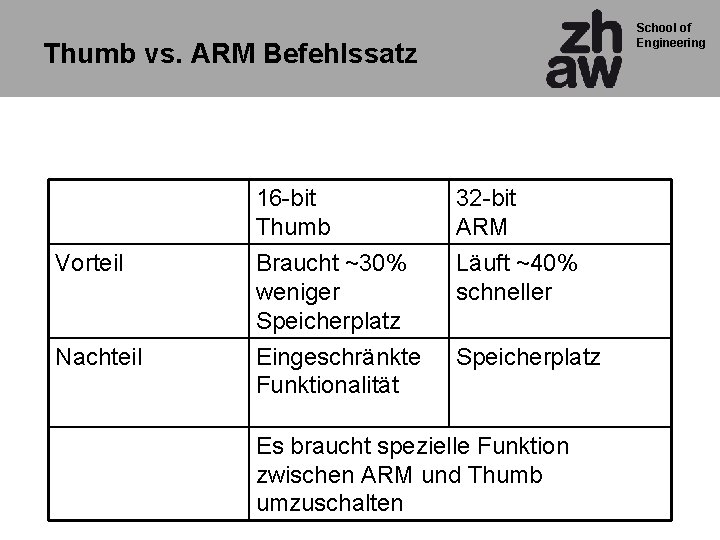

School of Engineering Thumb vs. ARM Befehlssatz 16 -bit Thumb 32 -bit ARM Vorteil Braucht ~30% weniger Speicherplatz Läuft ~40% schneller Nachteil Eingeschränkte Funktionalität Speicherplatz Es braucht spezielle Funktion zwischen ARM und Thumb umzuschalten

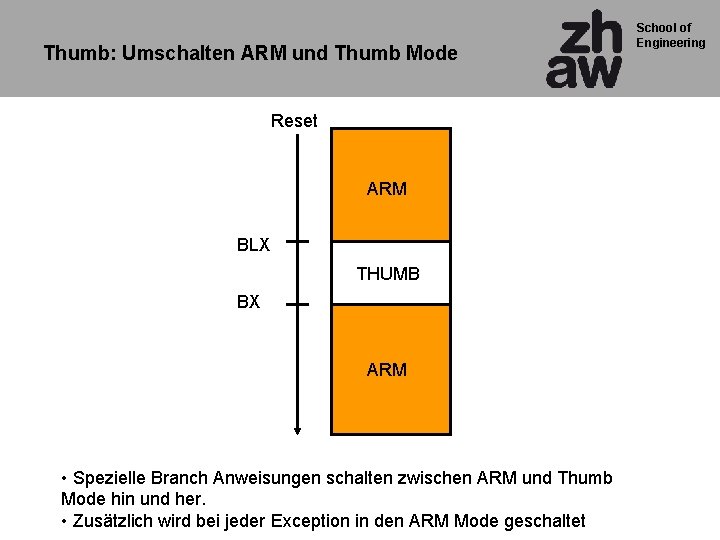

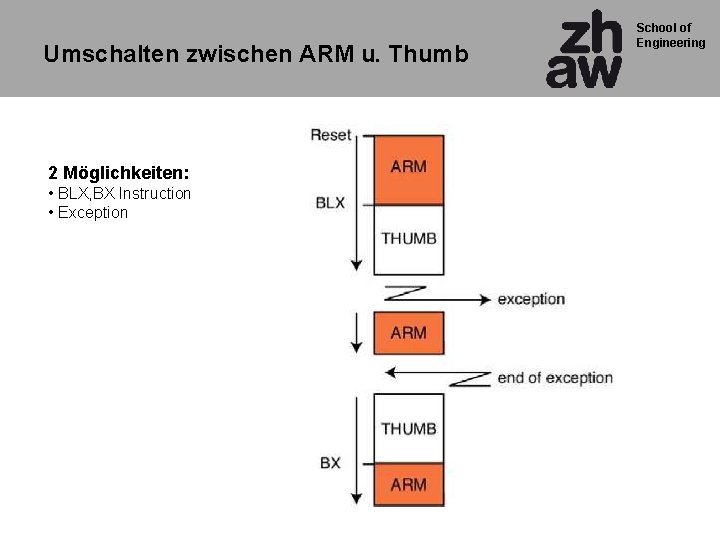

Thumb: Umschalten ARM und Thumb Mode Reset ARM BLX THUMB BX ARM • Spezielle Branch Anweisungen schalten zwischen ARM und Thumb Mode hin und her. • Zusätzlich wird bei jeder Exception in den ARM Mode geschaltet School of Engineering

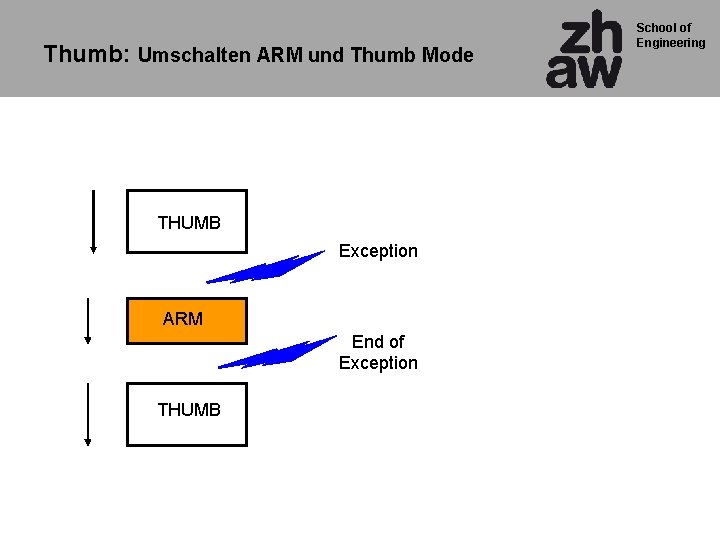

Thumb: Umschalten ARM und Thumb Mode THUMB Exception ARM End of Exception THUMB School of Engineering

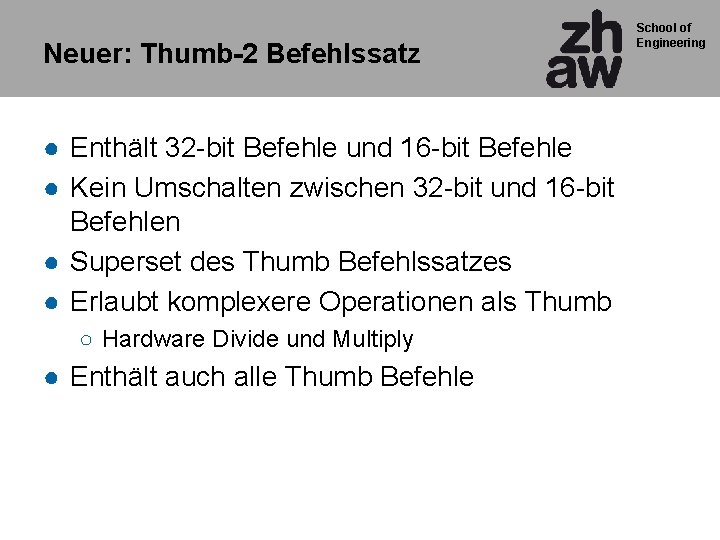

Neuer: Thumb-2 Befehlssatz ● Enthält 32 -bit Befehle und 16 -bit Befehle ● Kein Umschalten zwischen 32 -bit und 16 -bit Befehlen ● Superset des Thumb Befehlssatzes ● Erlaubt komplexere Operationen als Thumb ○ Hardware Divide und Multiply ● Enthält auch alle Thumb Befehle School of Engineering

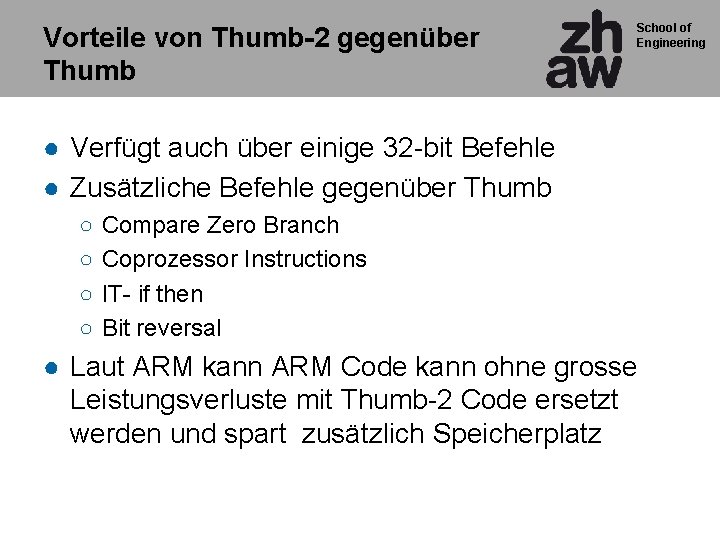

Vorteile von Thumb-2 gegenüber Thumb School of Engineering ● Verfügt auch über einige 32 -bit Befehle ● Zusätzliche Befehle gegenüber Thumb ○ ○ Compare Zero Branch Coprozessor Instructions IT- if then Bit reversal ● Laut ARM kann ARM Code kann ohne grosse Leistungsverluste mit Thumb-2 Code ersetzt werden und spart zusätzlich Speicherplatz

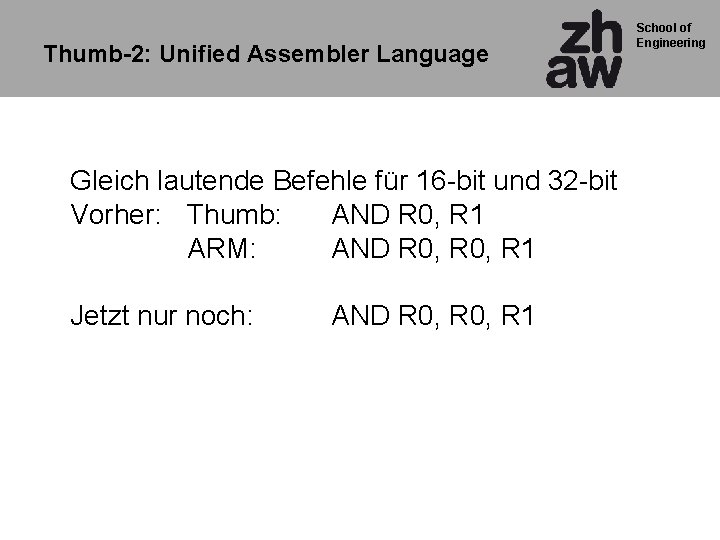

Thumb-2: Unified Assembler Language Gleich lautende Befehle für 16 -bit und 32 -bit Vorher: Thumb: AND R 0, R 1 ARM: AND R 0, R 1 Jetzt nur noch: AND R 0, R 1 School of Engineering

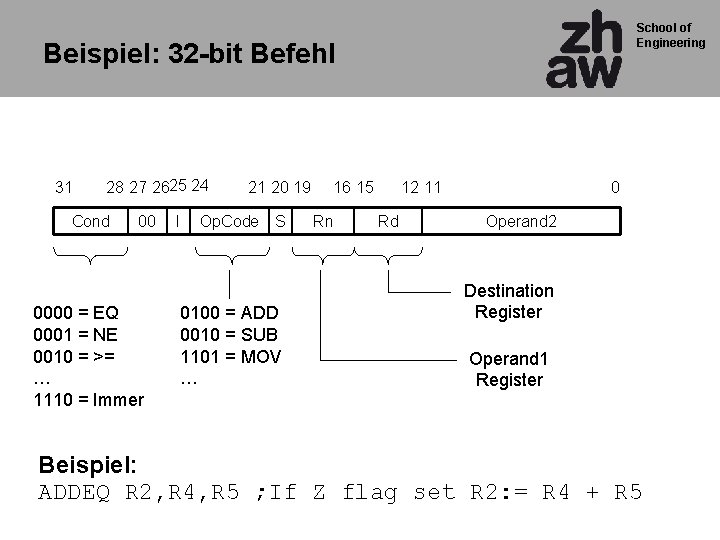

School of Engineering Beispiel: 32 -bit Befehl 31 28 27 2625 24 Cond 00 0000 = EQ 0001 = NE 0010 = >= … 1110 = Immer I 21 20 19 Op. Code S 0100 = ADD 0010 = SUB 1101 = MOV … 16 15 Rn 12 11 Rd 0 Operand 2 Destination Register Operand 1 Register Beispiel: ADDEQ R 2, R 4, R 5 ; If Z flag set R 2: = R 4 + R 5

School of Engineering Beispiel: 16 -bit Befehl 15 14 0 1 13 12 11 10 0 0 9 8 7 Op 6 5 4 3 2 1 0 Rs Rd Source/Destination Register • Thumb hat keine Conditional Instruction • Thumb-2 hat IT (If Then Instruction und CZB (compare zero branch) Source Register 2 0101 = ADC 0110 = SBC 0000 = AND …

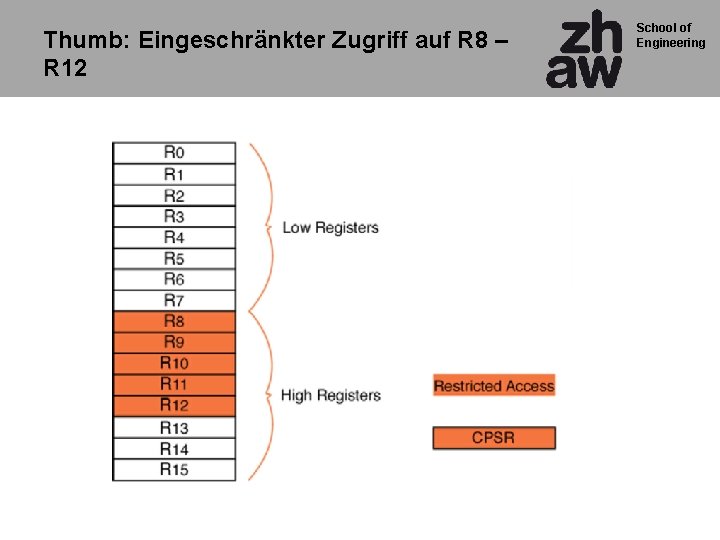

Thumb: Eingeschränkter Zugriff auf R 8 – R 12 School of Engineering

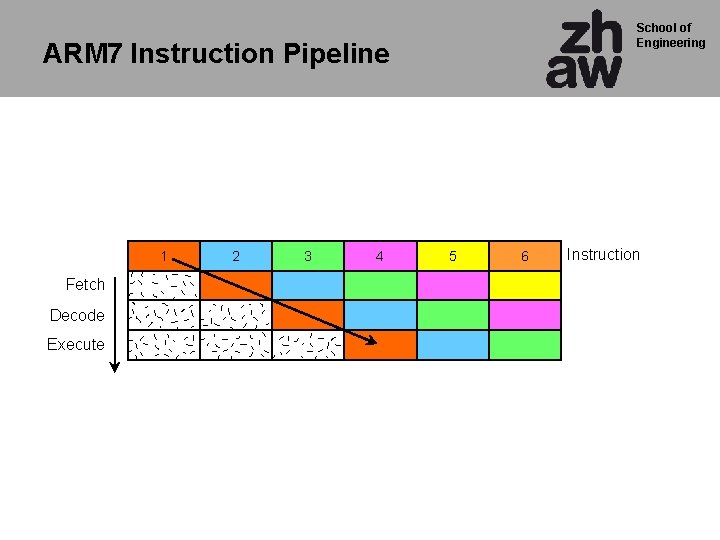

School of Engineering ARM Instruction Pipeline

School of Engineering ARM 7 Instruction Pipeline 1 Fetch Decode Execute 2 3 4 5 6 Instruction

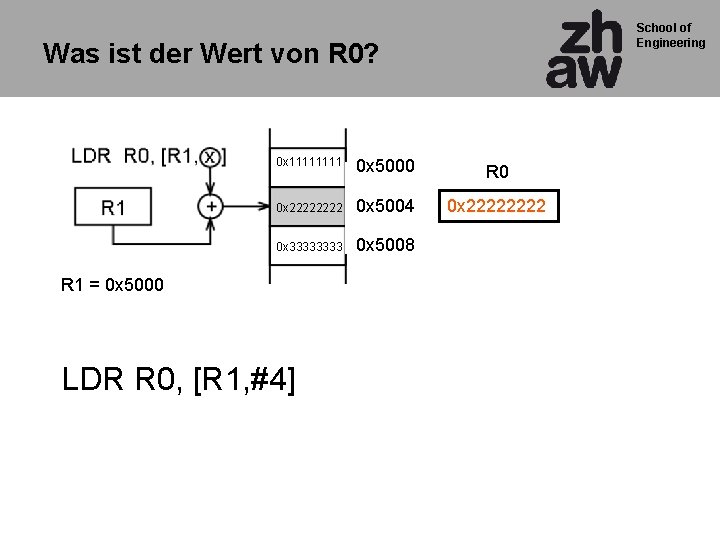

School of Engineering Was ist der Wert von R 0? 0 x 1111 0 x 5000 R 0 0 x 2222 0 x 5004 0 x 2222 0 x 3333 0 x 5008 R 1 = 0 x 5000 LDR R 0, [R 1, #4]

![Welche Adresse steht danach im PC? 0 x 4000 LDR PC, [PC, #4] PC Welche Adresse steht danach im PC? 0 x 4000 LDR PC, [PC, #4] PC](http://slidetodoc.com/presentation_image_h/cd40390c7ab6d91a45101713558573b4/image-22.jpg)

Welche Adresse steht danach im PC? 0 x 4000 LDR PC, [PC, #4] PC PC 0 x 0000400 c LDR PC, [PC, #4] 0 x 4000 0 x 2222 0 x 4004 0 x 3333 0 x 4008 0 x 4444 0 x 400 C School of Engineering

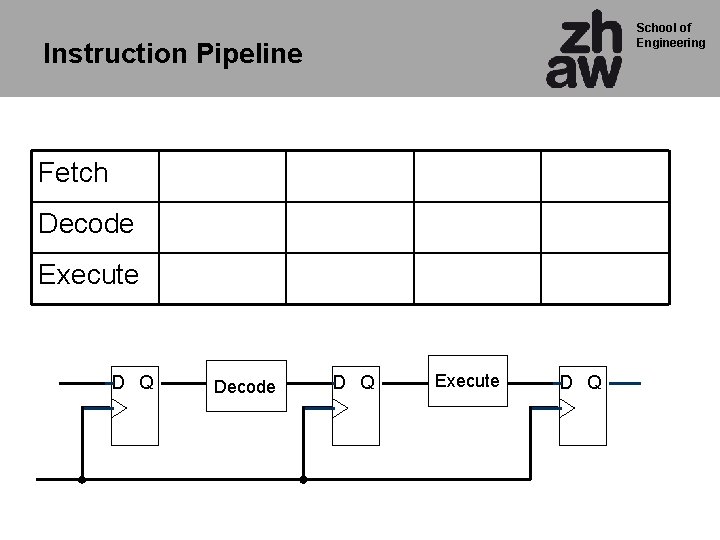

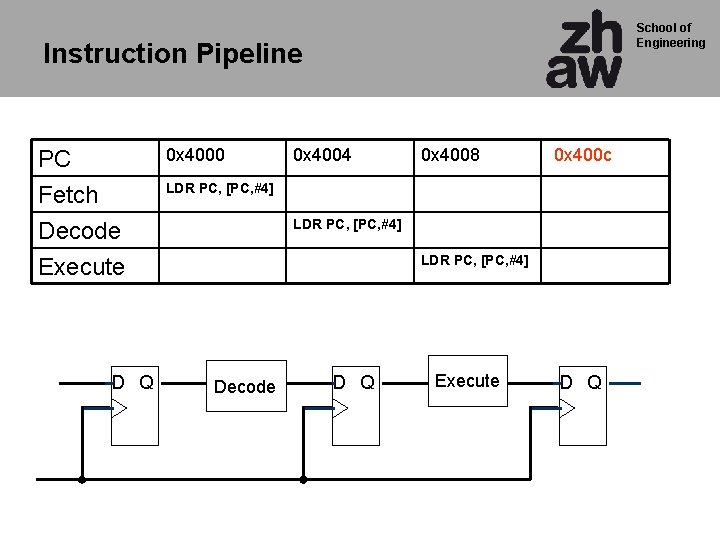

School of Engineering Instruction Pipeline Fetch Decode Execute D Q Decode D Q Execute D Q

School of Engineering Instruction Pipeline PC Fetch Decode Execute D Q 0 x 4000 0 x 4004 0 x 4008 0 x 400 c LDR PC, [PC, #4] Decode D Q Execute D Q

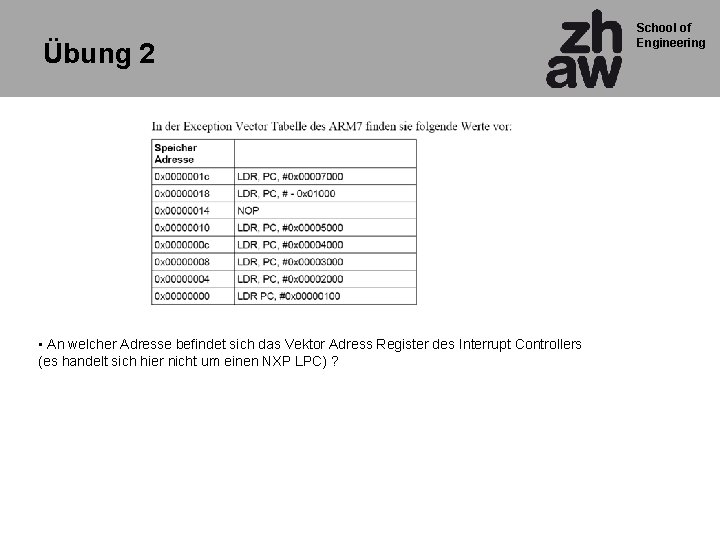

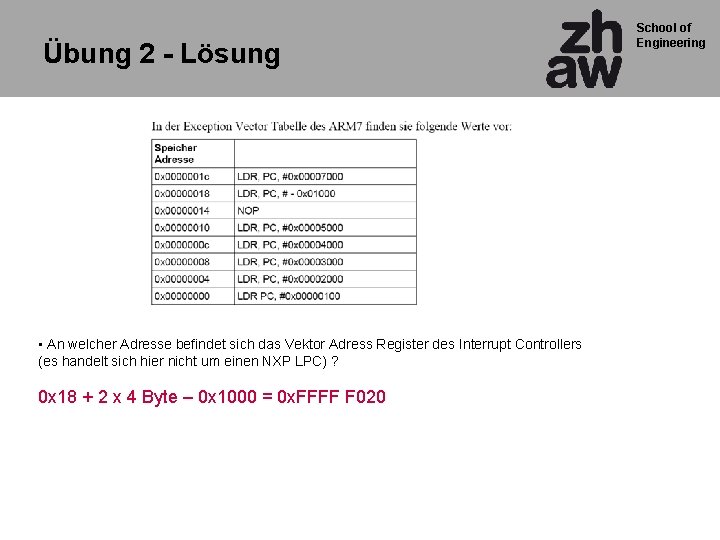

Übung 2 • An welcher Adresse befindet sich das Vektor Adress Register des Interrupt Controllers (es handelt sich hier nicht um einen NXP LPC) ? School of Engineering

Übung 2 - Lösung • An welcher Adresse befindet sich das Vektor Adress Register des Interrupt Controllers (es handelt sich hier nicht um einen NXP LPC) ? 0 x 18 + 2 x 4 Byte – 0 x 1000 = 0 x. FFFF F 020 School of Engineering

School of Engineering Branches (Context Switch)

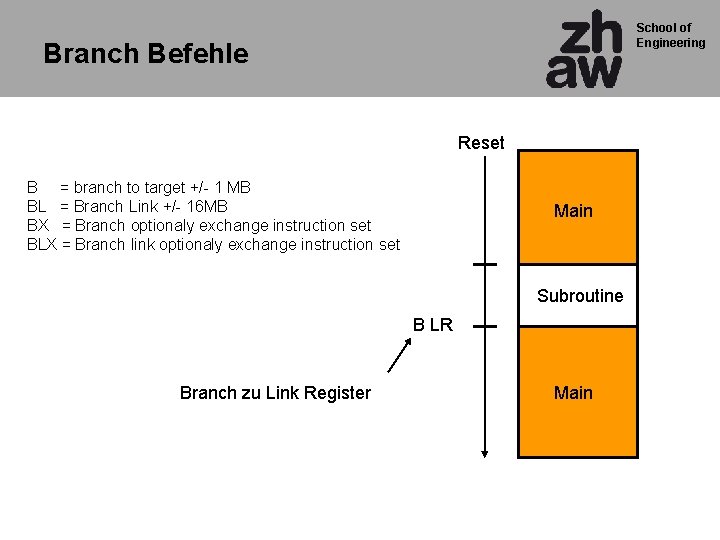

School of Engineering Branch Befehle Reset B = branch to target +/- 1 MB BL = Branch Link +/- 16 MB BX = Branch optionaly exchange instruction set BLX = Branch link optionaly exchange instruction set Main Subroutine B LR Branch zu Link Register Main

Umschalten zwischen ARM u. Thumb 2 Möglichkeiten: • BLX, BX Instruction • Exception School of Engineering

School of Engineering Einfacher Branch B = Branch zu Adresse 0 x 8000 LDR R 2, # 10 Bei einem Branch wird die gesamte Pipeline gespült (geflusht)

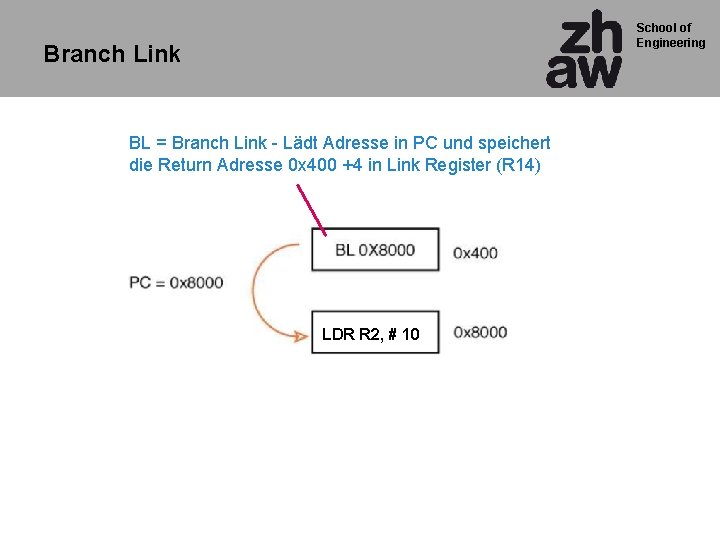

School of Engineering Branch Link BL = Branch Link - Lädt Adresse in PC und speichert die Return Adresse 0 x 400 +4 in Link Register (R 14) LDR R 2, # 10

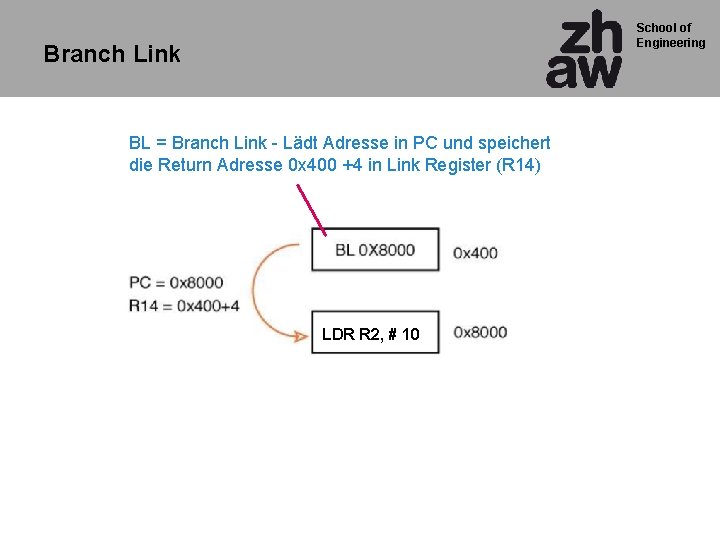

School of Engineering Branch Link BL = Branch Link - Lädt Adresse in PC und speichert die Return Adresse 0 x 400 +4 in Link Register (R 14) LDR R 2, # 10

School of Engineering Data Processing Instructions

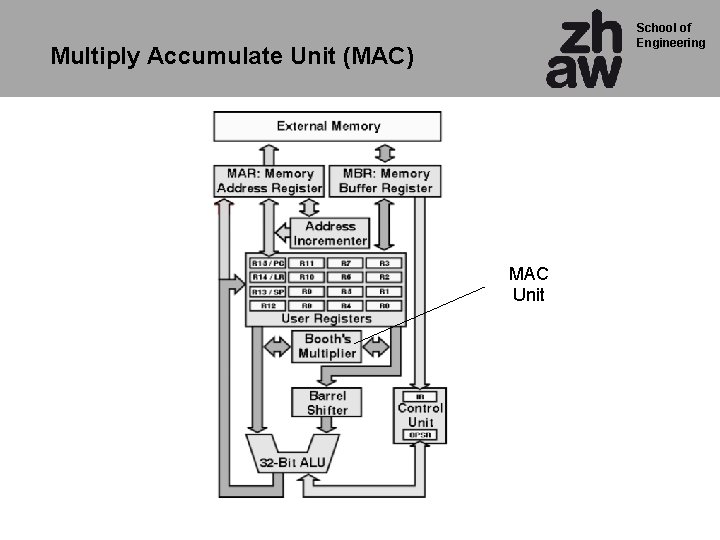

School of Engineering Multiply Accumulate Unit (MAC) MAC Unit

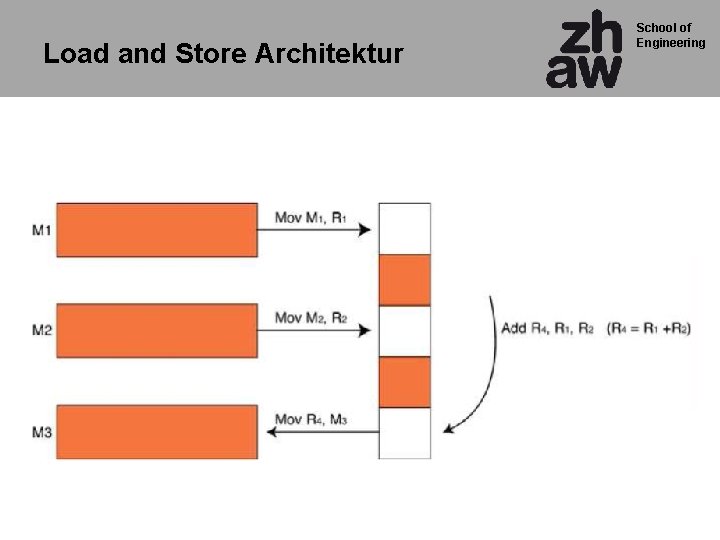

Load and Store Architektur School of Engineering

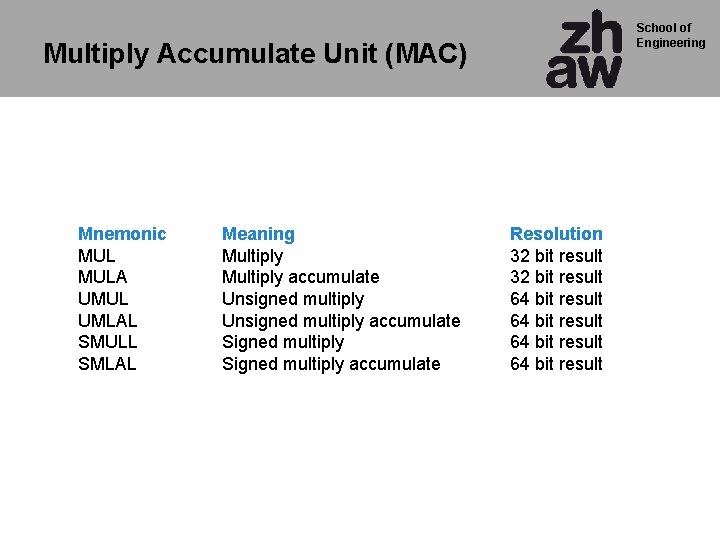

School of Engineering Multiply Accumulate Unit (MAC) Mnemonic MULA UMUL UMLAL SMULL SMLAL Meaning Multiply accumulate Unsigned multiply accumulate Signed multiply accumulate Resolution 32 bit result 64 bit result

Data Prozessing OP Codes Kürzel AND EOR SUB RSB ADD ADC SBC RSC TST TEQ CMP CMN ORR MOV BIC MVN Bedeutung Logical bitwise AND Logical bitwise exclusive OR Subtract Reverse Subtract Add with carry Subtract with carry Reverse Subtract with carry Test Equivalence Compare negated Logical bitwise OR Move Bit clear Move negated School of Engineering

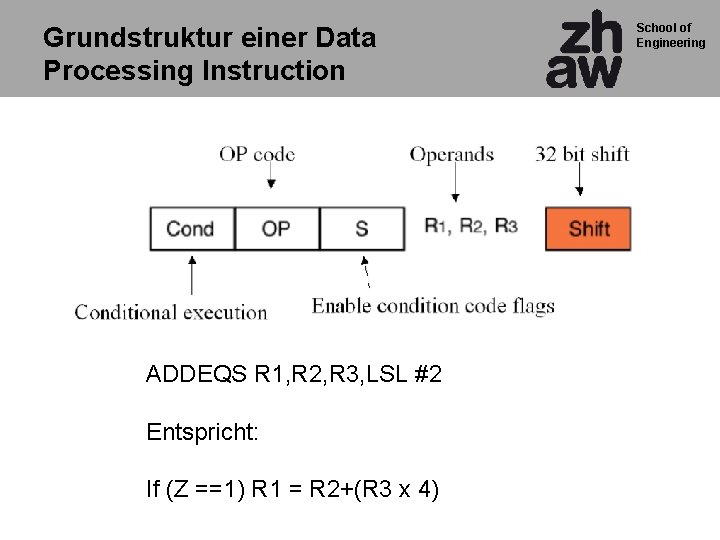

Grundstruktur einer Data Processing Instruction ADDEQS R 1, R 2, R 3, LSL #2 Entspricht: If (Z ==1) R 1 = R 2+(R 3 x 4) School of Engineering

School of Engineering Data Transfer Instructions

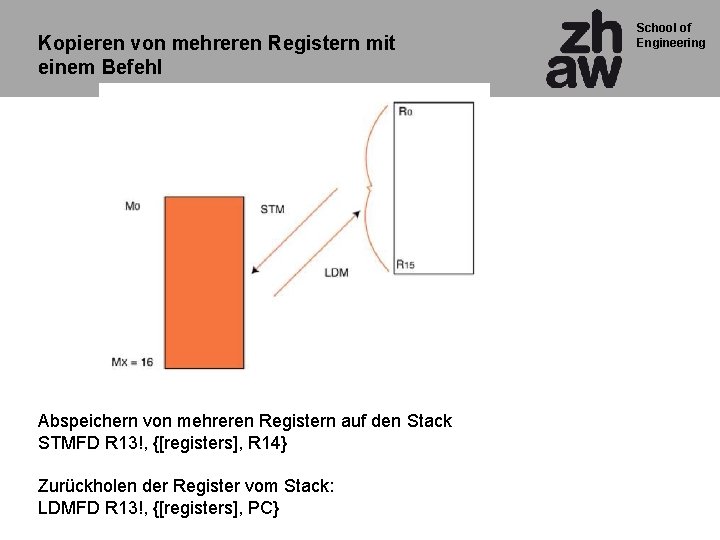

Kopieren von mehreren Registern mit einem Befehl Abspeichern von mehreren Registern auf den Stack STMFD R 13!, {[registers], R 14} Zurückholen der Register vom Stack: LDMFD R 13!, {[registers], PC} School of Engineering

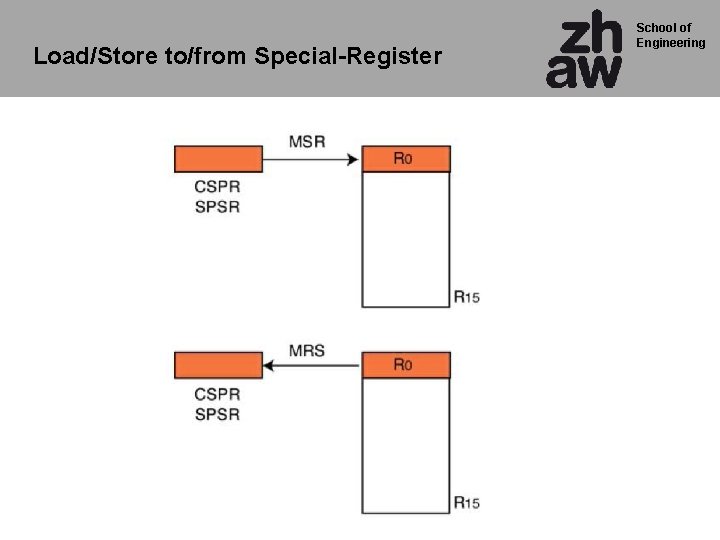

Load/Store to/from Special-Register School of Engineering

School of Engineering Bedingte Befehle Können zum Teil Branches ersetzen

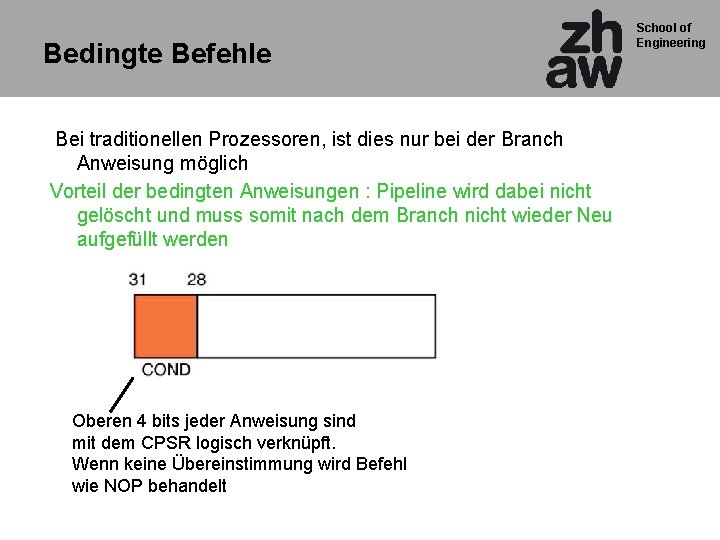

Bedingte Befehle Bei traditionellen Prozessoren, ist dies nur bei der Branch Anweisung möglich Vorteil der bedingten Anweisungen : Pipeline wird dabei nicht gelöscht und muss somit nach dem Branch nicht wieder Neu aufgefüllt werden Oberen 4 bits jeder Anweisung sind mit dem CPSR logisch verknüpft. Wenn keine Übereinstimmung wird Befehl wie NOP behandelt School of Engineering

School of Engineering Beispiel einer Instruktion mit Condition 31 28 27 2625 24 Cond 00 0000 = EQ 0001 = NE 0010 = >= … 1110 = Immer I 21 20 19 Op. Code S 0100 = ADD 0010 = SUB 1101 = MOV … 16 15 Rn 12 11 Rd 0 Operand 2 Destination Register Operand 1 Register Beispiel: ADDEQ R 2, R 4, R 5 ; If Z flag set R 2: = R 4 + R 5

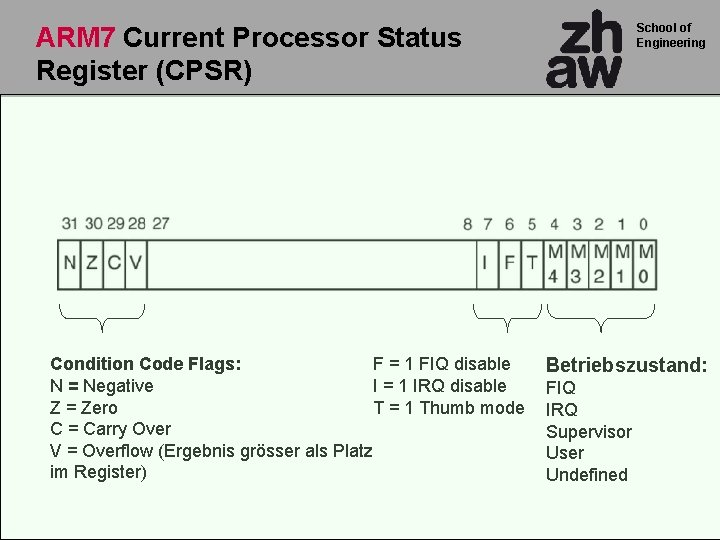

School of Engineering ARM 7 Current Processor Status Register (CPSR) Condition Code Flags: F = 1 FIQ disable N = Negative I = 1 IRQ disable Z = Zero T = 1 Thumb mode C = Carry Over V = Overflow (Ergebnis grösser als Platz im Register) Betriebszustand: FIQ IRQ Supervisor User Undefined

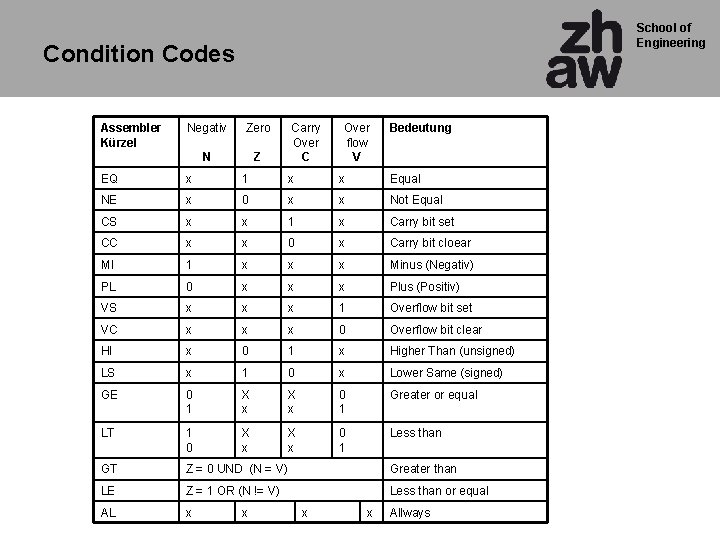

School of Engineering Condition Codes Assembler Kürzel Negativ Zero N Z Carry Over C Over flow V Bedeutung EQ x 1 x x Equal NE x 0 x x Not Equal CS x x 1 x Carry bit set CC x x 0 x Carry bit cloear MI 1 x x x Minus (Negativ) PL 0 x x x Plus (Positiv) VS x x x 1 Overflow bit set VC x x x 0 Overflow bit clear HI x 0 1 x Higher Than (unsigned) LS x 1 0 x Lower Same (signed) GE 0 1 X x 0 1 Greater or equal LT 1 0 X x 0 1 Less than GT Z = 0 UND (N = V) Greater than LE Z = 1 OR (N != V) Less than or equal AL x x Allways

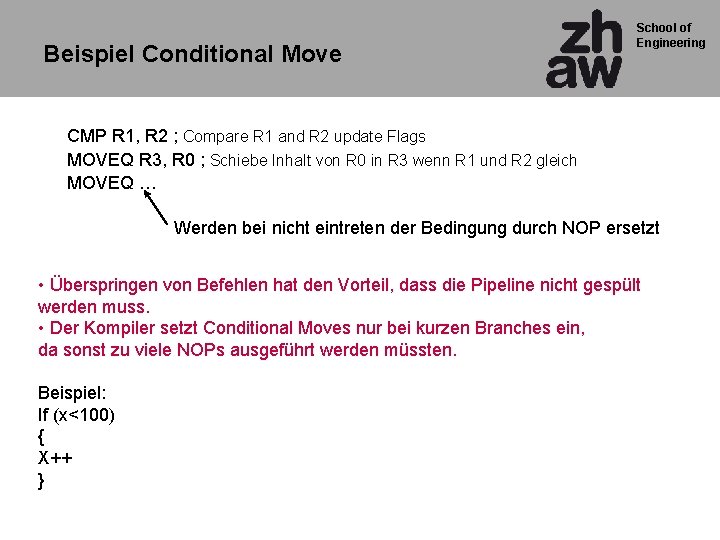

Beispiel Conditional Move School of Engineering CMP R 1, R 2 ; Compare R 1 and R 2 update Flags MOVEQ R 3, R 0 ; Schiebe Inhalt von R 0 in R 3 wenn R 1 und R 2 gleich MOVEQ … Werden bei nicht eintreten der Bedingung durch NOP ersetzt • Überspringen von Befehlen hat den Vorteil, dass die Pipeline nicht gespült werden muss. • Der Kompiler setzt Conditional Moves nur bei kurzen Branches ein, da sonst zu viele NOPs ausgeführt werden müssten. Beispiel: If (x<100) { X++ }

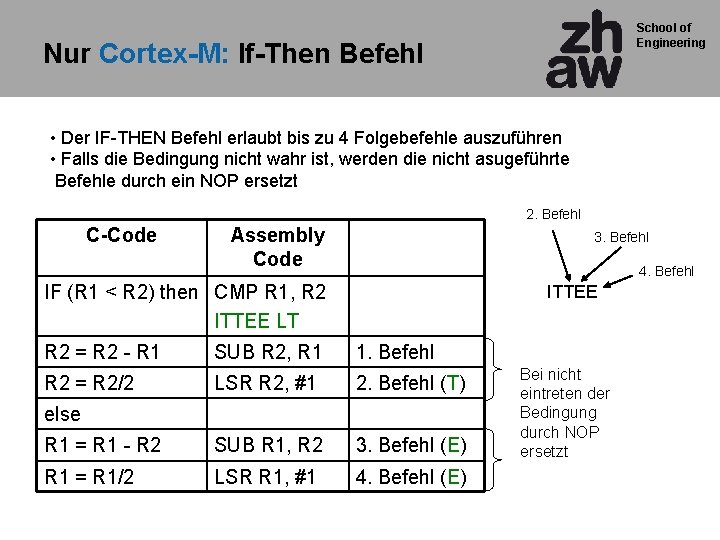

School of Engineering Nur Cortex-M: If-Then Befehl • Der IF-THEN Befehl erlaubt bis zu 4 Folgebefehle auszuführen • Falls die Bedingung nicht wahr ist, werden die nicht asugeführte Befehle durch ein NOP ersetzt 2. Befehl C-Code Assembly Code 3. Befehl 4. Befehl IF (R 1 < R 2) then CMP R 1, R 2 ITTEE LT ITTEE R 2 = R 2 - R 1 SUB R 2, R 1 1. Befehl R 2 = R 2/2 LSR R 2, #1 2. Befehl (T) R 1 = R 1 - R 2 SUB R 1, R 2 3. Befehl (E) R 1 = R 1/2 LSR R 1, #1 4. Befehl (E) else Bei nicht eintreten der Bedingung durch NOP ersetzt

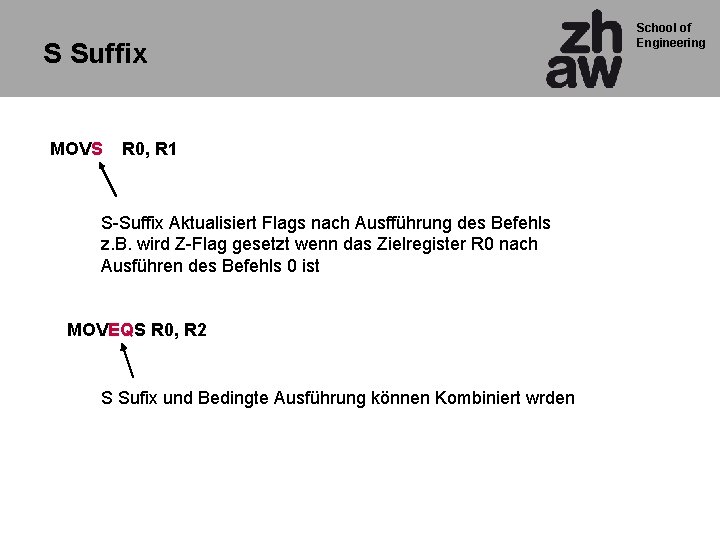

S Suffix MOVS R 0, R 1 S-Suffix Aktualisiert Flags nach Ausfführung des Befehls z. B. wird Z-Flag gesetzt wenn das Zielregister R 0 nach Ausführen des Befehls 0 ist MOVEQS R 0, R 2 S Sufix und Bedingte Ausführung können Kombiniert wrden School of Engineering

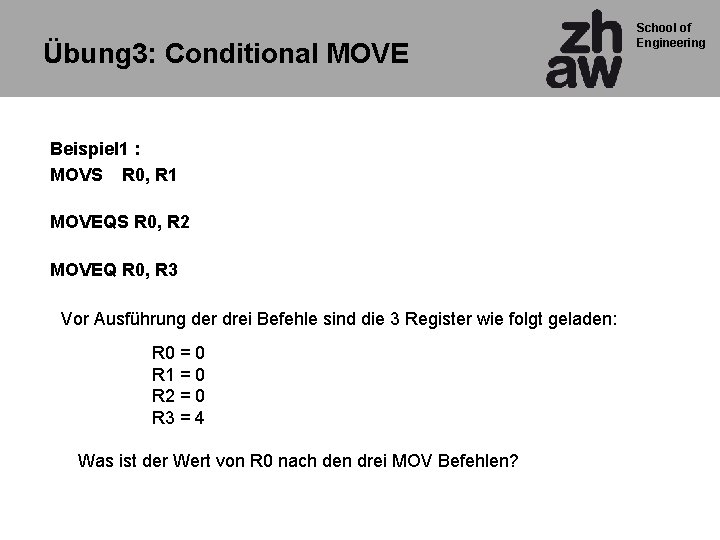

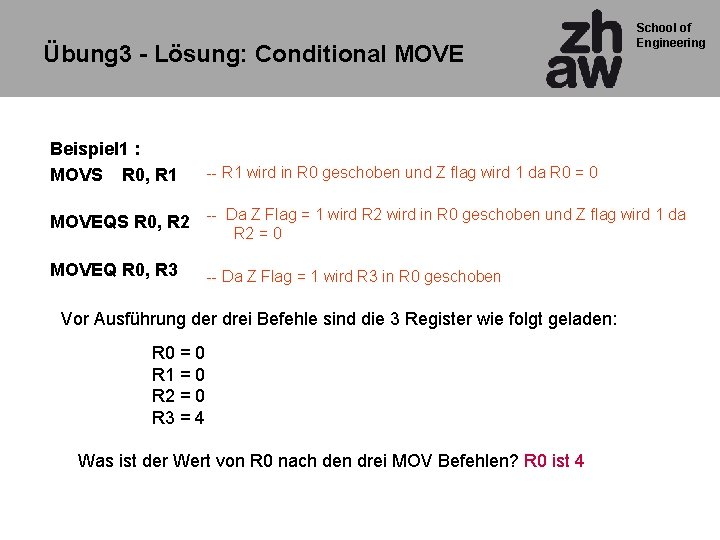

Übung 3: Conditional MOVE Beispiel 1 : MOVS R 0, R 1 MOVEQS R 0, R 2 MOVEQ R 0, R 3 Vor Ausführung der drei Befehle sind die 3 Register wie folgt geladen: R 0 = 0 R 1 = 0 R 2 = 0 R 3 = 4 Was ist der Wert von R 0 nach den drei MOV Befehlen? School of Engineering

Übung 3 - Lösung: Conditional MOVE Beispiel 1 : MOVS R 0, R 1 School of Engineering -- R 1 wird in R 0 geschoben und Z flag wird 1 da R 0 = 0 MOVEQS R 0, R 2 -- Da Z Flag = 1 wird R 2 wird in R 0 geschoben und Z flag wird 1 da R 2 = 0 MOVEQ R 0, R 3 -- Da Z Flag = 1 wird R 3 in R 0 geschoben Vor Ausführung der drei Befehle sind die 3 Register wie folgt geladen: R 0 = 0 R 1 = 0 R 2 = 0 R 3 = 4 Was ist der Wert von R 0 nach den drei MOV Befehlen? R 0 ist 4

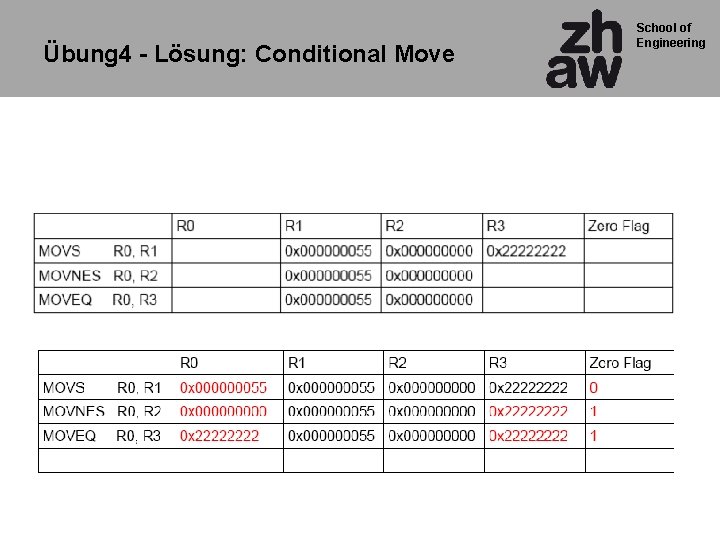

Übung 4: Conditional Move School of Engineering

Übung 4 - Lösung: Conditional Move School of Engineering

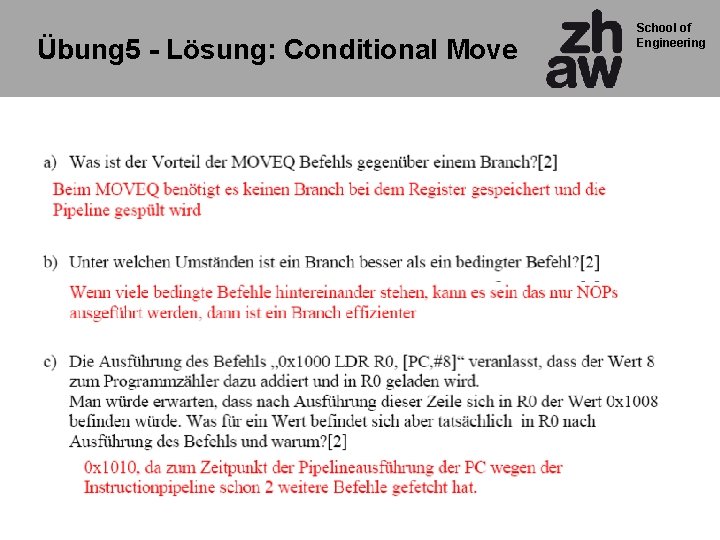

Übung 5: Conditional Move School of Engineering

Übung 5 - Lösung: Conditional Move School of Engineering

- Slides: 55