Schedulability Analysis and Optimization for the Synthesis of

Schedulability Analysis and Optimization for the Synthesis of Multi-Cluster Distributed Embedded Systems Paul Pop, Petru Eles, Zebo Peng Embedded Systems Lab (ESLAB) Linköping University, Sweden 1 of 1/15 14

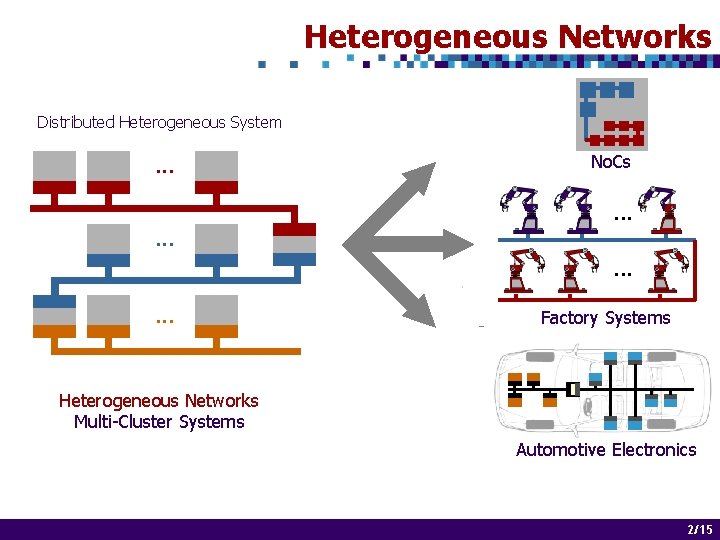

Heterogeneous Networks Distributed Heterogeneous System . . . No. Cs. . . Factory Systems Heterogeneous Networks Multi-Cluster Systems Automotive Electronics 2 of 2/15 14

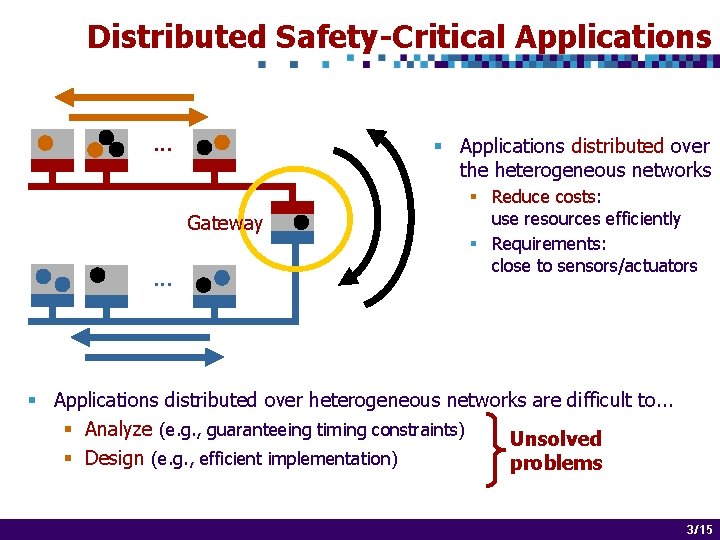

Distributed Safety-Critical Applications. . . § Applications distributed over the heterogeneous networks Gateway . . . § Reduce costs: use resources efficiently § Requirements: close to sensors/actuators § Applications distributed over heterogeneous networks are difficult to. . . § Analyze (e. g. , guaranteeing timing constraints) Unsolved § Design (e. g. , efficient implementation) problems 3 of 3/15 14

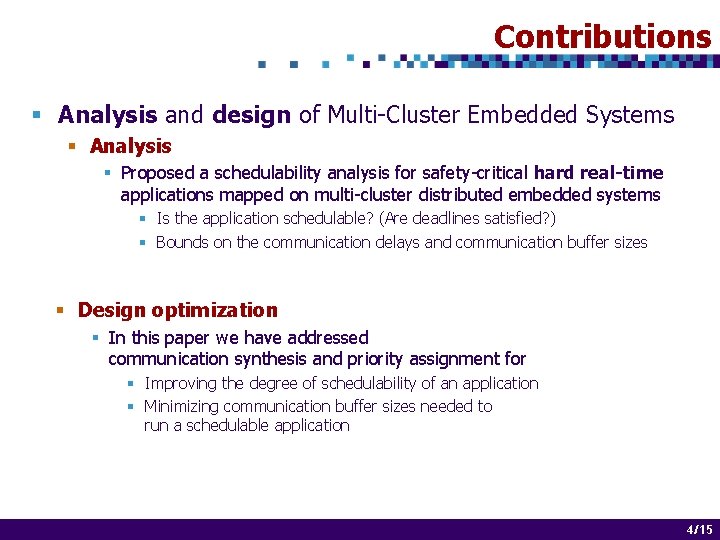

Contributions § Analysis and design of Multi-Cluster Embedded Systems § Analysis § Proposed a schedulability analysis for safety-critical hard real-time applications mapped on multi-cluster distributed embedded systems § Is the application schedulable? (Are deadlines satisfied? ) § Bounds on the communication delays and communication buffer sizes § Design optimization § Several In this paper designwe problems have addressed can be addressed once an analysissynthesis communication is available. and priority assignment for § Improving the degree of schedulability of an application § Minimizing communication buffer sizes needed to run a schedulable application 4 of 4/15 14

Outline § Motivation § Contributions System architecture and application model § Schedulability analysis for multi-clusters § Optimization strategies § Experimental results § Message and future work 5 of 5/15 14

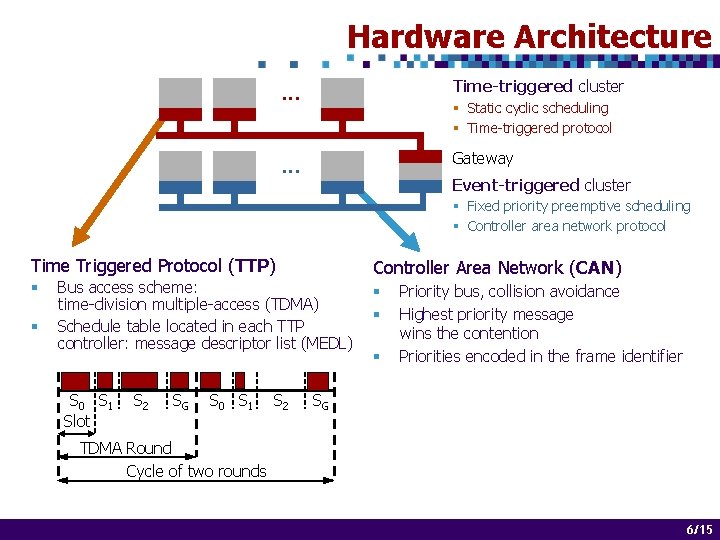

Hardware Architecture. . . Time-triggered cluster . . . Gateway § Static cyclic scheduling § Time-triggered protocol Event-triggered cluster § Fixed priority preemptive scheduling § Controller area network protocol Time Triggered Protocol (TTP) § § Bus access scheme: time-division multiple-access (TDMA) Schedule table located in each TTP controller: message descriptor list (MEDL) S 0 S 1 Slot S 2 SG S 0 S 1 S 2 Controller Area Network (CAN) § § § Priority bus, collision avoidance Highest priority message wins the contention Priorities encoded in the frame identifier SG TDMA Round Cycle of two rounds 6 of 6/15 14

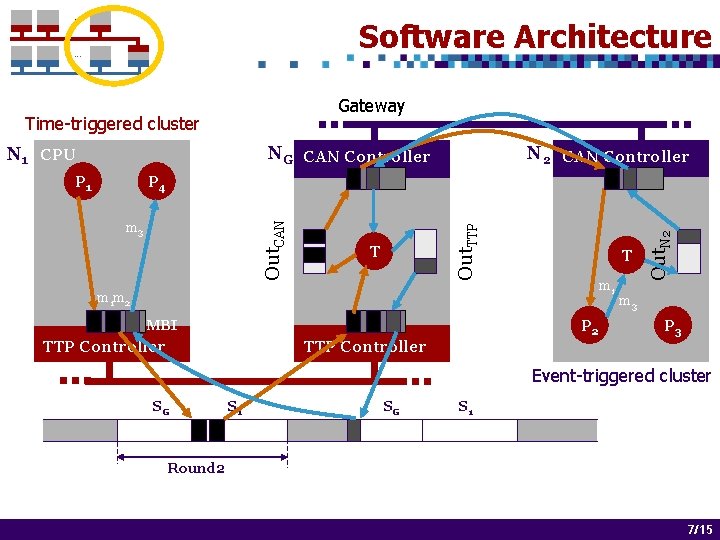

. . . Software Architecture . . . Gateway Time-triggered cluster NG CPU CAN Controller N 1 CPU Out. CAN m 3 T T m 1 m 2 P 2 MBI TTP Controller Out. N 2 P 4 Out. TTP P 1 N 2 CPU CAN Controller m 3 MBI P 3 Event-triggered cluster SG S 1 Round 2 7 of 7/15 14

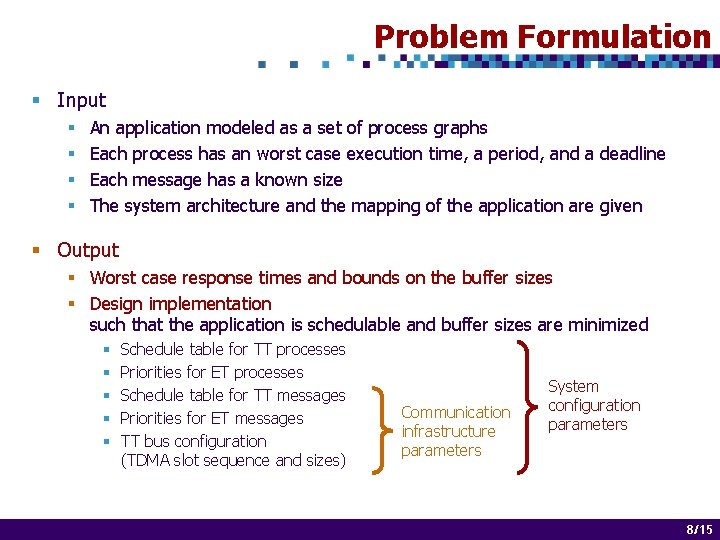

Problem Formulation § Input § § An application modeled as a set of process graphs Each process has an worst case execution time, a period, and a deadline Each message has a known size The system architecture and the mapping of the application are given § Output § Worst case response times and bounds on the buffer sizes. . . § Design implementation such that the application is schedulable and buffer sizes are minimized. . . § Schedule table for TT processes § Priorities for ET processes System § Schedule table for TT messages configuration Application: setfor of ET process graphs Mapping Architecture: Multi-cluster Communication § Priorities messages parameters infrastructure § TT bus configuration parameters (TDMA slot sequence and sizes) 8 of 8/15 14

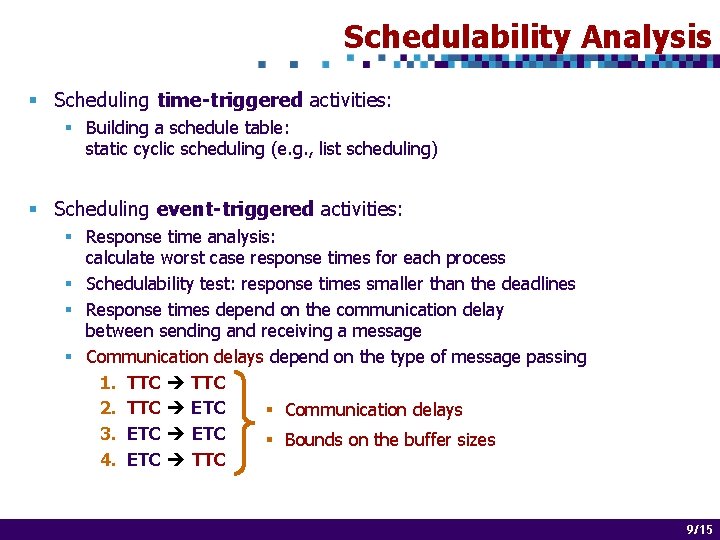

Schedulability Analysis § Scheduling time-triggered activities: § Building a schedule table: static cyclic scheduling (e. g. , list scheduling) § Scheduling event-triggered activities: § Response time analysis: calculate worst case response times for each process § Schedulability test: response times smaller than the deadlines § Response times depend on the communication delay between sending and receiving a message § Communication delays depend on the type of message passing 1. TTC 2. TTC ETC § Communication delays 3. ETC § Bounds on the buffer sizes 4. ETC TTC 9 of 9/15 14

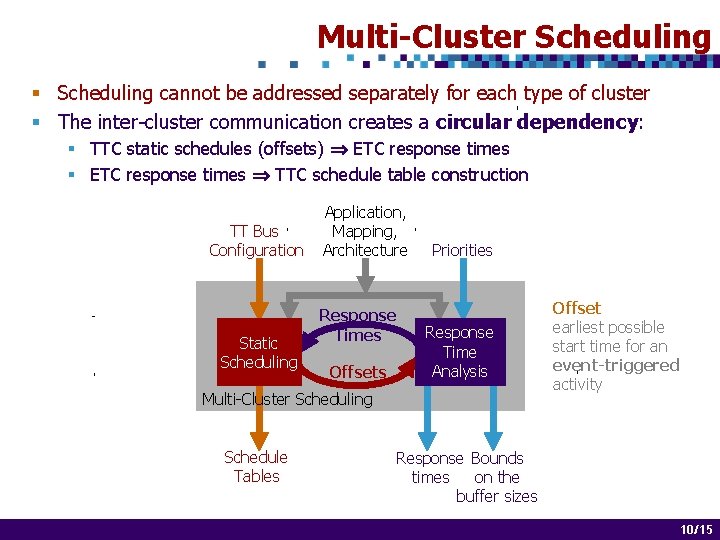

Multi-Cluster Scheduling § Scheduling cannot be addressed separately for each type of cluster § The inter-cluster communication creates a circular dependency: § TTC static schedules (offsets) ETC response times § ETC response times TTC schedule table construction TT Bus Configuration Static Scheduling Application, Mapping, Architecture Response Times Offsets Priorities Response Time Analysis Multi-Cluster Scheduling Schedule Tables Offset earliest possible start time for an event-triggered activity Response Bounds times on the buffer sizes 10 of 10/15 14

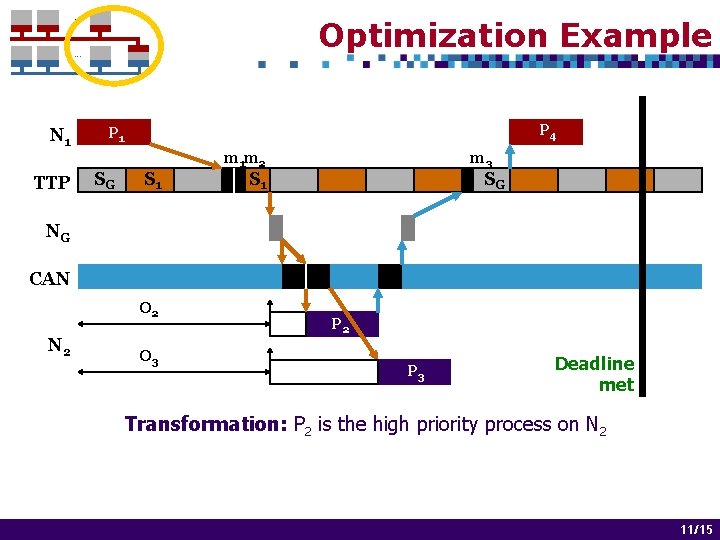

. . . Optimization Example . . . N 1 TTP P 4 P 1 S SG 1 m 1 m 2 SS G 1 m 3 SS G 1 SG m 3 SG P 4 m 3 SG NG CAN O 2 N 2 O 3 P 2 P 3 Deadline missed! met Transformation: S 1 is Pthe slot, high m priority process on Nsooner 2 isfirst 1 and m 2 are sent 2 11 of 11/15 14

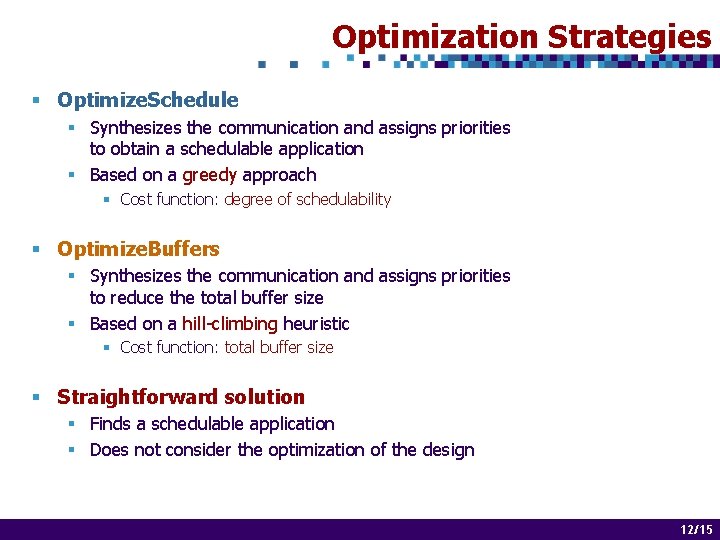

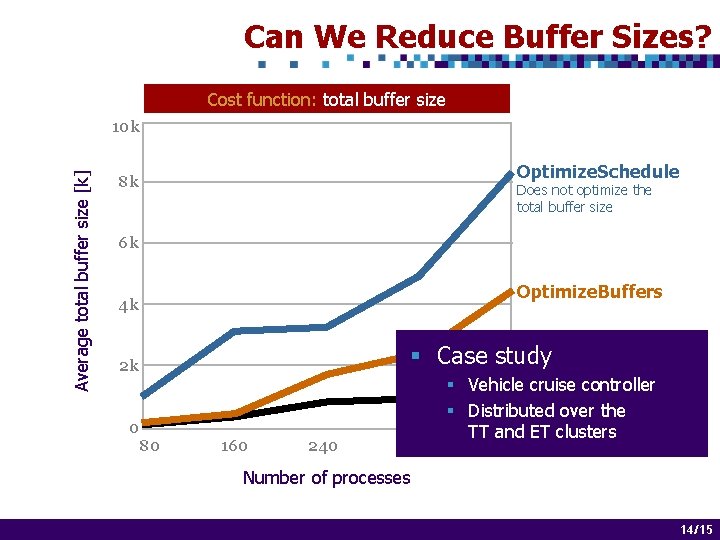

Optimization Strategies § Optimize. Schedule § Synthesizes the communication and assigns priorities to obtain a schedulable application § Based on a greedy approach § Cost function: degree of schedulability § Optimize. Buffers § Synthesizes the communication and assigns priorities to reduce the total buffer size § Based on a hill-climbing heuristic § Cost function: total buffer size § Straightforward solution § Finds a schedulable application § Does not consider the optimization of the design 12 of 12/15 14

![Can We Improve Schedulability? Average Percentage Deviation [%] Cost function: degree of schedulability Straightforward Can We Improve Schedulability? Average Percentage Deviation [%] Cost function: degree of schedulability Straightforward](http://slidetodoc.com/presentation_image_h2/c86fe3a11253492a9d17c831096702c1/image-13.jpg)

Can We Improve Schedulability? Average Percentage Deviation [%] Cost function: degree of schedulability Straightforward solution 120 Does not perform optimizations 100 80 60 Optimize. Schedule? 40 Optimize. Schedule 20 0 80 160 240 320 Number of processes Simulated Annealing 400 Near-optimal values for the degree of schedulability 13 of 13/15 14

Can We Reduce Buffer Sizes? Cost function: total buffer size Average total buffer size [k] 10 k Optimize. Schedule 8 k Does not optimize the total buffer size 6 k Optimize. Buffers? Optimize. Buffers 4 k Simulated Annealing § Case study Near-optimal values for the 2 k 0 80 160 240 320 § Vehicletotal cruise buffercontroller size § Distributed over the TT and ET clusters 400 Number of processes 14 of 14/15 14

Message and Future Work Analysis and optimization methods are needed for the efficient implementation of applications distributed over interconnected heterogeneous networks. § Future Work § Explore more design problems § Mapping for multi-clusters § How to partition an application in ET and TT activities? 15 of 15/15 14

- Slides: 15