ScanFlash ADC Low Power HighThroughput AD Converters Melvin

![Target Specifications • • 2 Channels [2 -Scan-Flash ADC] 8 bit per channel Power Target Specifications • • 2 Channels [2 -Scan-Flash ADC] 8 bit per channel Power](https://slidetodoc.com/presentation_image_h/b11dfe76b8780b93c9e117543bbe8042/image-10.jpg)

- Slides: 51

Scan-Flash ADC Low Power, High-Throughput AD Converters Melvin Eze Pennsylvania State University eze@cse. psu. edu Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Outline • • • ADC Converters Flash ADC Scan-Flash Architecture Target Specifications Schedule References Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

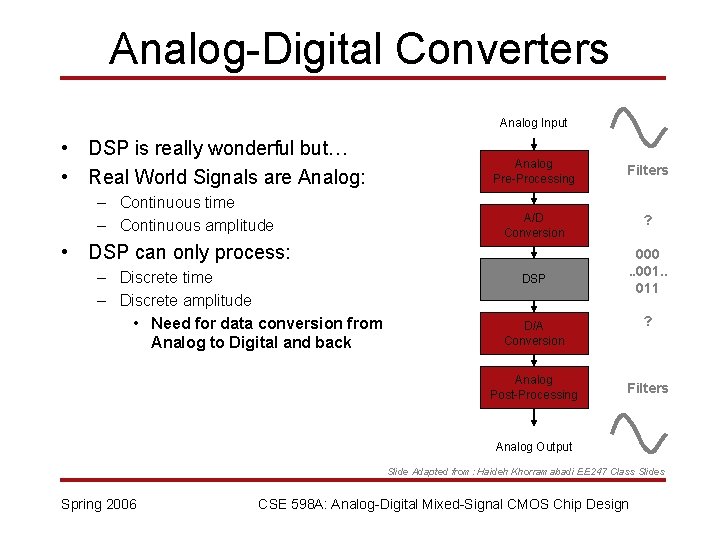

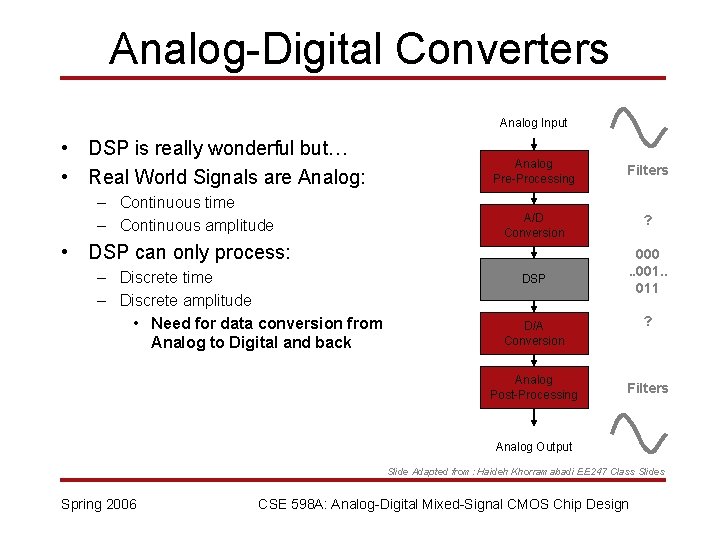

Analog-Digital Converters Analog Input • DSP is really wonderful but… • Real World Signals are Analog: – Continuous time – Continuous amplitude Analog Pre-Processing Filters A/D Conversion ? • DSP can only process: – Discrete time – Discrete amplitude • Need for data conversion from Analog to Digital and back DSP 000. . 001. . 011 ? D/A Conversion Analog Post-Processing Filters Analog Output Slide Adapted from: Haideh Khorramabadi EE 247 Class Slides Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

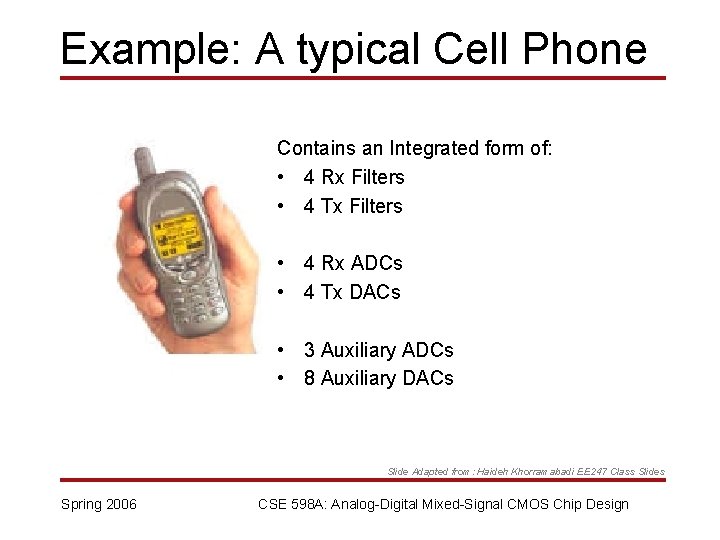

Example: A typical Cell Phone Contains an Integrated form of: • 4 Rx Filters • 4 Tx Filters • 4 Rx ADCs • 4 Tx DACs • 3 Auxiliary ADCs • 8 Auxiliary DACs Slide Adapted from: Haideh Khorramabadi EE 247 Class Slides Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

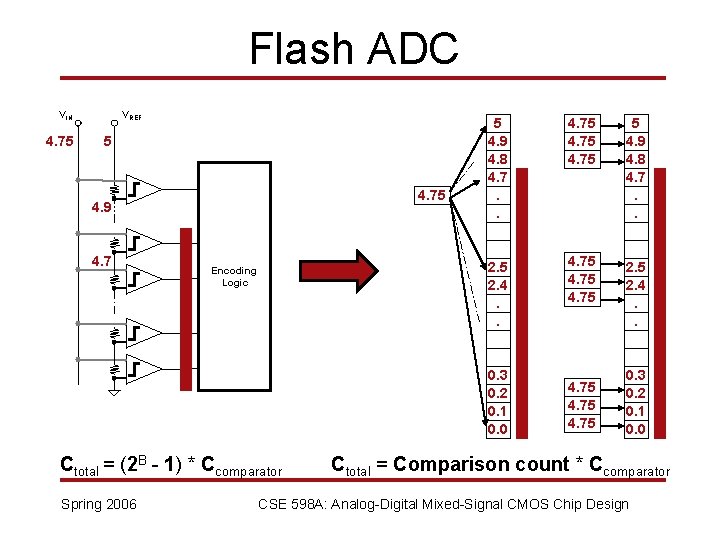

Flash ADC Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

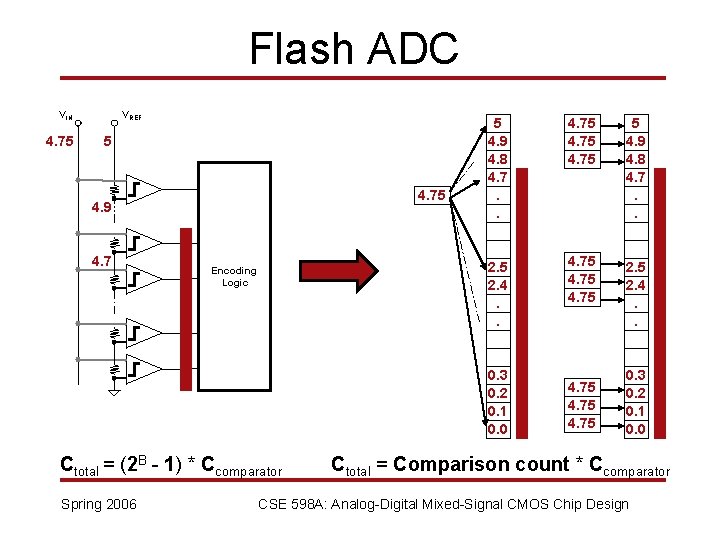

Flash ADC VIN 4. 75 VREF 5 4. 75 4. 9 4. 7 Encoding Logic 5 4. 9 4. 8 4. 7. . 4. 75 5 4. 9 4. 8 4. 7. . 2. 5 2. 4. 75 2. 4. . 0. 3 0. 2 0. 1 0. 0 Ctotal = (2 B - 1) * Ccomparator Spring 2006 4. 75 0. 3 0. 2 0. 1 0. 0 Ctotal = Comparison count * Ccomparator CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

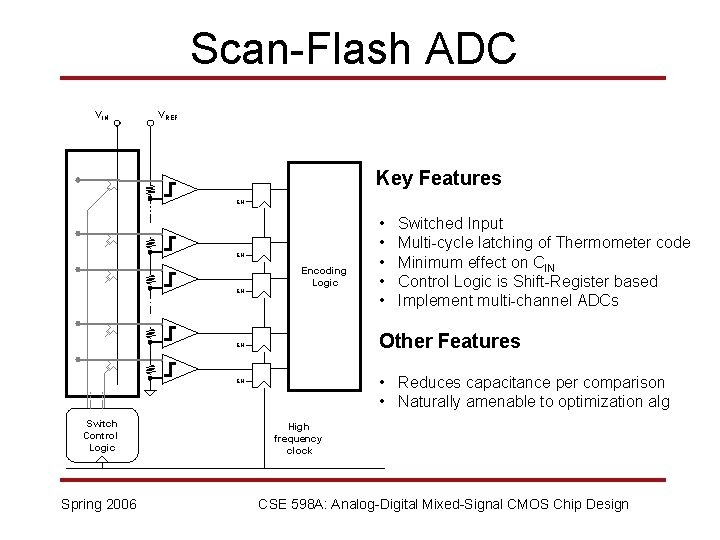

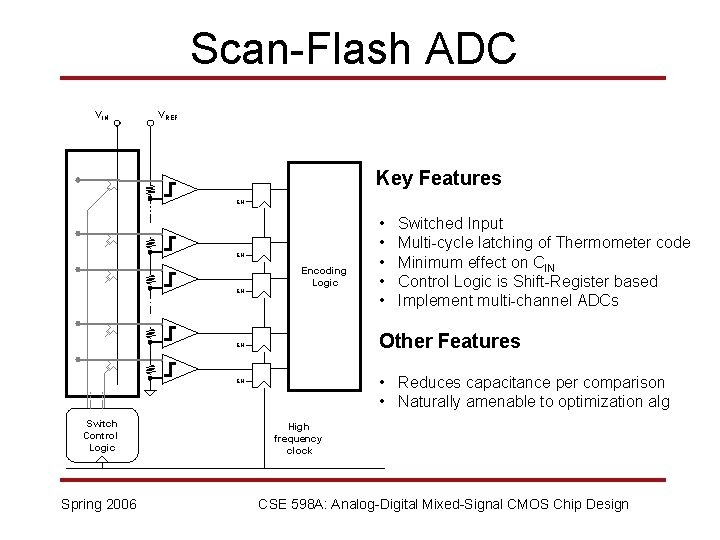

Scan-Flash ADC VIN VREF Key Features EN EN EN Encoding Logic • Reduces capacitance per comparison • Naturally amenable to optimization alg EN Spring 2006 Switched Input Multi-cycle latching of Thermometer code Minimum effect on CIN Control Logic is Shift-Register based Implement multi-channel ADCs Other Features EN Switch Control Logic • • • High frequency clock CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

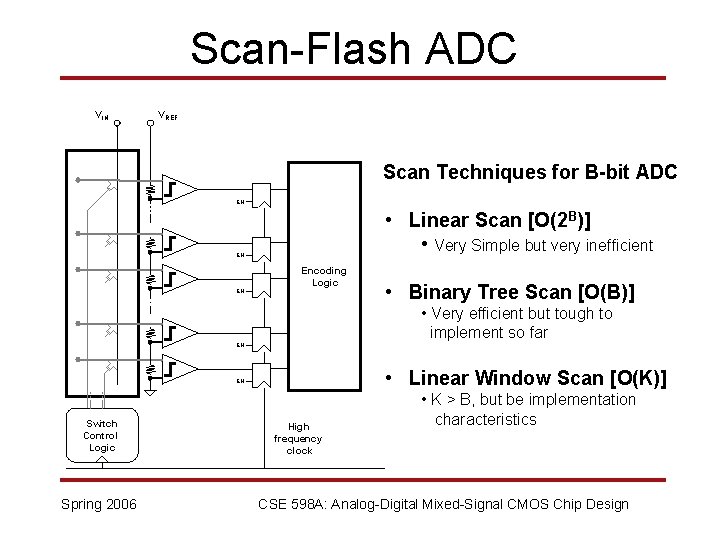

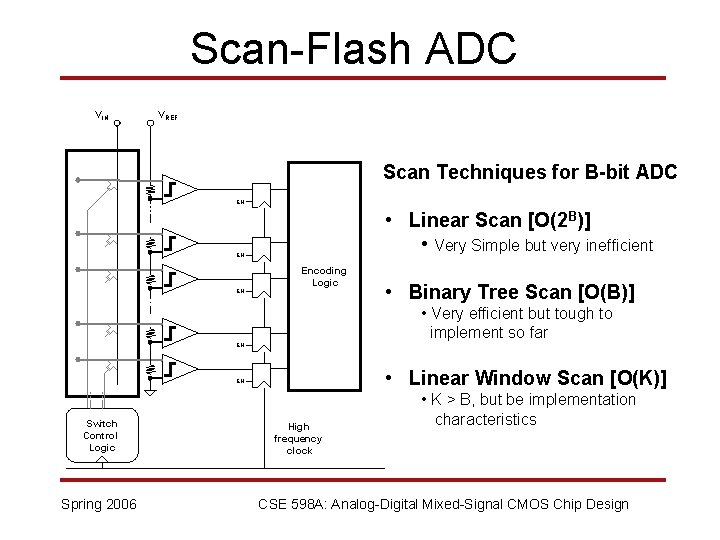

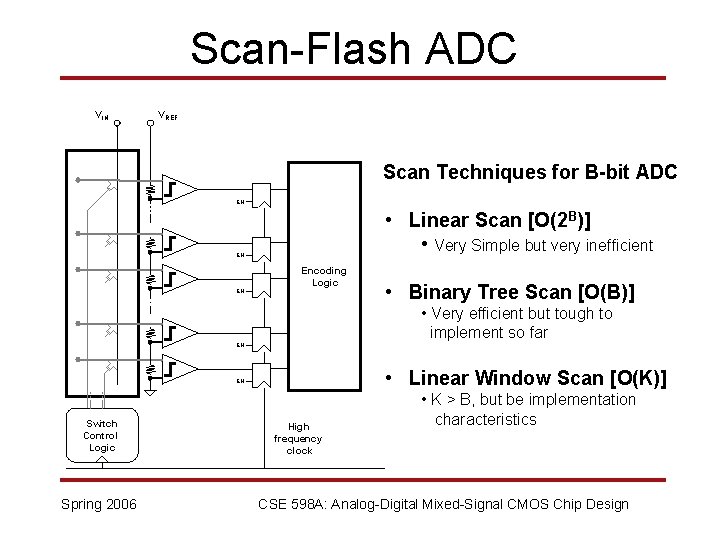

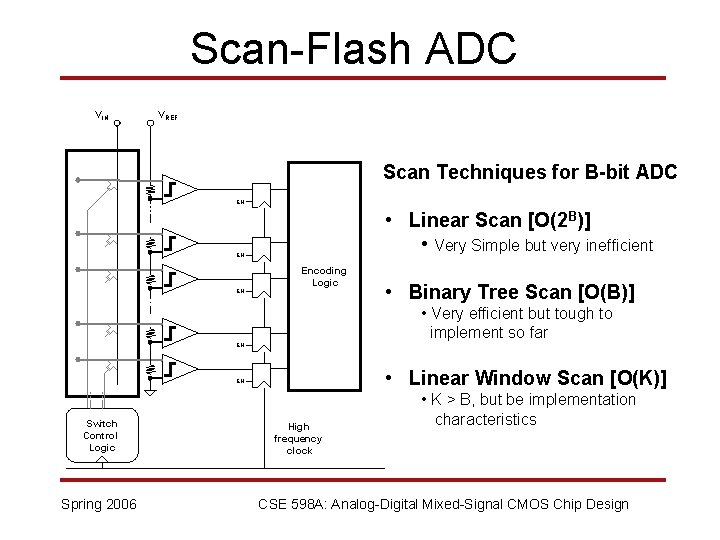

Scan-Flash ADC VIN VREF Scan Techniques for B-bit ADC EN • Linear Scan [O(2 B)] • Very Simple but very inefficient EN EN Encoding Logic • Binary Tree Scan [O(B)] • Very efficient but tough to implement so far EN • Linear Window Scan [O(K)] EN Switch Control Logic Spring 2006 High frequency clock • K > B, but be implementation characteristics CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

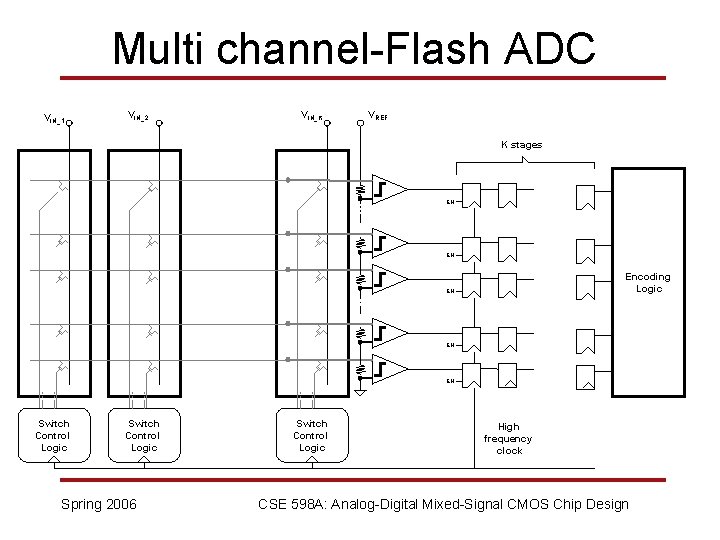

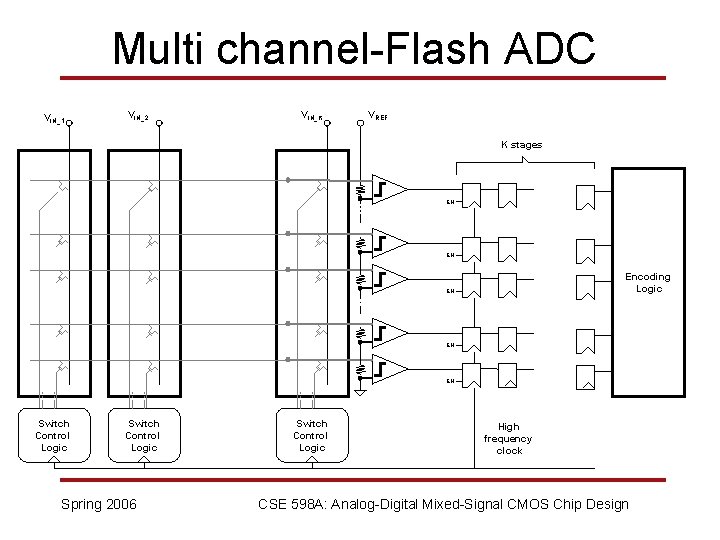

Multi channel-Flash ADC VIN_1 VIN_2 VIN_K VREF K stages EN EN Encoding Logic EN EN EN Switch Control Logic Spring 2006 Switch Control Logic High frequency clock CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

![Target Specifications 2 Channels 2 ScanFlash ADC 8 bit per channel Power Target Specifications • • 2 Channels [2 -Scan-Flash ADC] 8 bit per channel Power](https://slidetodoc.com/presentation_image_h/b11dfe76b8780b93c9e117543bbe8042/image-10.jpg)

Target Specifications • • 2 Channels [2 -Scan-Flash ADC] 8 bit per channel Power Supply: 5 V Power Consumption: 400 m. W DNL/INL: 1 LSB Area: 1 mm 2 Speed: 50 MSPS per channel (100 MSPS aggregate) Operating Frequency: 100 MHz Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Scan-Flash ADC Low Power, High-Throughput AD Converters Melvin Eze Pennsylvania State University eze@cse. psu. edu Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Schedule • • • Week 1: Specifications and Initial Simulations Week 2: Complete SPICE Implementation of Switch Week 3: Complete Verilog Implementation of Digital Control Week 4: Schematic Layout of single channel SCAN-FLASH -no ROM in Cadence Schematic Editor Week 5: Begin Module layout in Virtuoso and SPICE simulations Week 6: More Layout Week 7: Complete Layout Week 8: Full System test and Performance Analysis Week 9: Debug and Complete Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Progress • • Week 1 - Week 4 Initial simulation of 3 -bit single channel Simulation and schematic layout Initial Floor plan for layout Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

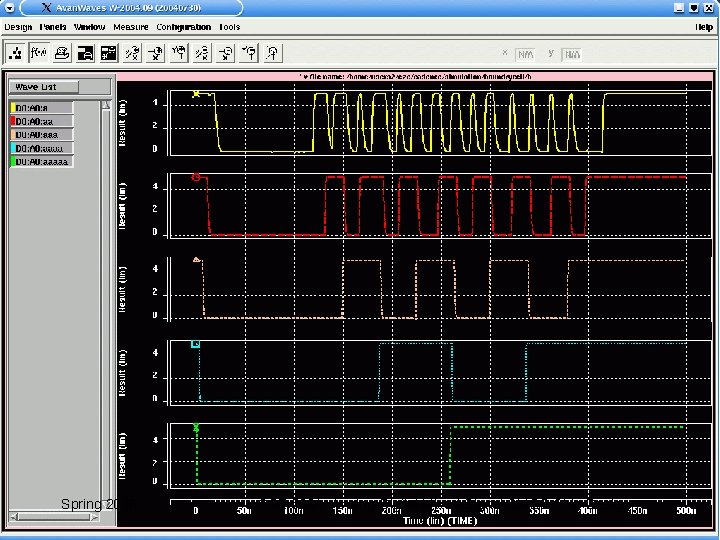

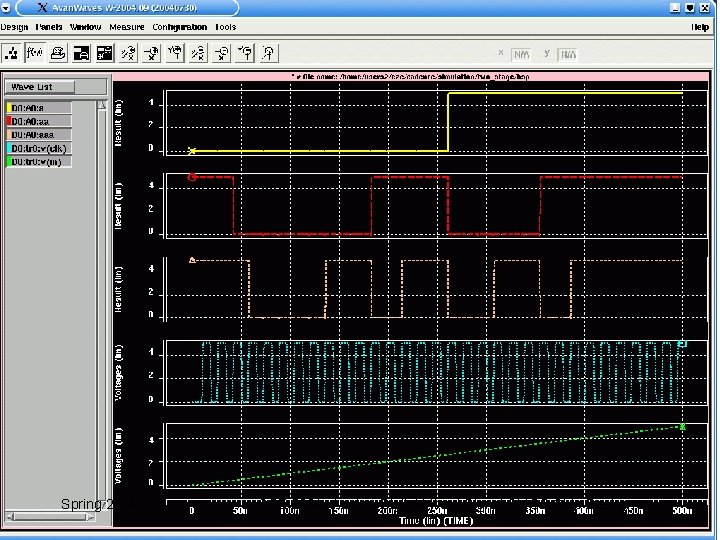

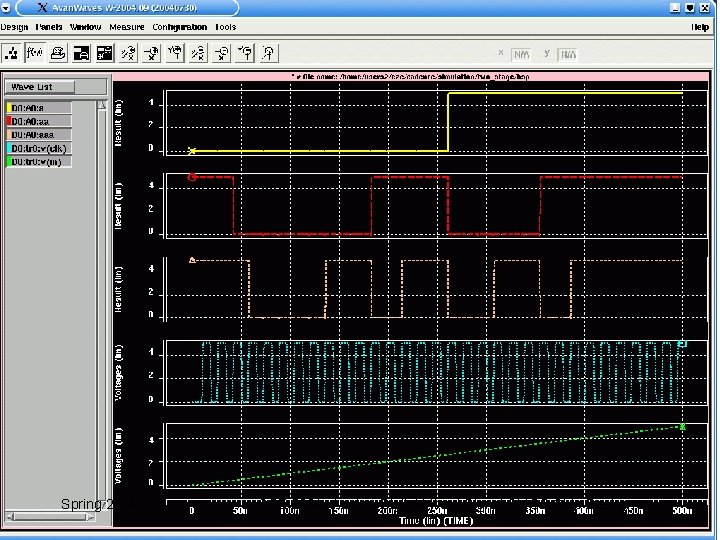

Design Verification Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

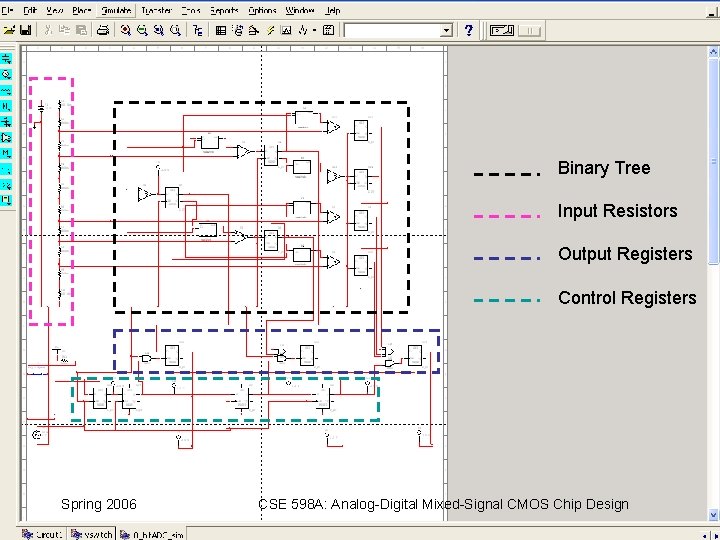

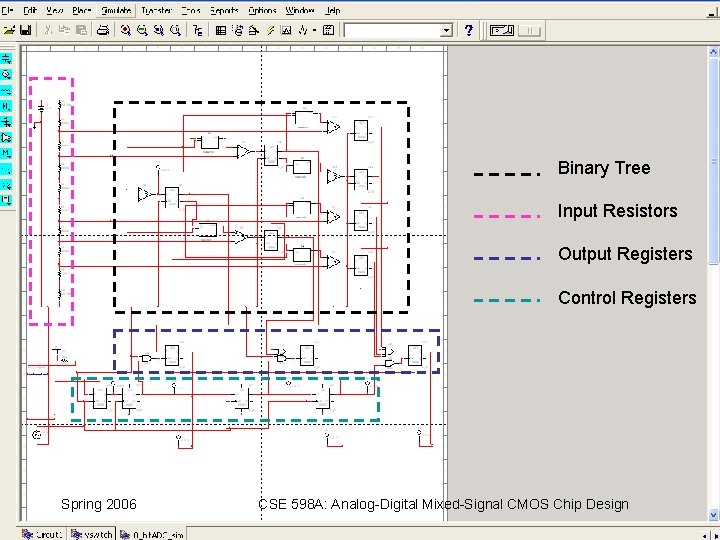

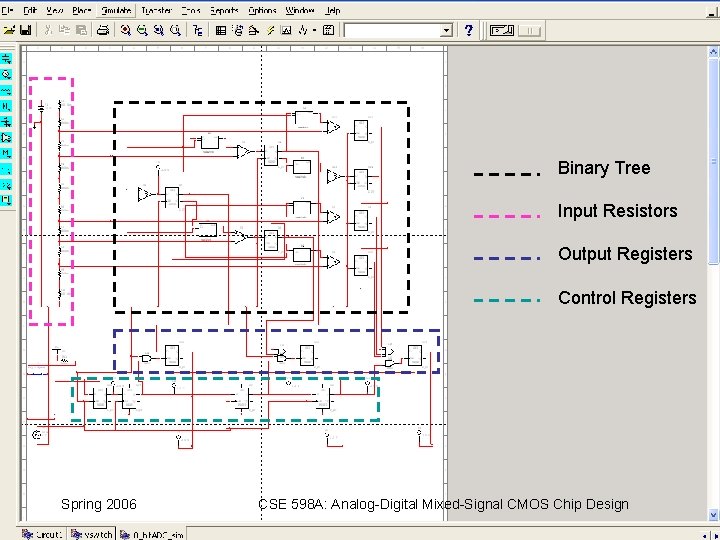

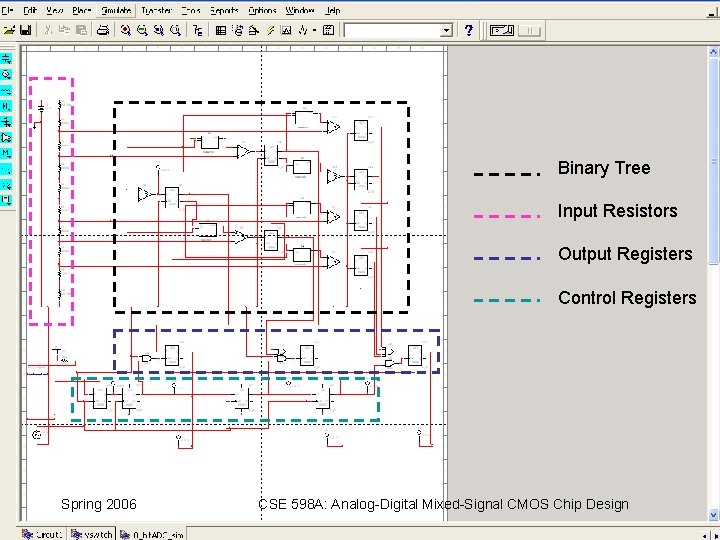

Binary Tree Input Resistors Output Registers Control Registers Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

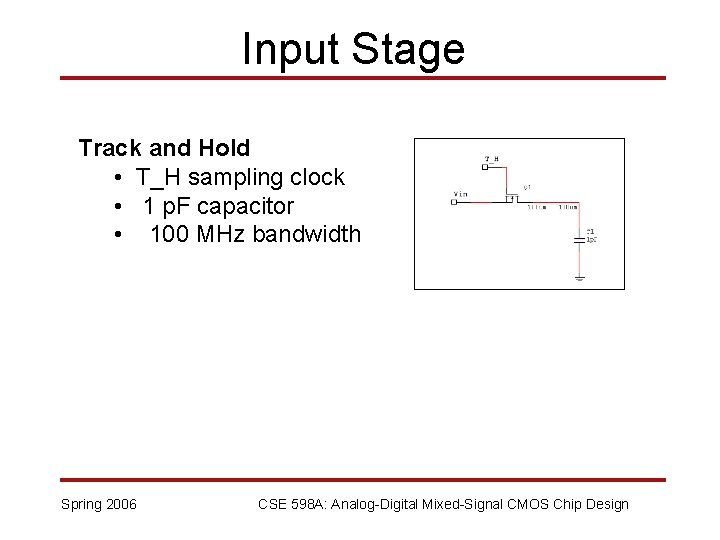

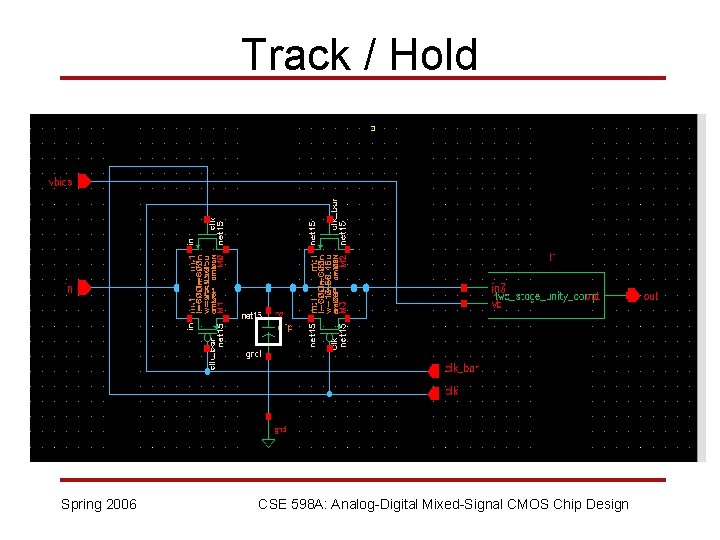

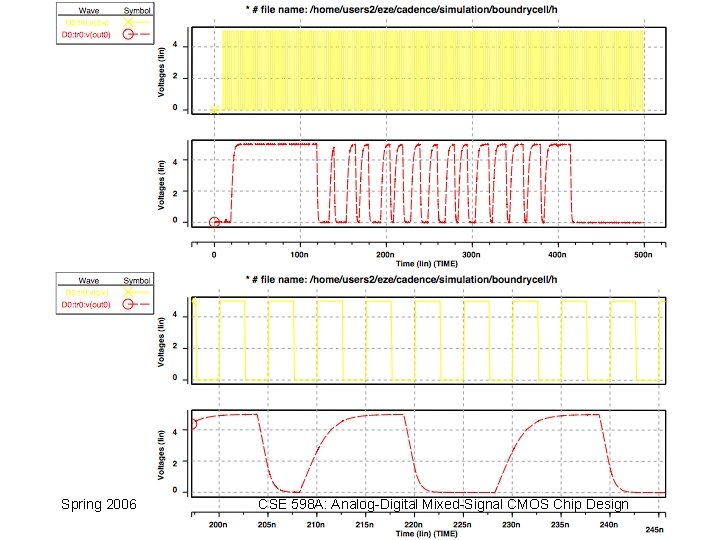

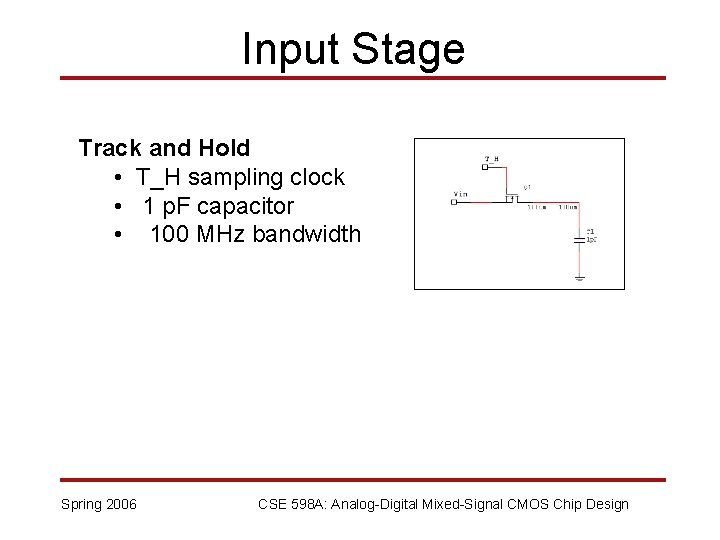

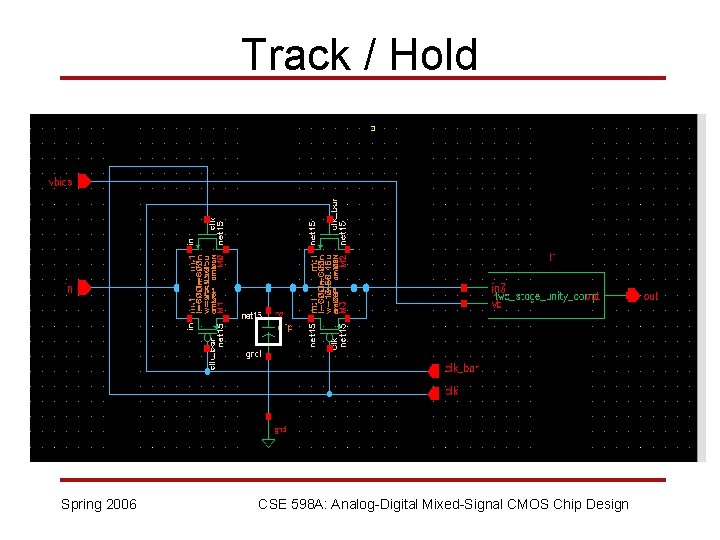

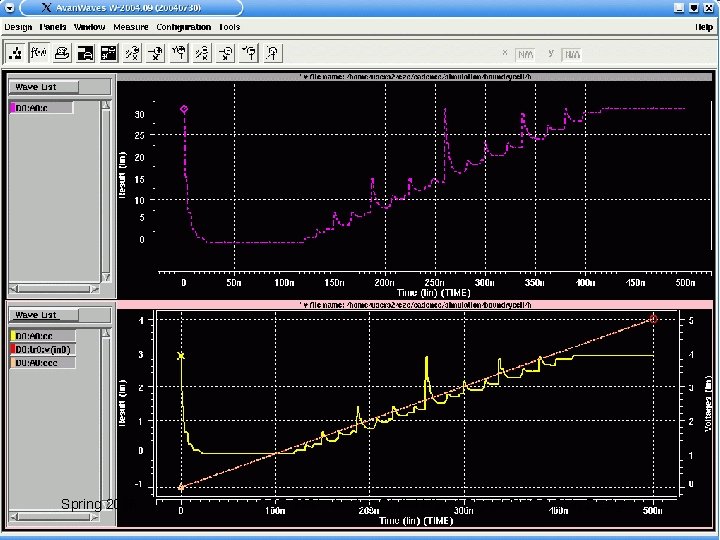

Input Stage Track and Hold • T_H sampling clock • 1 p. F capacitor • 100 MHz bandwidth Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

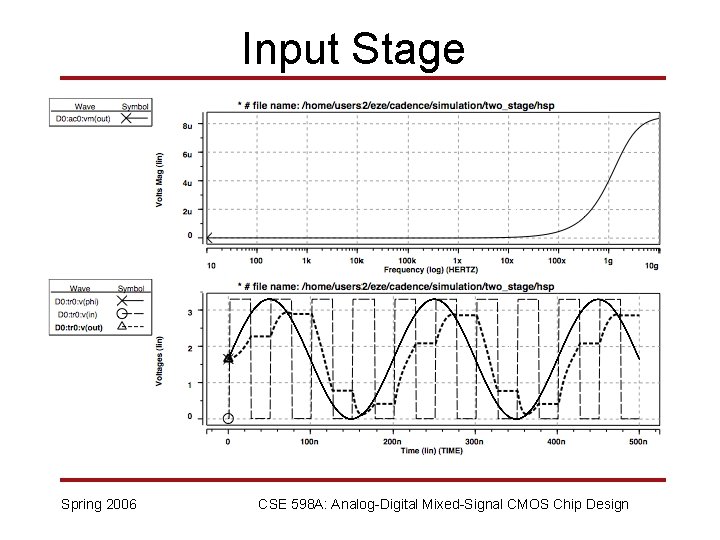

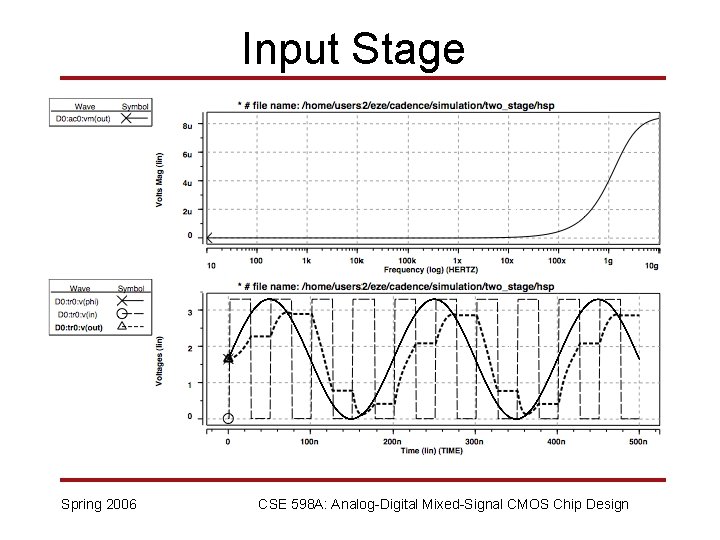

Input Stage Track and Hold Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

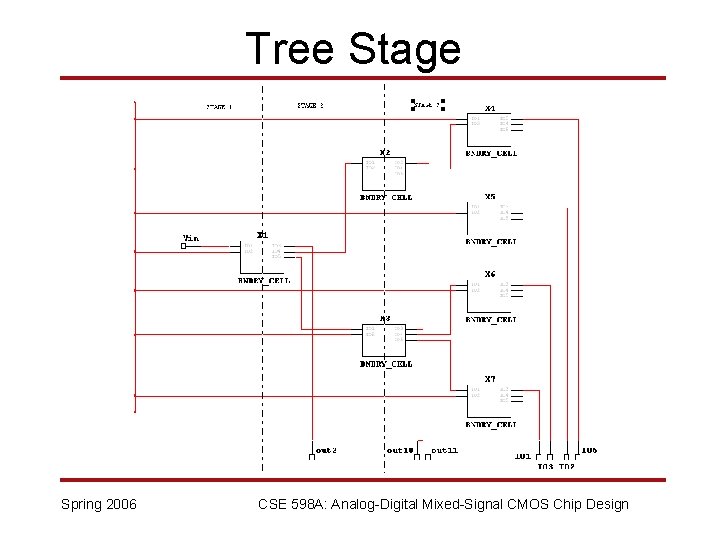

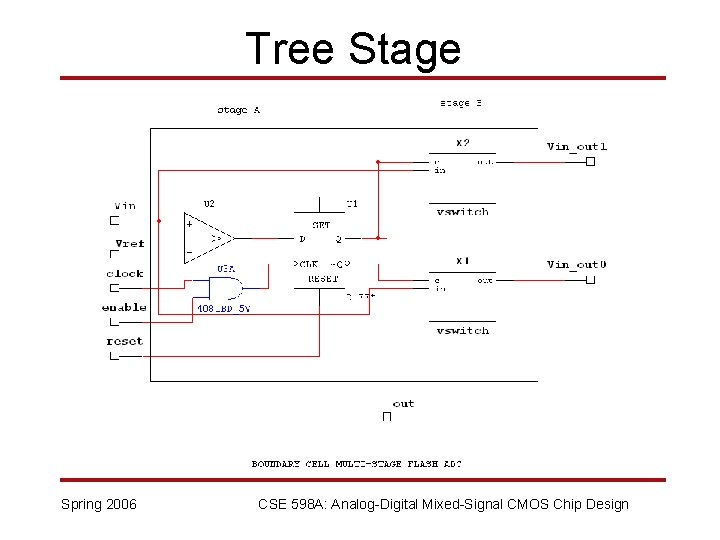

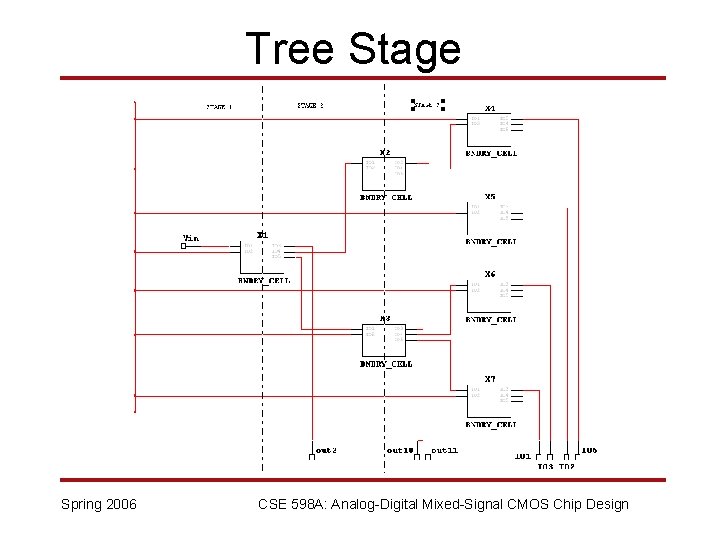

Tree Stage Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

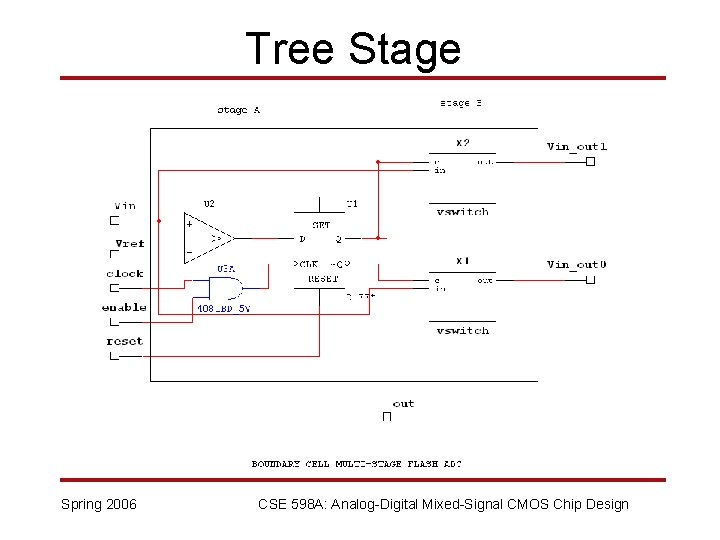

Tree Stage Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

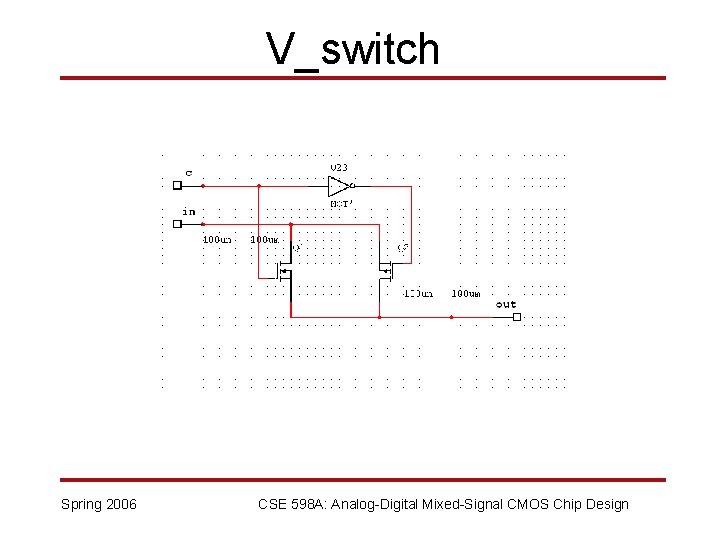

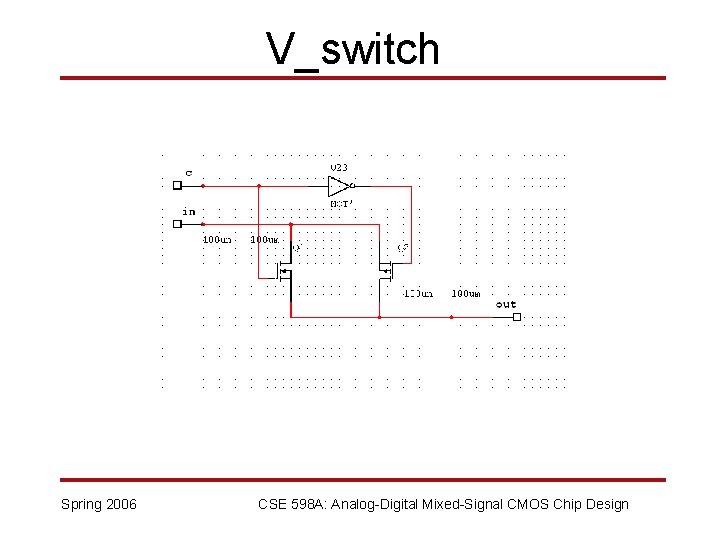

V_switch Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

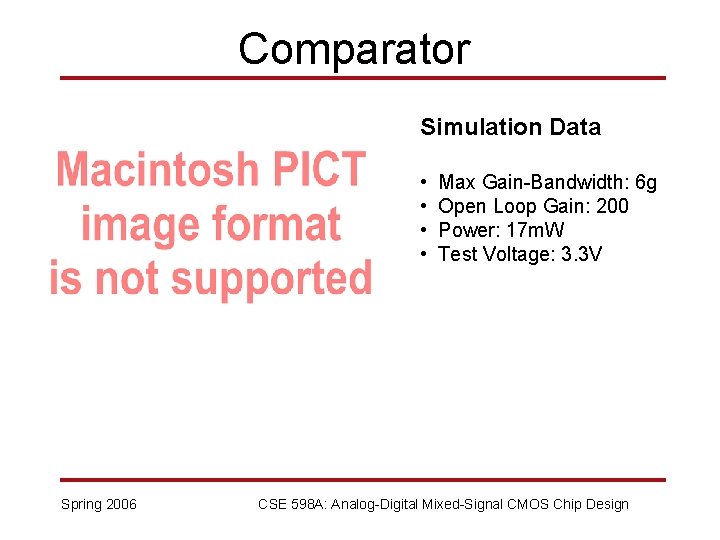

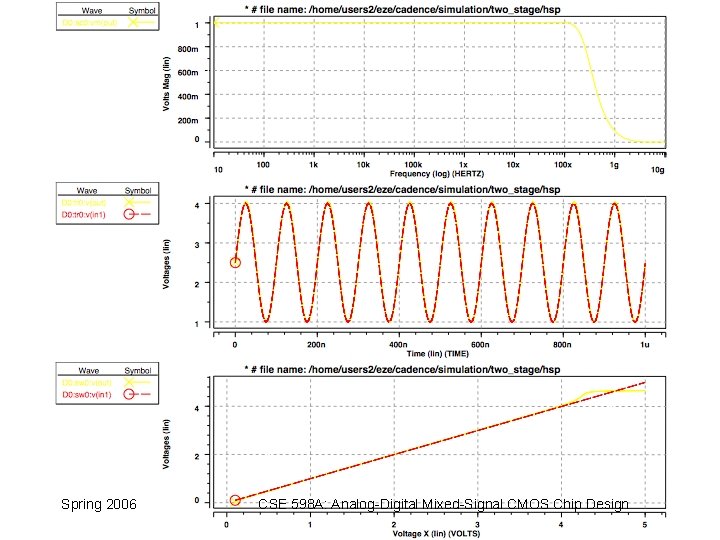

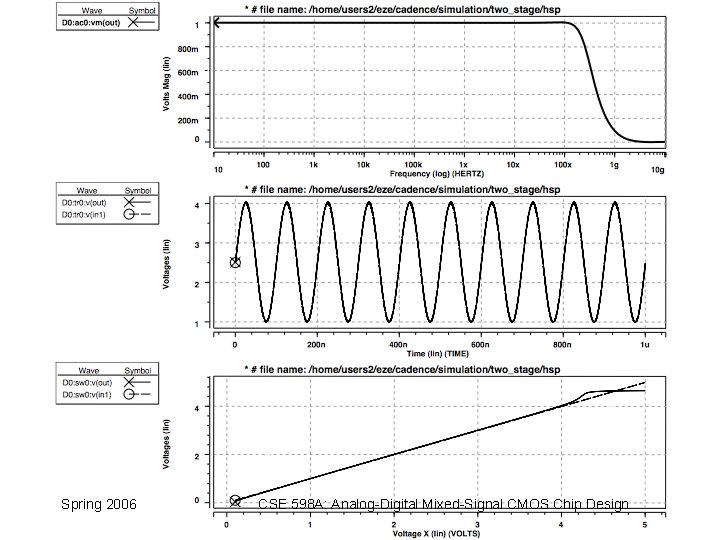

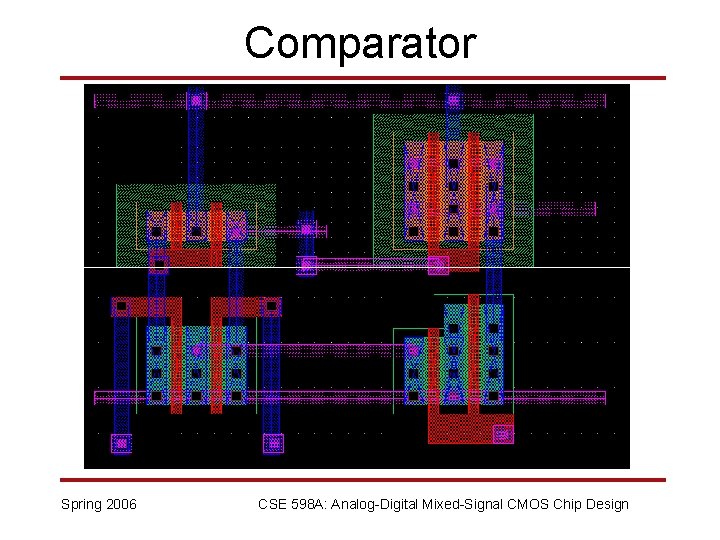

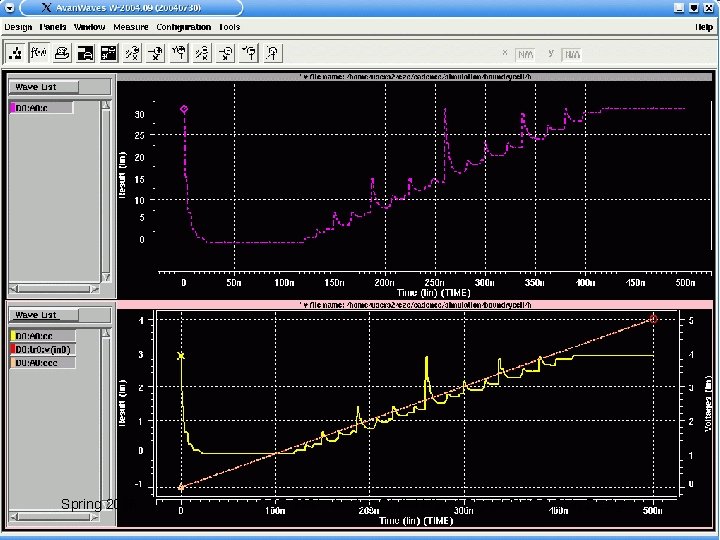

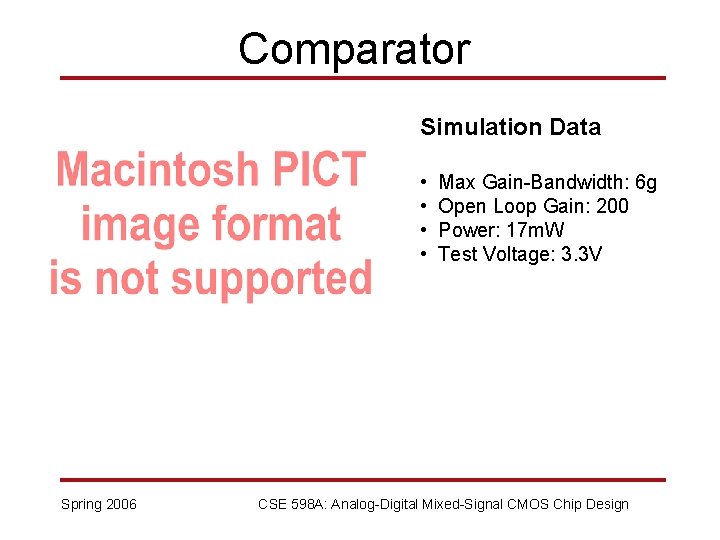

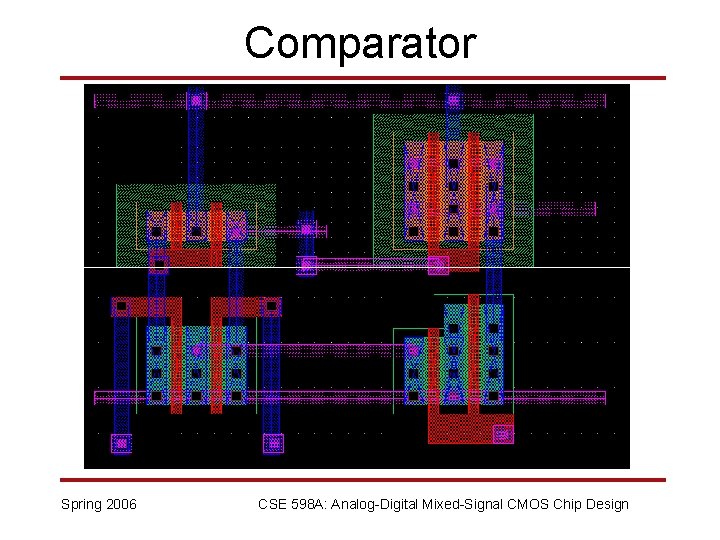

Comparator Simulation Data • • Spring 2006 Max Gain-Bandwidth: 6 g Open Loop Gain: 200 Power: 17 m. W Test Voltage: 3. 3 V CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Comparator Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

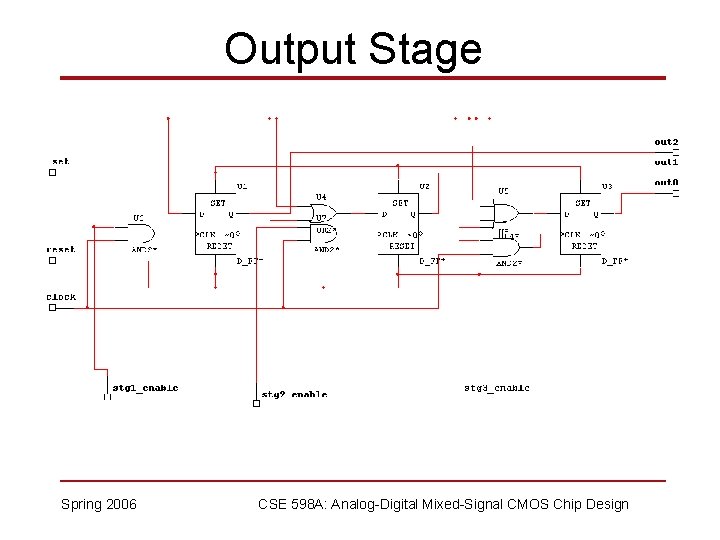

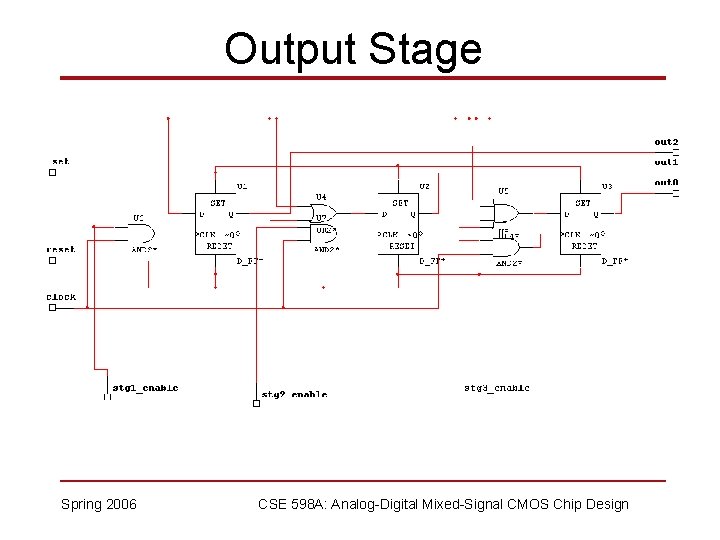

Output Stage Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

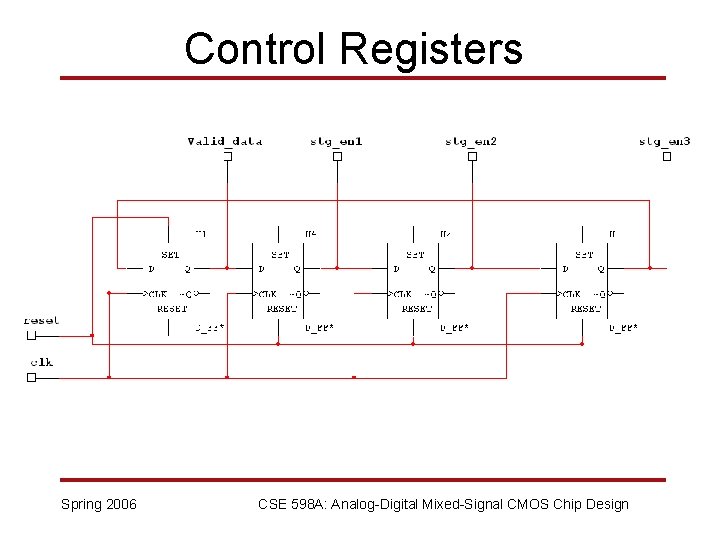

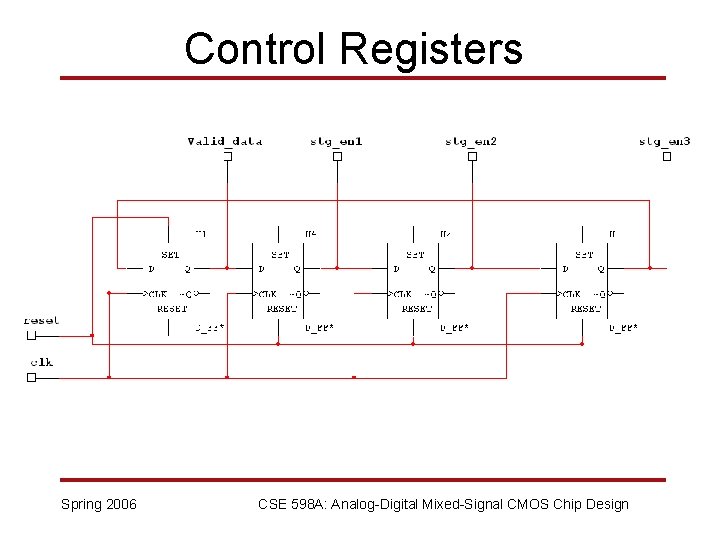

Control Registers Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

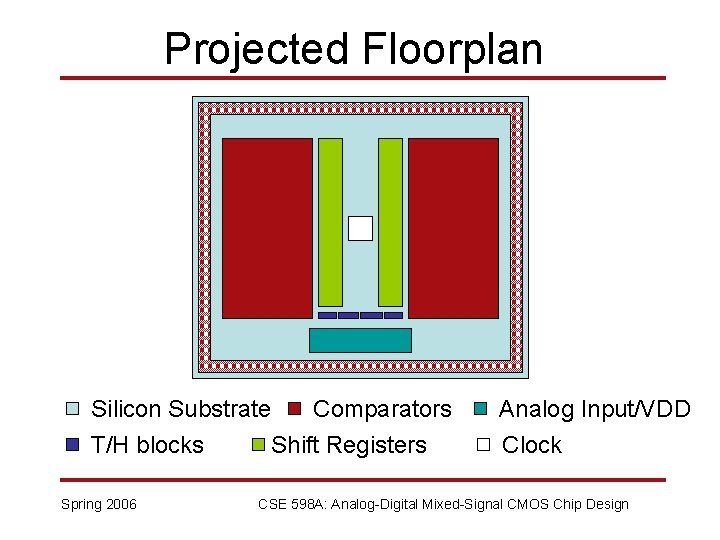

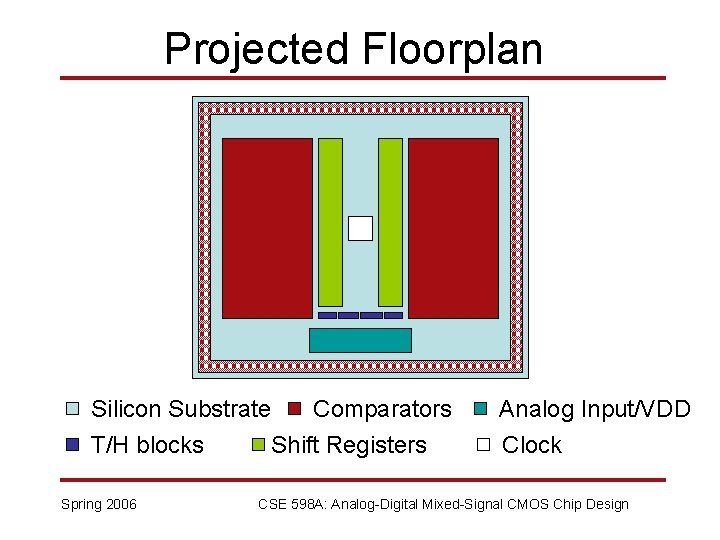

Projected Floorplan Silicon Substrate Comparators T/H blocks Shift Registers Spring 2006 Analog Input/VDD Clock CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Components Scan/Hold, Unity Gain, Comparator, Resistor Ladder, D Flip-flop, DC Biasing Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Scan-Flash ADC VIN VREF Scan Techniques for B-bit ADC EN • Linear Scan [O(2 B)] • Very Simple but very inefficient EN EN Encoding Logic • Binary Tree Scan [O(B)] • Very efficient but tough to implement so far EN • Linear Window Scan [O(K)] EN Switch Control Logic Spring 2006 High frequency clock • K > B, but be implementation characteristics CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Binary Tree Input Resistors Output Registers Control Registers Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

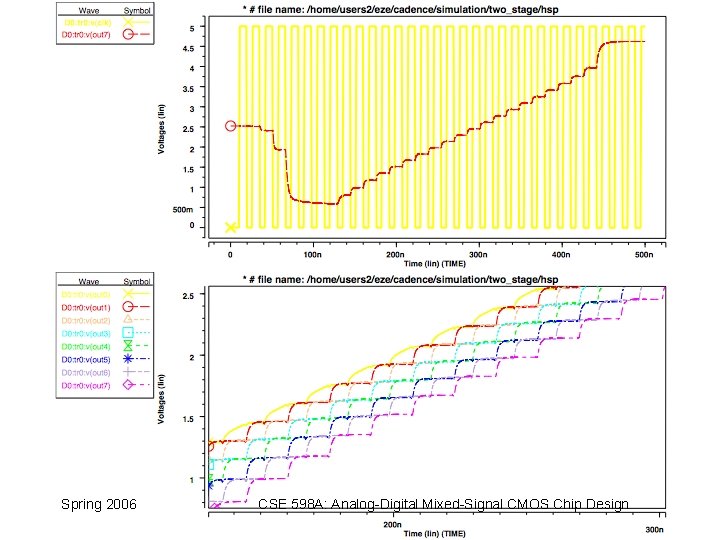

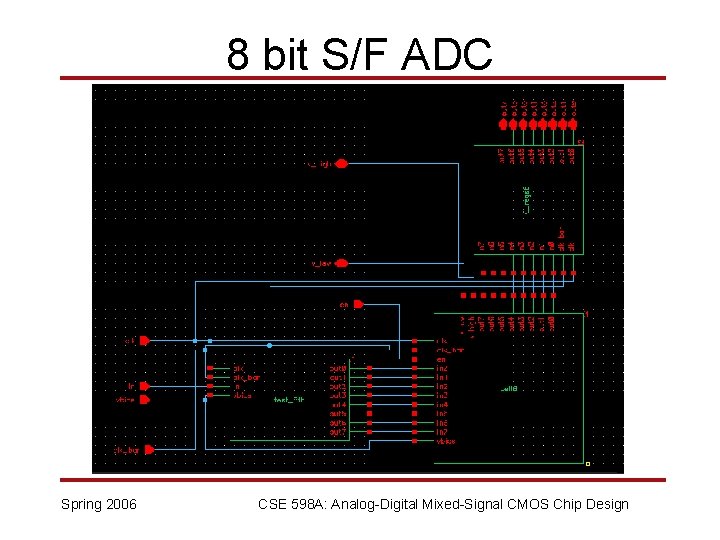

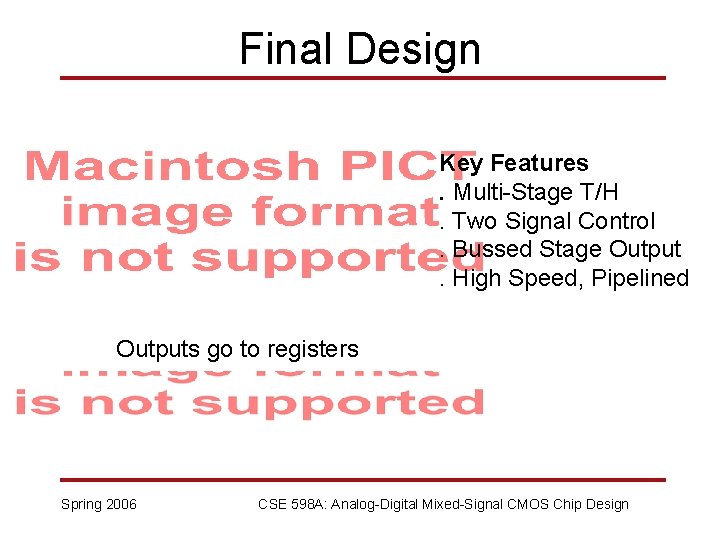

Final Design Key Features. Multi-Stage T/H. Two Signal Control. Bussed Stage Output. High Speed, Pipelined Outputs go to registers Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

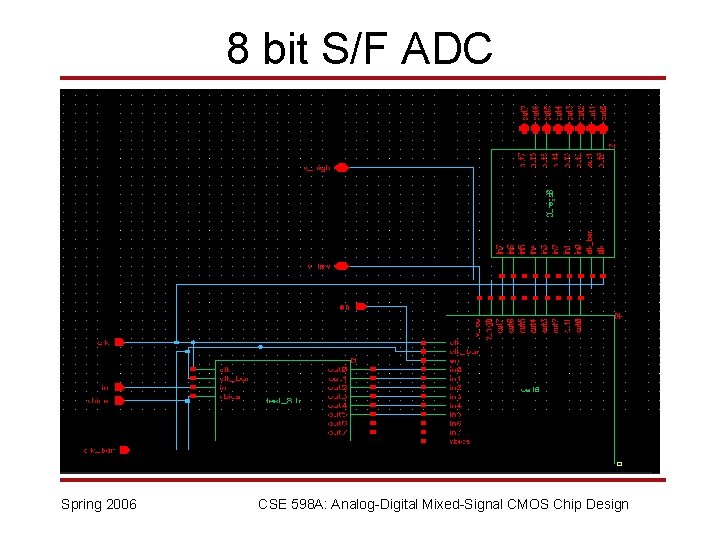

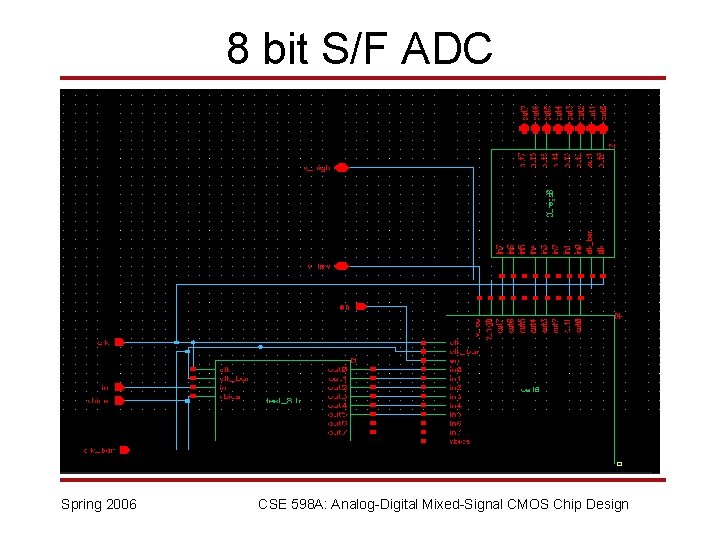

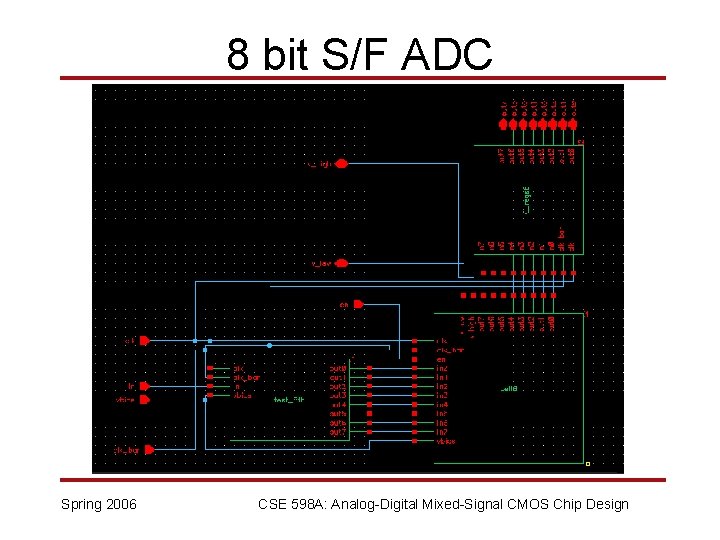

8 bit S/F ADC Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Track / Hold Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

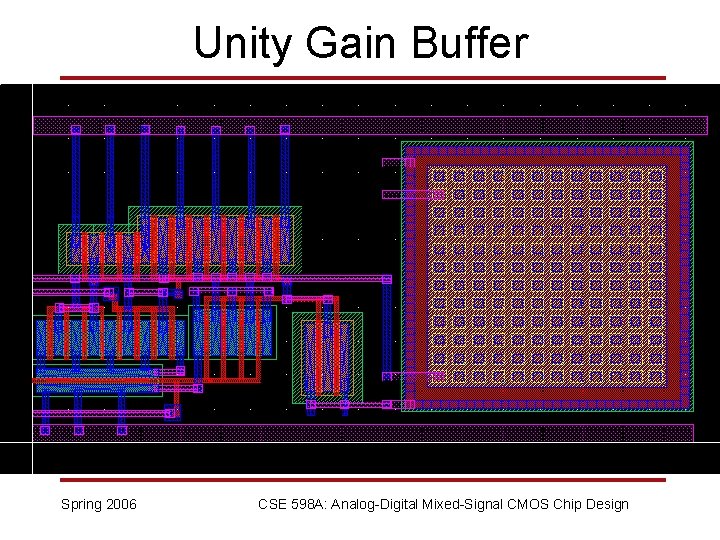

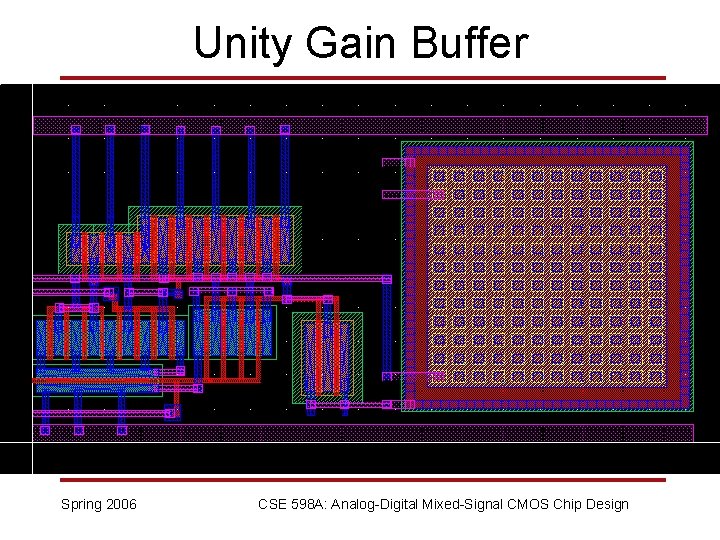

Unity Gain Buffer Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

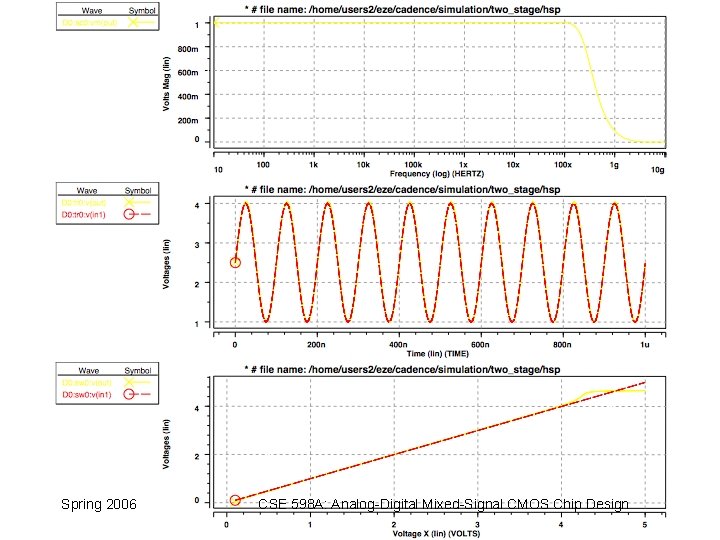

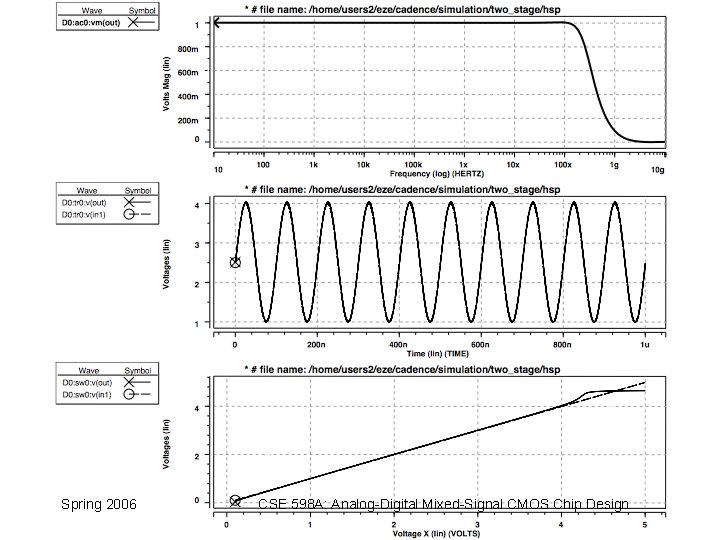

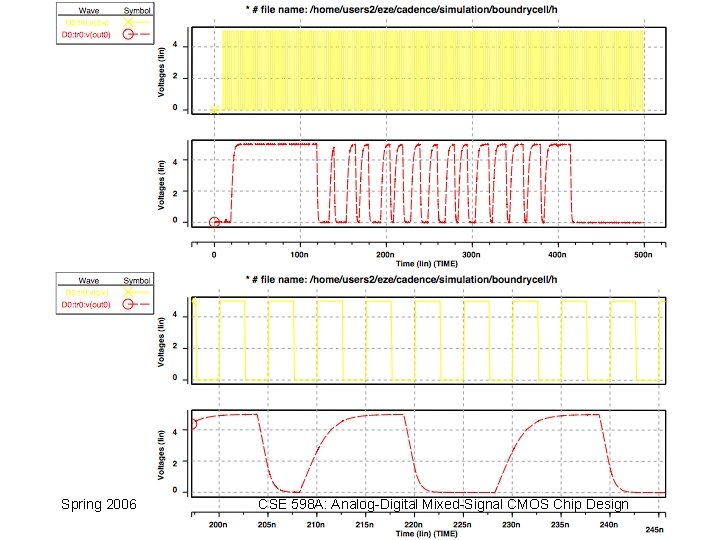

Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

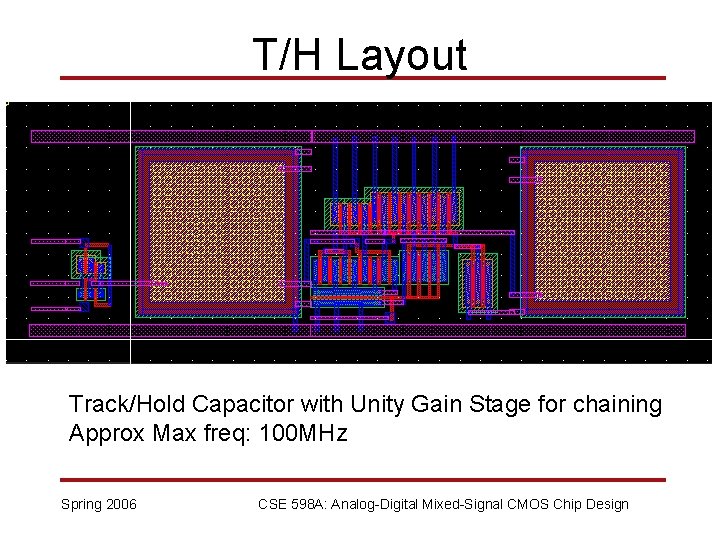

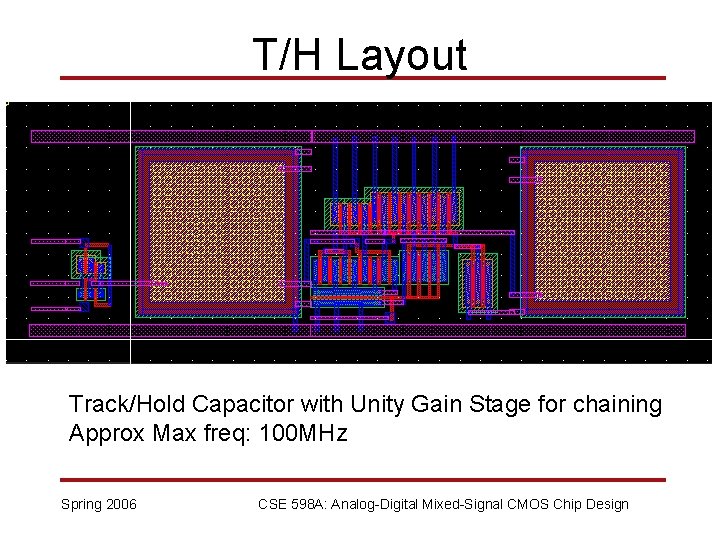

T/H Layout • �� Track/Hold Capacitor with Unity Gain Stage for chaining Approx Max freq: 100 MHz Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

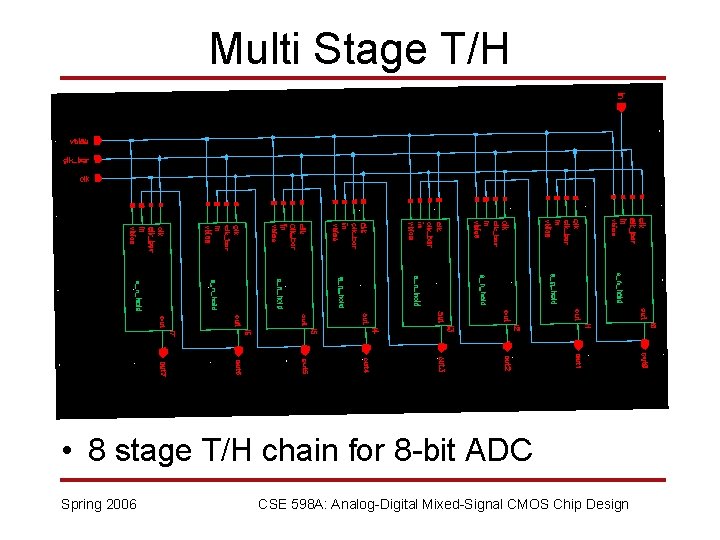

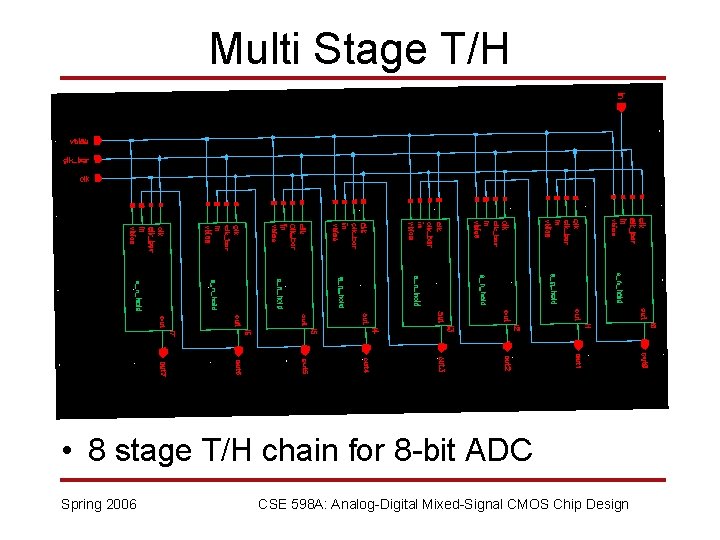

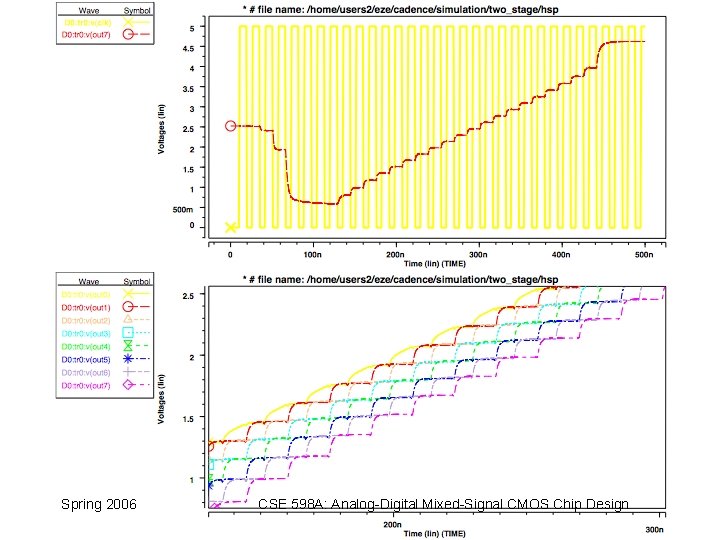

Multi Stage T/H • 8 stage T/H chain for 8 -bit ADC Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

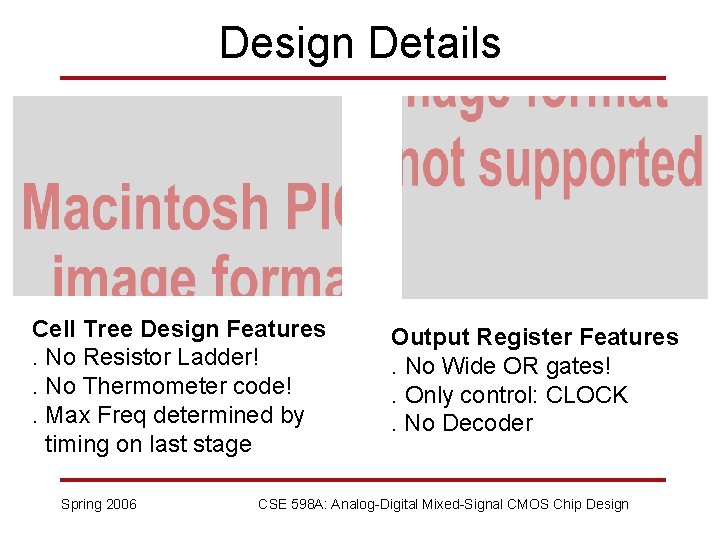

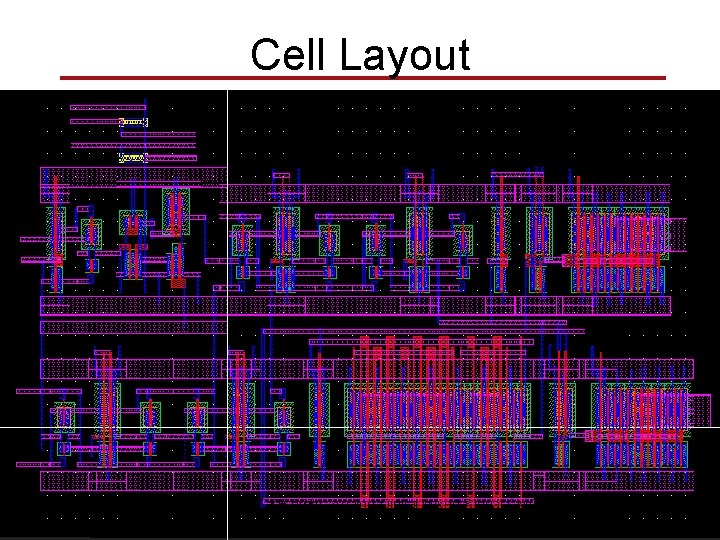

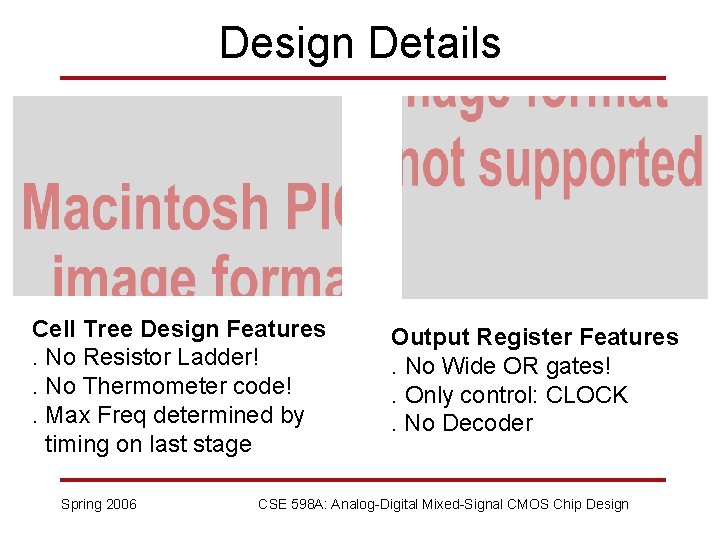

Design Details Cell Tree Design Features. No Resistor Ladder!. No Thermometer code!. Max Freq determined by timing on last stage Spring 2006 Output Register Features. No Wide OR gates!. Only control: CLOCK. No Decoder CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

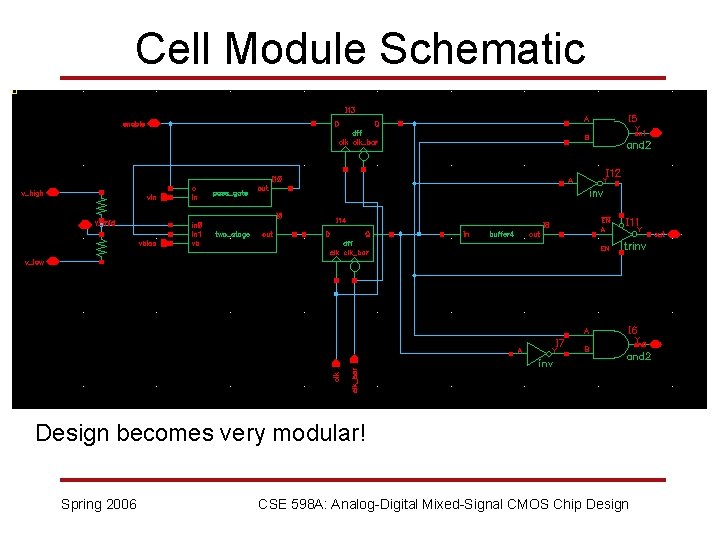

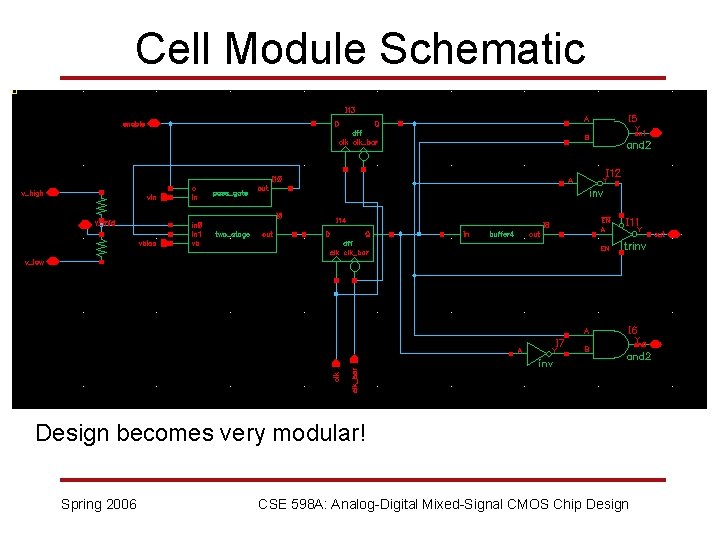

Cell Module Schematic Design becomes very modular! Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

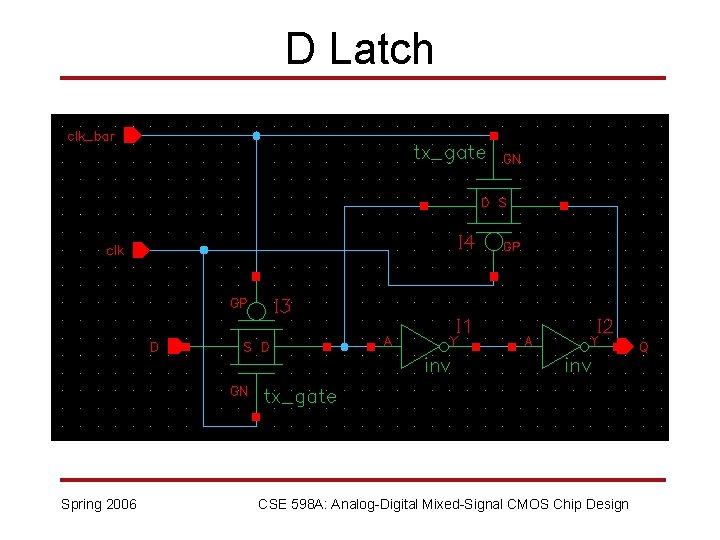

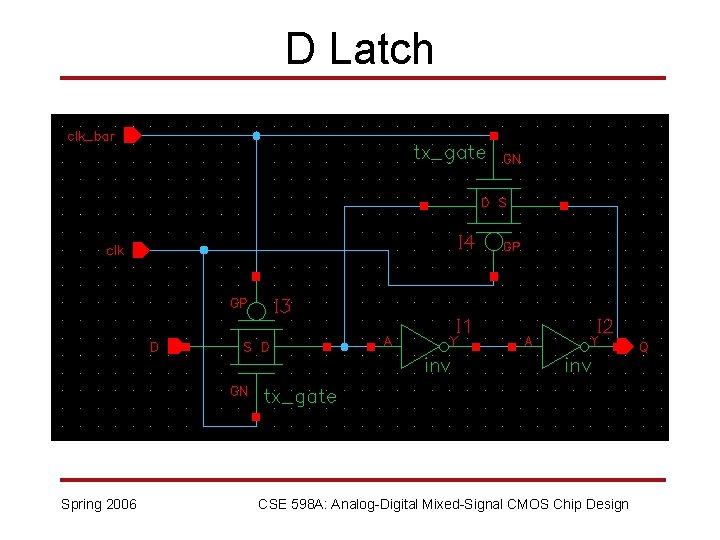

D Latch Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

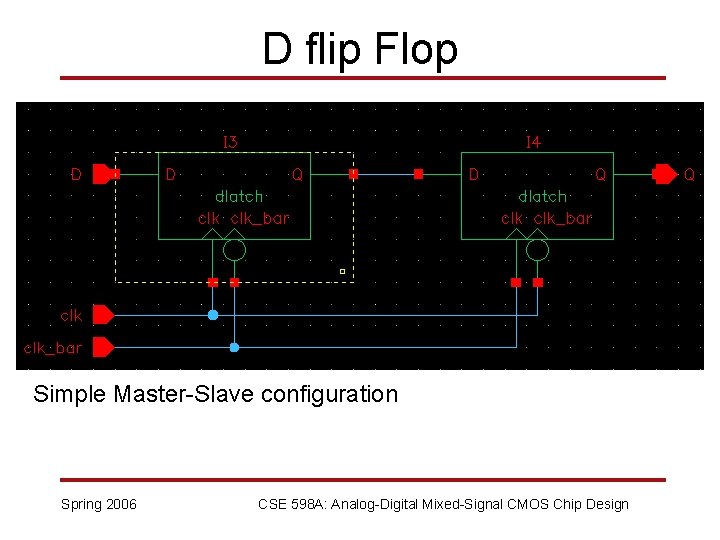

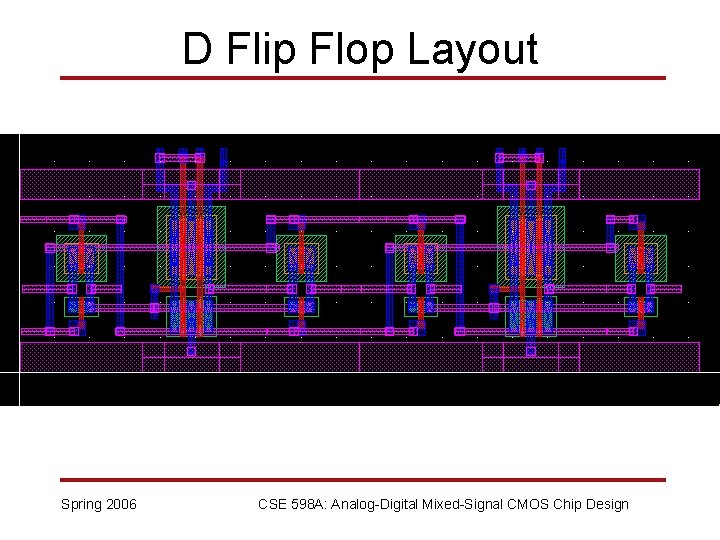

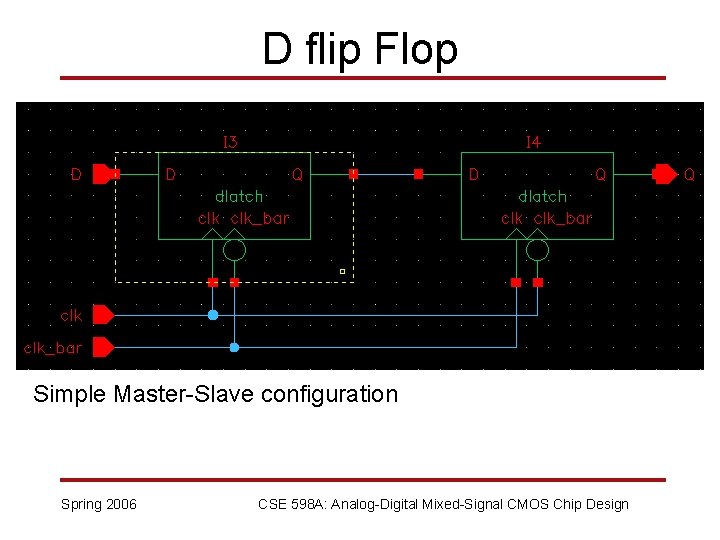

D flip Flop Simple Master-Slave configuration Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

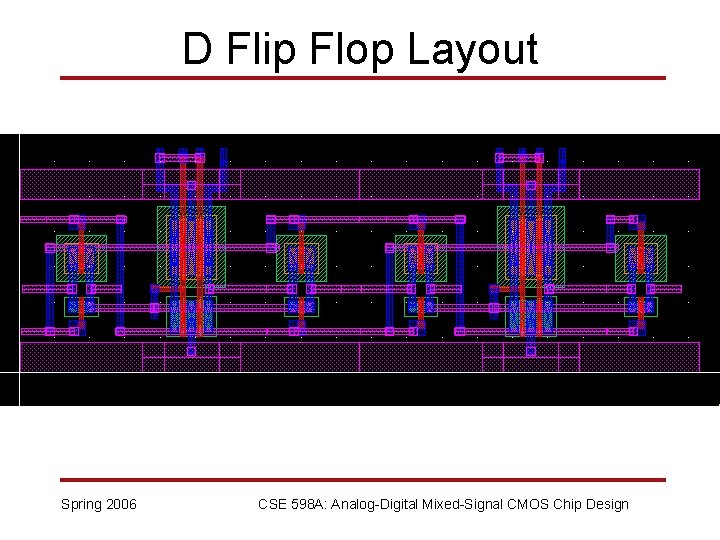

D Flip Flop Layout Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Comparator Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

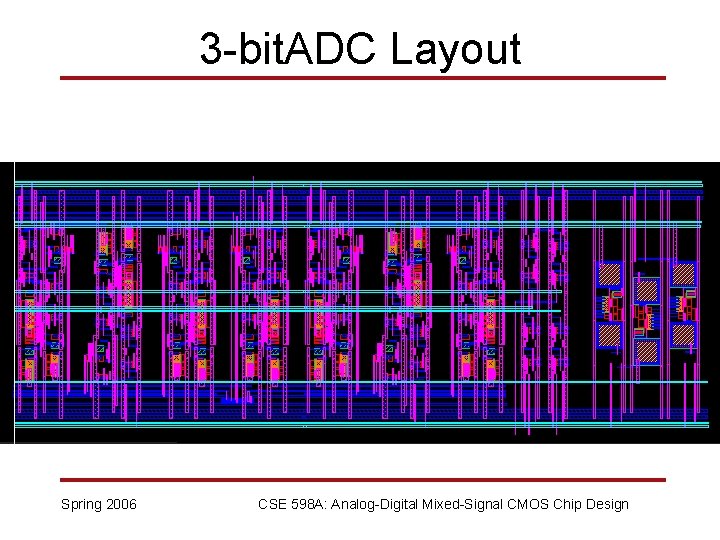

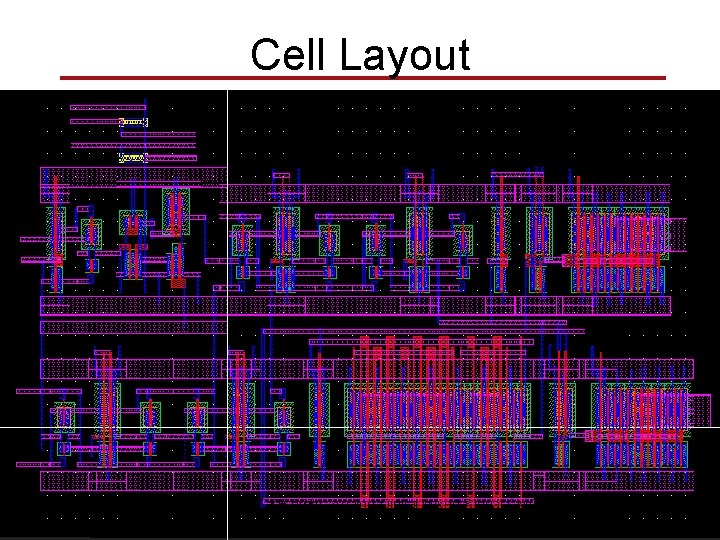

Cell Layout Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

8 bit S/F ADC Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

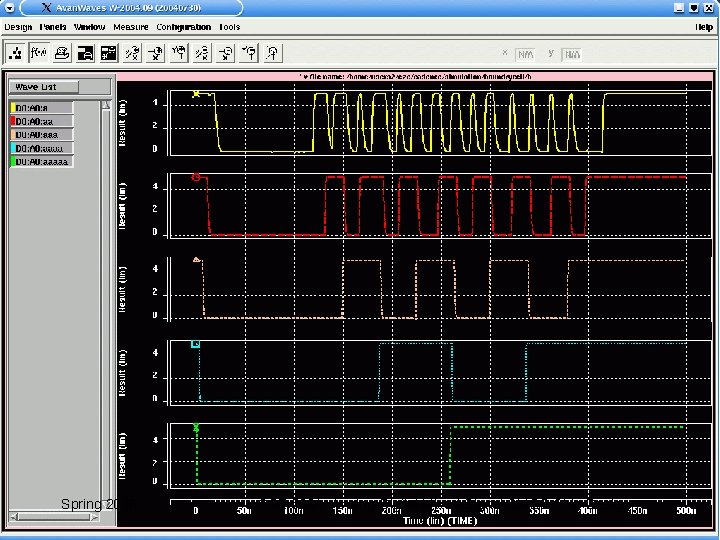

Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

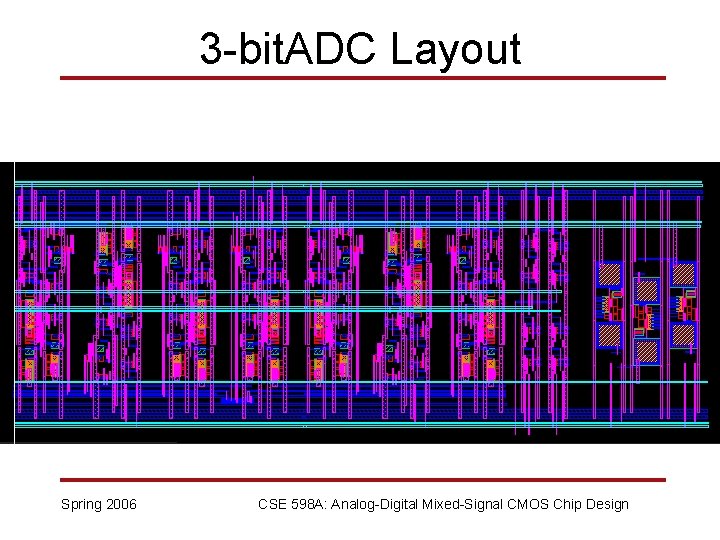

3 -bit. ADC Layout Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design

References • Rezhavi, B: CMOS Analog Circuit Design Spring 2006 CSE 598 A: Analog-Digital Mixed-Signal CMOS Chip Design