Scaling I Mohammad Sharifkhani Reading Text book II

Scaling I Mohammad Sharifkhani

Reading • Text book II (pp. 123)

Acknowledgement Some of the slides/figures in this series is brought from other people’s slides in various conferences. So I would like to appreciate them all.

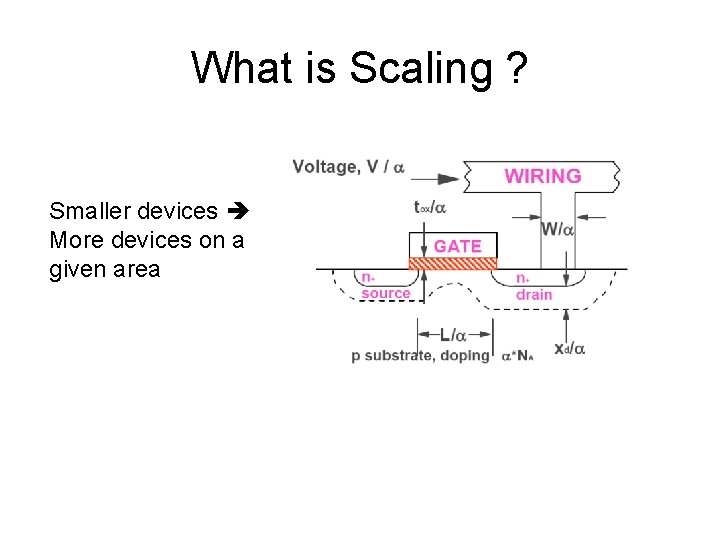

What is Scaling ? Smaller devices More devices on a given area

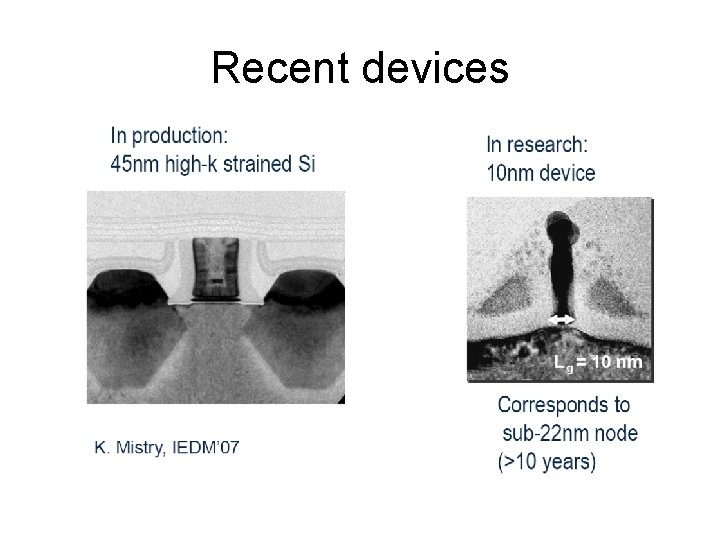

Recent devices

Are they really MOS?

Challenges • 1. Complexity • 2. Cost of integrated circuits is increasing • 3. Power • 4. Robustness issues • 5. The interconnect problem

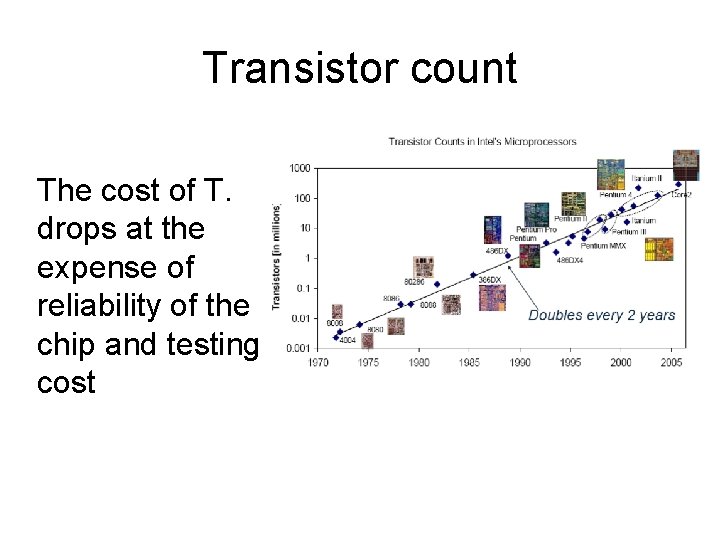

Transistor count The cost of T. drops at the expense of reliability of the chip and testing cost

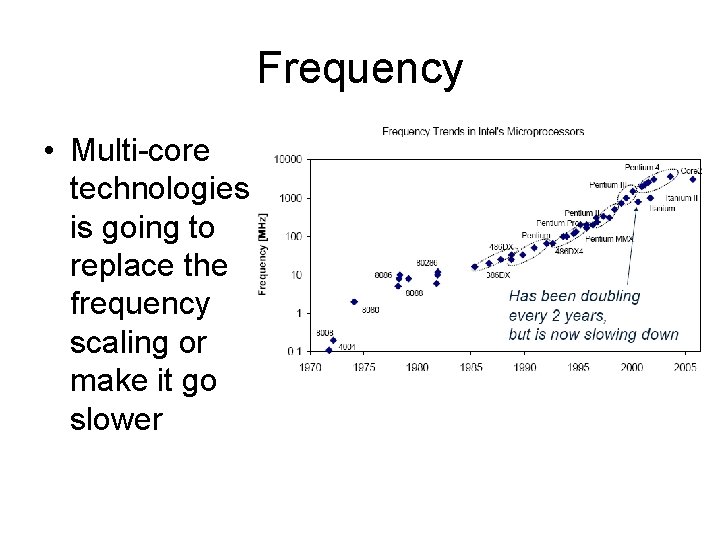

Frequency • Multi-core technologies is going to replace the frequency scaling or make it go slower

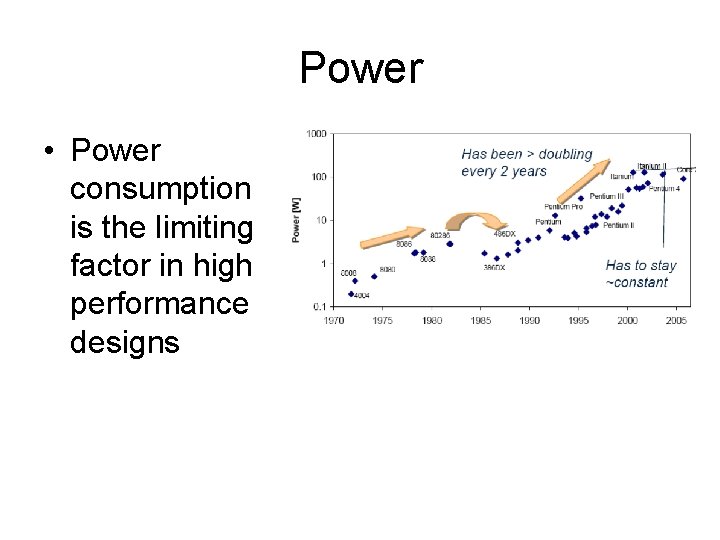

Power • Power consumption is the limiting factor in high performance designs

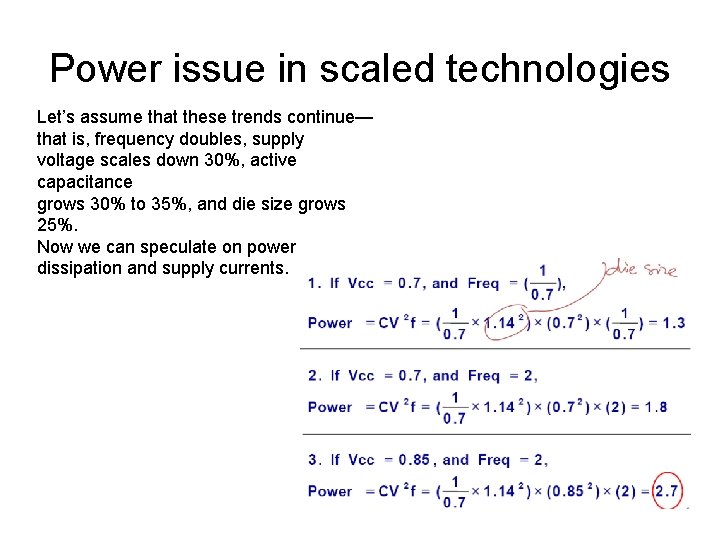

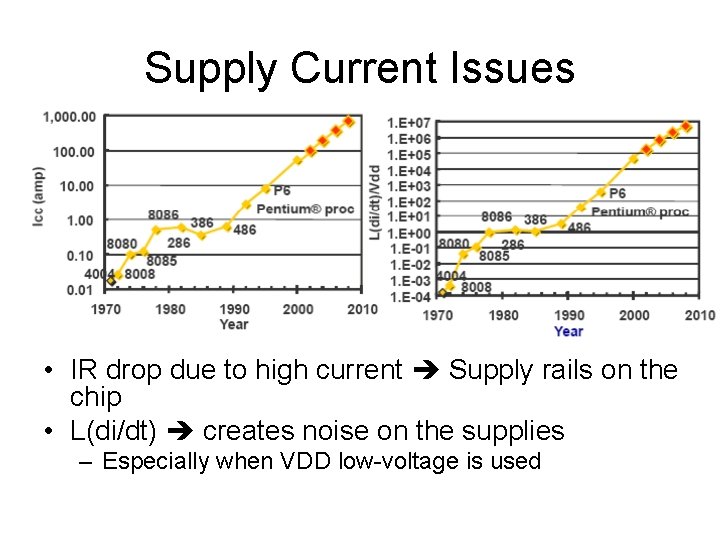

Power issue in scaled technologies Let’s assume that these trends continue— that is, frequency doubles, supply voltage scales down 30%, active capacitance grows 30% to 35%, and die size grows 25%. Now we can speculate on power dissipation and supply currents.

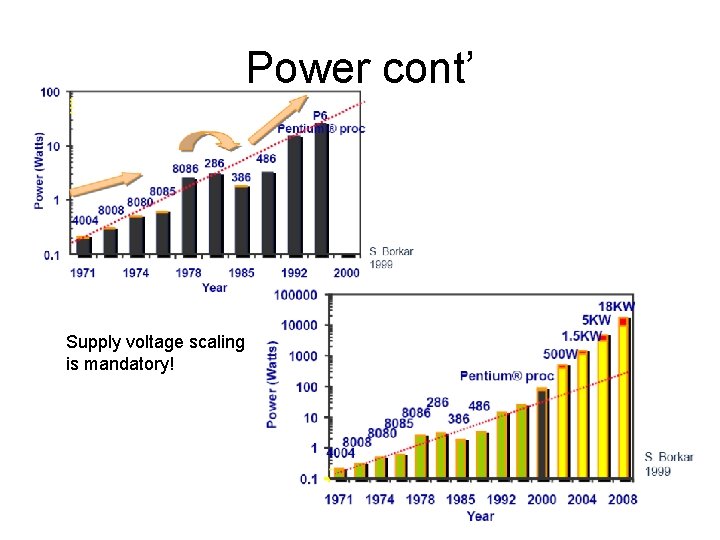

Power cont’ Supply voltage scaling is mandatory!

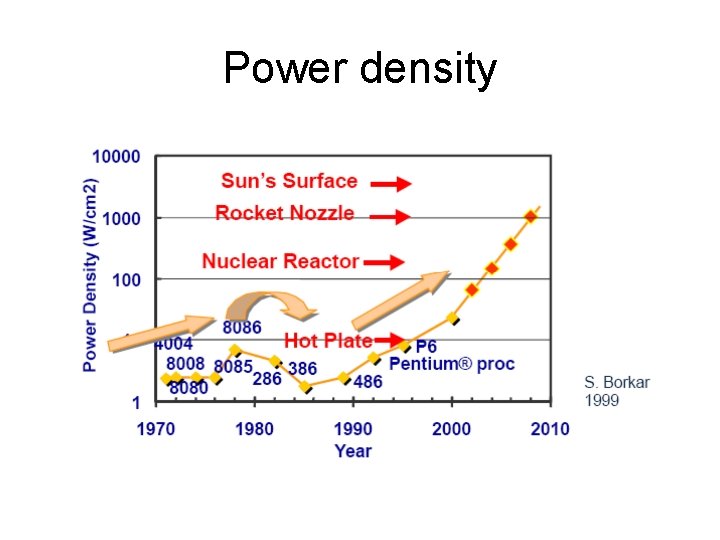

Power density

Supply Current Issues • IR drop due to high current Supply rails on the chip • L(di/dt) creates noise on the supplies – Especially when VDD low-voltage is used

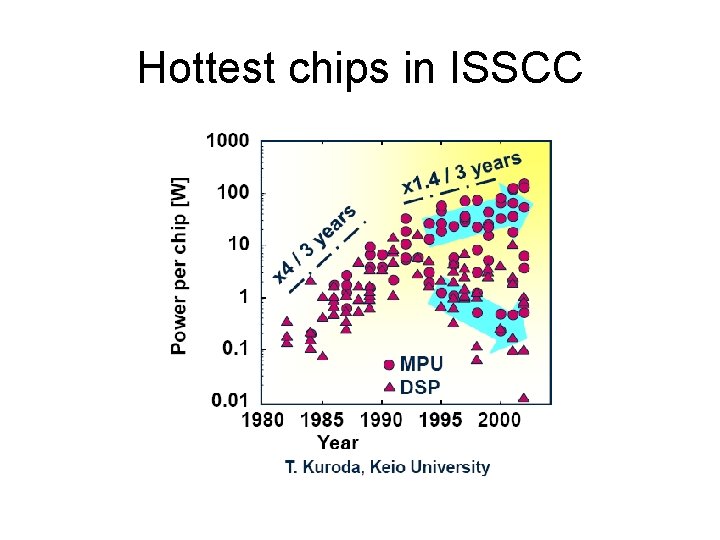

Hottest chips in ISSCC

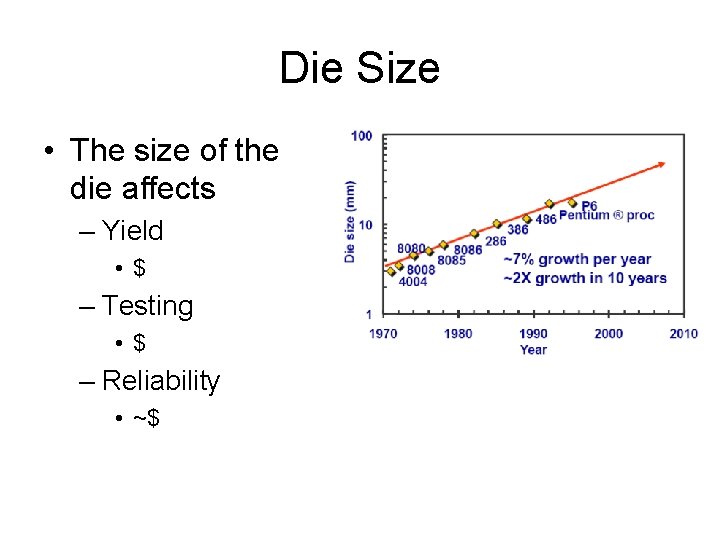

Die Size • The size of the die affects – Yield • $ – Testing • $ – Reliability • ~$

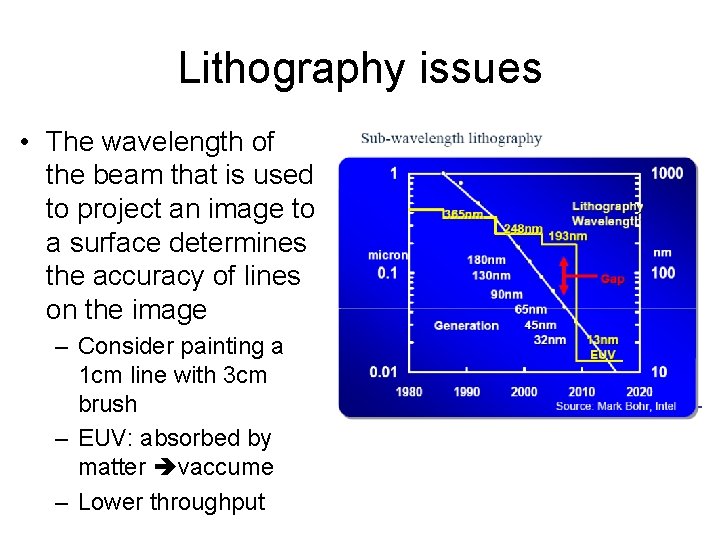

Lithography issues • The wavelength of the beam that is used to project an image to a surface determines the accuracy of lines on the image – Consider painting a 1 cm line with 3 cm brush – EUV: absorbed by matter vaccume – Lower throughput

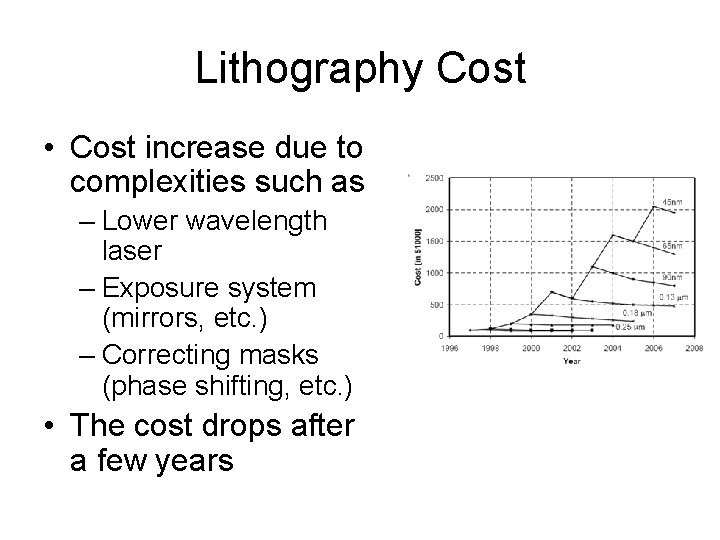

Lithography Cost • Cost increase due to complexities such as – Lower wavelength laser – Exposure system (mirrors, etc. ) – Correcting masks (phase shifting, etc. ) • The cost drops after a few years

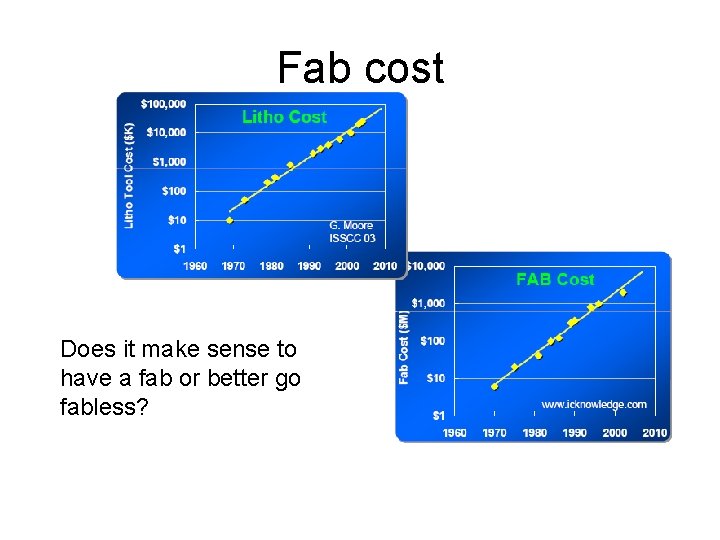

Fab cost Does it make sense to have a fab or better go fabless?

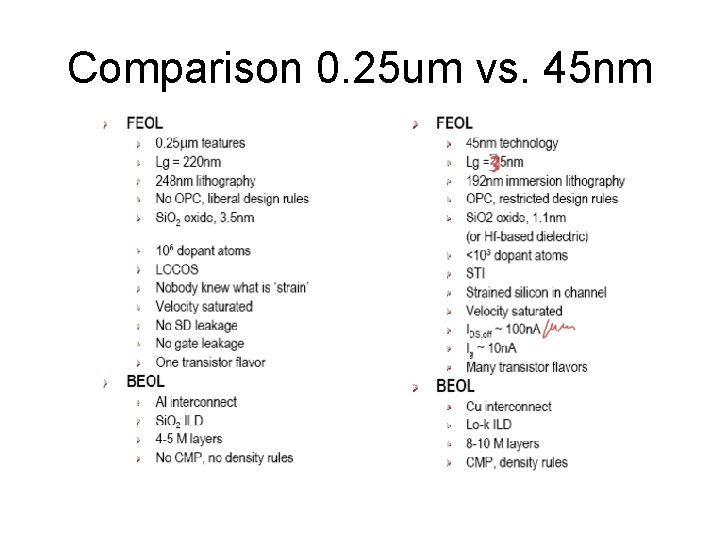

Comparison 0. 25 um vs. 45 nm

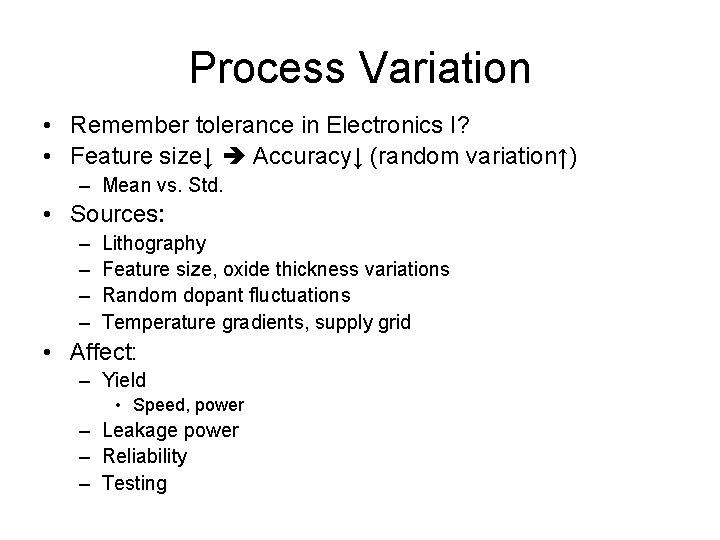

Process Variation • Remember tolerance in Electronics I? • Feature size↓ Accuracy↓ (random variation↑) – Mean vs. Std. • Sources: – – Lithography Feature size, oxide thickness variations Random dopant fluctuations Temperature gradients, supply grid • Affect: – Yield • Speed, power – Leakage power – Reliability – Testing

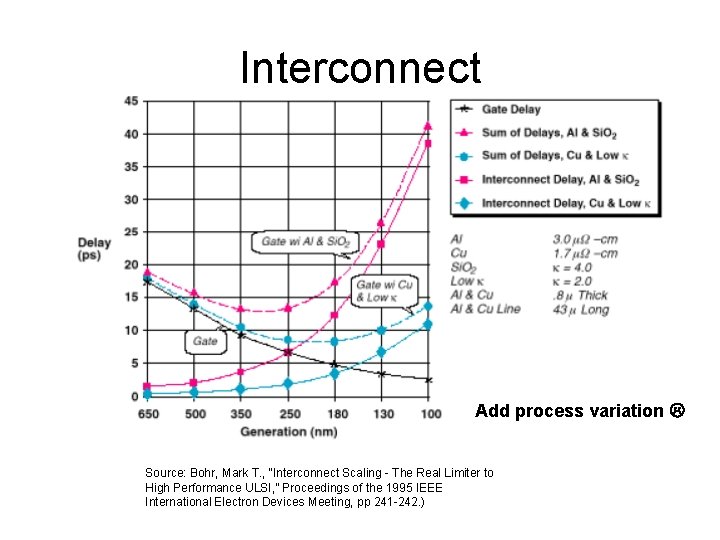

Interconnect Add process variation Source: Bohr, Mark T. , “Interconnect Scaling - The Real Limiter to High Performance ULSI, ” Proceedings of the 1995 IEEE International Electron Devices Meeting, pp 241 -242. )

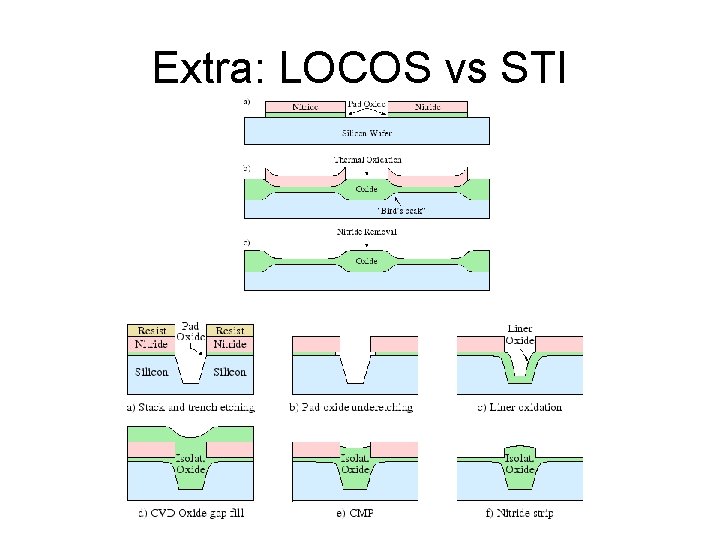

Extra: LOCOS vs STI

- Slides: 23