SCA Communication Understanding Slave SCA E LINK 80

- Slides: 6

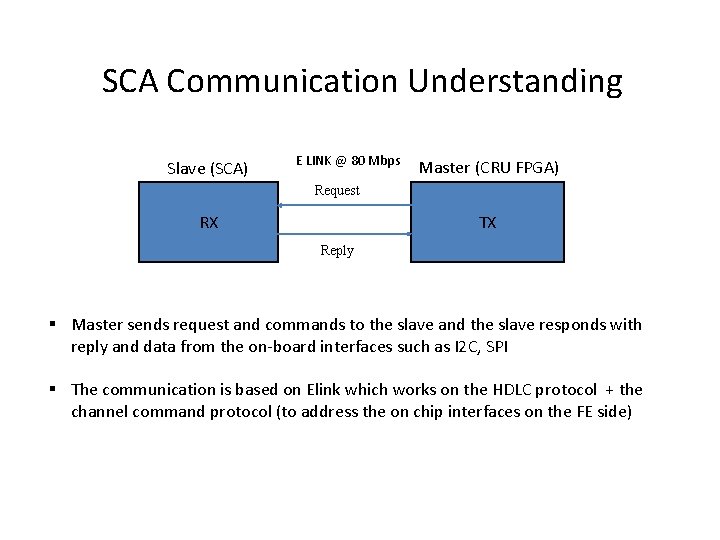

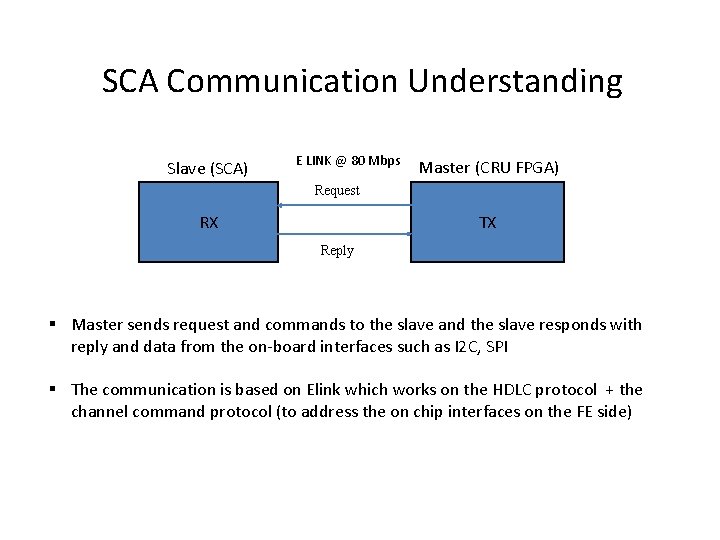

SCA Communication Understanding Slave (SCA) E LINK @ 80 Mbps Master (CRU FPGA) Request TX RX Reply § Master sends request and commands to the slave and the slave responds with reply and data from the on-board interfaces such as I 2 C, SPI § The communication is based on Elink which works on the HDLC protocol + the channel command protocol (to address the on chip interfaces on the FE side)

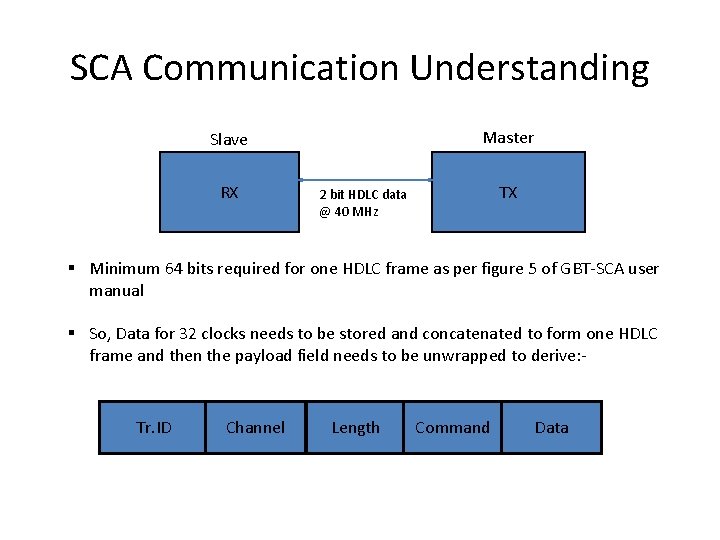

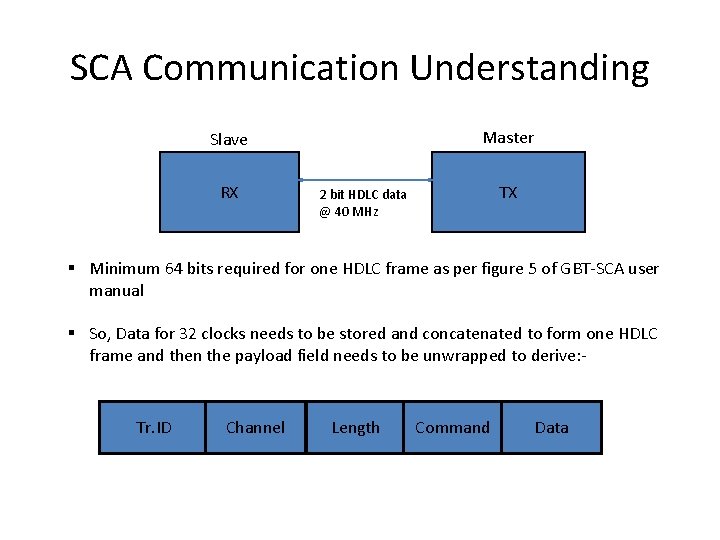

SCA Communication Understanding Master Slave RX TX 2 bit HDLC data @ 40 MHz § Minimum 64 bits required for one HDLC frame as per figure 5 of GBT-SCA user manual § So, Data for 32 clocks needs to be stored and concatenated to form one HDLC frame and then the payload field needs to be unwrapped to derive: - Tr. ID Channel Length Command Data

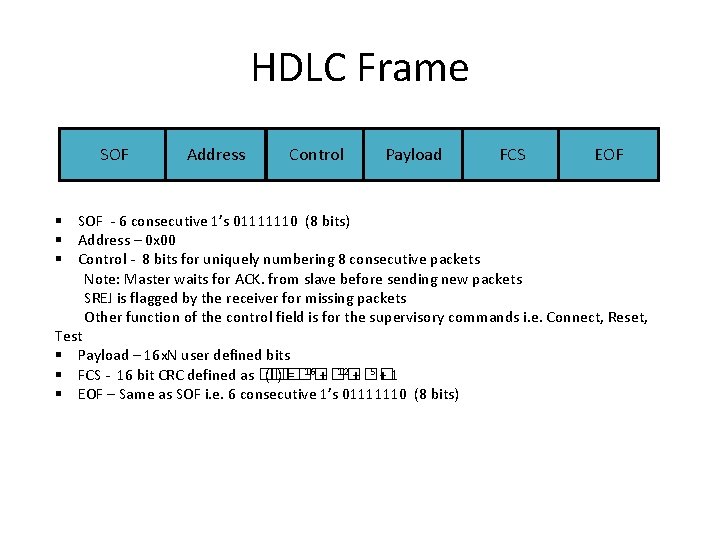

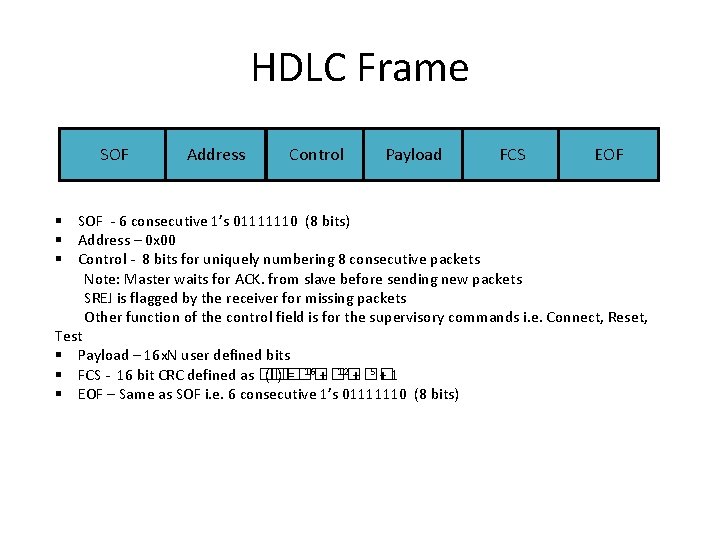

HDLC Frame SOF Address Control Payload FCS EOF § SOF - 6 consecutive 1’s 01111110 (8 bits) § Address – 0 x 00 § Control - 8 bits for uniquely numbering 8 consecutive packets Note: Master waits for ACK. from slave before sending new packets SREJ is flagged by the receiver for missing packets Other function of the control field is for the supervisory commands i. e. Connect, Reset, Test § Payload – 16 x. N user defined bits 16 + �� 12 + �� 5+1 § FCS - 16 bit CRC defined as �� (�� ) = �� § EOF – Same as SOF i. e. 6 consecutive 1’s 01111110 (8 bits)

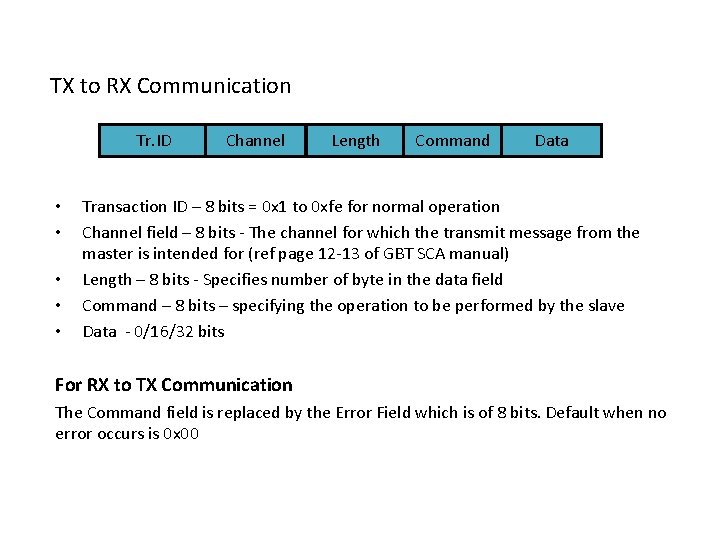

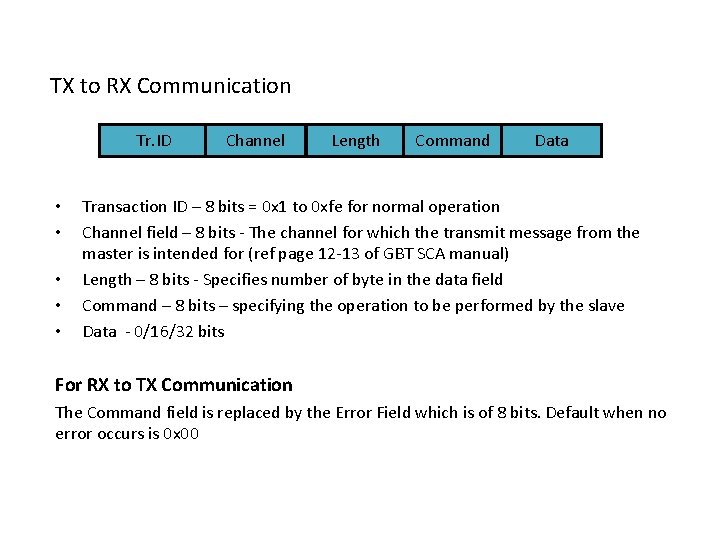

TX to RX Communication Tr. ID • • • Channel Length Command Data Transaction ID – 8 bits = 0 x 1 to 0 xfe for normal operation Channel field – 8 bits - The channel for which the transmit message from the master is intended for (ref page 12 -13 of GBT SCA manual) Length – 8 bits - Specifies number of byte in the data field Command – 8 bits – specifying the operation to be performed by the slave Data - 0/16/32 bits For RX to TX Communication The Command field is replaced by the Error Field which is of 8 bits. Default when no error occurs is 0 x 00

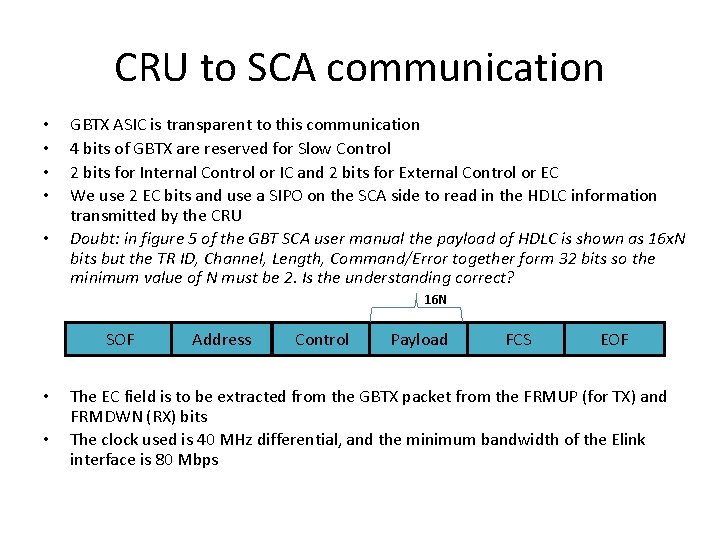

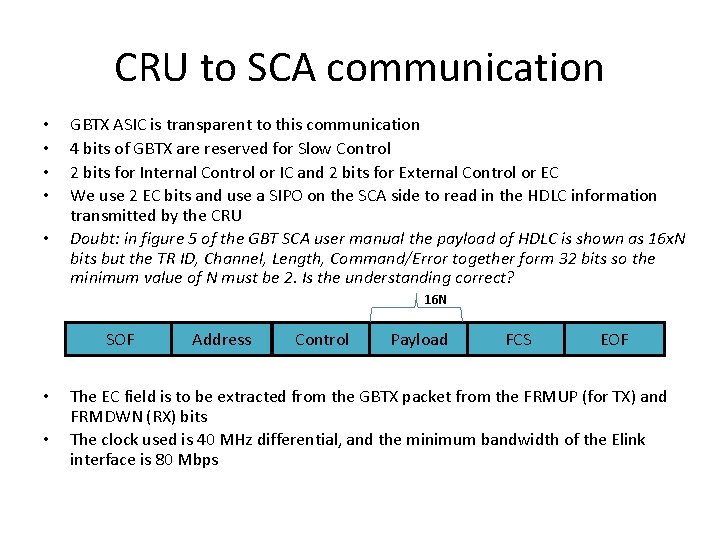

CRU to SCA communication • • • GBTX ASIC is transparent to this communication 4 bits of GBTX are reserved for Slow Control 2 bits for Internal Control or IC and 2 bits for External Control or EC We use 2 EC bits and use a SIPO on the SCA side to read in the HDLC information transmitted by the CRU Doubt: in figure 5 of the GBT SCA user manual the payload of HDLC is shown as 16 x. N bits but the TR ID, Channel, Length, Command/Error together form 32 bits so the minimum value of N must be 2. Is the understanding correct? 16 N SOF • • Address Control Payload FCS EOF The EC field is to be extracted from the GBTX packet from the FRMUP (for TX) and FRMDWN (RX) bits The clock used is 40 MHz differential, and the minimum bandwidth of the Elink interface is 80 Mbps

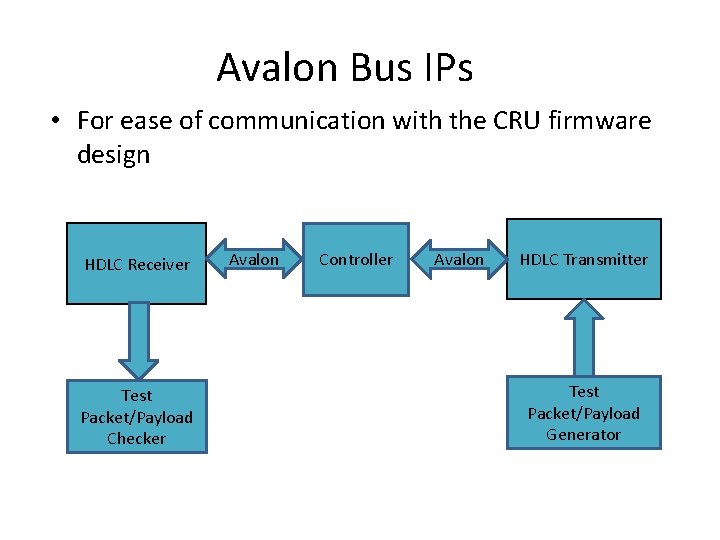

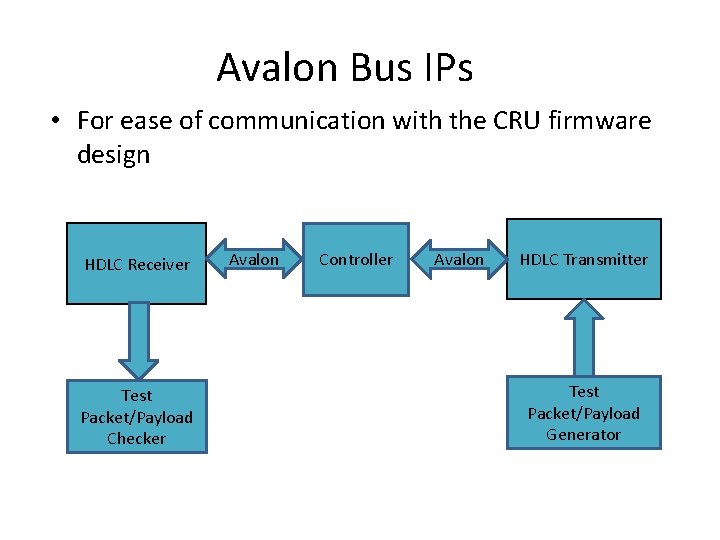

Avalon Bus IPs • For ease of communication with the CRU firmware design HDLC Receiver Test Packet/Payload Checker Avalon Controller Avalon HDLC Transmitter Test Packet/Payload Generator