SBSA 1 n Fast DAQ Alexandre Camsonne October

SBS/A 1 n Fast DAQ Alexandre Camsonne October 19 th 2012

Outline • • • Overview Experiments Channel count Module flipping Test stand CODA 3 / Intel CPU Task list Manpower Timeline Conclusions

Overview • Mixed DAQ using VME for GEM readout and Fastbus for other detectors • Use multiple crates and modules to reduce deadtime

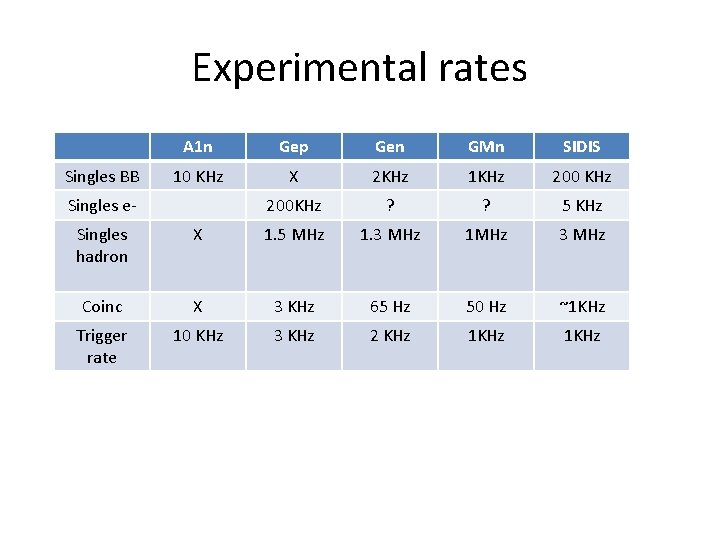

Experimental rates Singles BB A 1 n Gep Gen GMn SIDIS 10 KHz X 2 KHz 1 KHz 200 KHz ? ? 5 KHz Singles e. Singles hadron X 1. 5 MHz 1. 3 MHz 1 MHz 3 MHz Coinc X 3 KHz 65 Hz 50 Hz ~1 KHz Trigger rate 10 KHz 3 KHz 2 KHz 1 KHz

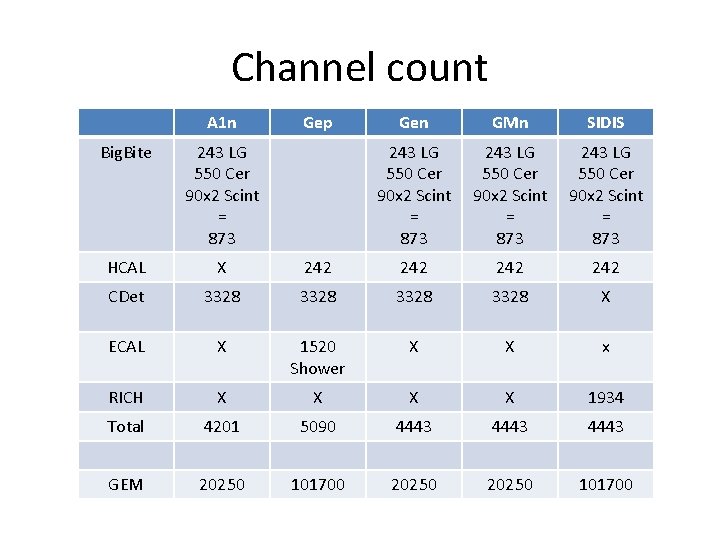

Channel count A 1 n Gep Gen GMn SIDIS 243 LG 550 Cer 90 x 2 Scint = 873 Big. Bite 243 LG 550 Cer 90 x 2 Scint = 873 HCAL X 242 242 CDet 3328 X ECAL X 1520 Shower X X x RICH X X 1934 Total 4201 5090 4443 GEM 20250 101700

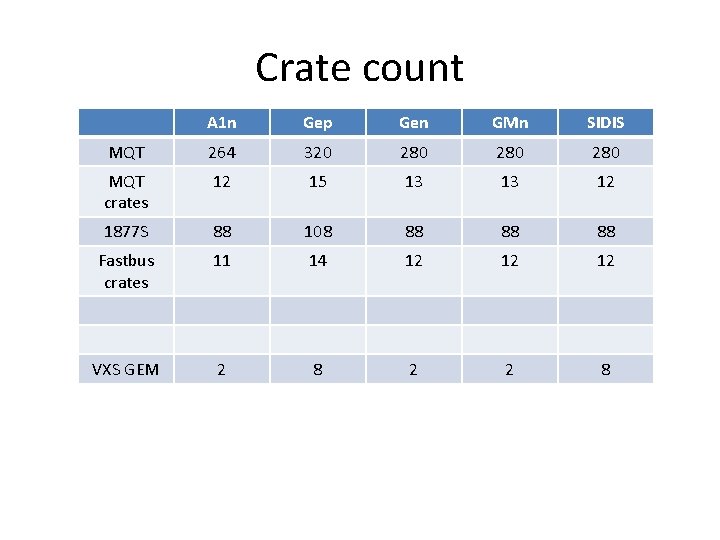

Crate count A 1 n Gep Gen GMn SIDIS MQT 264 320 280 280 MQT crates 12 15 13 13 12 1877 S 88 108 88 88 88 Fastbus crates 11 14 12 12 12 VXS GEM 2 8 2 2 8

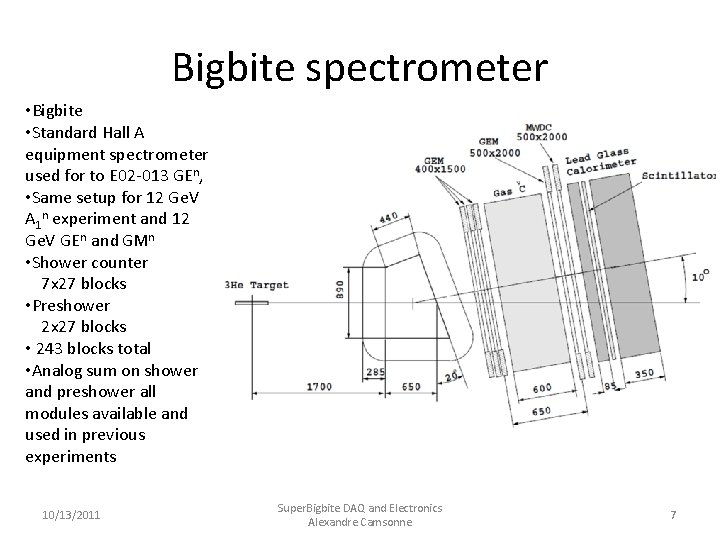

Bigbite spectrometer • Bigbite • Standard Hall A equipment spectrometer used for to E 02 -013 GEn, • Same setup for 12 Ge. V A 1 n experiment and 12 Ge. V GEn and GMn • Shower counter 7 x 27 blocks • Preshower 2 x 27 blocks • 243 blocks total • Analog sum on shower and preshower all modules available and used in previous experiments 10/13/2011 Super. Bigbite DAQ and Electronics Alexandre Camsonne 7

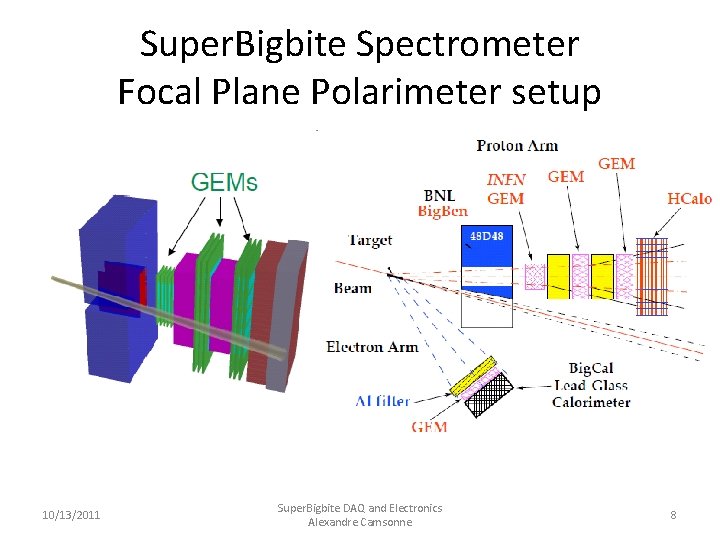

Super. Bigbite Spectrometer Focal Plane Polarimeter setup 10/13/2011 Super. Bigbite DAQ and Electronics Alexandre Camsonne 8

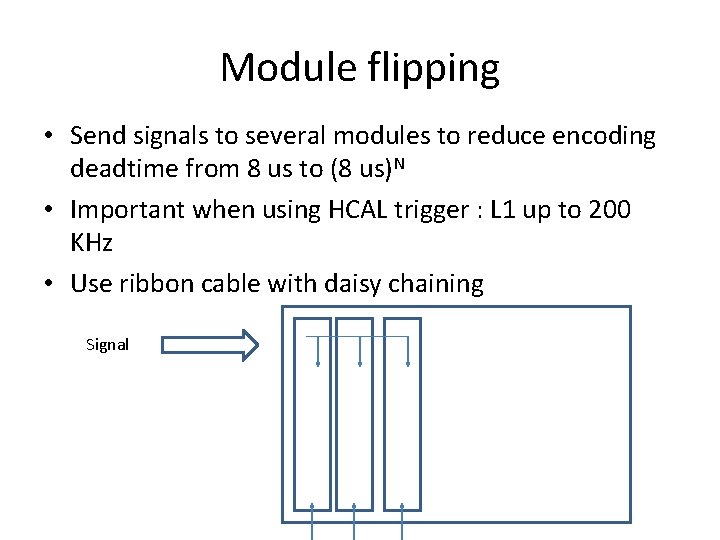

Module flipping • Send signals to several modules to reduce encoding deadtime from 8 us to (8 us)N • Important when using HCAL trigger : L 1 up to 200 KHz • Use ribbon cable with daisy chaining Signal

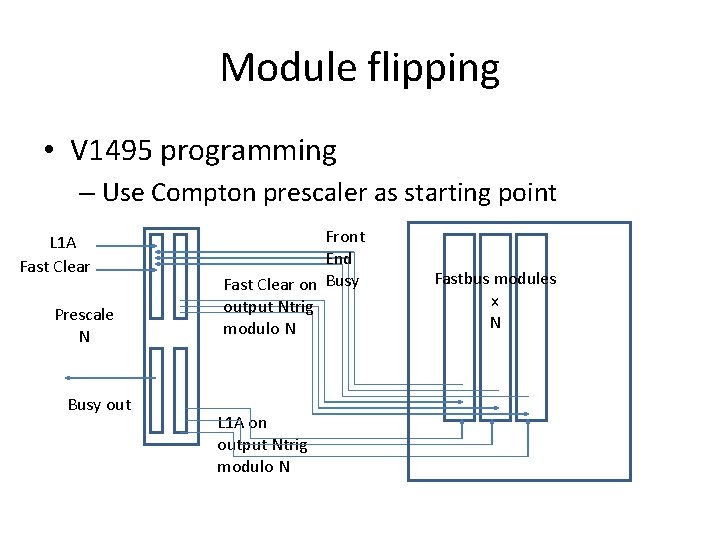

Module flipping • V 1495 programming – Use Compton prescaler as starting point L 1 A Fast Clear Prescale N Busy out Front End Fast Clear on Busy output Ntrig modulo N L 1 A on output Ntrig modulo N Fastbus modules x N

Module flipping • V 1495 programming – First version working should be good enough to evaluate dead time improvement – Need implement busy logic and fast clear – Want to implement FIFO to store state for readout and TDC output with board status for sync check – Need to check synch and timing resolution

Test stand • • • 2 Fastbus Crate and PS from Hall B OSP done CODA running from 2 SFI with Intel VME CPU TS and VME 64 X crate to be installed Error on boards – Interference of TI with Fastbus, one bug fixed with new TI ( missing interrupt line ) – Possibly some other issues between SFI and VME TI – Debugging

Intel CPU • Installed Linux operating system on Compact Flash so board can boot stand alone • Readout of Fastbus working • Trigger with old VME TI with SFI working trying new TI to test improvement with event blocking • Develop code for Fastbus readout with new TI • Develop code for module flipping readout • Port MPD code to Intel CPU

MQT • 16 channels per board • Current drawn to be determined • Additional cost of MQT power supplies most likely similar to Fastbus PS with FAN about 11 K$

Tasks • • Test GAC, ATC board spares Test SFI spares V 1495 Module flipping programming Test Intel CPU

Man Power • Alexandre Camsonne • Sergey Abrahamyan • Daniel Kirby • Mark Jones 10/13/2011 Super. Bigbite DAQ and Electronics Alexandre Camsonne 16

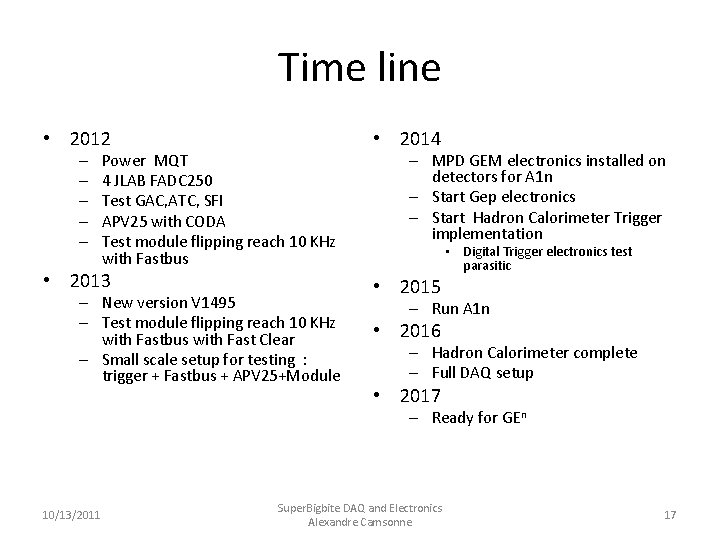

Time line • 2012 – – – Power MQT 4 JLAB FADC 250 Test GAC, ATC, SFI APV 25 with CODA Test module flipping reach 10 KHz with Fastbus • 2013 – New version V 1495 – Test module flipping reach 10 KHz with Fastbus with Fast Clear – Small scale setup for testing : trigger + Fastbus + APV 25+Module • 2014 – MPD GEM electronics installed on detectors for A 1 n – Start Gep electronics – Start Hadron Calorimeter Trigger implementation • 2015 • Digital Trigger electronics test parasitic – Run A 1 n • 2016 – Hadron Calorimeter complete – Full DAQ setup • 2017 – Ready for GEn 10/13/2011 Super. Bigbite DAQ and Electronics Alexandre Camsonne 17

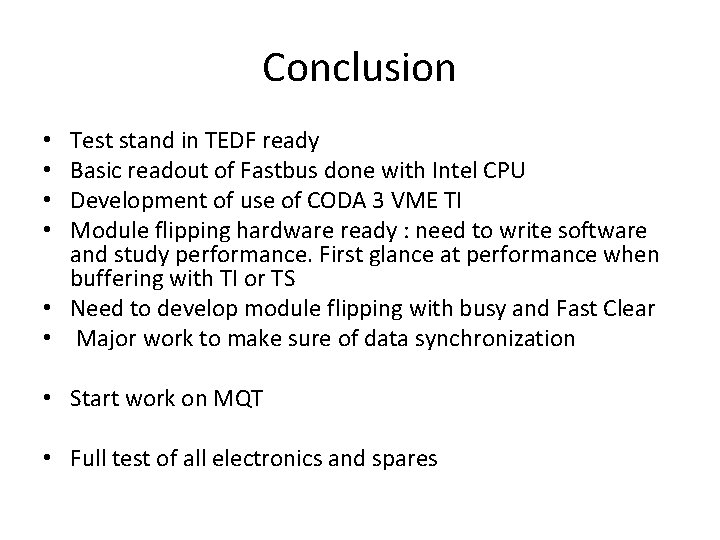

Conclusion Test stand in TEDF ready Basic readout of Fastbus done with Intel CPU Development of use of CODA 3 VME TI Module flipping hardware ready : need to write software and study performance. First glance at performance when buffering with TI or TS • Need to develop module flipping with busy and Fast Clear • Major work to make sure of data synchronization • • • Start work on MQT • Full test of all electronics and spares

- Slides: 18