SAR ADC Input Drive Definition by example using

SAR ADC Input Drive (Definition by example using ADS 8528) Tim Green, MGTS Precision Linear Analog Applications February 16, 2016 1

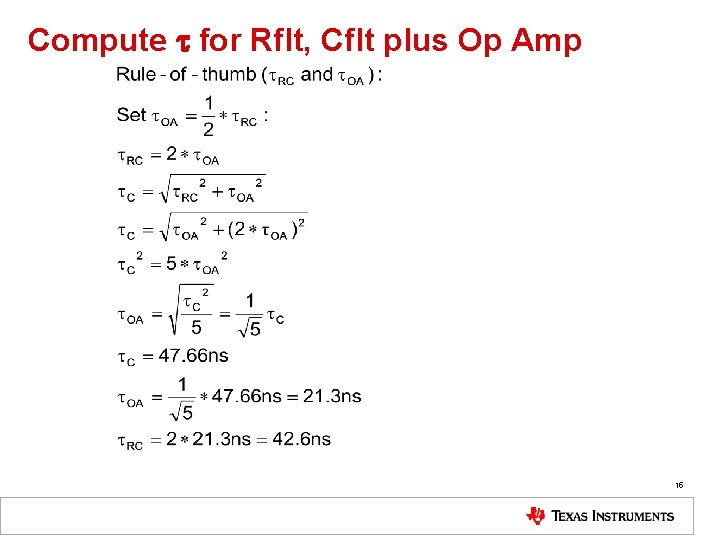

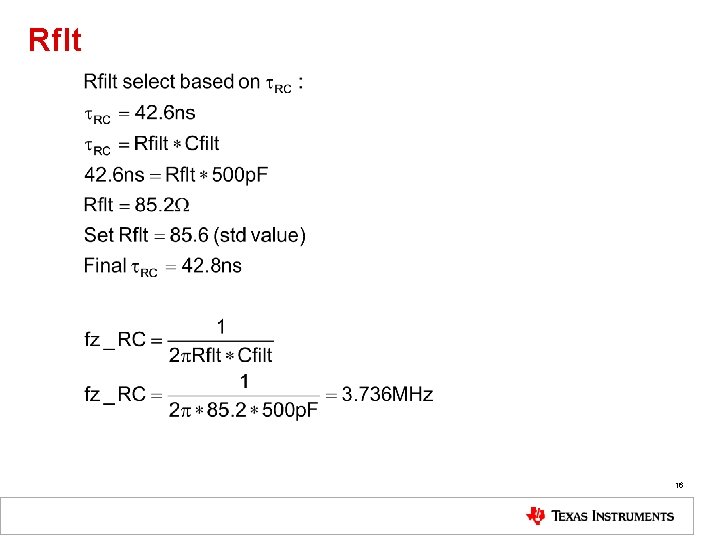

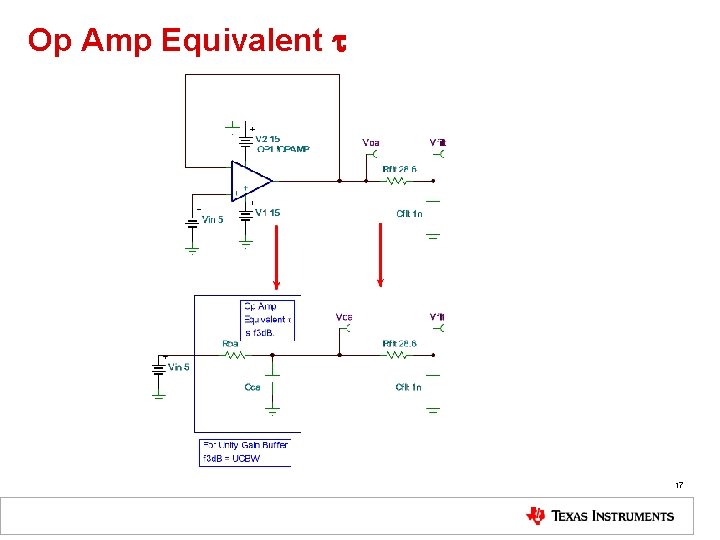

Summary – SAR ADC Input Drive 1) Start by defining tacq and tconv. 2) Model ADC input from datasheet. 3) Based on Vin full-scale compute charge for Csh. 4) Assume ½ charge will come from Cflt and ½ charge from Op Amp. 5) Assume initial drop on Cflt=100 m. V (or your desired delta_V) at beginning of tacq. 6) Choose Cflt based on ½ charge on Csh and 100 m. V drop. 7) Design goal is for <1/2 LSB error and full settle by ¾ of tacq. 8) Compute t. C based on 100 m. V drop on Cflt and ¾ tacq. 9) Assume t. C equals square root sum of squares of t. RC and t. OA. 10) Assume t. OA equals ½* t. RC and solve for t. RC and t. OA. 11) Use Cflt and t. RC to find Rflt. 12) Use t. OA to f 3 d. B for Op Amp. 13) Create Impedance Plot vs Frequency Rflt, Cflt 14) Plot Op Amp Zout based on t. OA and ensure intersect of Op Amp Zout and Rflt is 2*(1/t. RC) 15) Step 14) assures if Aol moves by ½ or double in UGBW still have stable circuit. 16) Any Op Amp with UGBW in the Zout Hi-frequency box and to the right of 2*(1/t. RC) is a possible choice. UGBW is where Zout inductive turns to resistive at high frequency. 17) Choose Op Amp. Verify SPICE Macromodel for Aol and Zo or Zout from Datasheet. 18) Iterate with different Op Amp and Rflt, Cflt adjustments until accuracy and settling < tacq. 19) Check op amp out and voltage across Cfilt recover to Steady State voltage at end of tconv. 20) Op Amps with gain can be low pass filtered in their feedback (CF) to get close to unity gain Zout characteristic which allows for lower BW amp when using op amp in gain. 2

ADS 8528 Input Model 3

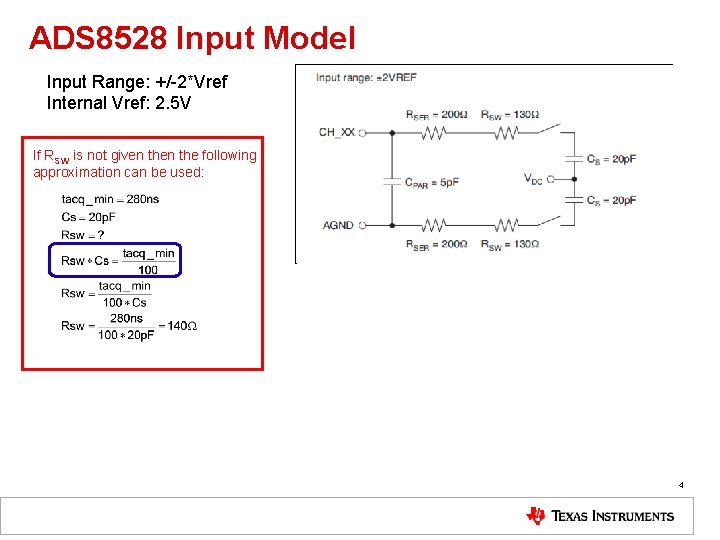

ADS 8528 Input Model Input Range: +/-2*Vref Internal Vref: 2. 5 V If RSW is not given the following approximation can be used: 4

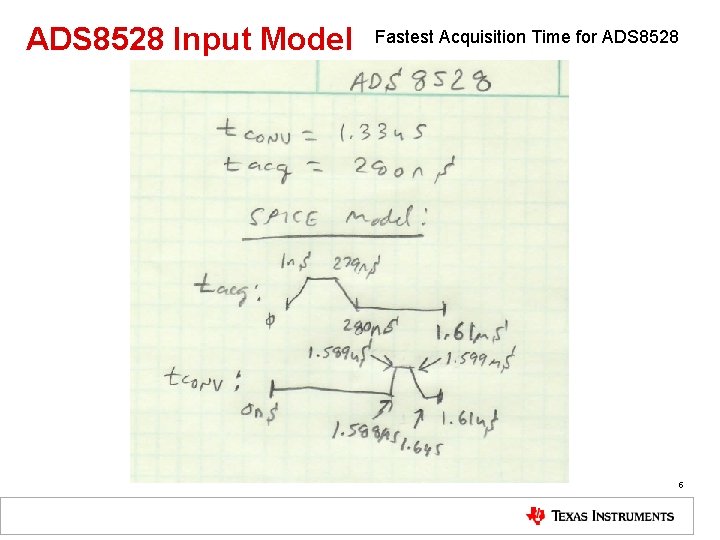

ADS 8528 Input Model Fastest Acquisition Time for ADS 8528 5

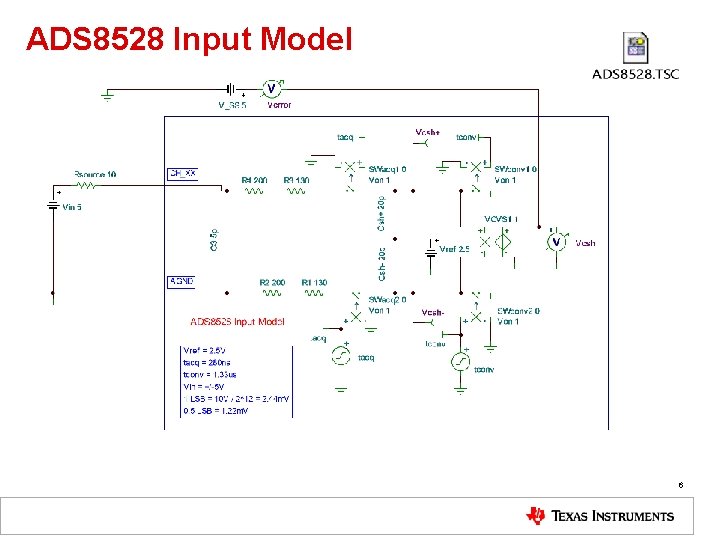

ADS 8528 Input Model 6

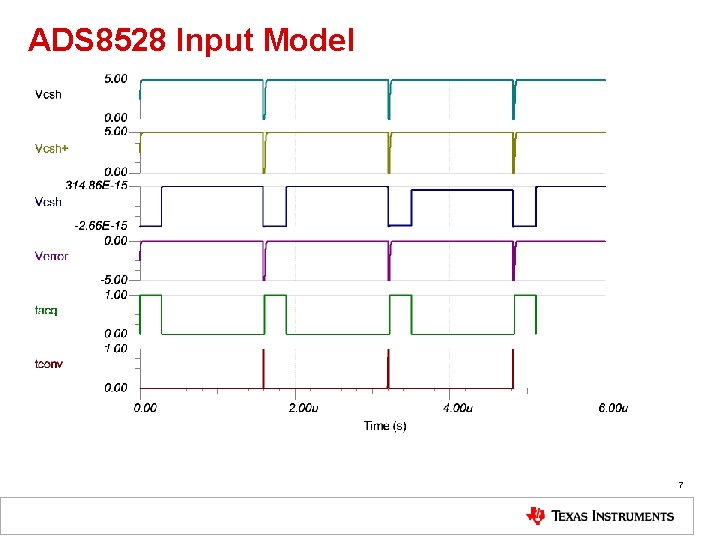

ADS 8528 Input Model 7

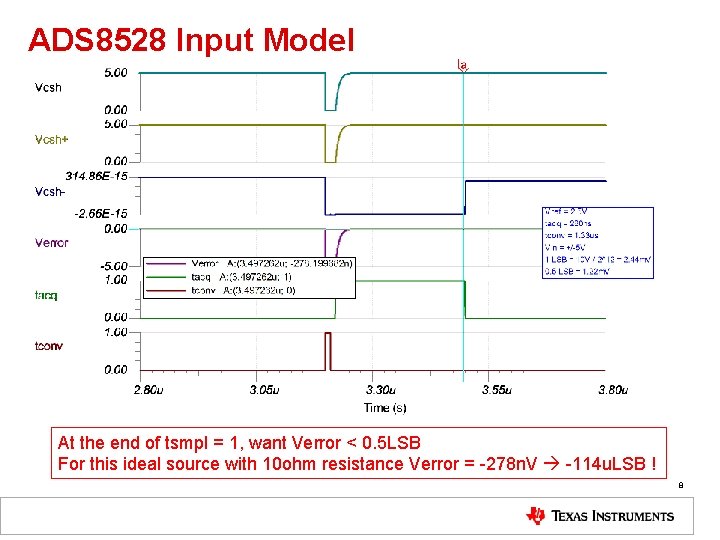

ADS 8528 Input Model At the end of tsmpl = 1, want Verror < 0. 5 LSB For this ideal source with 10 ohm resistance Verror = -278 n. V -114 u. LSB ! 8

ADS 8528 Input Drive Cflt, Rflt, Op Amp 9

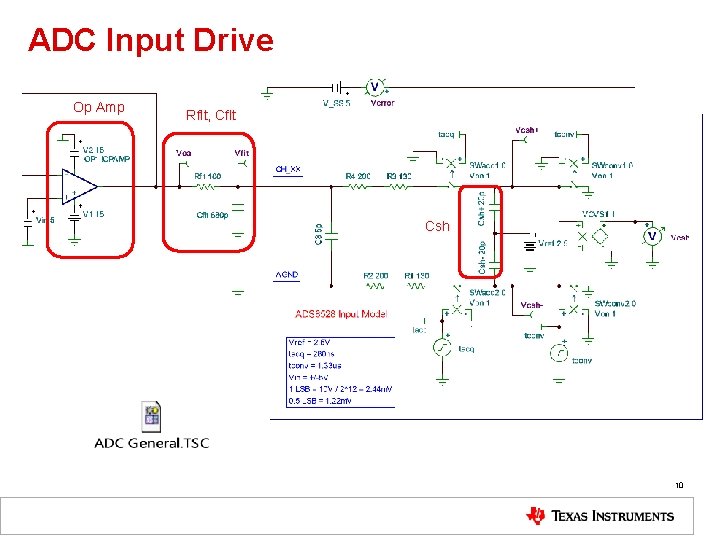

ADC Input Drive Op Amp Rflt, Cflt Csh 10

Cflt 11

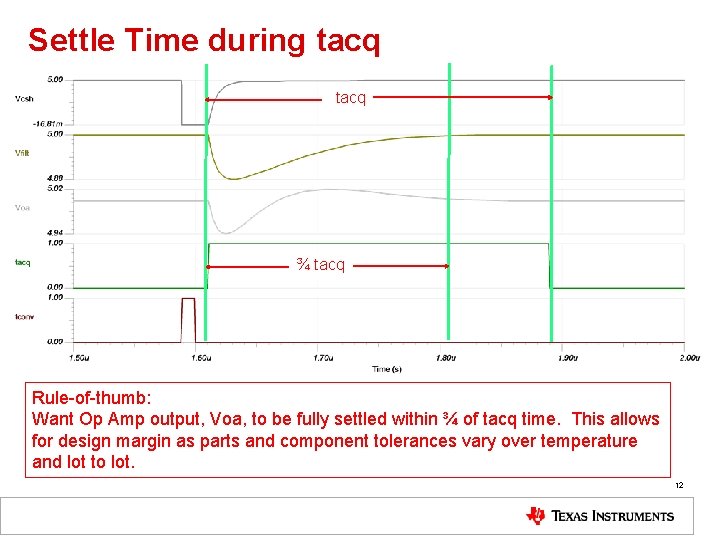

Settle Time during tacq ¾ tacq Rule-of-thumb: Want Op Amp output, Voa, to be fully settled within ¾ of tacq time. This allows for design margin as parts and component tolerances vary over temperature and lot to lot. 12

Compute t for Rflt, Cflt plus Op Amp 13

Compute t for Rflt, Cflt plus Op Amp 14

Compute t for Rflt, Cflt plus Op Amp 15

Rflt 16

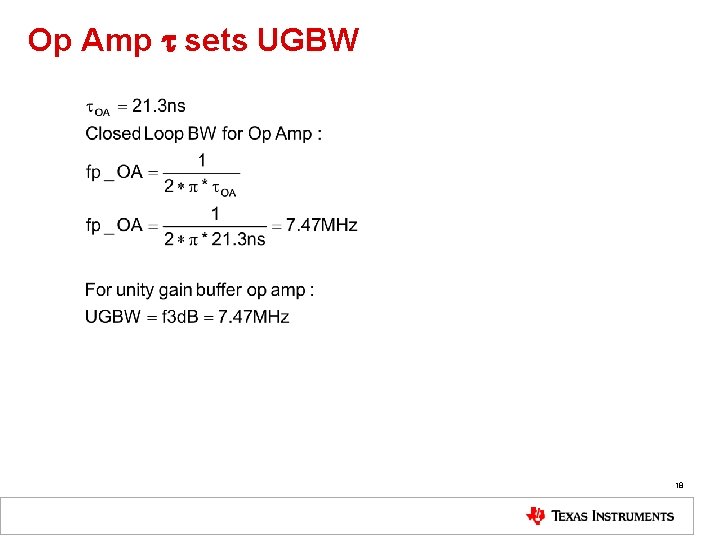

Op Amp Equivalent t 17

Op Amp t sets UGBW 18

Possible Op Amp Candidates 19

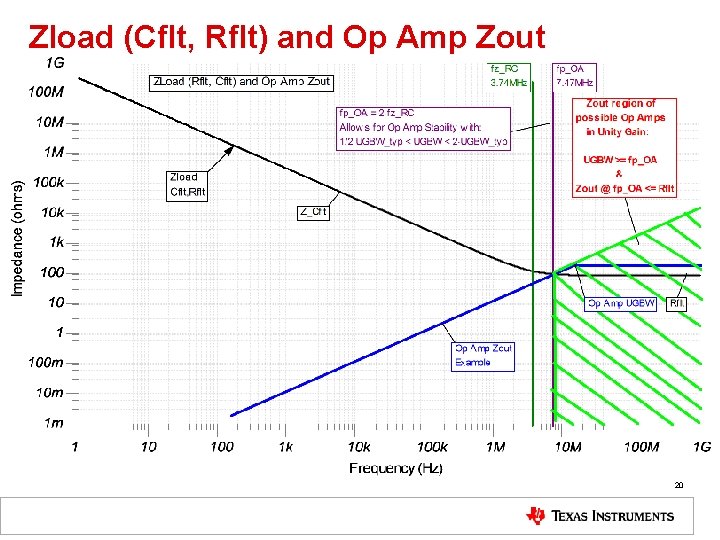

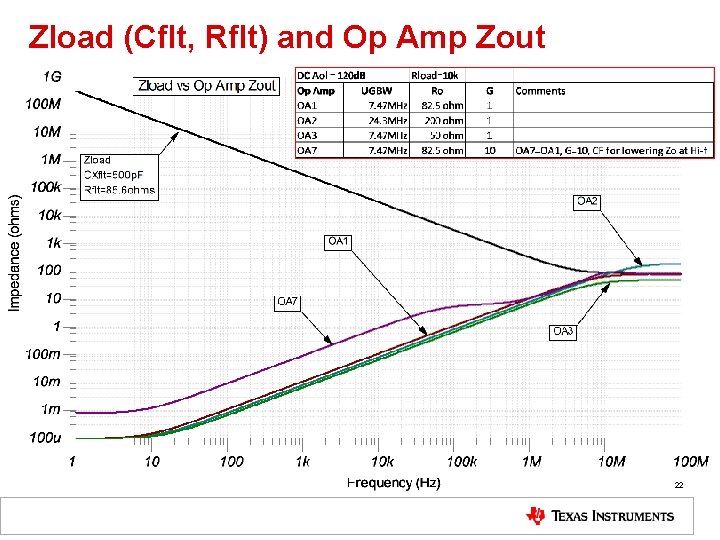

Zload (Cflt, Rflt) and Op Amp Zout 20

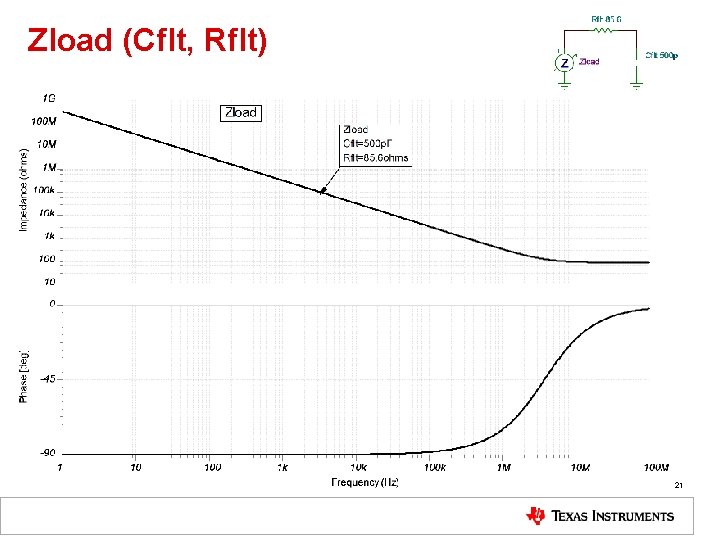

Zload (Cflt, Rflt) 21

Zload (Cflt, Rflt) and Op Amp Zout 22

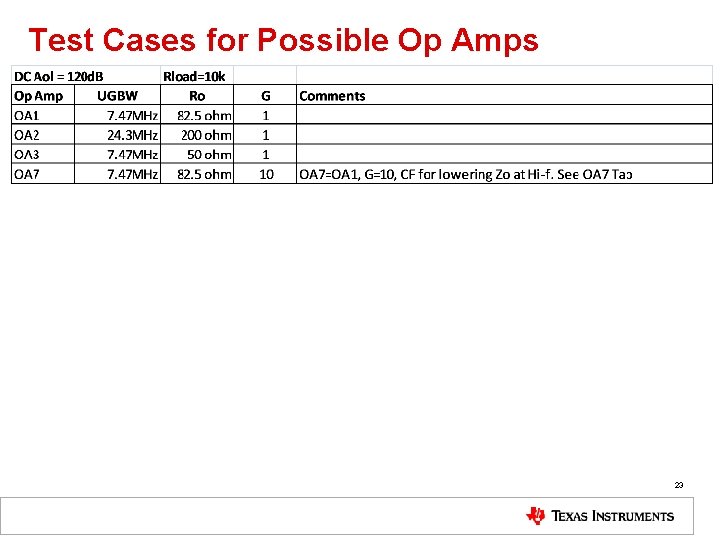

Test Cases for Possible Op Amps 23

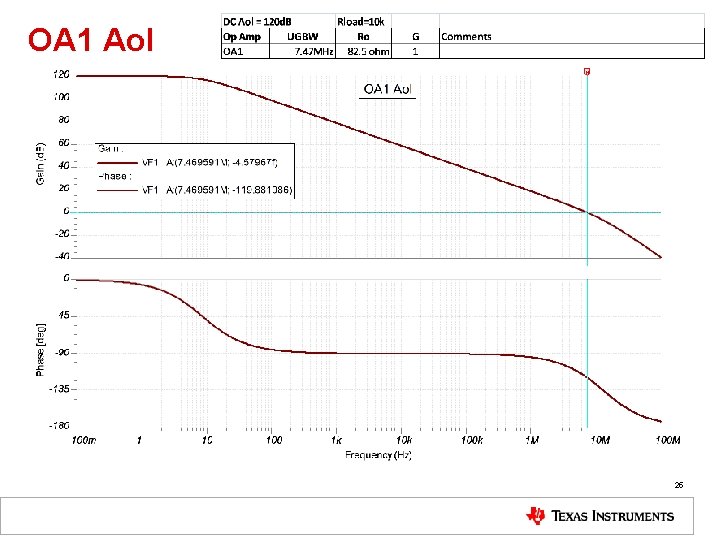

OA 1 Aol 24

OA 1 Aol 25

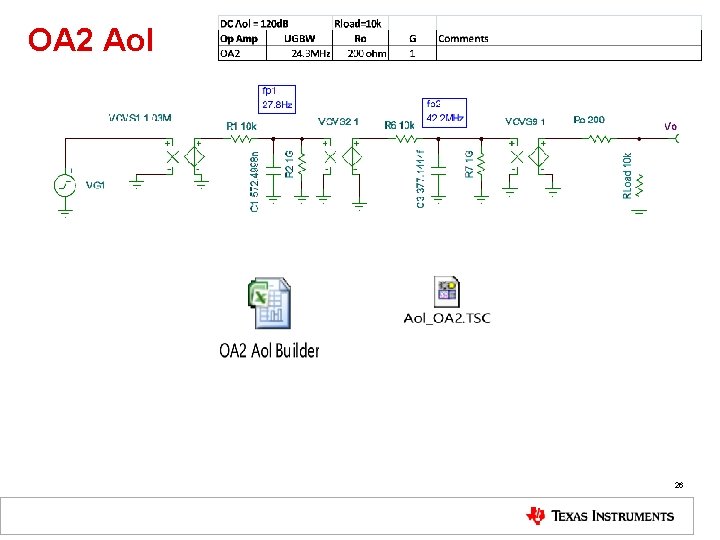

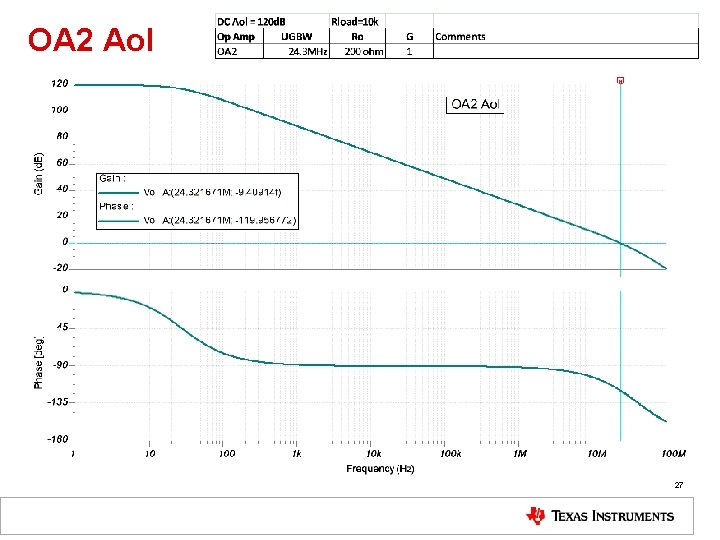

OA 2 Aol 26

OA 2 Aol 27

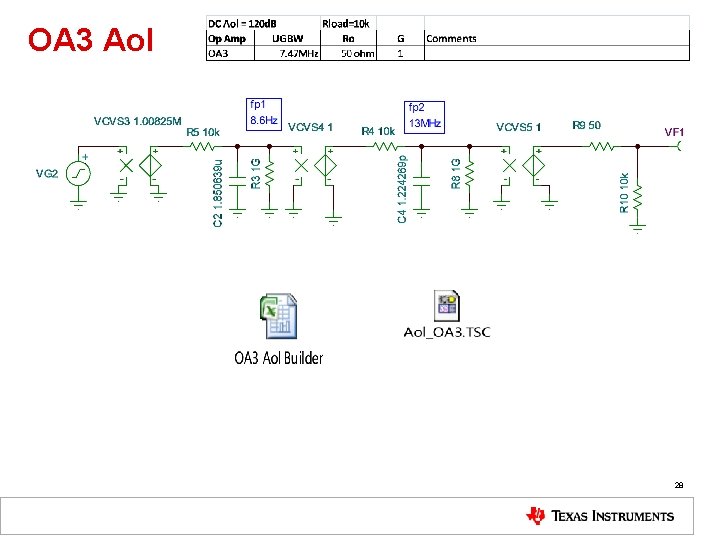

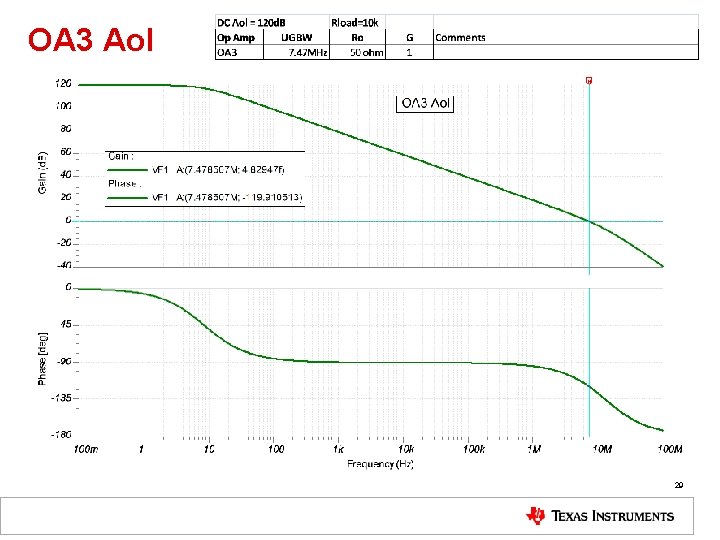

OA 3 Aol 28

OA 3 Aol 29

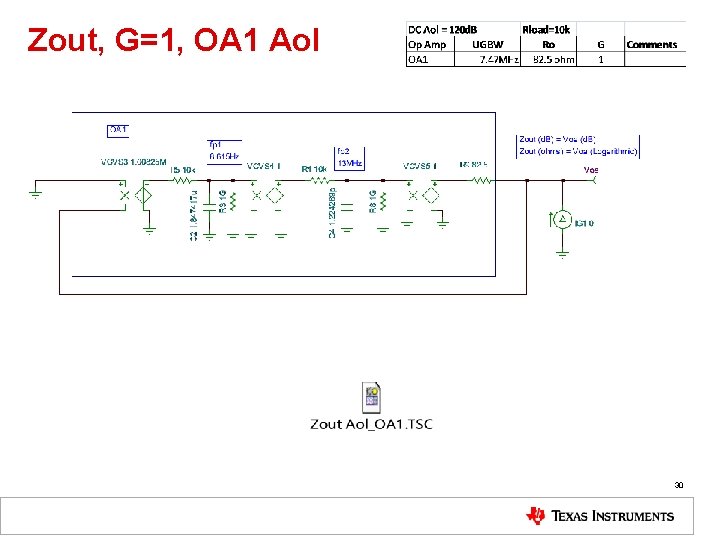

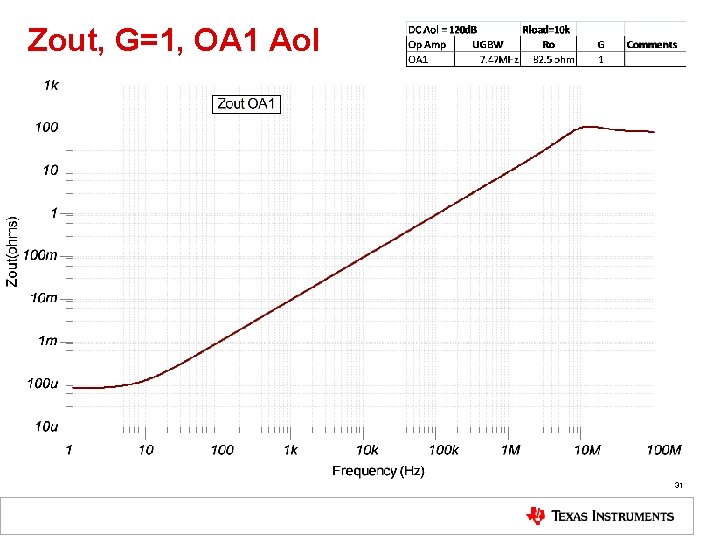

Zout, G=1, OA 1 Aol 30

Zout, G=1, OA 1 Aol 31

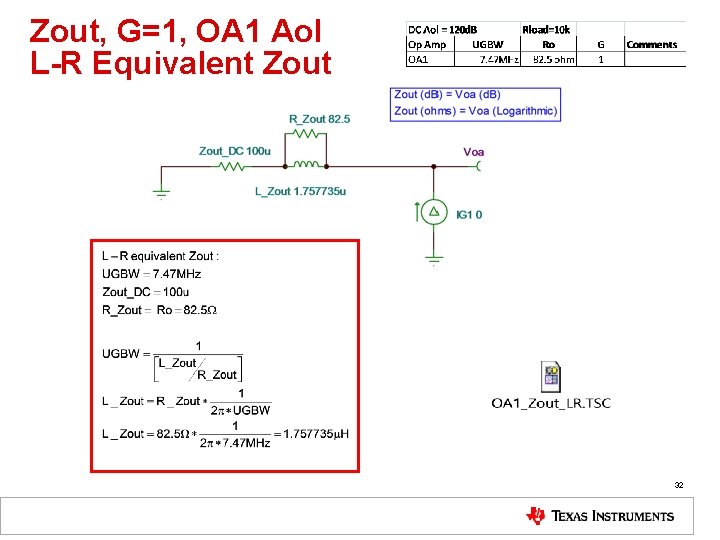

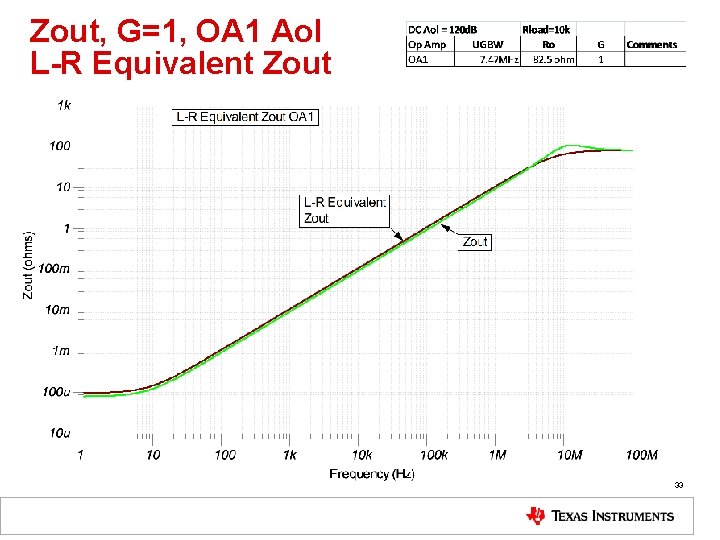

Zout, G=1, OA 1 Aol L-R Equivalent Zout 32

Zout, G=1, OA 1 Aol L-R Equivalent Zout 33

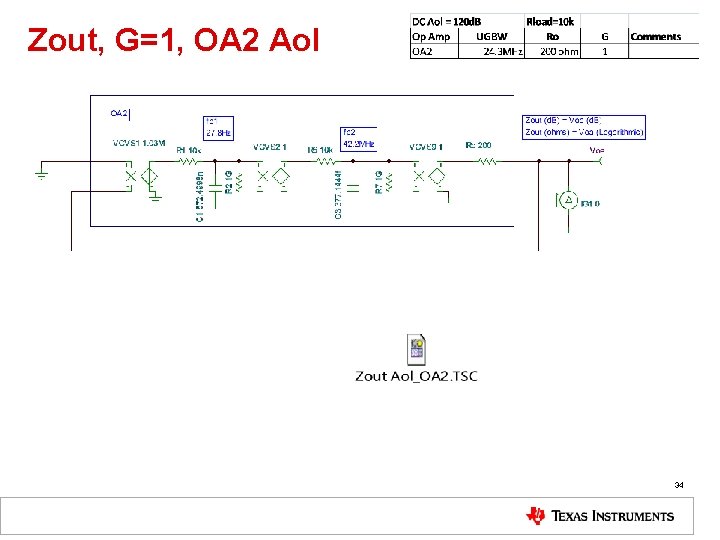

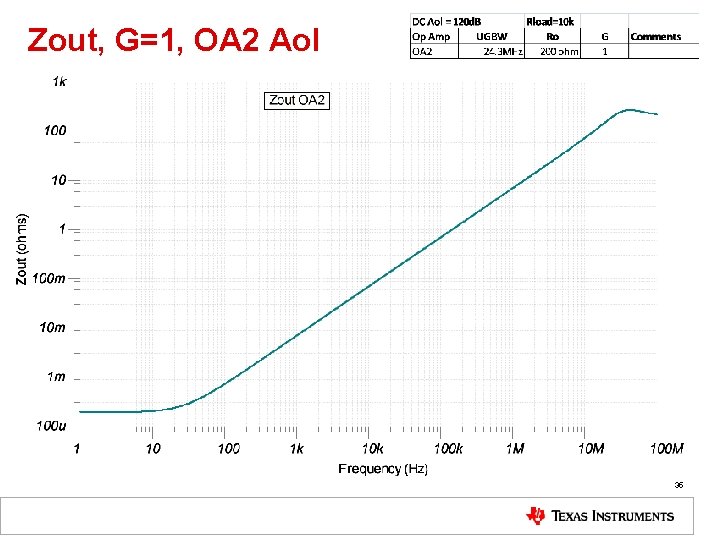

Zout, G=1, OA 2 Aol 34

Zout, G=1, OA 2 Aol 35

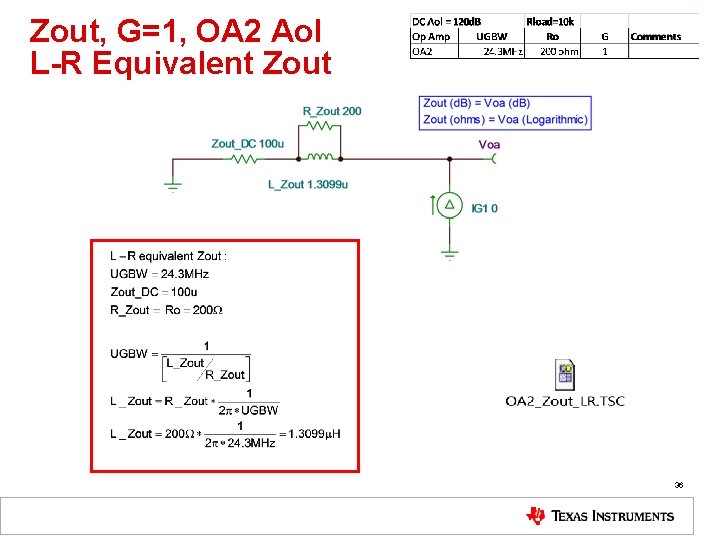

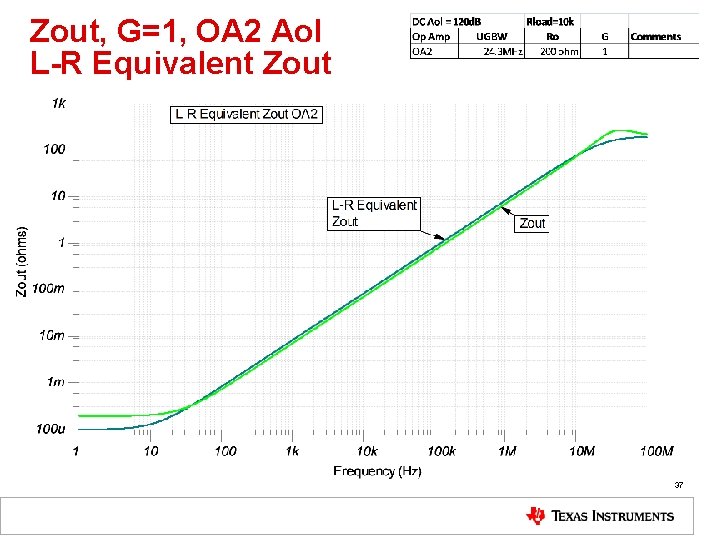

Zout, G=1, OA 2 Aol L-R Equivalent Zout 36

Zout, G=1, OA 2 Aol L-R Equivalent Zout 37

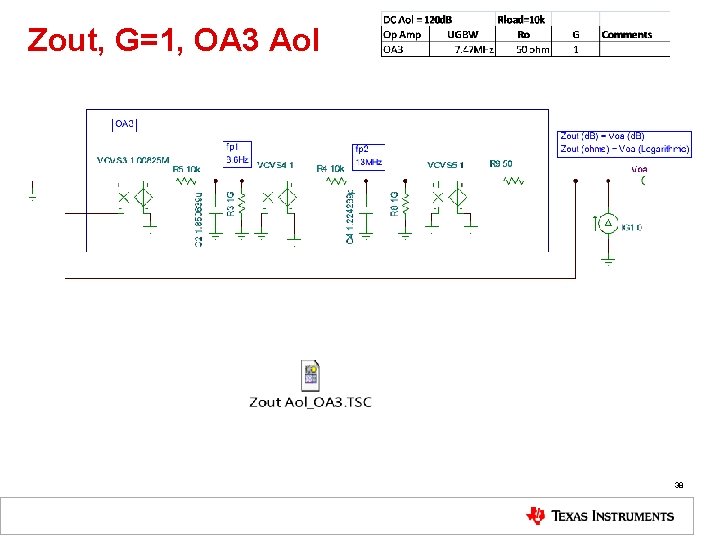

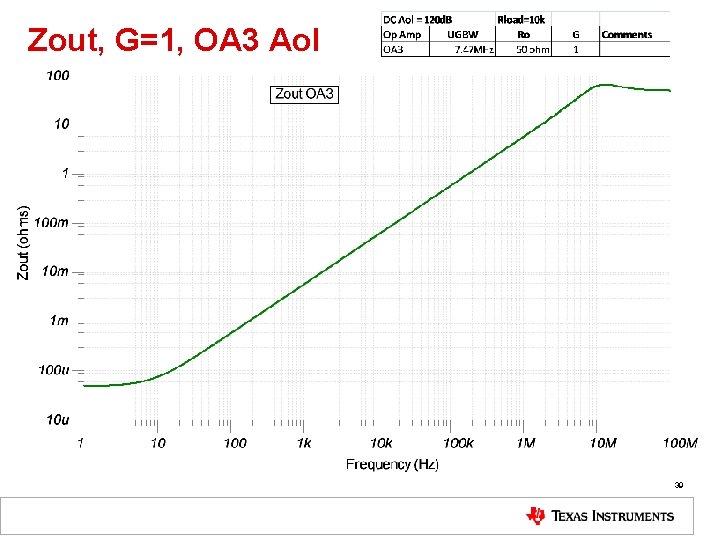

Zout, G=1, OA 3 Aol 38

Zout, G=1, OA 3 Aol 39

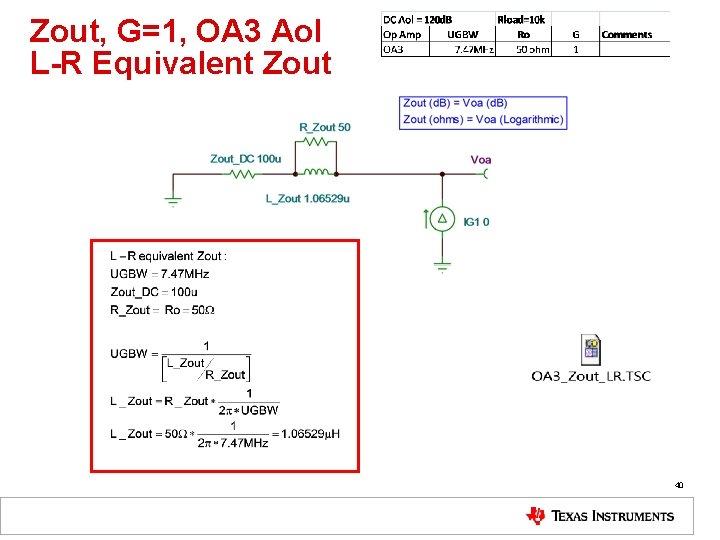

Zout, G=1, OA 3 Aol L-R Equivalent Zout 40

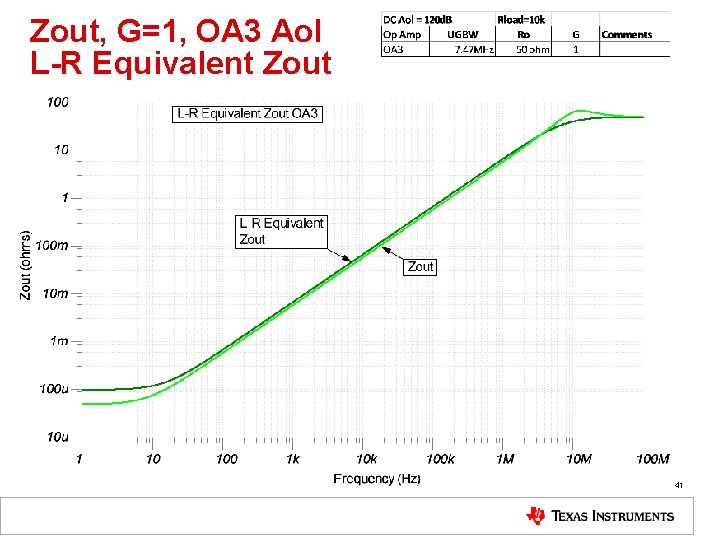

Zout, G=1, OA 3 Aol L-R Equivalent Zout 41

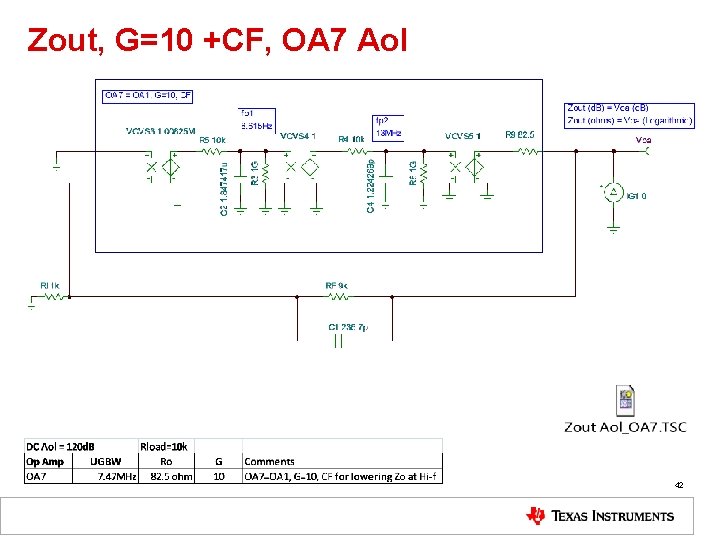

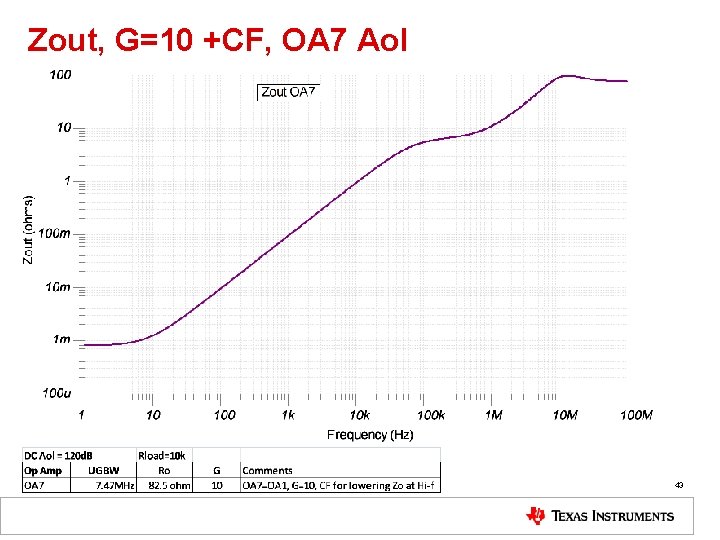

Zout, G=10 +CF, OA 7 Aol 42

Zout, G=10 +CF, OA 7 Aol 43

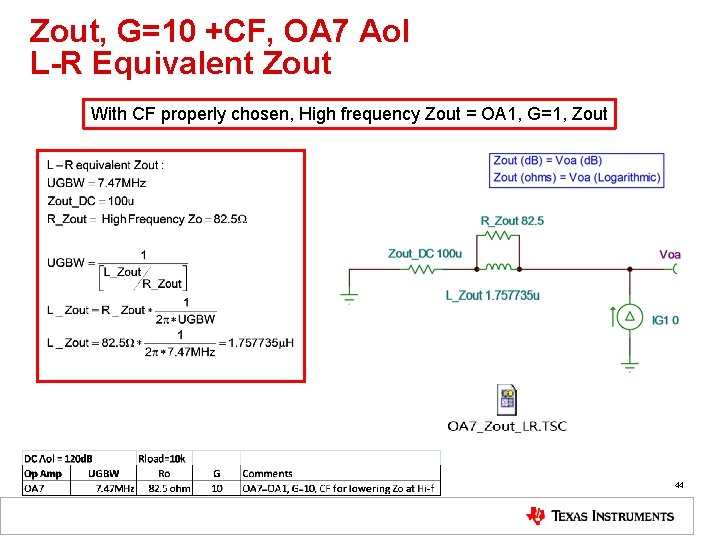

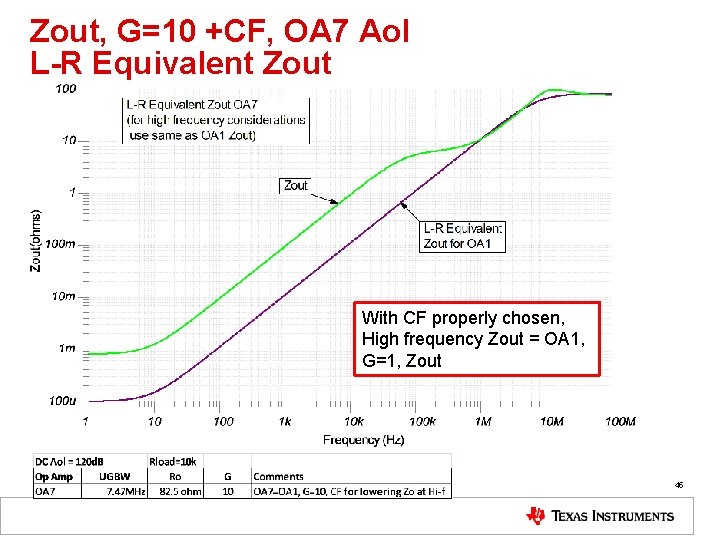

Zout, G=10 +CF, OA 7 Aol L-R Equivalent Zout With CF properly chosen, High frequency Zout = OA 1, G=1, Zout 44

Zout, G=10 +CF, OA 7 Aol L-R Equivalent Zout With CF properly chosen, High frequency Zout = OA 1, G=1, Zout 45

Possible Op Amp Candidates Driving ADS 8528 46

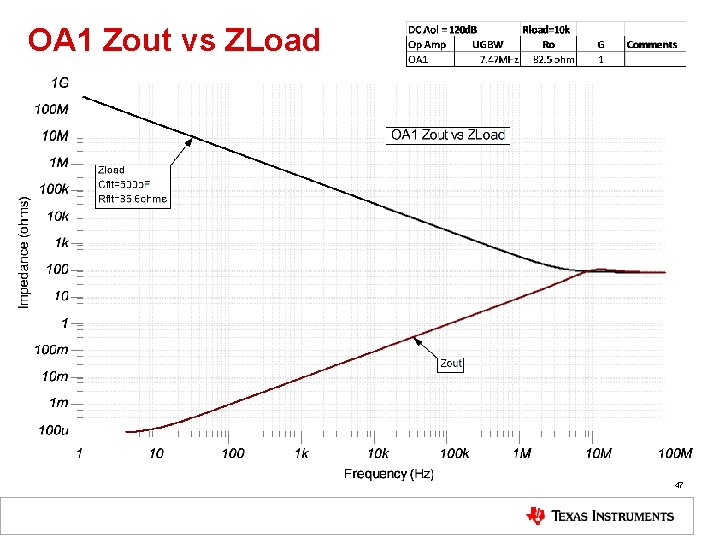

OA 1 Zout vs ZLoad 47

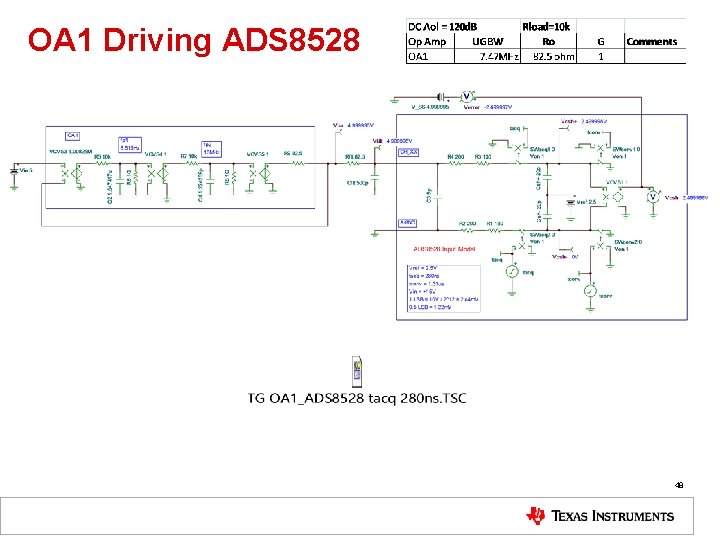

OA 1 Driving ADS 8528 48

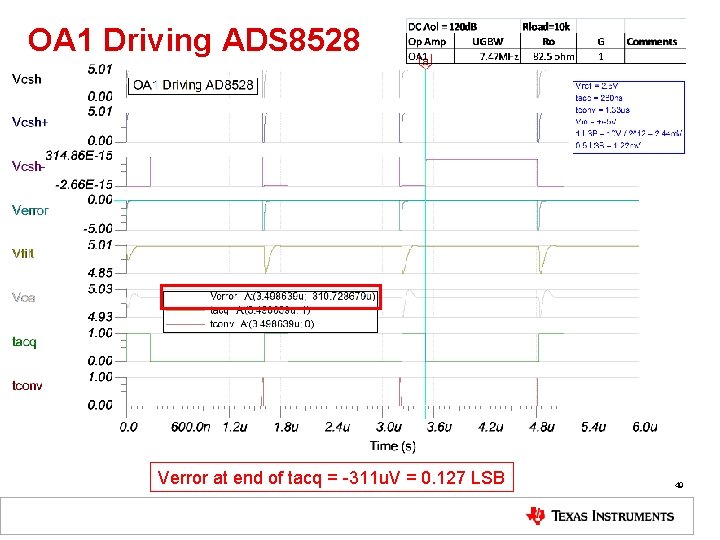

OA 1 Driving ADS 8528 Verror at end of tacq = -311 u. V = 0. 127 LSB 49

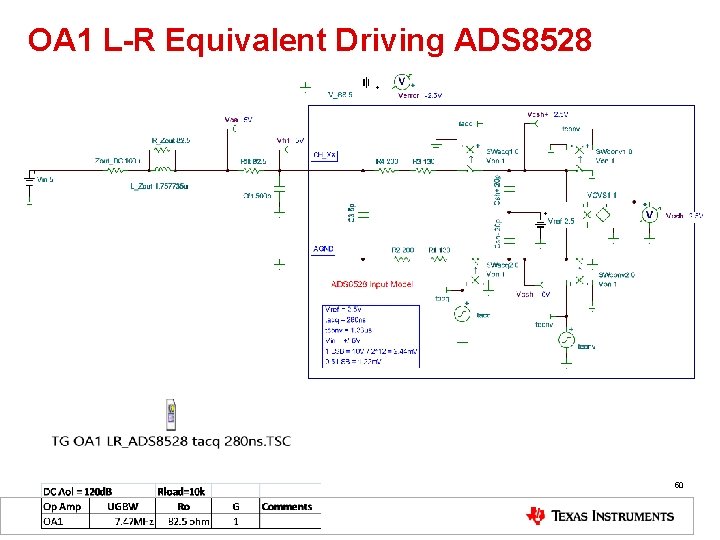

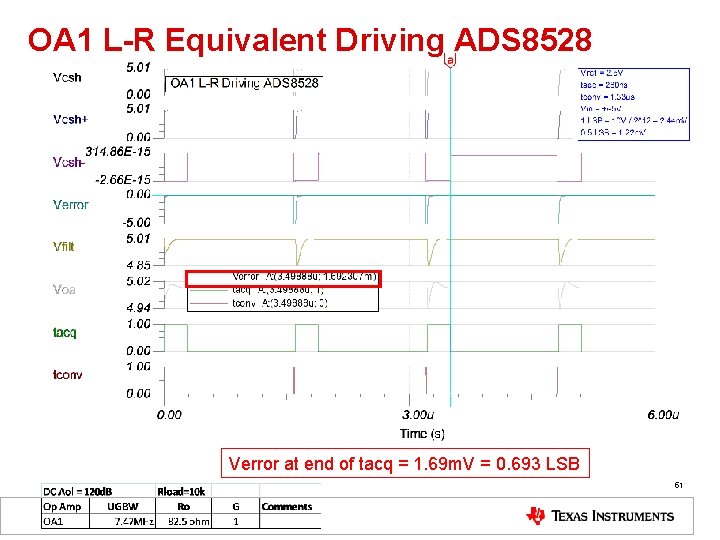

OA 1 L-R Equivalent Driving ADS 8528 50

OA 1 L-R Equivalent Driving ADS 8528 Verror at end of tacq = 1. 69 m. V = 0. 693 LSB 51

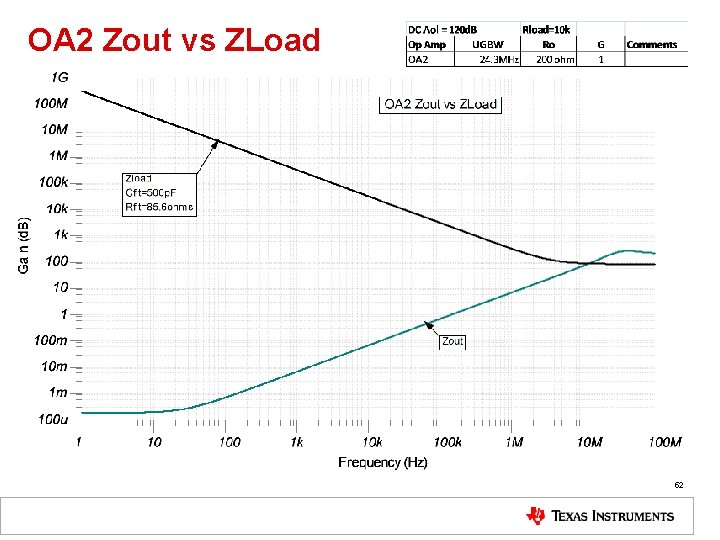

OA 2 Zout vs ZLoad 52

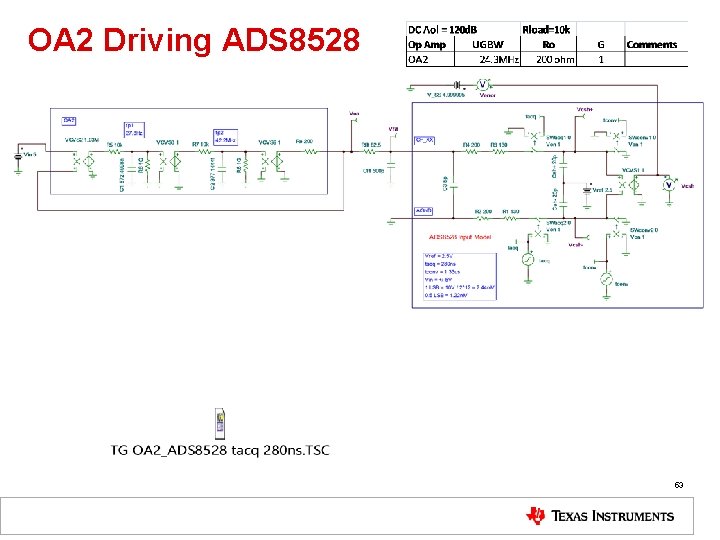

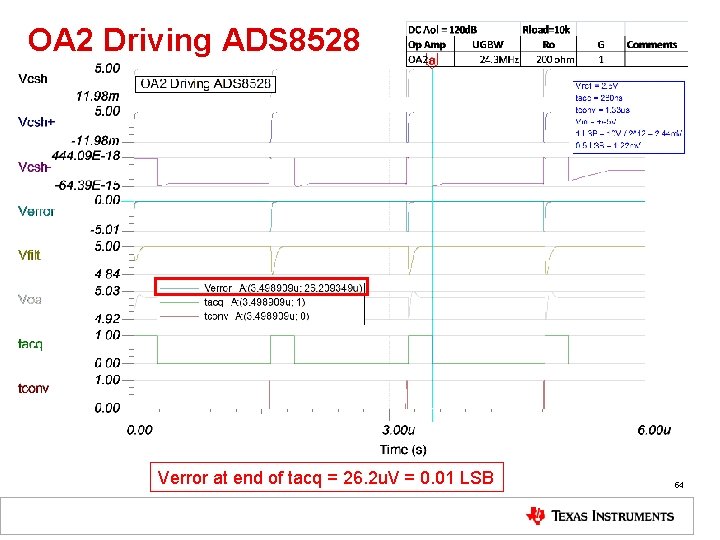

OA 2 Driving ADS 8528 53

OA 2 Driving ADS 8528 Verror at end of tacq = 26. 2 u. V = 0. 01 LSB 54

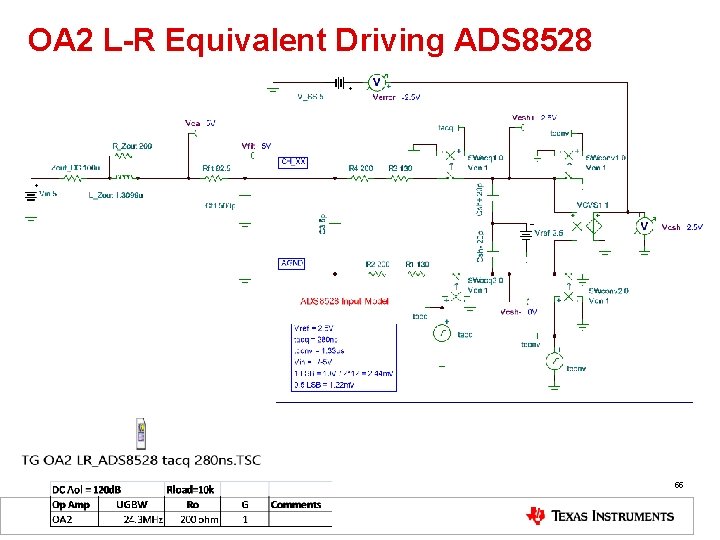

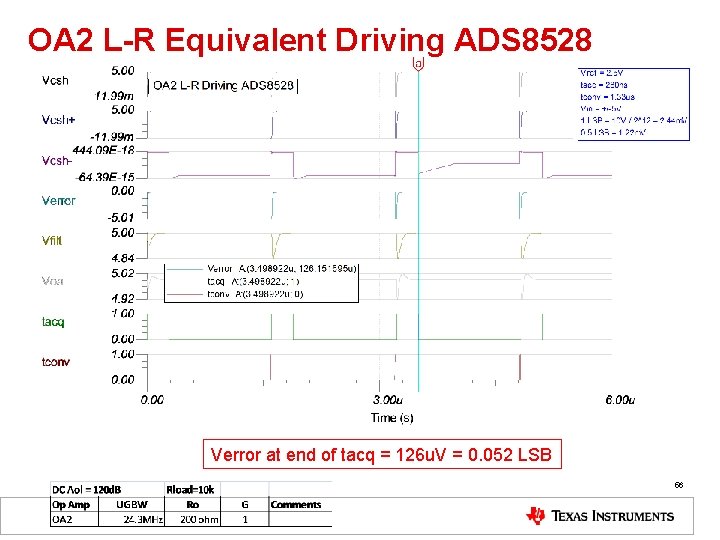

OA 2 L-R Equivalent Driving ADS 8528 55

OA 2 L-R Equivalent Driving ADS 8528 Verror at end of tacq = 126 u. V = 0. 052 LSB 56

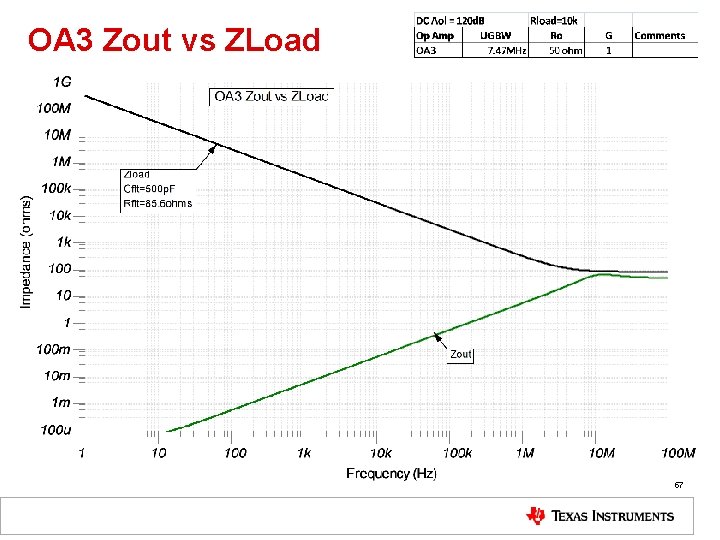

OA 3 Zout vs ZLoad 57

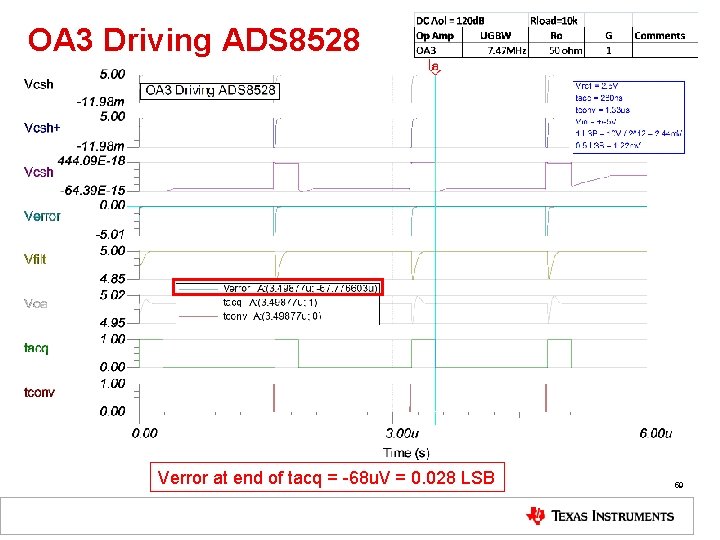

OA 3 Driving ADS 8528 58

OA 3 Driving ADS 8528 Verror at end of tacq = -68 u. V = 0. 028 LSB 59

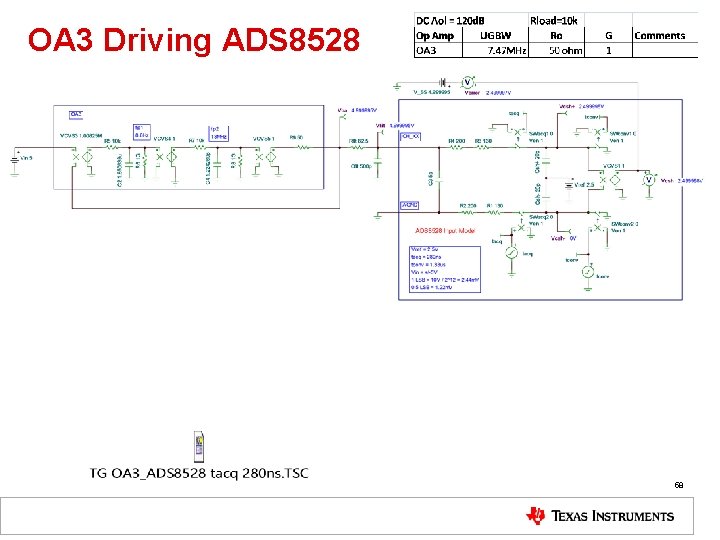

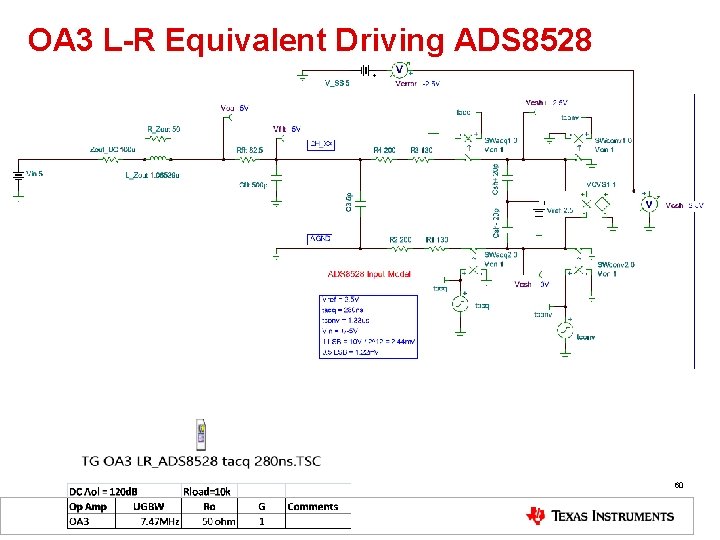

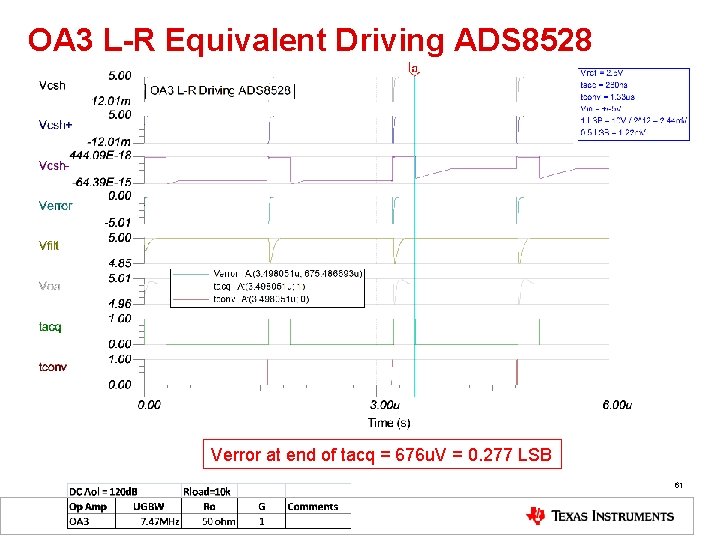

OA 3 L-R Equivalent Driving ADS 8528 60

OA 3 L-R Equivalent Driving ADS 8528 Verror at end of tacq = 676 u. V = 0. 277 LSB 61

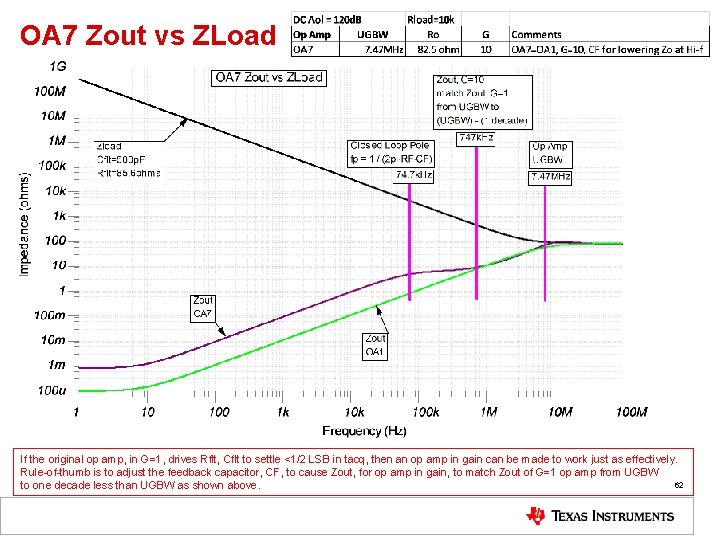

OA 7 Zout vs ZLoad If the original op amp, in G=1, drives Rflt, Cflt to settle <1/2 LSB in tacq, then an op amp in gain can be made to work just as effectively. Rule-of-thumb is to adjust the feedback capacitor, CF, to cause Zout, for op amp in gain, to match Zout of G=1 op amp from UGBW 62 to one decade less than UGBW as shown above.

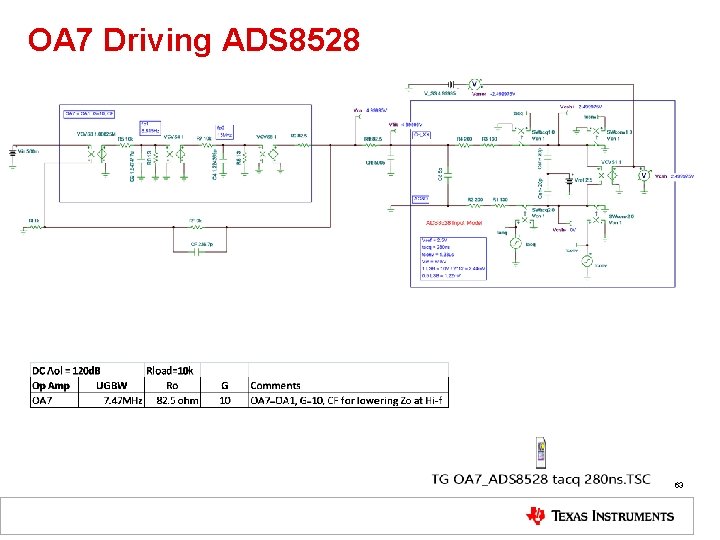

OA 7 Driving ADS 8528 63

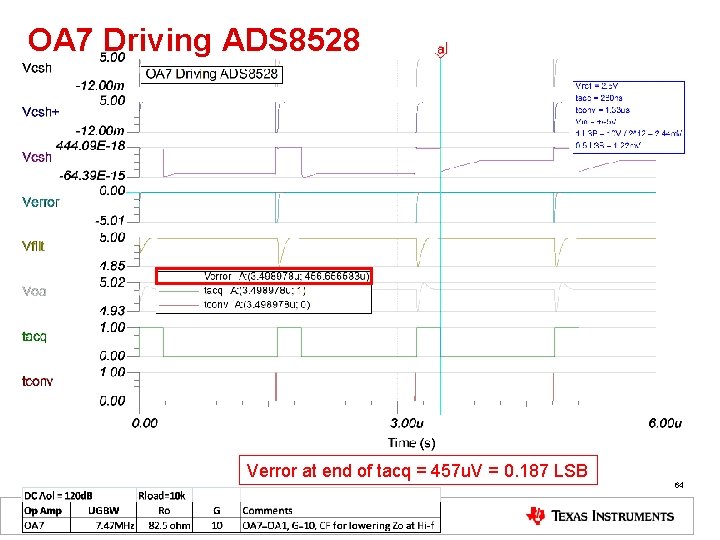

OA 7 Driving ADS 8528 Verror at end of tacq = 457 u. V = 0. 187 LSB 64

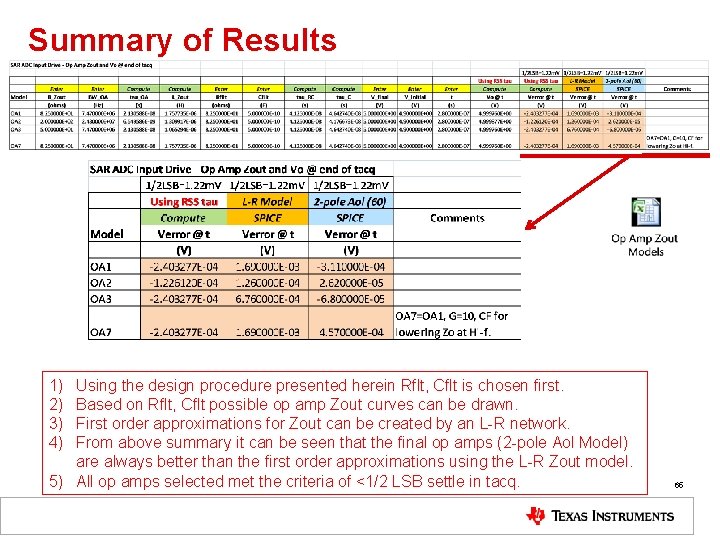

Summary of Results 1) 2) 3) 4) Using the design procedure presented herein Rflt, Cflt is chosen first. Based on Rflt, Cflt possible op amp Zout curves can be drawn. First order approximations for Zout can be created by an L-R network. From above summary it can be seen that the final op amps (2 -pole Aol Model) are always better than the first order approximations using the L-R Zout model. 5) All op amps selected met the criteria of <1/2 LSB settle in tacq. 65

Appendix 1 Modeling CDAC SAR Input A case study of ADS 8320 66

Background Information 67

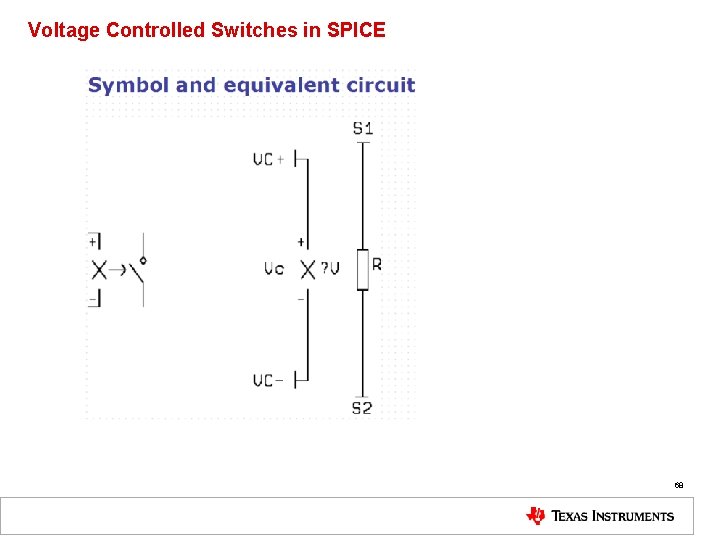

Voltage Controlled Switches in SPICE 68

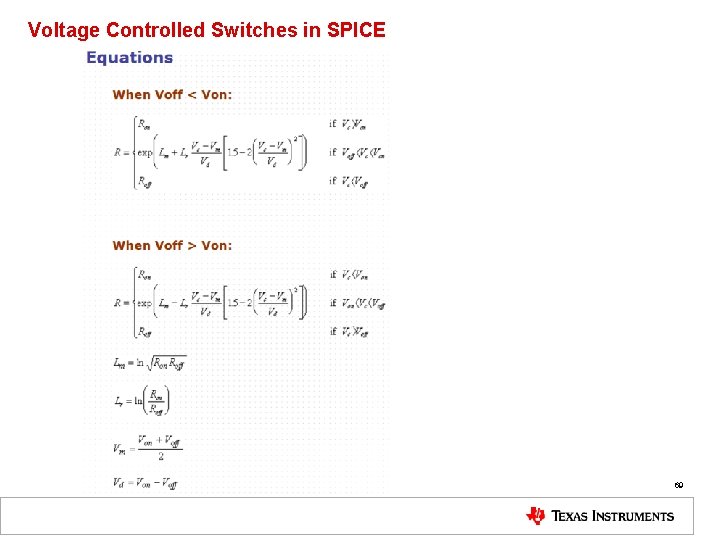

Voltage Controlled Switches in SPICE 69

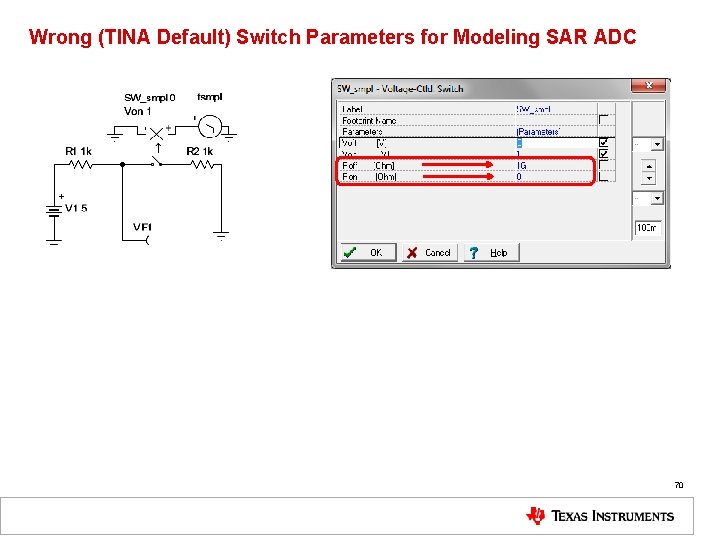

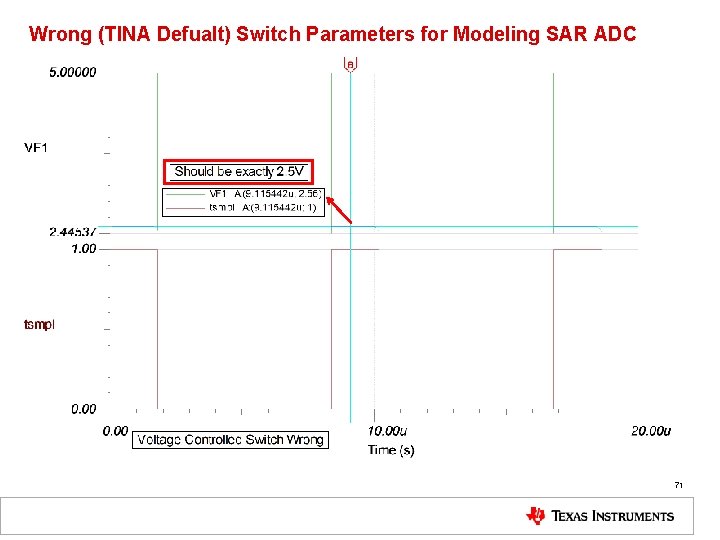

Wrong (TINA Default) Switch Parameters for Modeling SAR ADC 70

Wrong (TINA Defualt) Switch Parameters for Modeling SAR ADC 71

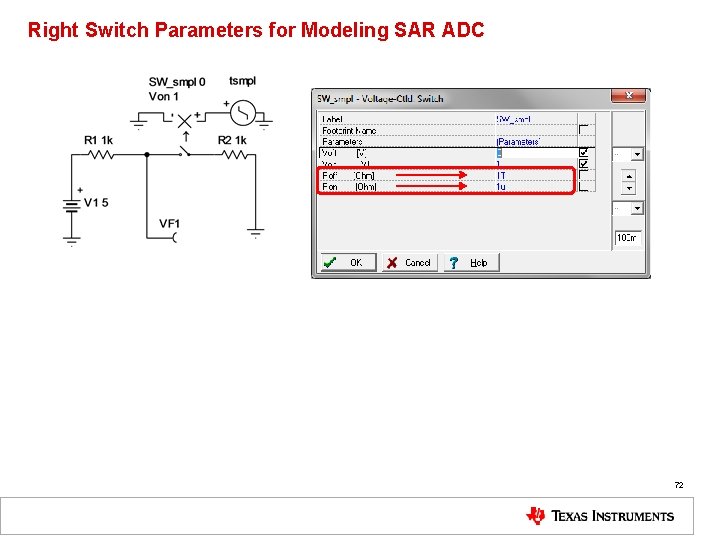

Right Switch Parameters for Modeling SAR ADC 72

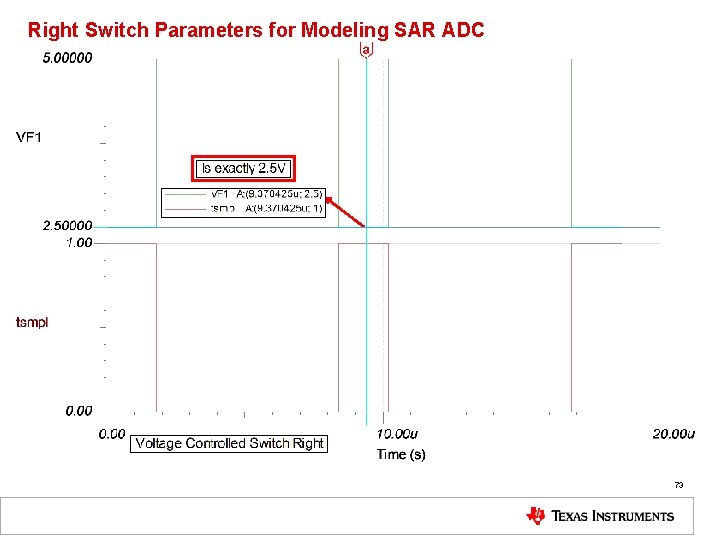

Right Switch Parameters for Modeling SAR ADC 73

Modeling the SAR Input 74

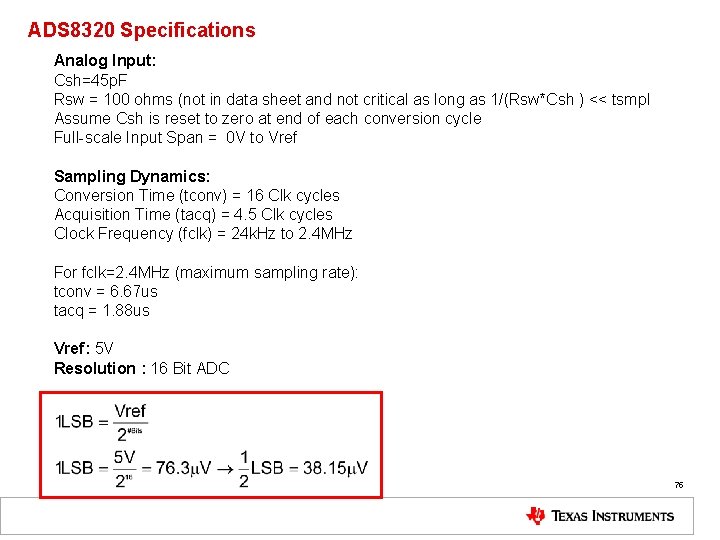

ADS 8320 Specifications Analog Input: Csh=45 p. F Rsw = 100 ohms (not in data sheet and not critical as long as 1/(Rsw*Csh ) << tsmpl Assume Csh is reset to zero at end of each conversion cycle Full-scale Input Span = 0 V to Vref Sampling Dynamics: Conversion Time (tconv) = 16 Clk cycles Acquisition Time (tacq) = 4. 5 Clk cycles Clock Frequency (fclk) = 24 k. Hz to 2. 4 MHz For fclk=2. 4 MHz (maximum sampling rate): tconv = 6. 67 us tacq = 1. 88 us Vref: 5 V Resolution : 16 Bit ADC 75

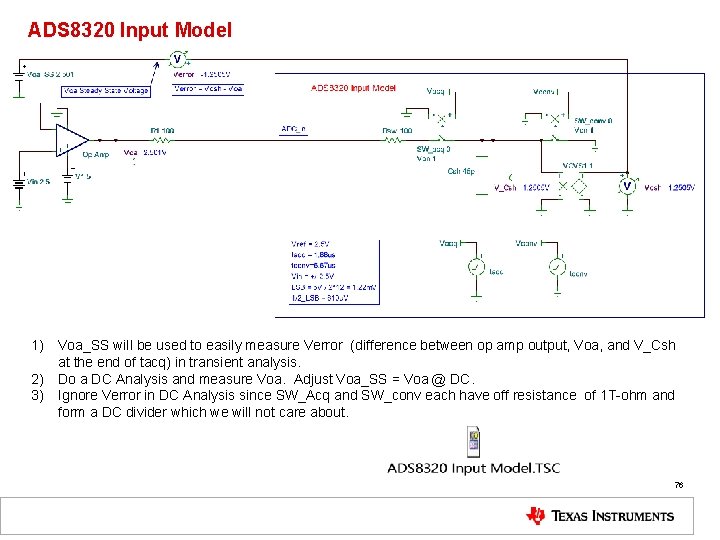

ADS 8320 Input Model 1) Voa_SS will be used to easily measure Verror (difference between op amp output, Voa, and V_Csh at the end of tacq) in transient analysis. 2) Do a DC Analysis and measure Voa. Adjust Voa_SS = Voa @ DC. 3) Ignore Verror in DC Analysis since SW_Acq and SW_conv each have off resistance of 1 T-ohm and form a DC divider which we will not care about. 76

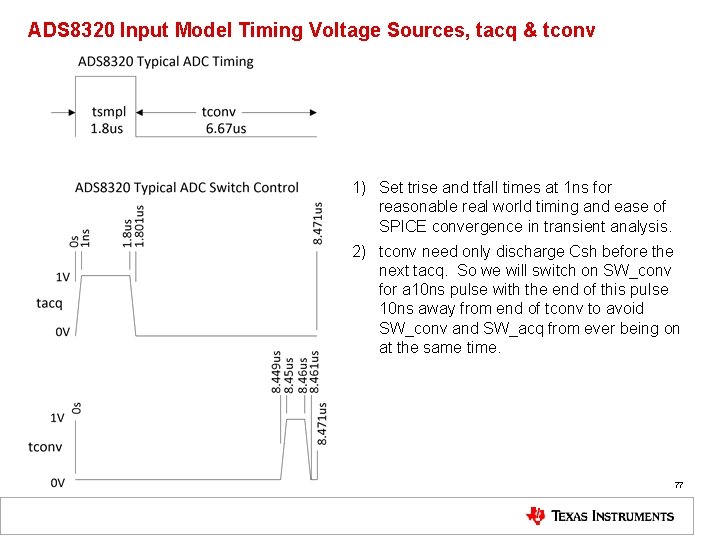

ADS 8320 Input Model Timing Voltage Sources, tacq & tconv 1) Set trise and tfall times at 1 ns for reasonable real world timing and ease of SPICE convergence in transient analysis. 2) tconv need only discharge Csh before the next tacq. So we will switch on SW_conv for a 10 ns pulse with the end of this pulse 10 ns away from end of tconv to avoid SW_conv and SW_acq from ever being on at the same time. 77

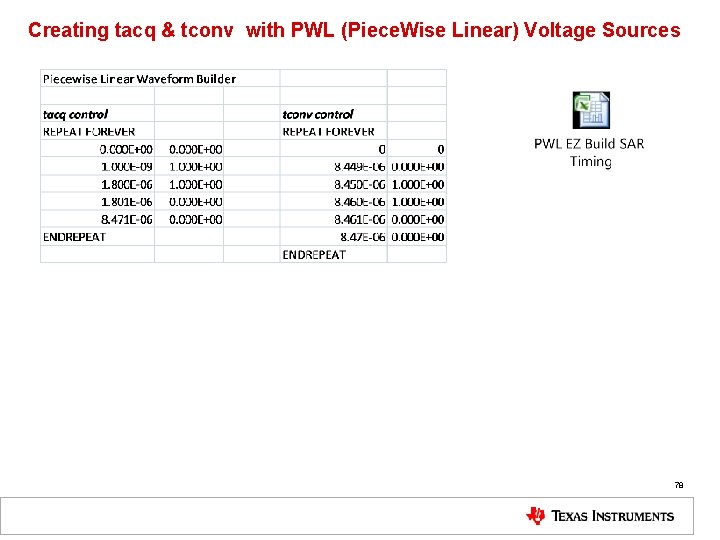

Creating tacq & tconv with PWL (Piece. Wise Linear) Voltage Sources 78

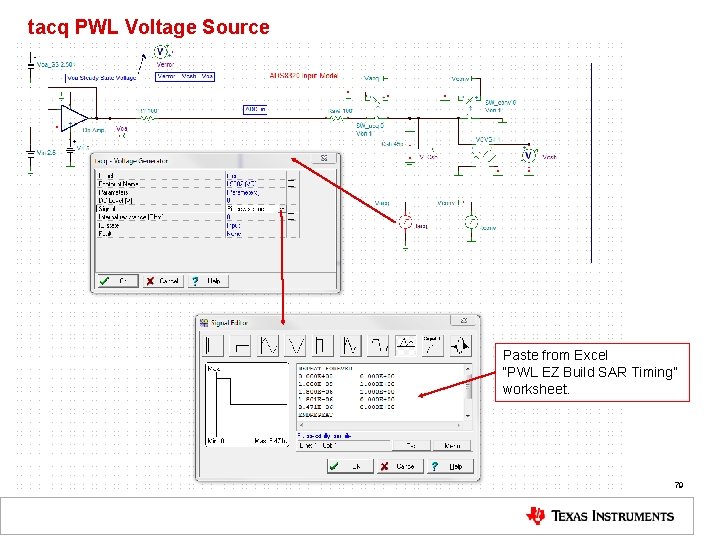

tacq PWL Voltage Source Paste from Excel “PWL EZ Build SAR Timing” worksheet. 79

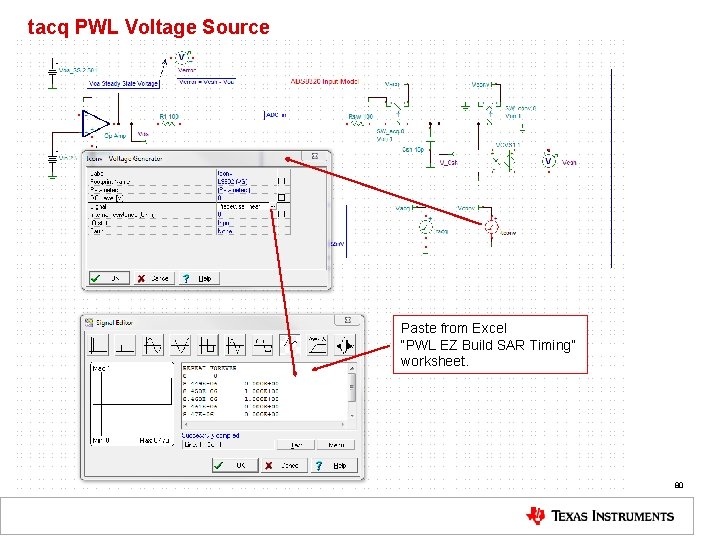

tacq PWL Voltage Source Paste from Excel “PWL EZ Build SAR Timing” worksheet. 80

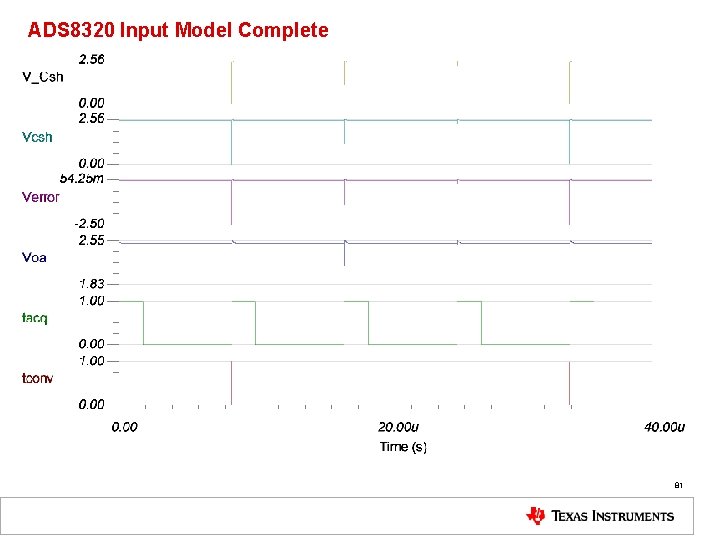

ADS 8320 Input Model Complete 81

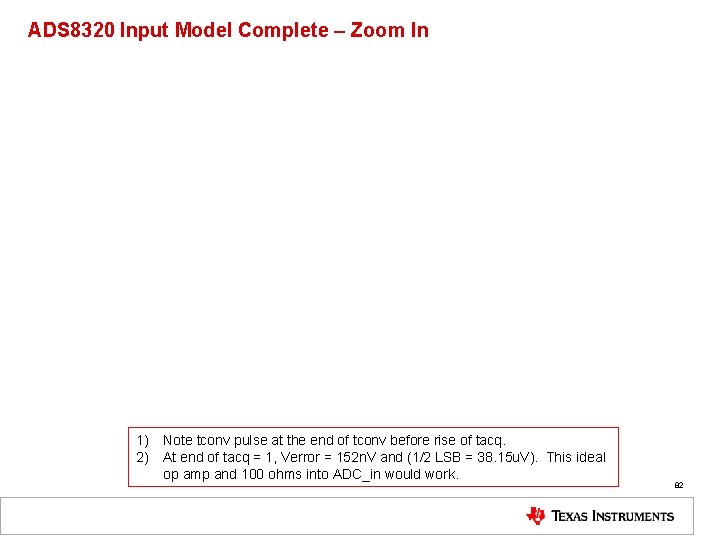

ADS 8320 Input Model Complete – Zoom In 1) Note tconv pulse at the end of tconv before rise of tacq. 2) At end of tacq = 1, Verror = 152 n. V and (1/2 LSB = 38. 15 u. V). This ideal op amp and 100 ohms into ADC_in would work. 82

Input Drive of SAR ADC 83

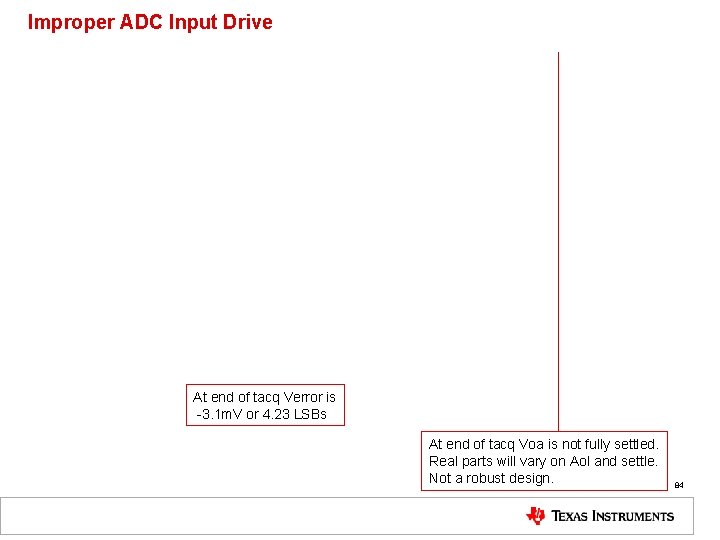

Improper ADC Input Drive At end of tacq Verror is -3. 1 m. V or 4. 23 LSBs At end of tacq Voa is not fully settled. Real parts will vary on Aol and settle. Not a robust design. 84

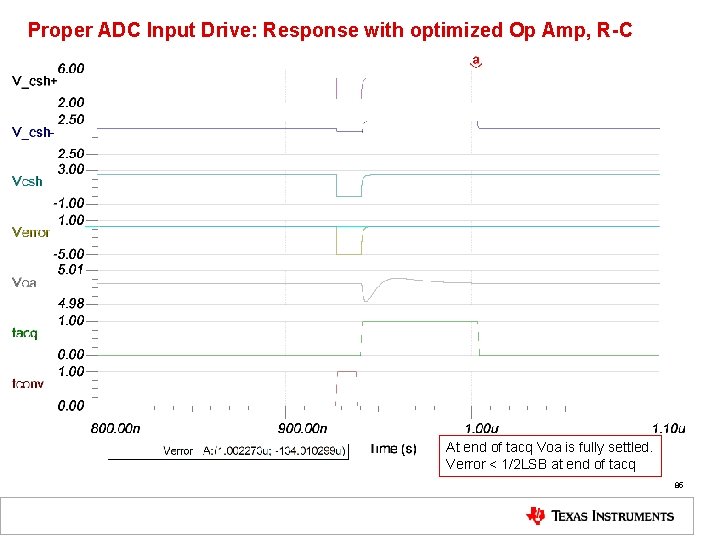

Proper ADC Input Drive: Response with optimized Op Amp, R-C At end of tacq Voa is fully settled. Verror < 1/2 LSB at end of tacq 85

Appendix 2 Op Amp Output Impedance Open Loop (ZO) & Closed Loop (ZOUT) 86

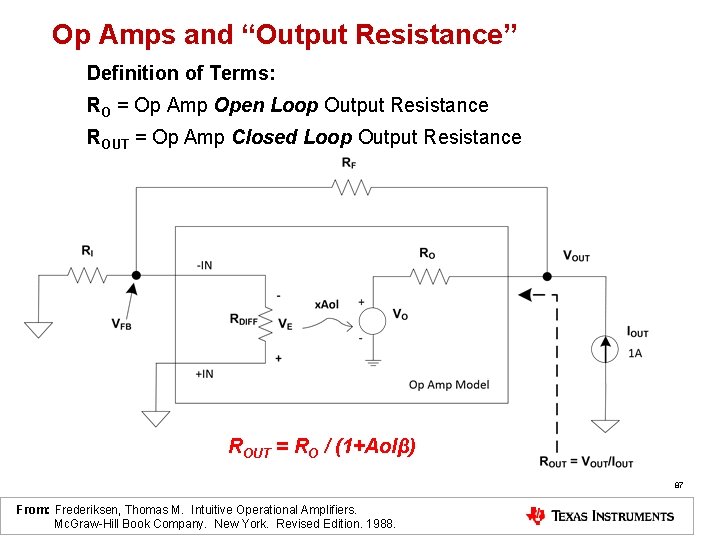

Op Amps and “Output Resistance” Definition of Terms: RO = Op Amp Open Loop Output Resistance ROUT = Op Amp Closed Loop Output Resistance ROUT = RO / (1+Aolβ) 87 From: Frederiksen, Thomas M. Intuitive Operational Amplifiers. Mc. Graw-Hill Book Company. New York. Revised Edition. 1988.

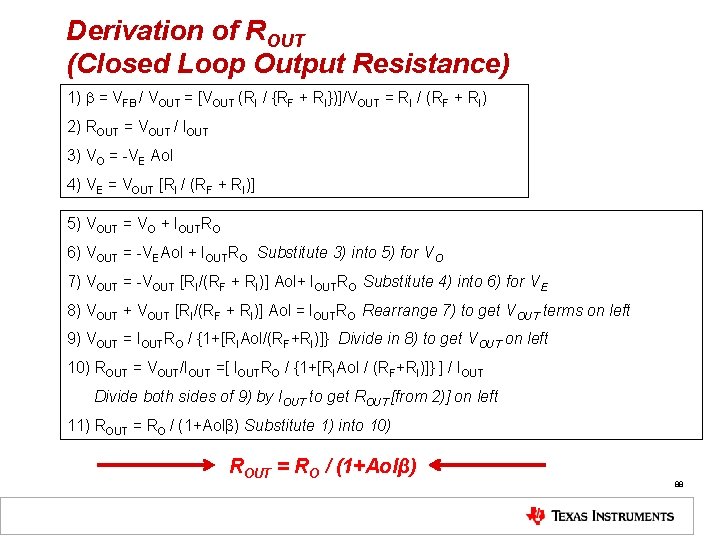

Derivation of ROUT (Closed Loop Output Resistance) 1) b = VFB / VOUT = [VOUT (RI / {RF + RI})]/VOUT = RI / (RF + RI) 2) ROUT = VOUT / IOUT 3) VO = -VE Aol 4) VE = VOUT [RI / (RF + RI)] 5) VOUT = VO + IOUTRO 6) VOUT = -VEAol + IOUTRO Substitute 3) into 5) for VO 7) VOUT = -VOUT [RI/(RF + RI)] Aol+ IOUTRO Substitute 4) into 6) for VE 8) VOUT + VOUT [RI/(RF + RI)] Aol = IOUTRO Rearrange 7) to get VOUT terms on left 9) VOUT = IOUTRO / {1+[RIAol/(RF+RI)]} Divide in 8) to get VOUT on left 10) ROUT = VOUT/IOUT =[ IOUTRO / {1+[RIAol / (RF+RI)]} ] / IOUT Divide both sides of 9) by IOUT to get ROUT [from 2)] on left 11) ROUT = RO / (1+Aolβ) Substitute 1) into 10) ROUT = RO / (1+Aolβ) 88

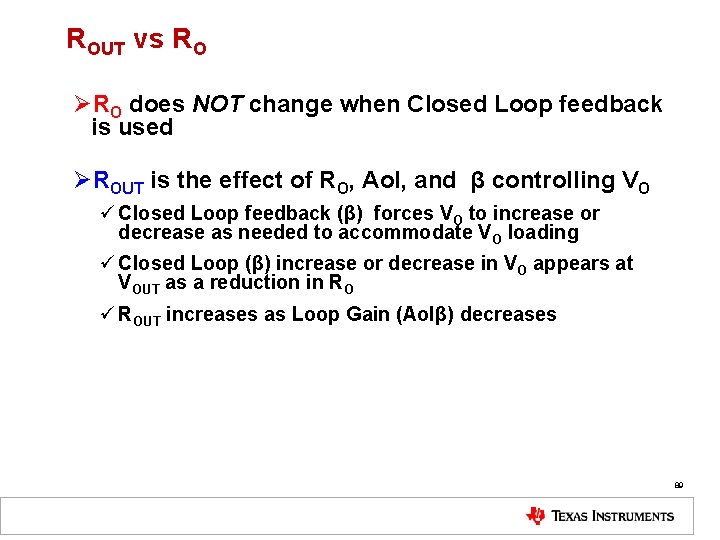

ROUT vs RO ØRO does NOT change when Closed Loop feedback is used ØROUT is the effect of RO, Aol, and β controlling VO ü Closed Loop feedback (β) forces VO to increase or decrease as needed to accommodate VO loading ü Closed Loop (β) increase or decrease in VO appears at VOUT as a reduction in RO ü ROUT increases as Loop Gain (Aolβ) decreases 89

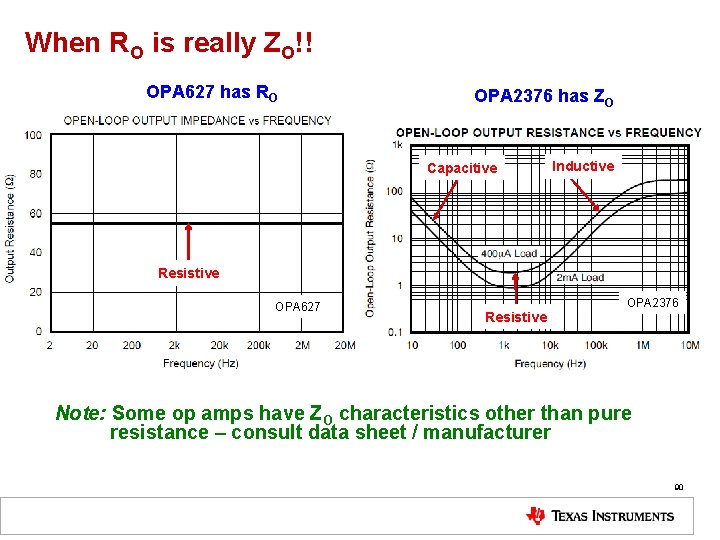

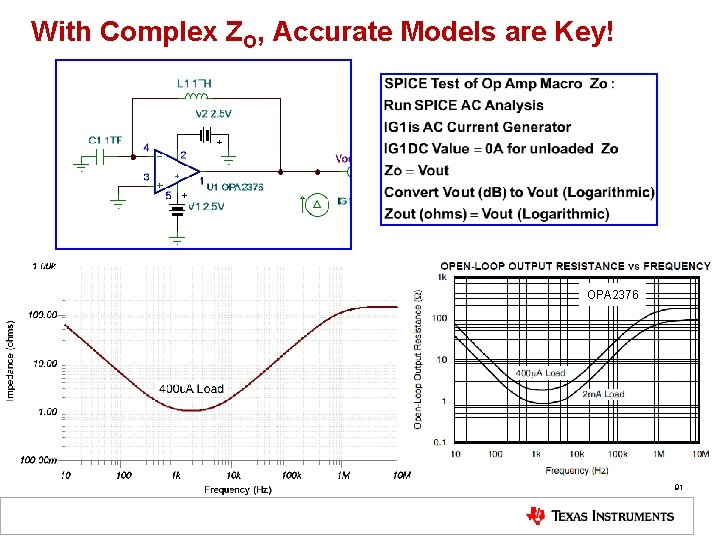

When RO is really ZO!! OPA 627 has RO OPA 2376 has ZO Capacitive Inductive Resistive OPA 627 Resistive OPA 2376 Note: Some op amps have ZO characteristics other than pure resistance – consult data sheet / manufacturer 90

With Complex ZO, Accurate Models are Key! OPA 2376 91

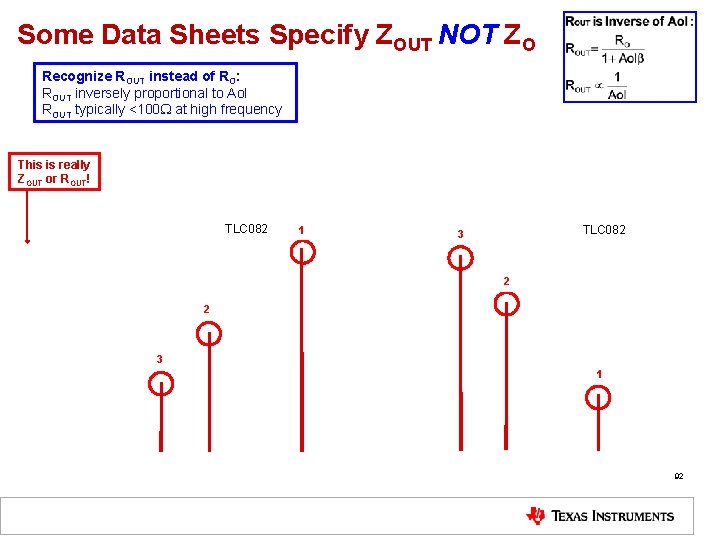

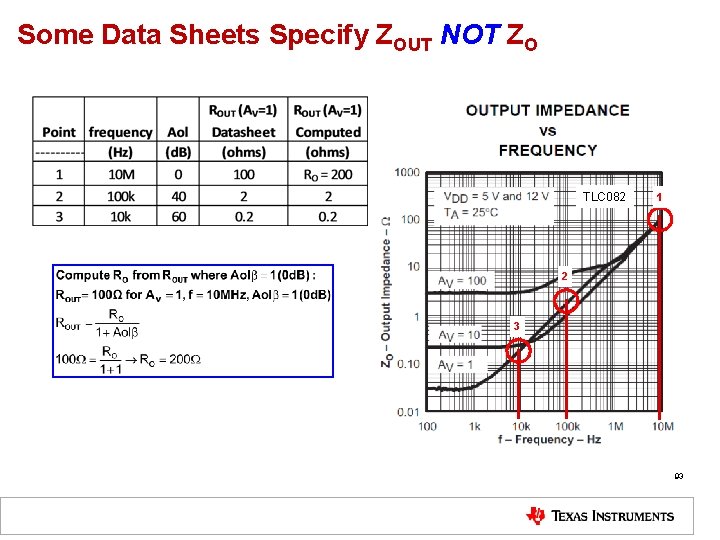

Some Data Sheets Specify ZOUT NOT ZO Recognize ROUT instead of RO: ROUT inversely proportional to Aol ROUT typically <100 W at high frequency This is really ZOUT or ROUT! TLC 082 1 TLC 082 3 2 2 3 1 92

Some Data Sheets Specify ZOUT NOT ZO TLC 082 1 2 3 93

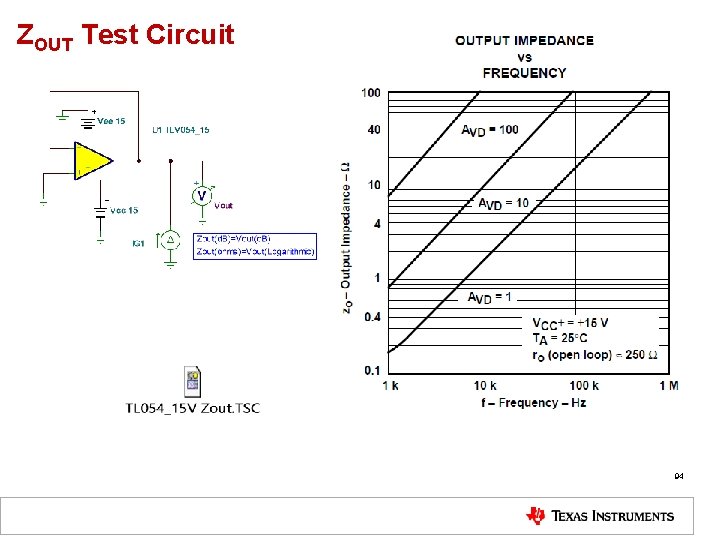

ZOUT Test Circuit 94

ZOUT Test Circuit 95

Op Amp Stability Reference For detailed, definition-by-example of 10 different ways to stabilize op amps driving capacitive loads, and additional technical information on solving op amp stability problems, visit the Texas Instruments E 2 E Forum at: http: //e 2 e. ti. com/support/amplifiers/precision_amplifiers/w/design_notes/2645. solving-opamp-stability-issues. aspx Download Part 1, Part 2, Part 3, and Part 4. For more in-depth learning about op amps and op amp stability look at TI Precision Labs at: www. ti. com/precisionlabs Analog Engineer’s Pocket Reference A “must-have” for every Board/System Design Engineer Download: http: //www. ti. com/lsds/ti/amplifiers-linear/precision-amplifier-supportcommunity. page#pocketref Buy Hardcopy: https: //store. ti. com/Search. aspx? k=pocket+reference&pt=-1 All Embedded Schematics in this presentation can be run in the Free TINA_TI SPICE simulator available at: http: //www. ti. com/tool/tina-ti 96

- Slides: 96