S 08 SH 8 SPI Serial Peripheral Interface

![Registers SPI Baud Rate Register (SPIBR) SPPR[2: 0] = SPI Baud Rate Prescale Divisor Registers SPI Baud Rate Register (SPIBR) SPPR[2: 0] = SPI Baud Rate Prescale Divisor](https://slidetodoc.com/presentation_image_h2/87bfda96538aa6e8421229e237d477f9/image-10.jpg)

- Slides: 16

S 08 SH 8 SPI Serial Peripheral Interface Vicente Gomez | Technical support Engineer JUN. 08. 2015 TM Confidential and Proprietary

Agenda Overview 2. Block diagram 3. Registers 4. SCI Hands-On 1. TM Confidential and Proprietary 1

SPI Overview TM Confidential and Proprietary 2

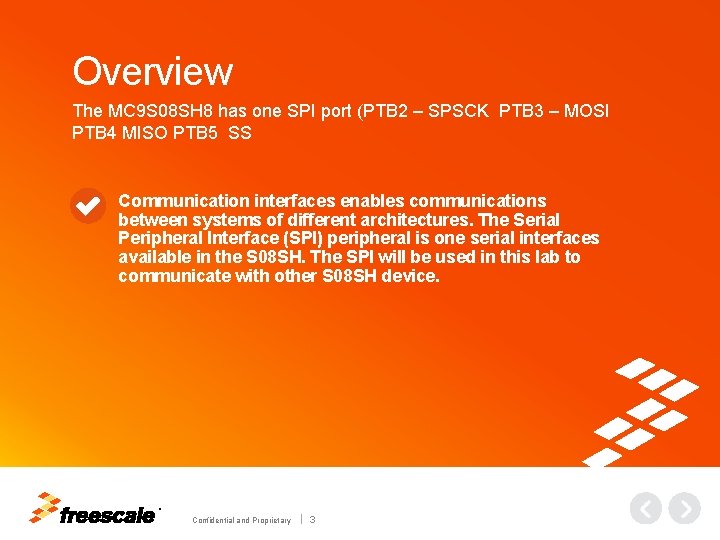

Overview The MC 9 S 08 SH 8 has one SPI port (PTB 2 – SPSCK PTB 3 – MOSI PTB 4 MISO PTB 5 SS Communication interfaces enables communications between systems of different architectures. The Serial Peripheral Interface (SPI) peripheral is one serial interfaces available in the S 08 SH. The SPI will be used in this lab to communicate with other S 08 SH device. TM Confidential and Proprietary 3

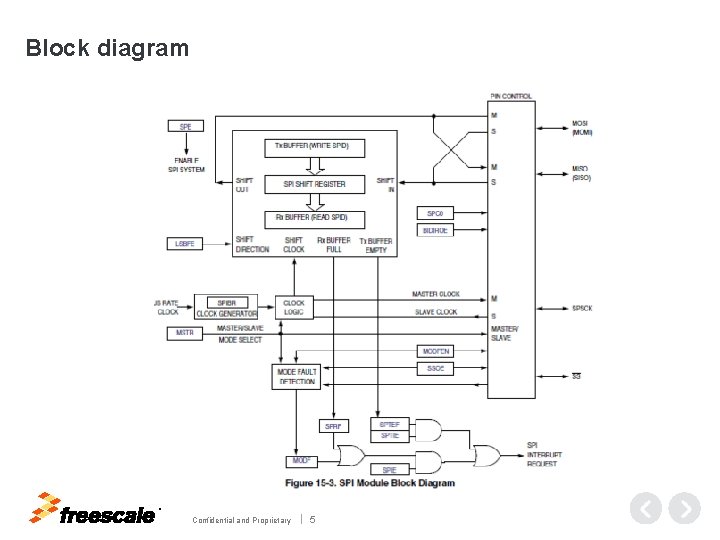

Block Diagram TM Confidential and Proprietary 4

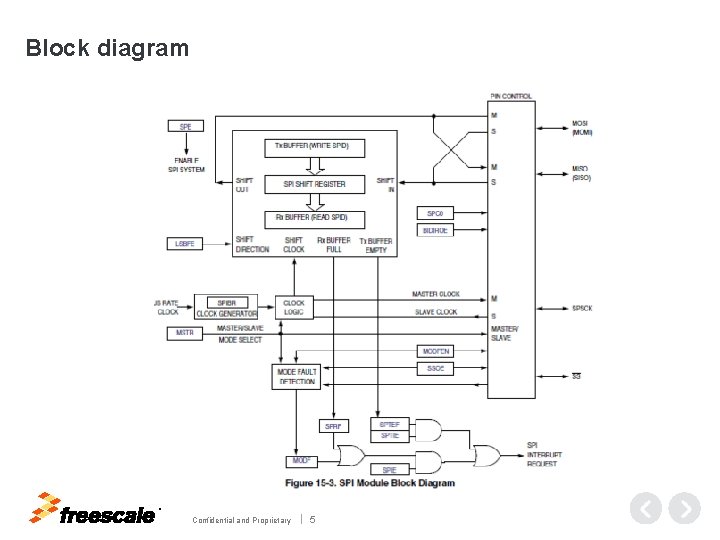

Block diagram TM Confidential and Proprietary 5

Registers TM Confidential and Proprietary 6

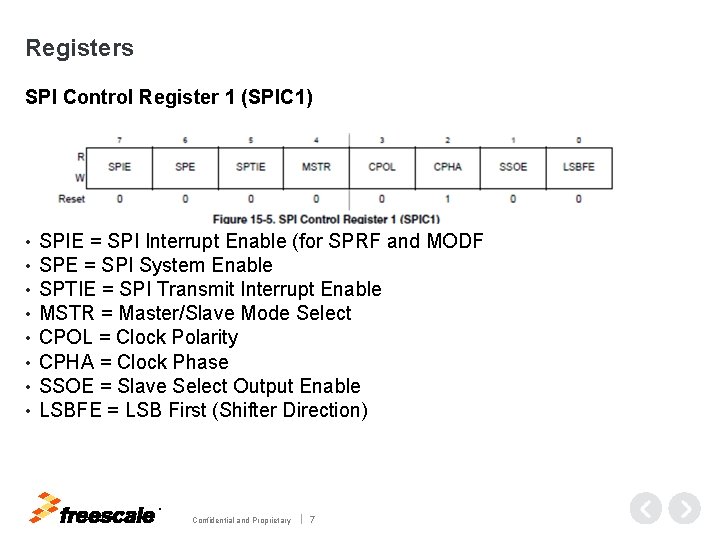

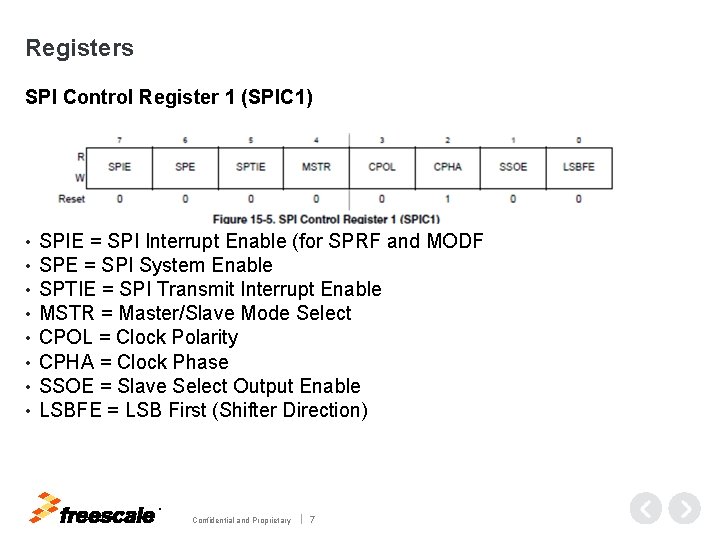

Registers SPI Control Register 1 (SPIC 1) • • SPIE = SPI Interrupt Enable (for SPRF and MODF SPE = SPI System Enable SPTIE = SPI Transmit Interrupt Enable MSTR = Master/Slave Mode Select CPOL = Clock Polarity CPHA = Clock Phase SSOE = Slave Select Output Enable LSBFE = LSB First (Shifter Direction) TM Confidential and Proprietary 7

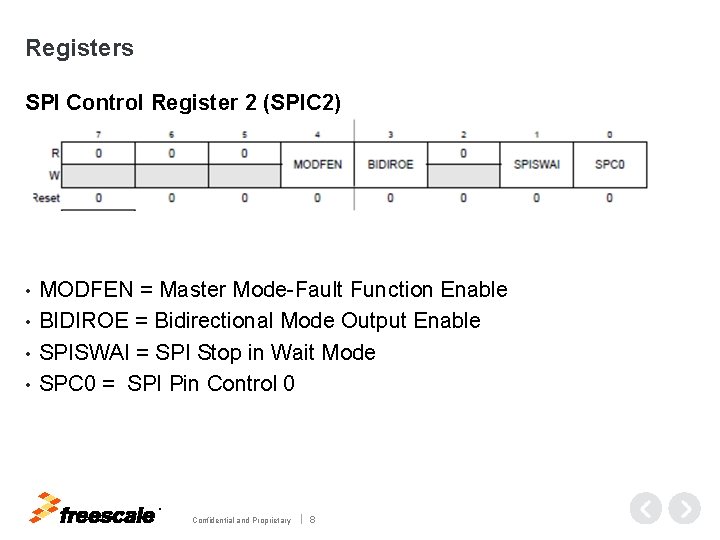

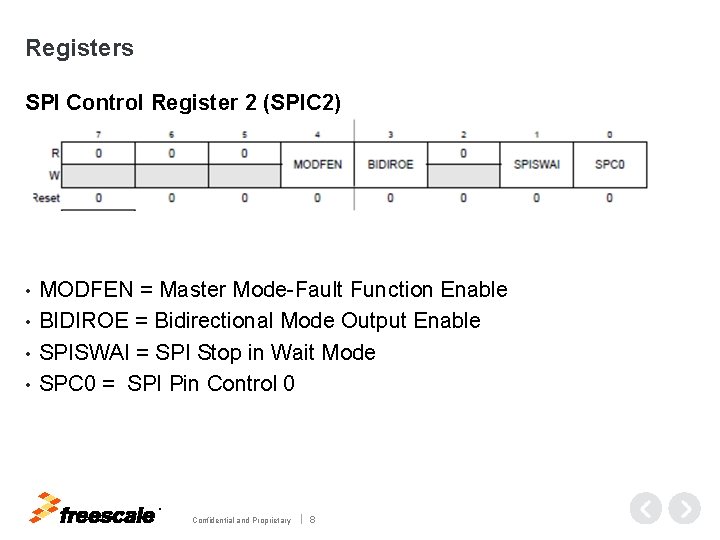

Registers SPI Control Register 2 (SPIC 2) MODFEN = Master Mode-Fault Function Enable • BIDIROE = Bidirectional Mode Output Enable • SPISWAI = SPI Stop in Wait Mode • SPC 0 = SPI Pin Control 0 • TM Confidential and Proprietary 8

![Registers SPI Baud Rate Register SPIBR SPPR2 0 SPI Baud Rate Prescale Divisor Registers SPI Baud Rate Register (SPIBR) SPPR[2: 0] = SPI Baud Rate Prescale Divisor](https://slidetodoc.com/presentation_image_h2/87bfda96538aa6e8421229e237d477f9/image-10.jpg)

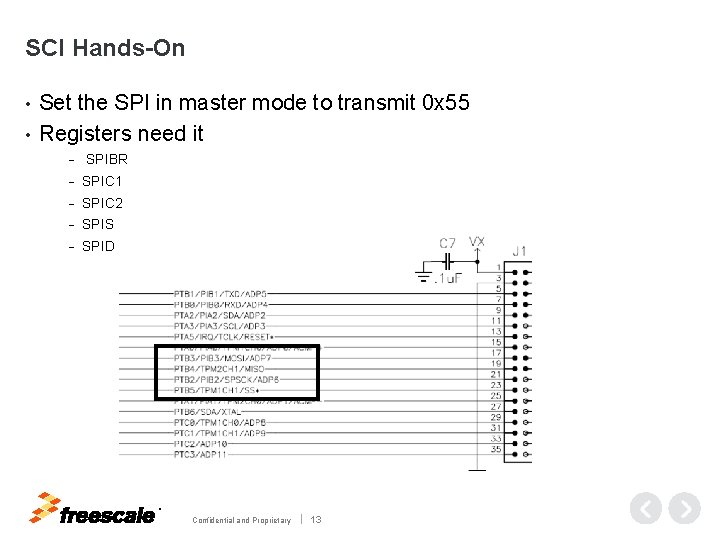

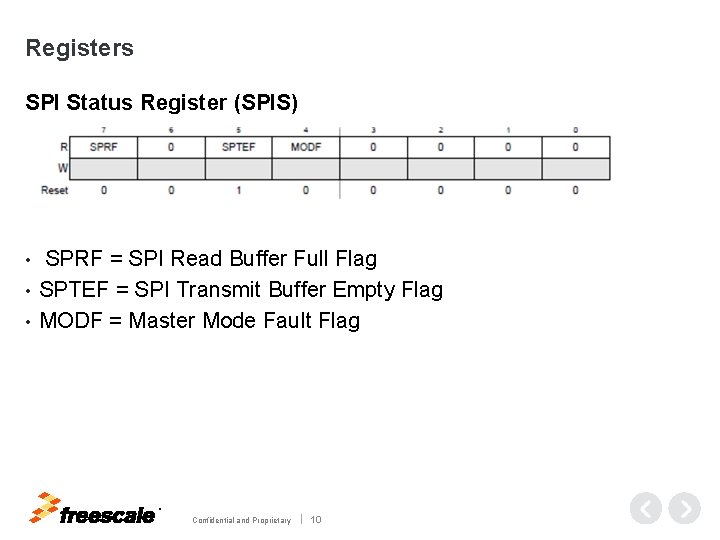

Registers SPI Baud Rate Register (SPIBR) SPPR[2: 0] = SPI Baud Rate Prescale Divisor • SPR[2: 0] = SPI Baud Rate Divisor • TM Confidential and Proprietary 9

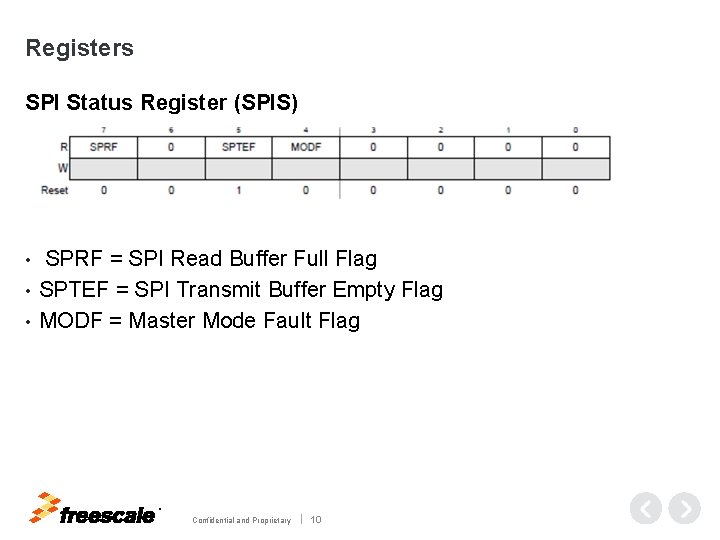

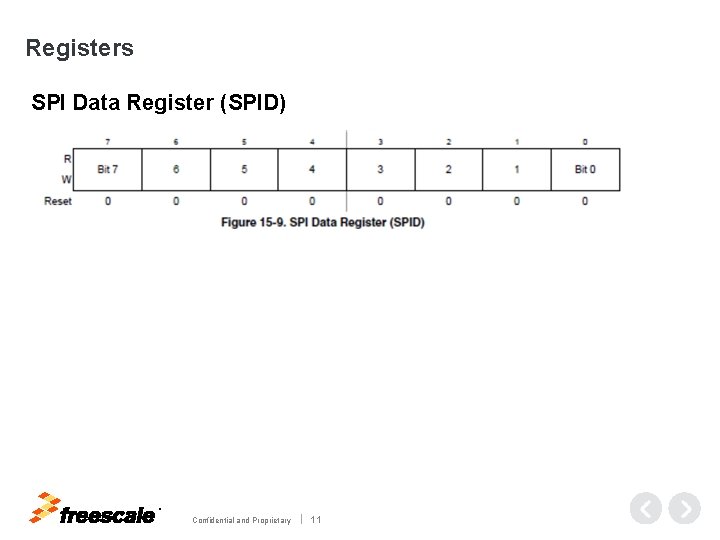

Registers SPI Status Register (SPIS) SPRF = SPI Read Buffer Full Flag • SPTEF = SPI Transmit Buffer Empty Flag • MODF = Master Mode Fault Flag • TM Confidential and Proprietary 10

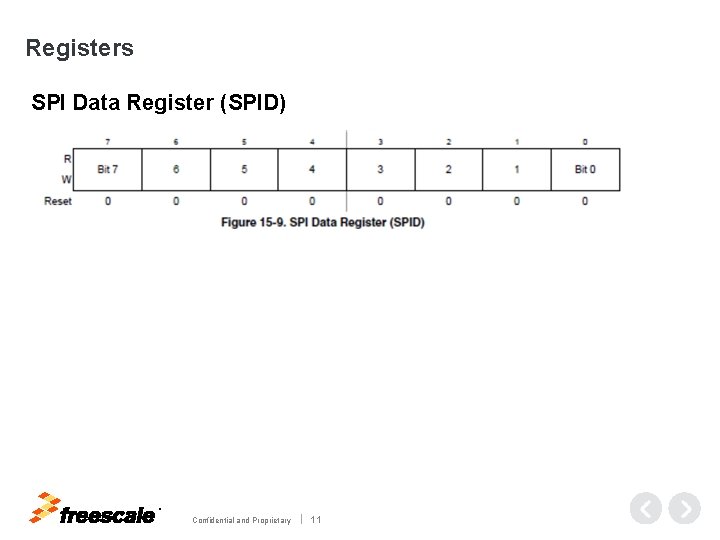

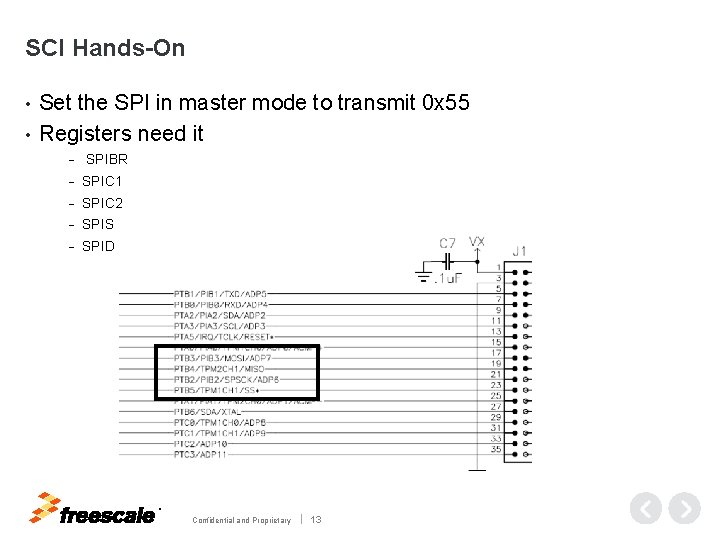

Registers SPI Data Register (SPID) TM Confidential and Proprietary 11

SPI Hands-On TM Confidential and Proprietary 12

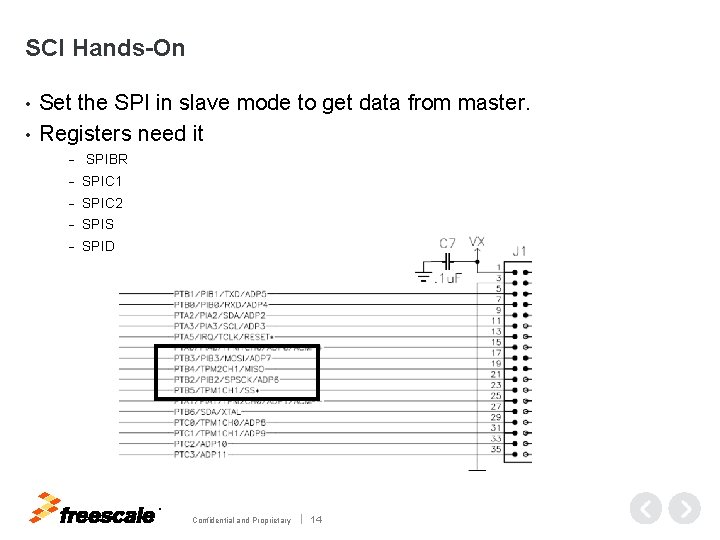

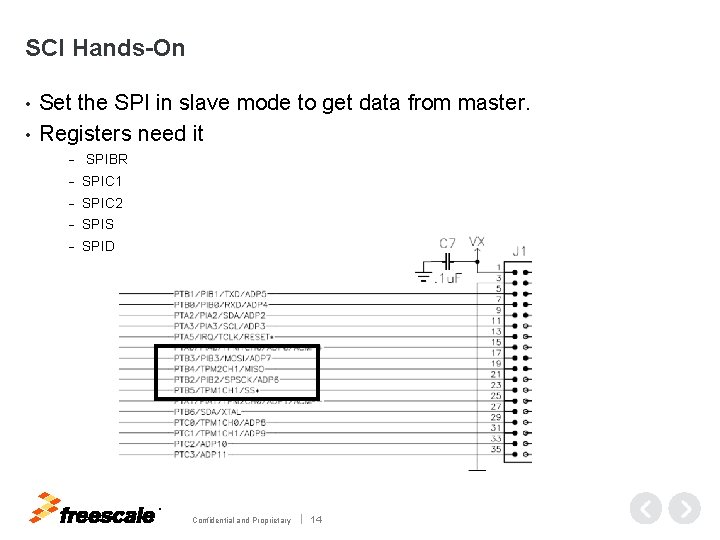

SCI Hands-On Set the SPI in master mode to transmit 0 x 55 • Registers need it • − SPIBR − SPIC 1 − SPIC 2 − SPIS − SPID TM Confidential and Proprietary 13

SCI Hands-On Set the SPI in slave mode to get data from master. • Registers need it • − SPIBR − SPIC 1 − SPIC 2 − SPIS − SPID TM Confidential and Proprietary 14

TM www. Freescale. com © 2014 Freescale Semiconductor, Inc. | Confidential and Proprietary