RPC Frontend Readout development Luca Pizzimento Salvatore Bruno

RPC Front-end & Read-out development Luca Pizzimento, Salvatore Bruno, Elio Alunno Camelia Riunione gruppo ATLAS Roma 2 19/12/2017

Summary Development of the front-end in Si-Ge technology Ø The new FE in development Ø October Testbeam FE system & FE final design Ø Work in progress Simulation and test of a TDC with 100 ps resolution Ø Ø Atlas TDC description Functions of the blocks Results Future Step Optimization of RPCs read-out panel with electromagnetic simulation Ø Different type of read-out panel simulation Ø Optimization Ø State of the art

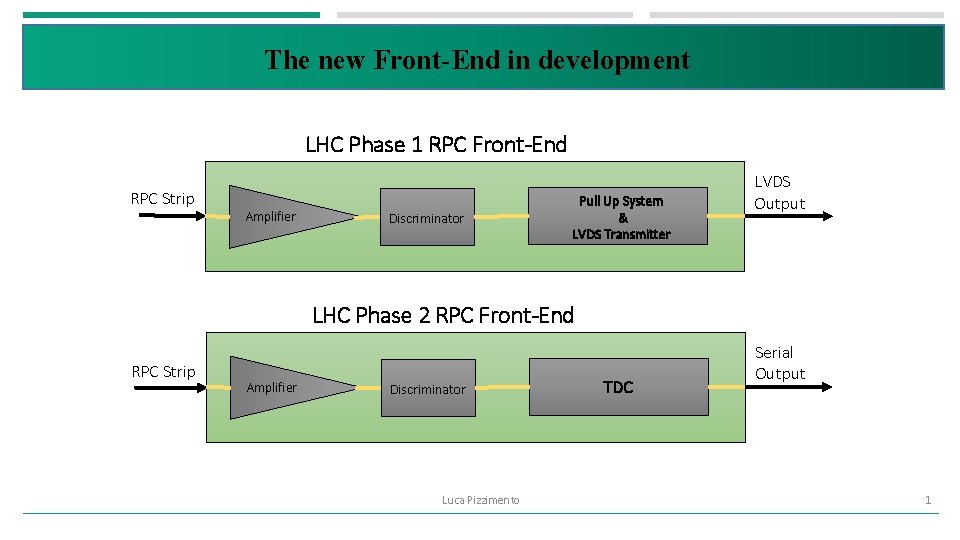

The new Front-End in development LHC Phase 1 RPC Front-End RPC Strip Amplifier Discriminator Pull Up System & LVDS Transmitter LVDS Output LHC Phase 2 RPC Front-End RPC Strip Amplifier Discriminator Luca Pizzimento TDC Serial Output 1

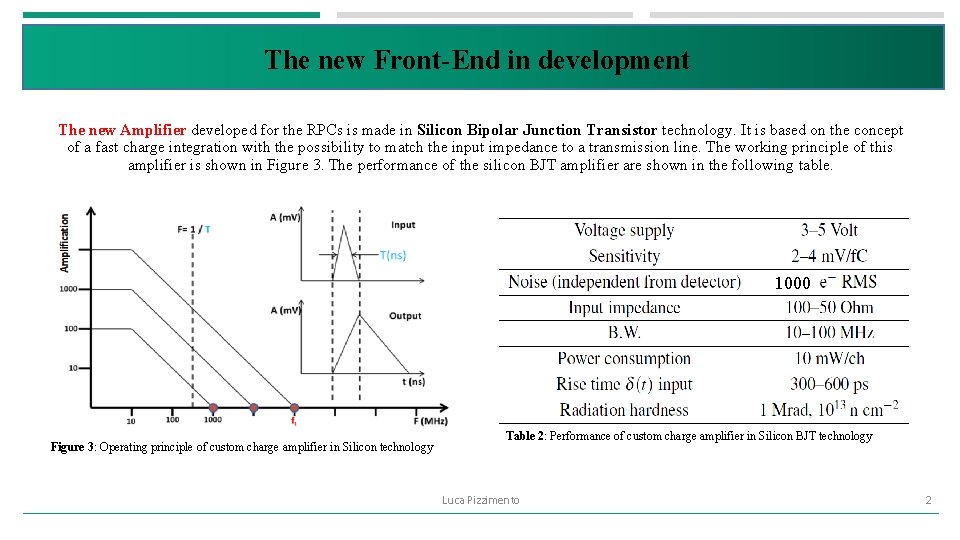

The new Front-End in development The new Amplifier developed for the RPCs is made in Silicon Bipolar Junction Transistor technology. It is based on the concept of a fast charge integration with the possibility to match the input impedance to a transmission line. The working principle of this amplifier is shown in Figure 3. The performance of the silicon BJT amplifier are shown in the following table. 1000 Figure 3: Operating principle of custom charge amplifier in Silicon technology Table 2: Performance of custom charge amplifier in Silicon BJT technology Luca Pizzimento 2

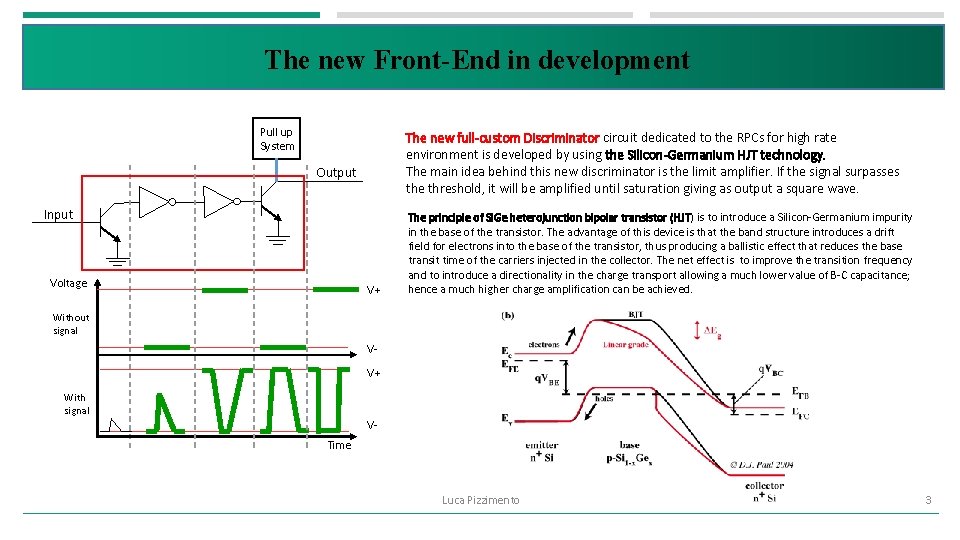

The new Front-End in development Pull up System The new full-custom Discriminator circuit dedicated to the RPCs for high rate environment is developed by using the Silicon-Germanium HJT technology. The main idea behind this new discriminator is the limit amplifier. If the signal surpasses the threshold, it will be amplified until saturation giving as output a square wave. Output Input Voltage V+ The principle of Si. Ge heterojunction bipolar transistor (HJT) is to introduce a Silicon-Germanium impurity in the base of the transistor. The advantage of this device is that the band structure introduces a drift field for electrons into the base of the transistor, thus producing a ballistic effect that reduces the base transit time of the carriers injected in the collector. The net effect is to improve the transition frequency and to introduce a directionality in the charge transport allowing a much lower value of B-C capacitance; hence a much higher charge amplification can be achieved. Without signal VV+ With signal VTime Luca Pizzimento 3

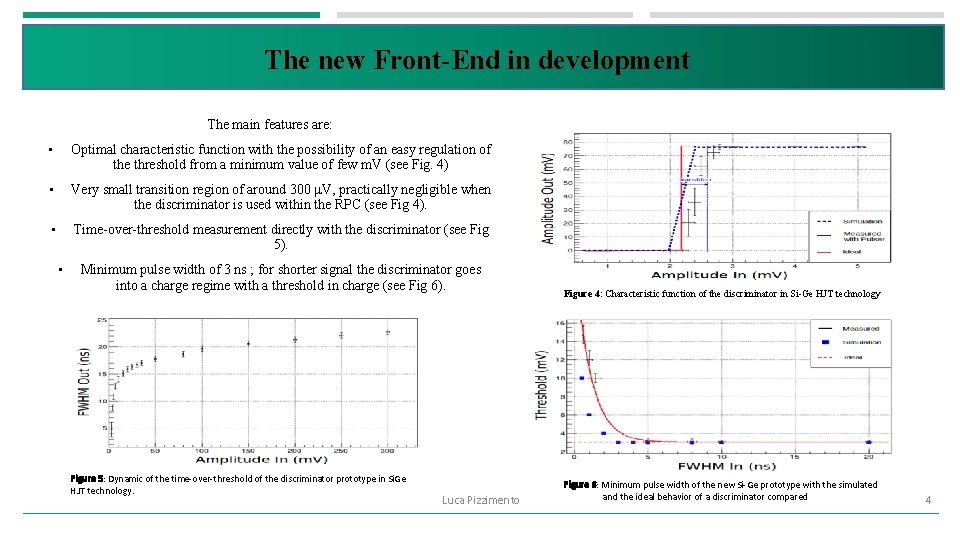

The new Front-End in development The main features are: • Optimal characteristic function with the possibility of an easy regulation of the threshold from a minimum value of few m. V (see Fig. 4) • Very small transition region of around 300 μV, practically negligible when the discriminator is used within the RPC (see Fig 4). • Time-over-threshold measurement directly with the discriminator (see Fig 5). • Minimum pulse width of 3 ns ; for shorter signal the discriminator goes into a charge regime with a threshold in charge (see Fig 6). Figure 5: Dynamic of the time-over-threshold of the discriminator prototype in Si. Ge HJT technology. Luca Pizzimento Figure 4: Characteristic function of the discriminator in Si-Ge HJT technology Figure 6: Minimum pulse width of the new Si-Ge prototype with the simulated and the ideal behavior of a discriminator compared 4

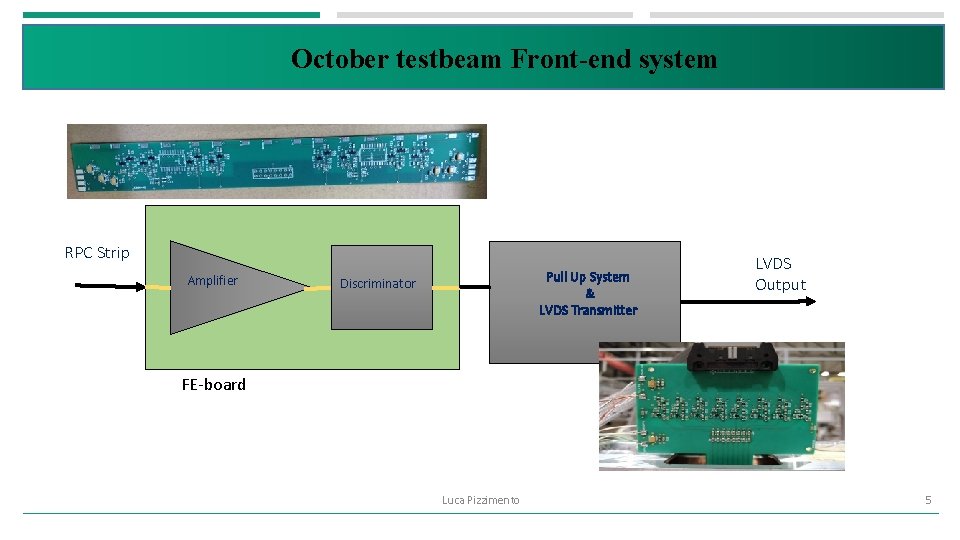

October testbeam Front-end system RPC Strip Amplifier Pull Up System & LVDS Transmitter Discriminator LVDS Output FE-board Luca Pizzimento 5

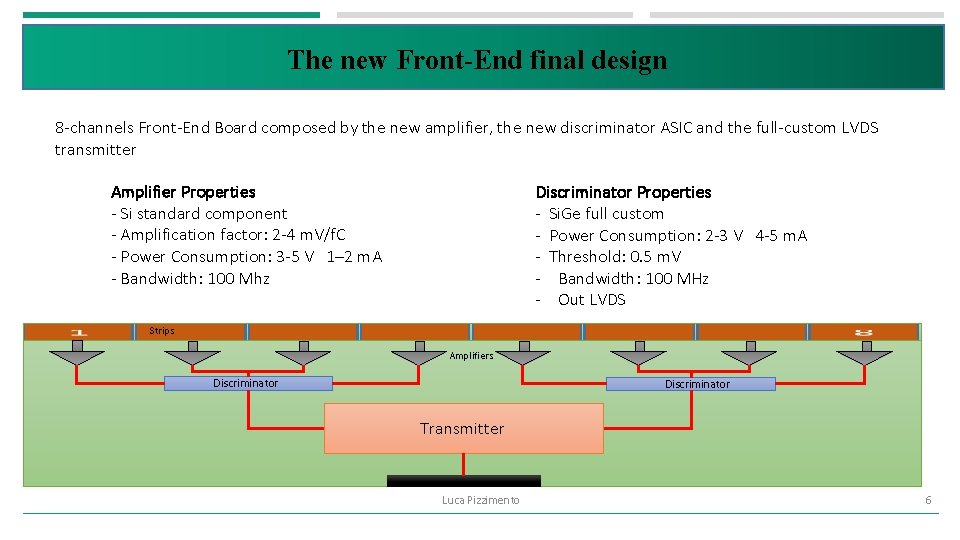

The new Front-End final design 8 -channels Front-End Board composed by the new amplifier, the new discriminator ASIC and the full-custom LVDS transmitter Amplifier Properties - Si standard component - Amplification factor: 2 -4 m. V/f. C - Power Consumption: 3 -5 V 1– 2 m. A - Bandwidth: 100 Mhz Discriminator Properties - Si. Ge full custom - Power Consumption: 2 -3 V 4 -5 m. A - Threshold: 0. 5 m. V - Bandwidth: 100 MHz - Out LVDS Strips Amplifiers Discriminator Transmitter Luca Pizzimento 6

Work in progress • Completing the analysis of the BIS 7 -8 FE prototype at H 8 • Final prototype FE board production & test • Completing the Discriminator ASICs & FE boards full order for the BIS 7 -8 production Luca Pizzimento 7

Summary Development of the front-end in Si-Ge technology Ø The new FE in development Ø October Testbeam FE system & FE final design Ø Work in progress Simulation and test of a TDC with 100 ps resolution Ø Ø Atlas TDC description Functions of the TDC blocks Results Future step Optimization of RPCs read-out panel with electromagnetic simulation Ø Different type of read-out panel simulation Ø Optimization Ø State of the art

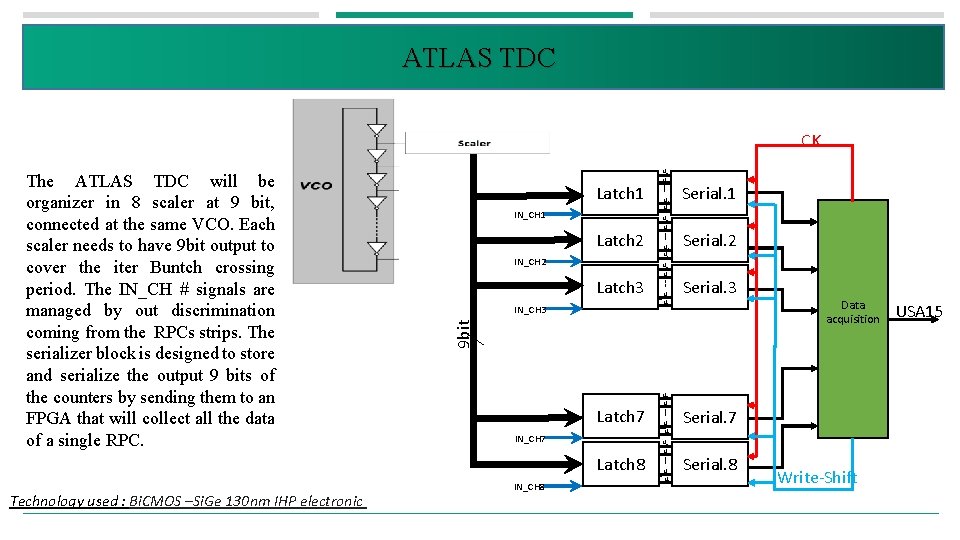

ATLAS TDC CK Latch 1 IN_CH 1 Latch 2 IN_CH 2 Latch 3 IN_CH 3 Latch 7 IN_CH 7 Latch 8 Technology used : Bi. CMOS –Si. Ge 130 nm IHP electronic N 0 N 1 N 7 N 8 Serial. 1 Serial. 2 Serial. 3 9 bit The ATLAS TDC will be organizer in 8 scaler at 9 bit, connected at the same VCO. Each scaler needs to have 9 bit output to cover the iter Buntch crossing period. The IN_CH # signals are managed by out discrimination coming from the RPCs strips. The serializer block is designed to store and serialize the output 9 bits of the counters by sending them to an FPGA that will collect all the data of a single RPC. IN_CH 8 N 0 N 1 N 7 N 8 Data acquisition Serial. 7 Serial. 8 Write-Shift USA 15

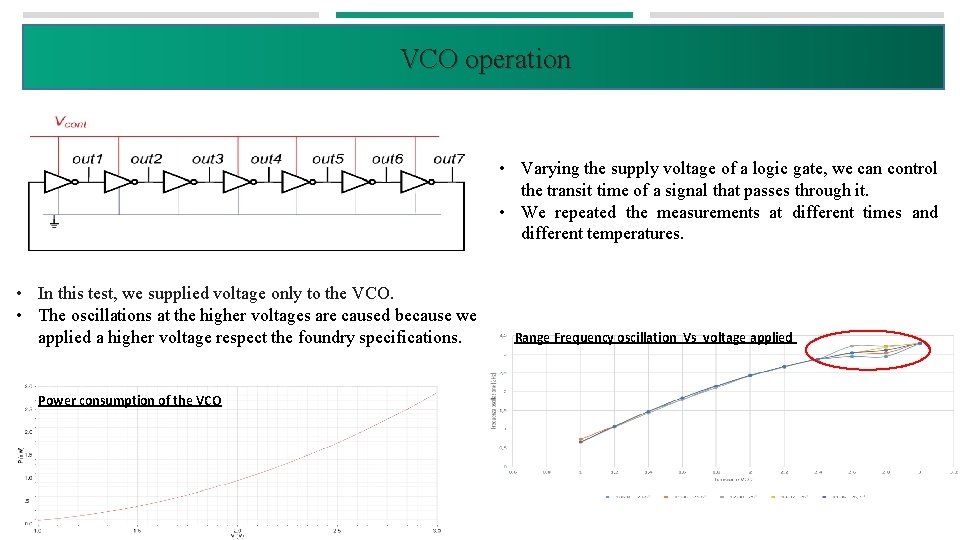

VCO operation • Varying the supply voltage of a logic gate, we can control the transit time of a signal that passes through it. • We repeated the measurements at different times and different temperatures. • In this test, we supplied voltage only to the VCO. • The oscillations at the higher voltages are caused because we applied a higher voltage respect the foundry specifications. Power consumption of the VCO Range Frequency oscillation Vs voltage applied

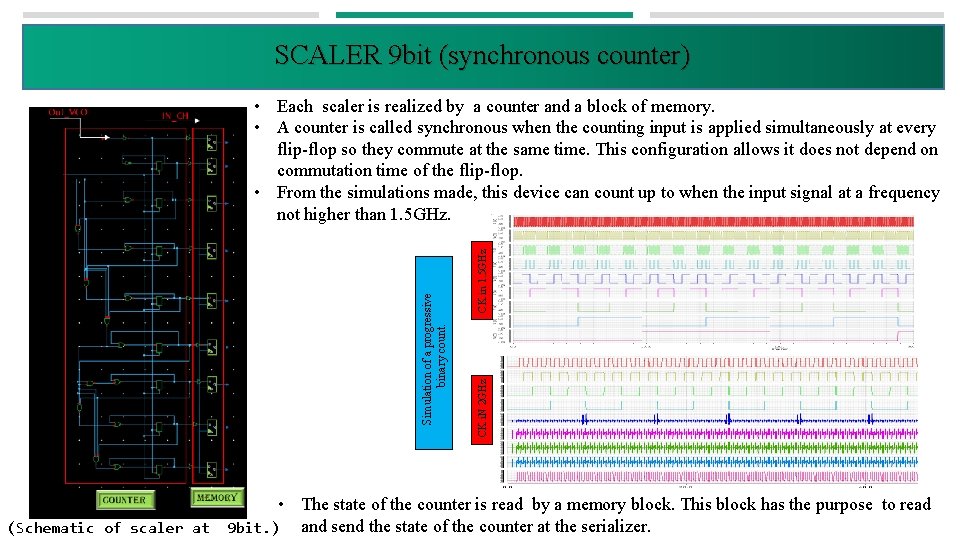

SCALER 9 bit (synchronous counter) CK in 1. 5 GHz CK i. N 2 GHz Simulation of a progressive binary count. • Each scaler is realized by a counter and a block of memory. • A counter is called synchronous when the counting input is applied simultaneously at every flip-flop so they commute at the same time. This configuration allows it does not depend on commutation time of the flip-flop. • From the simulations made, this device can count up to when the input signal at a frequency not higher than 1. 5 GHz. • The state of the counter is read by a memory block. This block has the purpose to read (Schematic of scaler at 9 bit. ) and send the state of the counter at the serializer.

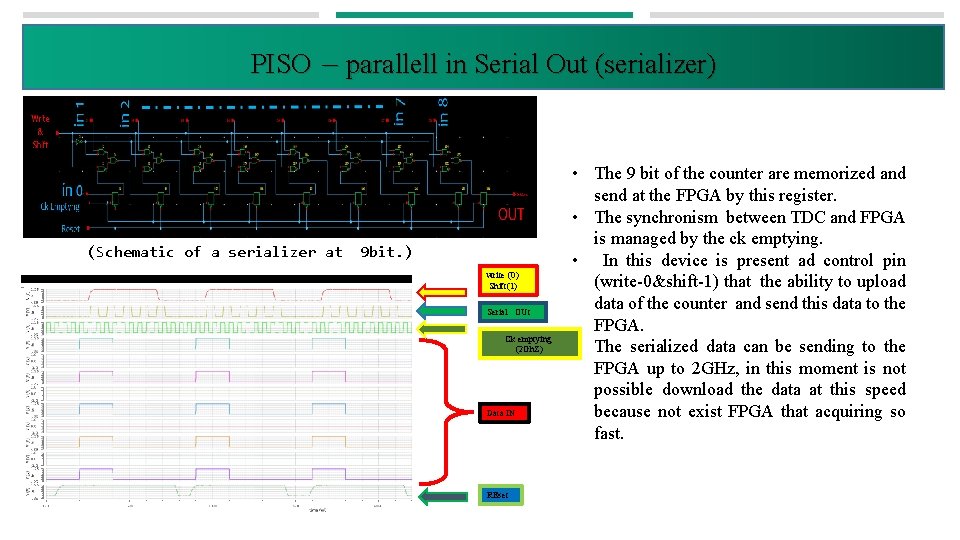

PISO – parallell in Serial Out (serializer) (Schematic of a serializer at 9 bit. ) write (0) Shift(1) Serial OUt Ck emptying (2 Gh. Z) Data IN REset • The 9 bit of the counter are memorized and send at the FPGA by this register. • The synchronism between TDC and FPGA is managed by the ck emptying. • In this device is present ad control pin (write-0&shift-1) that the ability to upload data of the counter and send this data to the FPGA. • The serialized data can be sending to the FPGA up to 2 GHz, in this moment is not possible download the data at this speed because not exist FPGA that acquiring so fast.

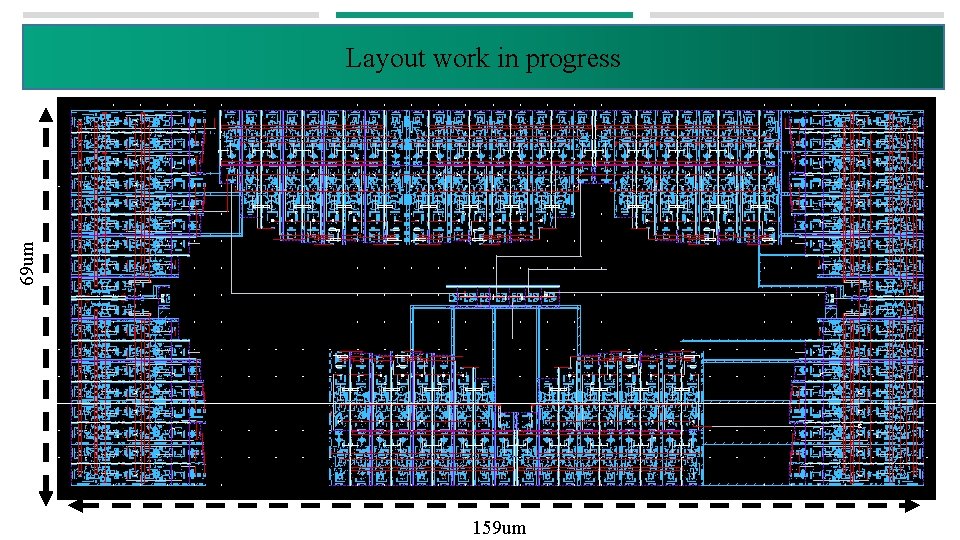

69 um Layout work in progress 159 um

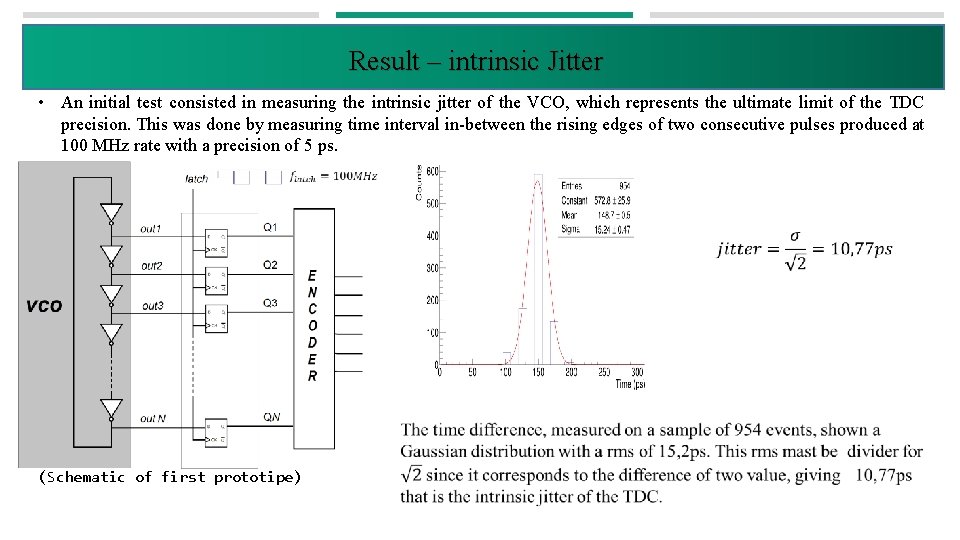

Result – intrinsic Jitter • An initial test consisted in measuring the intrinsic jitter of the VCO, which represents the ultimate limit of the TDC precision. This was done by measuring time interval in-between the rising edges of two consecutive pulses produced at 100 MHz rate with a precision of 5 ps. (Schematic of first prototipe)

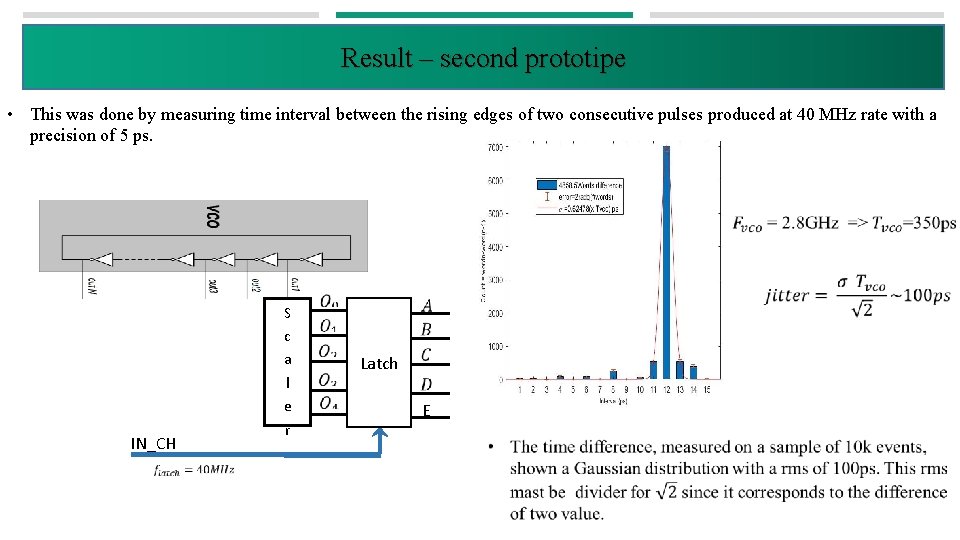

Result – second prototipe • This was done by measuring time interval between the rising edges of two consecutive pulses produced at 40 MHz rate with a precision of 5 ps. IN_CH S c a l e r Latch E

Future step Ø Design a prototype of TDC for the BI RPCs - 8 TDC channels with serialized output; q Test and study the outputs to check the integrity and properation of the device. q Studying, designing and optimization of the coupling between Discriminator and TDC. Ø The communication protocol between the TDC and the data acquisition system, compatible with the FPGA. Ø The pre-production will be carried out through small-volume production of the Europractice foundry service.

Summary Development of the front-end in Si-Ge technology Ø The new FE in development Ø October Testbeam FE system & FE final design Ø Work in progress Simulation and test of a TDC with 100 ps resolution Ø Ø Atlas TDC description Functions of the blocks Results Future Step Optimization of RPCs read-out panel with electromagnetic simulation Ø Different type of read-out panel simulation Ø Optimization Ø State of the art

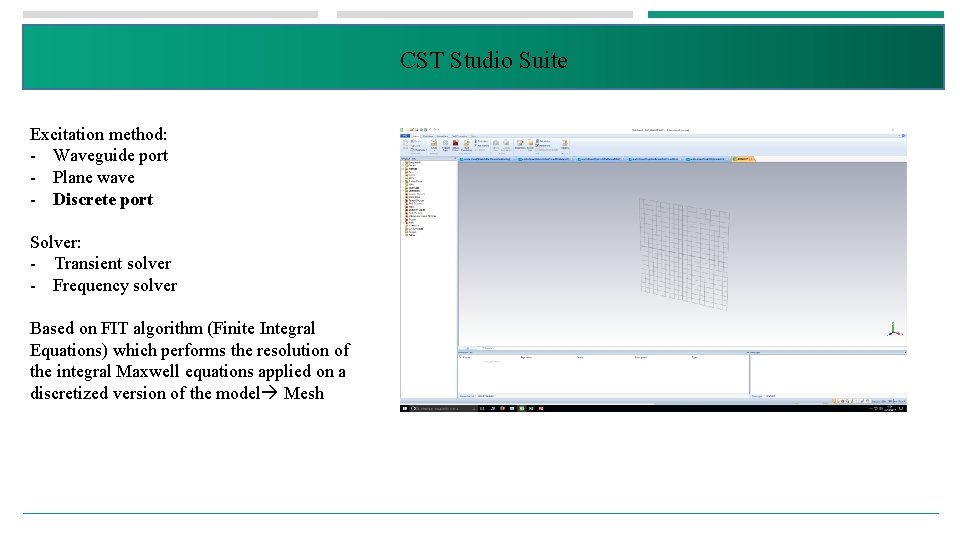

CST Studio Suite Excitation method: - Waveguide port - Plane wave - Discrete port Solver: - Transient solver - Frequency solver Based on FIT algorithm (Finite Integral Equations) which performs the resolution of the integral Maxwell equations applied on a discretized version of the model Mesh

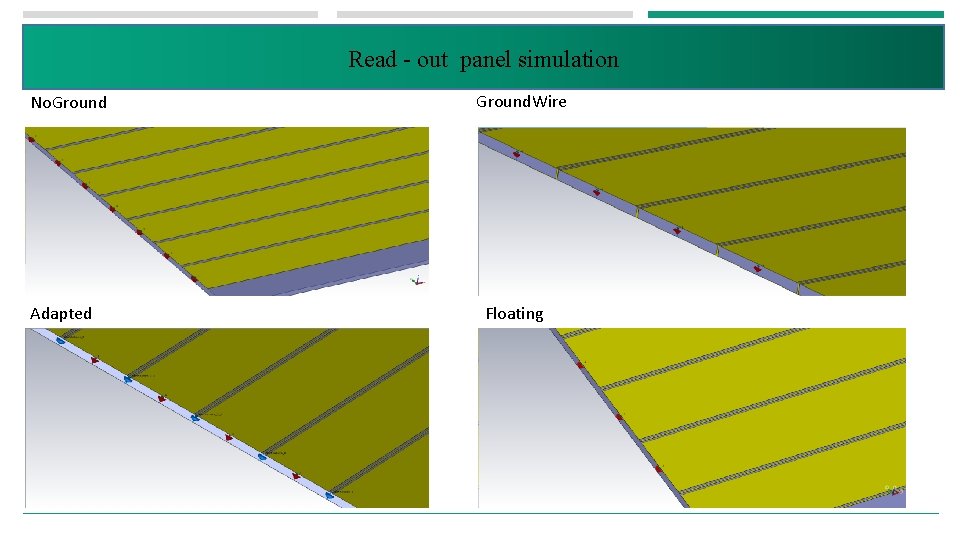

Read - out panel simulation No. Ground Adapted Ground. Wire Floating

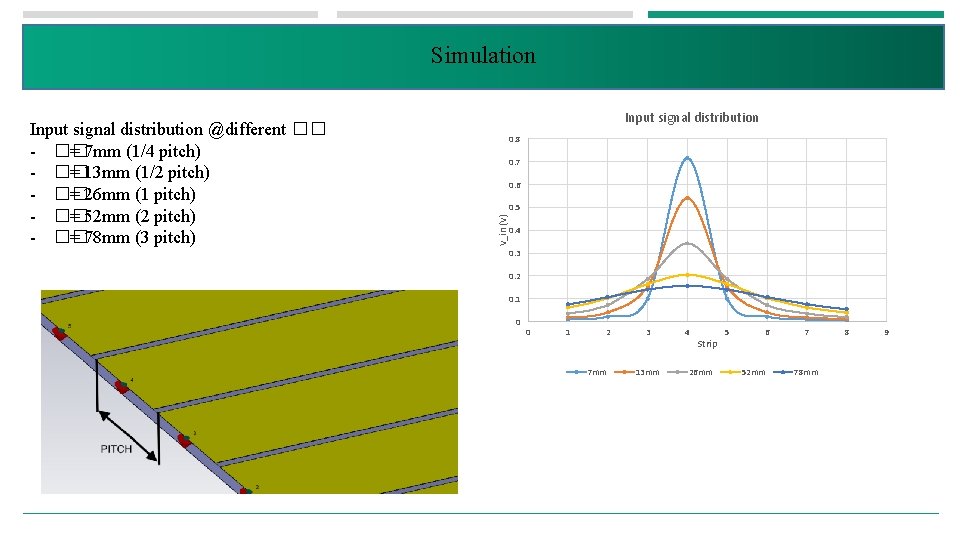

Simulation Input signal distribution 0. 8 0. 7 0. 6 0. 5 V_in (V) Input signal distribution @different �� - �� = 7 mm (1/4 pitch) - �� = 13 mm (1/2 pitch) - �� = 26 mm (1 pitch) - �� = 52 mm (2 pitch) - �� = 78 mm (3 pitch) 0. 4 0. 3 0. 2 0. 1 0 0 1 2 7 mm 3 13 mm 4 Strip 26 mm 5 6 52 mm 7 78 mm 8 9

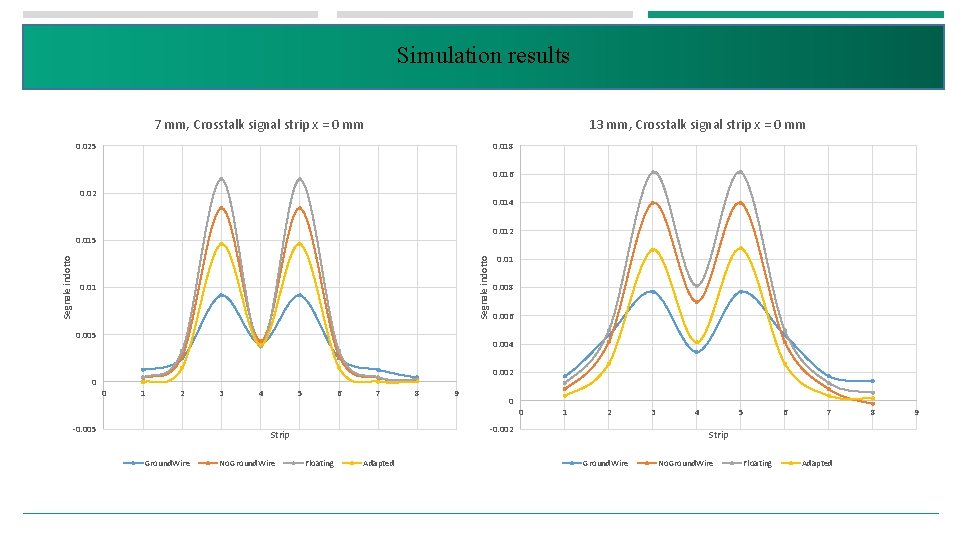

Simulation results 7 mm, Crosstalk signal strip x = 0 mm 13 mm, Crosstalk signal strip x = 0 mm 0. 025 0. 018 0. 016 0. 02 0. 014 0. 012 Segnale indotto 0. 015 0. 01 0. 005 0 0. 01 0. 008 0. 006 0. 004 0. 002 0 1 2 -0. 005 3 4 5 6 7 No. Ground. Wire 9 0 0 1 2 -0. 002 Strip Ground. Wire 8 Floating Adapted 3 4 5 6 7 Strip Ground. Wire No. Ground. Wire Floating Adapted 8 9

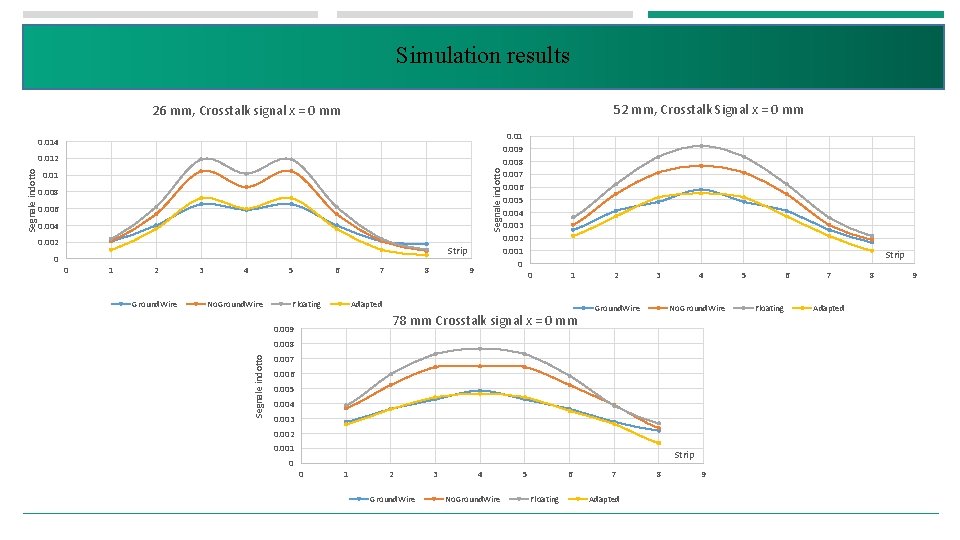

Simulation results 52 mm, Crosstalk Signal x = 0 mm 26 mm, Crosstalk signal x = 0 mm 0. 014 Segnale indotto 0. 01 0. 008 0. 006 0. 004 0. 002 0 Strip 0 1 2 Ground. Wire 3 4 5 No. Ground. Wire 6 7 Floating 8 9 Strip 0 1 Adapted 78 mm Crosstalk signal x = 0 mm 0. 009 2 3 Ground. Wire 4 No. Ground. Wire 0. 008 Segnale indotto 0. 012 0. 01 0. 009 0. 008 0. 007 0. 006 0. 005 0. 004 0. 003 0. 002 0. 001 0 Strip 0 1 2 Ground. Wire 3 4 No. Ground. Wire 5 6 Floating 7 Adapted 8 9

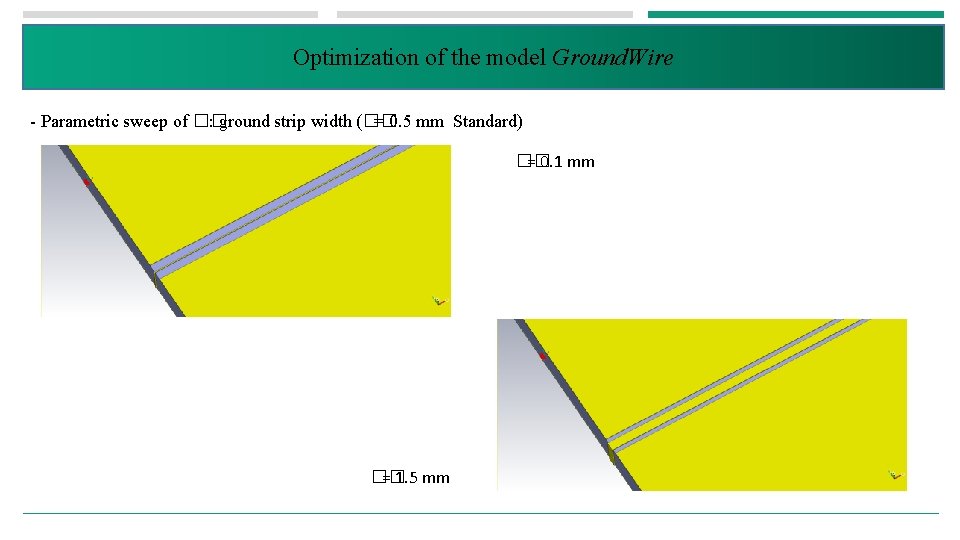

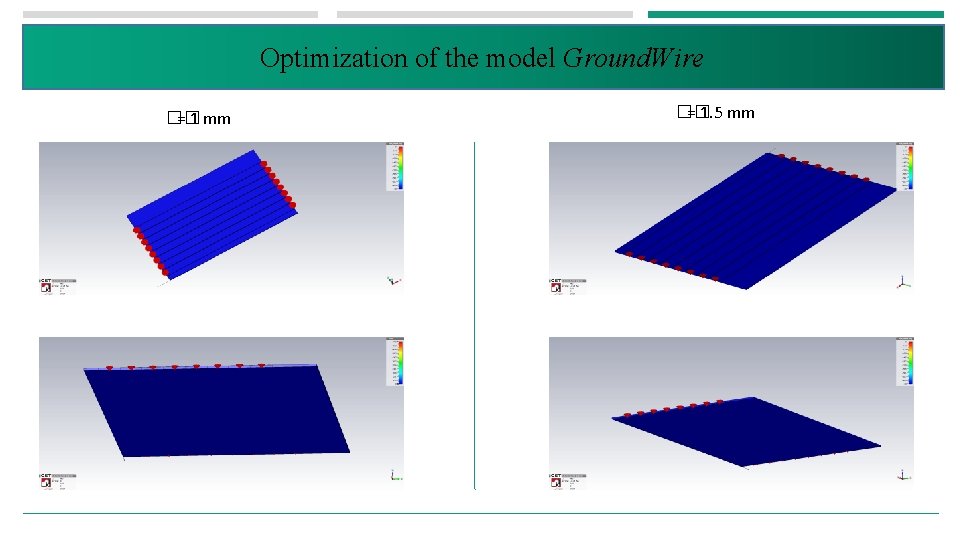

Optimization of the model Ground. Wire - Parametric sweep of �� : ground strip width (�� = 0. 5 mm Standard) �� = 0. 1 mm �� = 1. 5 mm

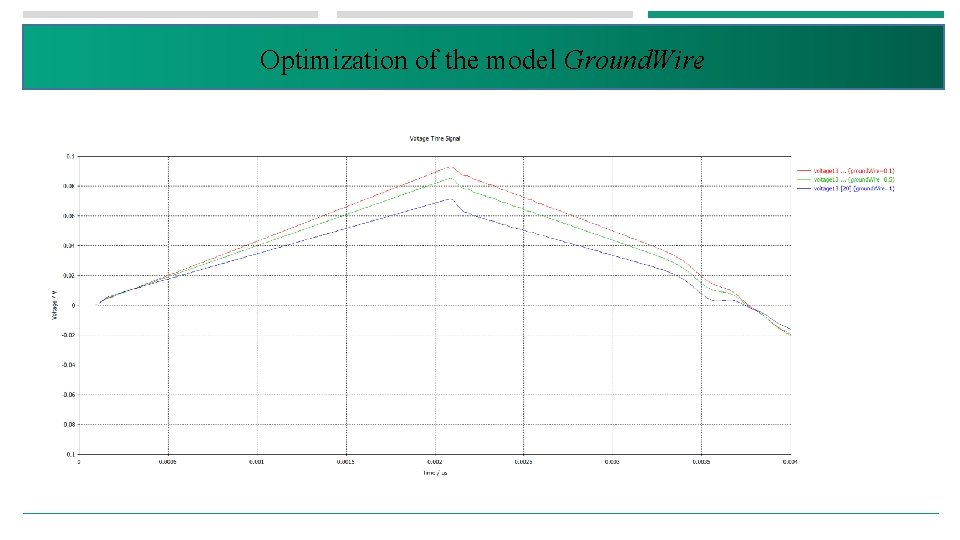

Optimization of the model Ground. Wire

Optimization of the model Ground. Wire

Optimization of the model Ground. Wire �� = 0. 1 mm �� = 1. 5 mm

Optimization of the model Ground. Wire �� = 1 mm �� = 1. 5 mm

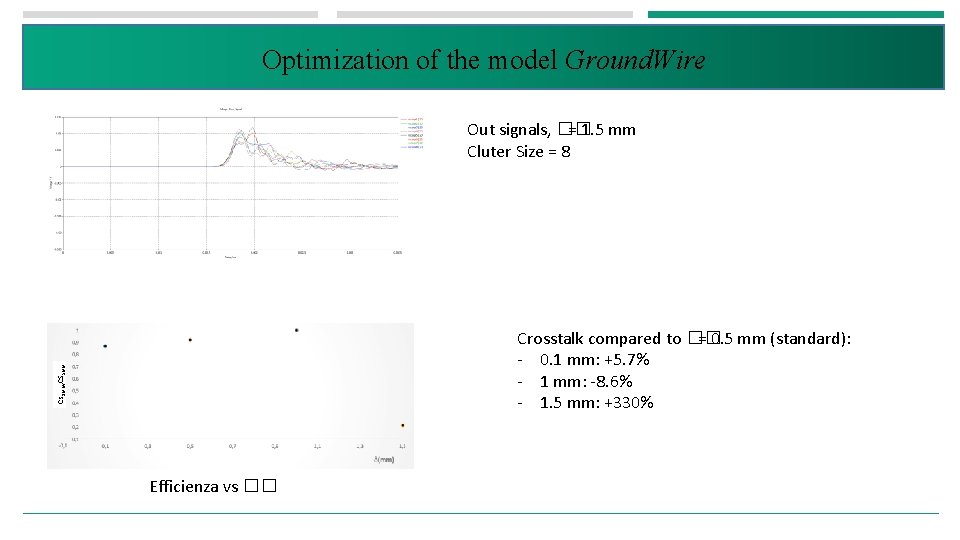

Optimization of the model Ground. Wire Out signals, �� = 1. 5 mm Cluter Size = 8 Cs 1 mm/CSxmm Crosstalk compared to �� = 0. 5 mm (standard): - 0. 1 mm: +5. 7% - 1 mm: -8. 6% - 1. 5 mm: +330% Efficienza vs ��

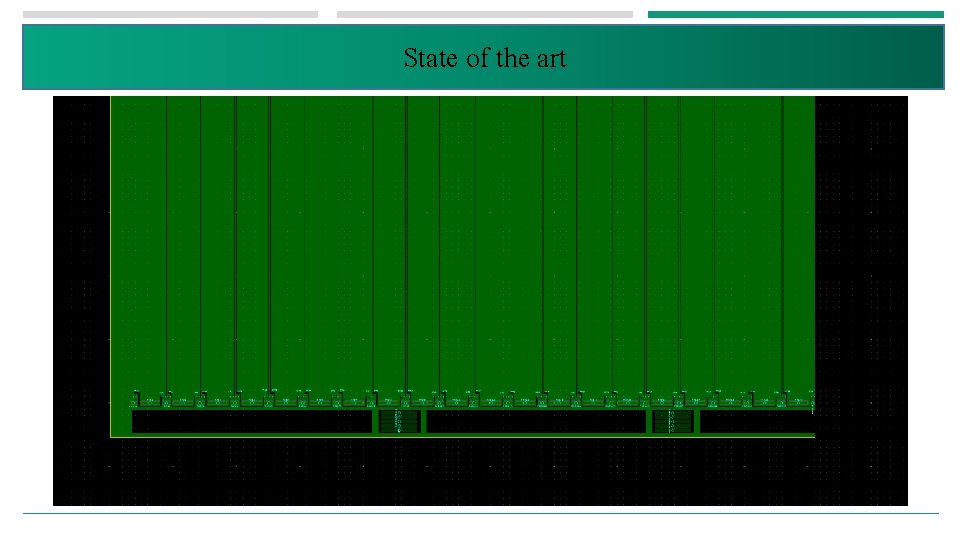

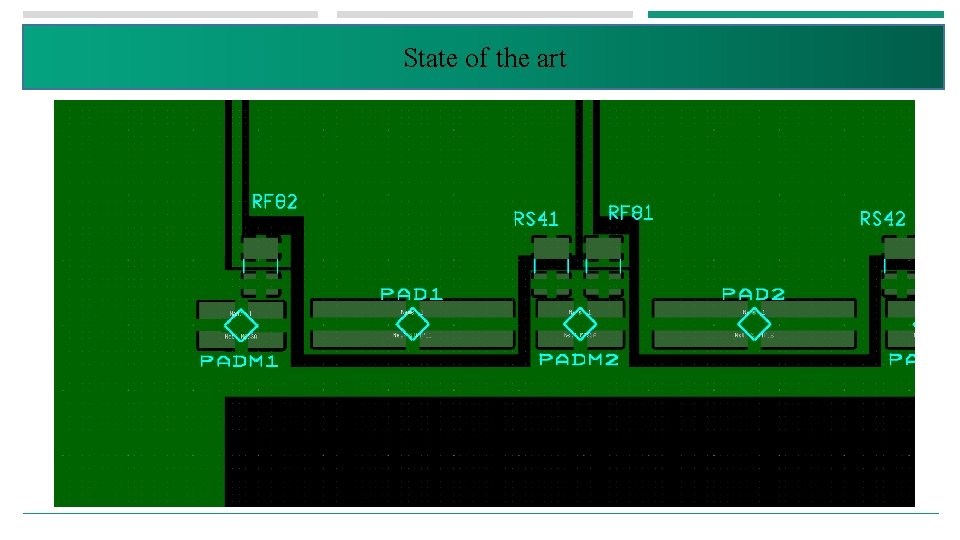

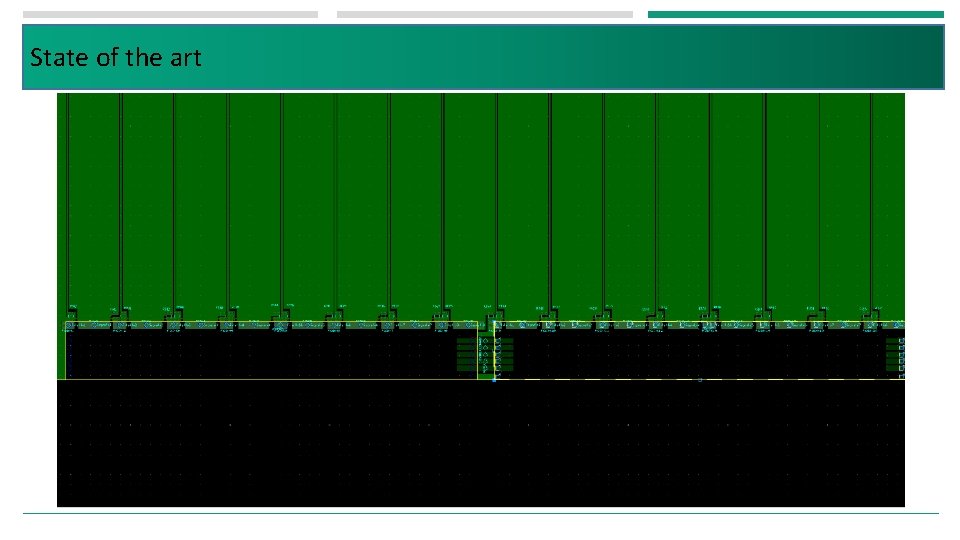

State of the art

State of the art

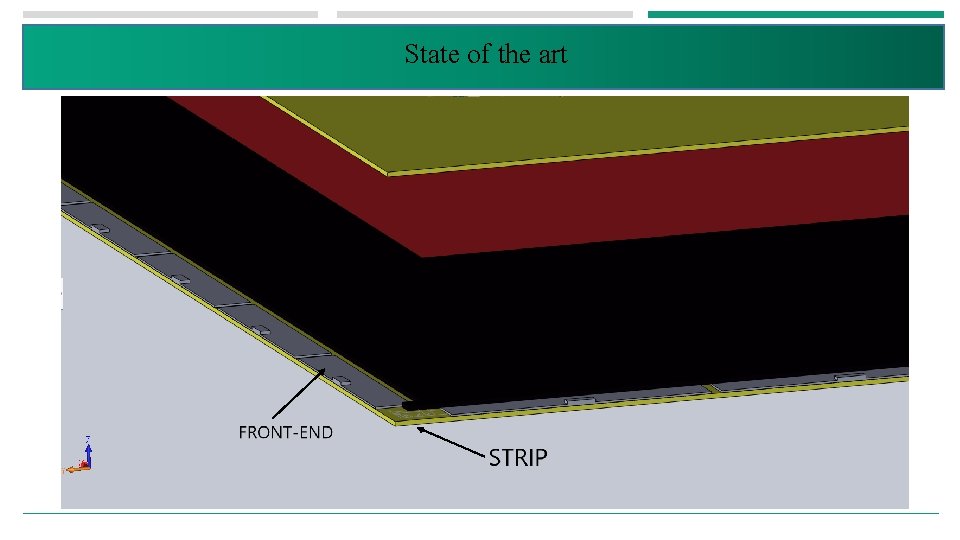

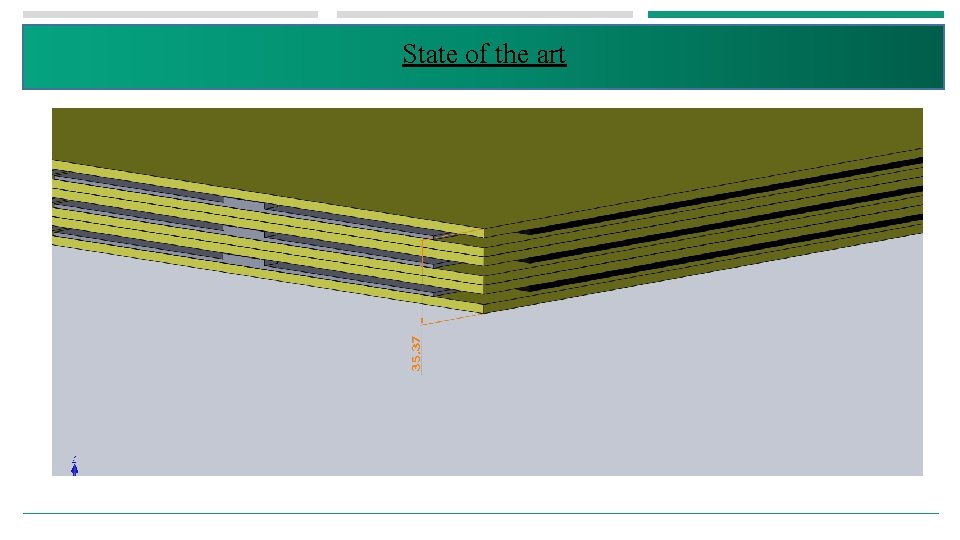

State of the art

State of the art

State of the art

Back up

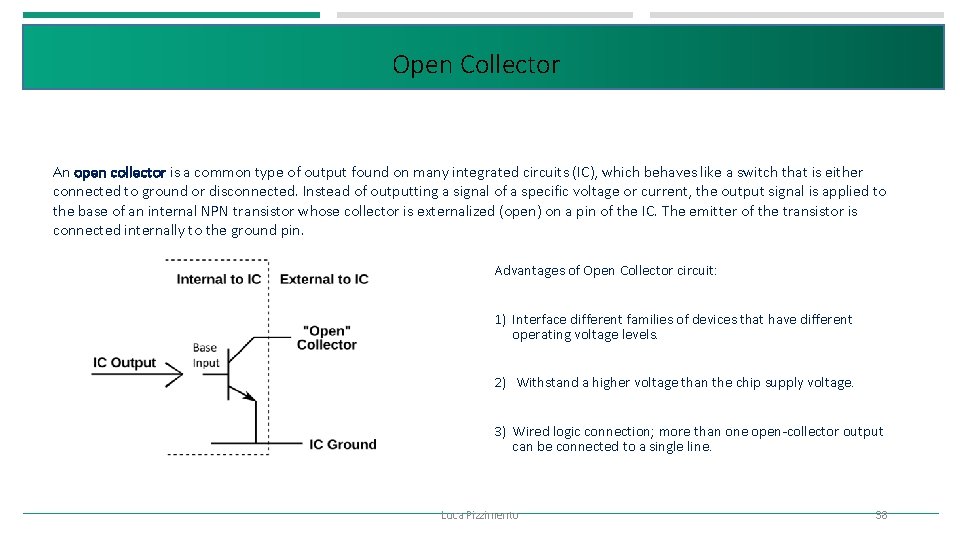

Open Collector An open collector is a common type of output found on many integrated circuits (IC), which behaves like a switch that is either connected to ground or disconnected. Instead of outputting a signal of a specific voltage or current, the output signal is applied to the base of an internal NPN transistor whose collector is externalized (open) on a pin of the IC. The emitter of the transistor is connected internally to the ground pin. Advantages of Open Collector circuit: 1) Interface different families of devices that have different operating voltage levels. 2) Withstand a higher voltage than the chip supply voltage. 3) Wired logic connection; more than one open-collector output can be connected to a single line. Luca Pizzimento 38

- Slides: 38