Roadmap Contiguous memory management and its limitations Paged

- Slides: 13

Roadmap • Contiguous memory management and its limitations • Paged memory management This presentation is intended to be • Motivation and overview • Binding, page table, mode. and the MMU viewed in the slideshow If you are • Segmented memory reading this management text, you are not in slide • Motivation and overview show • The mode. segment table Hit the F 5 function key to enter slideshow mode. MSJ-1

Summary of Contiguous Memory Management • Contiguous memory management means that the physical address space of a process must be a single contiguous block (sometimes known as a partition) in physical memory • External fragmentation is intrinsic to contiguous memory management • It is the variable length holes in memory that lead to external fragmentation and since processes are variable length, so too will be the holes • Even if we quantize our allocations and hence our holes, there can still be a variable number of quanta per hole and so we still will eventually have external fragmentation • Compaction is in fact a solution, but not for real time systems • To take the next step we’re going to have to drop the requirement for the physical address space of a process to be contiguous MSJ-2

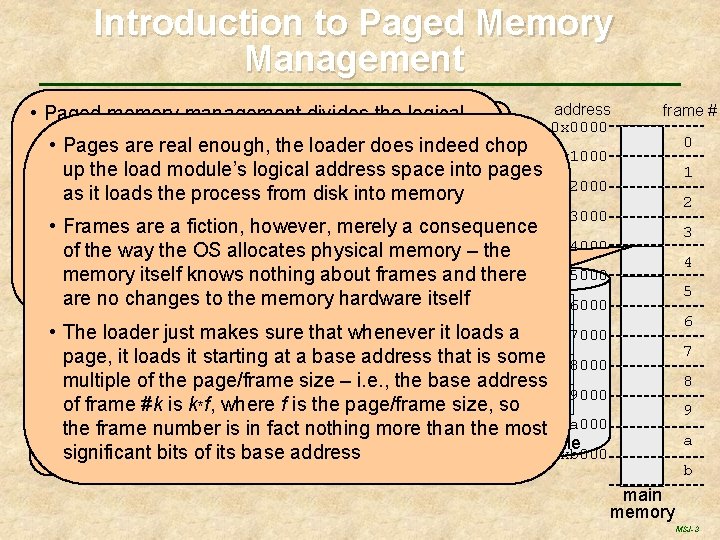

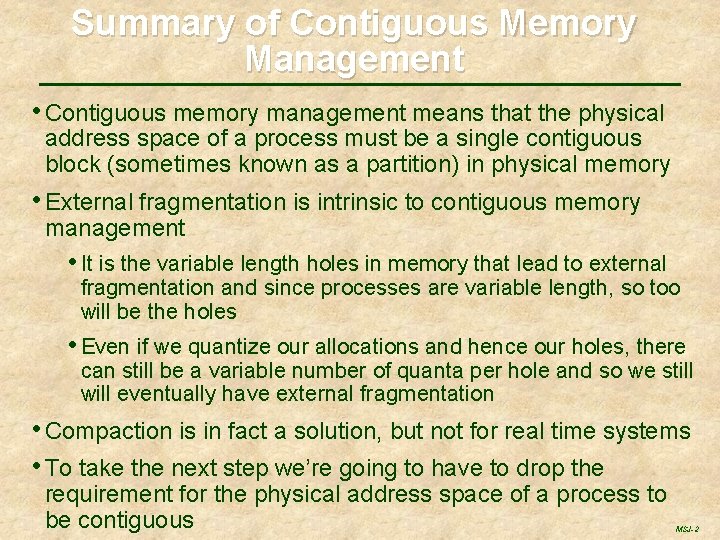

Introduction to Paged Memory Management address • Paged memory management theoflogical Here, for example, we see thedivides OS view memory 0 x 0000 3 12 4 3 address space of enough, the load module into fixed for a page/frame size of 2 the = loader (2 ) up =16 bytes =1 Kchop • Pages are real does indeed 16 0 x 1000 length chunks (quanta, called pages) before (that’s a load hex Kmodule’s there; it now would be 4096 , in decimal) up the logical address space into pages 10 0 x 2000 loading themthe independently into “frames” defined as it loads process from disk into memory by evenly spaced main memory addresses that 0 x 3000 • Frames are a fiction, however, merely a consequence appear to divide physical memory into fixed length 0 x 4000 offrame the way the OS allocates physical memory – the So 4 starts at physical address 4·(frame size) = • chunks The physical memory doesn’t see any of this; exactly the same size as pages 0 x 5000 itself knows nothing about frames 4· 1 K 0 x 4000 andboring runs up but not including the 16 = itmemory just continues its lifeto of receiving a and there • start Any can 5 go any arepage changes to theaframe memory hardware itself ofno frame atto 0 x 5000, or physical addresses 0 x 6000 page 0 physical address plus control bit which tells 0 x 4000 – 0 x 4 fff, inclusive whether tojust readmakes or write that address • it. The loader sure that whenever it loads a page 1 0 x 7000 page, it loads it starting at apages base into address • It’s up to the loader to load the that is some 0 x 8000 page 2 multiplephysical of the page/frame size it’s ‒ i. e. , base address correct addresses and up the to the 0 x 9000 page 3 of frame #k is k f, where f is the page/frame size, so MMU to properly* bind a logical address to a 0 xa 000 load the frame numberbefore is in fact nothing more than the most physical address it’s sent to the memory module significant bits of its base address 0 xb 000 (we’ll see how shortly) frame # 0 1 2 3 4 5 6 7 8 9 a b main memory MSJ-3

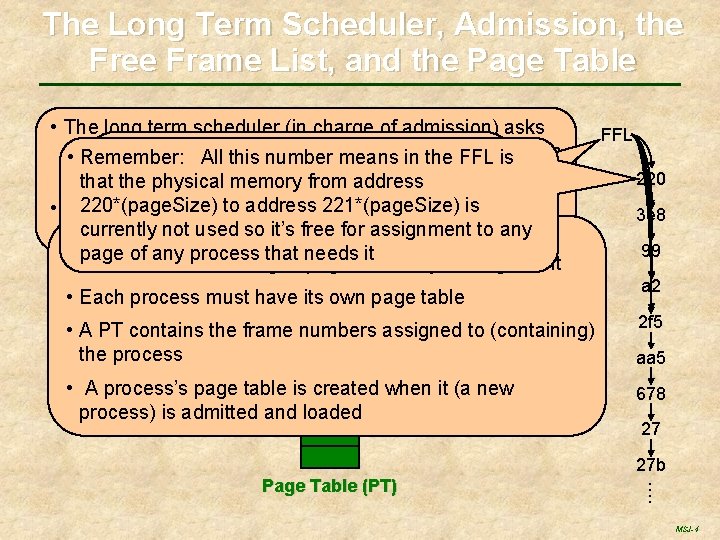

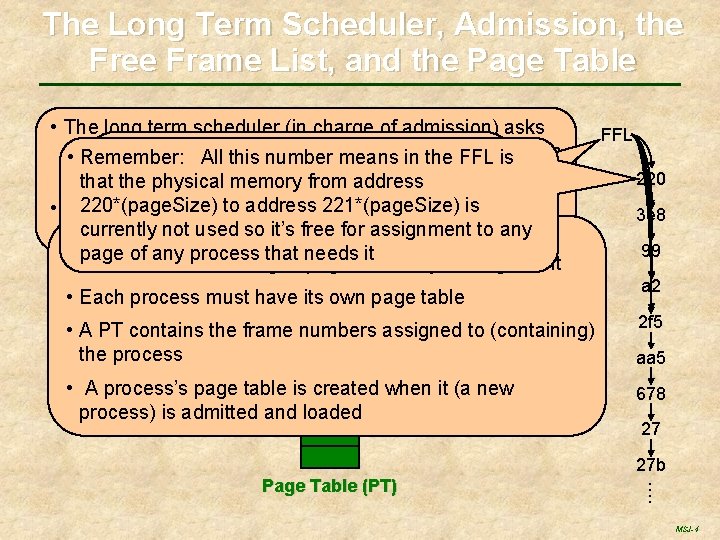

The Long Term Scheduler, Admission, the Free Frame List, and the Page Table • The long term scheduler (in charge of admission) asks the memory manager there are enough free frames For paged memory management, the free • Remember: All thisifnumber means in the FFL is on the free for the new space list islistsimplified tofrom aprocess free frame list that theframe physical memory address whose management is much to address is from • If 220*(page. Size) so, (FFL) the requisite number of 221*(page. Size) frames aresimpler removed thanand the older free list: currently not used so space it’s free for process’s assignment to any the FFL inserted new page • The page table (PT)into is athe data structure used for table the need to beneeds ordered page • Itofdoesn’t any process that it execution time binding of paged memory management • Since they’re fixed length, any frame is as • Each good process mustother havefor itsany ownuse page table as any whatsoever • A PT contains the frame numbers assigned to (containing) the process • A process’s page table is created when it (a new process) is admitted and loaded FFL 220 3 e 8 99 a 2 2 f 5 aa 5 678 27 27 b Page Table (PT) ⁞ MSJ-4

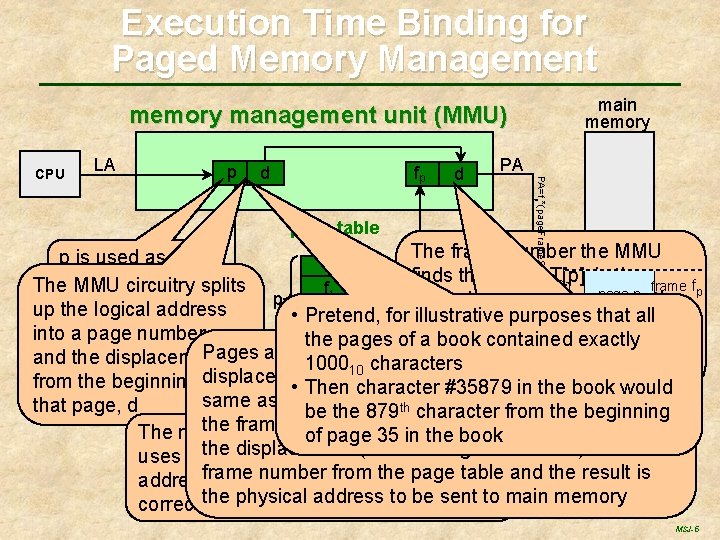

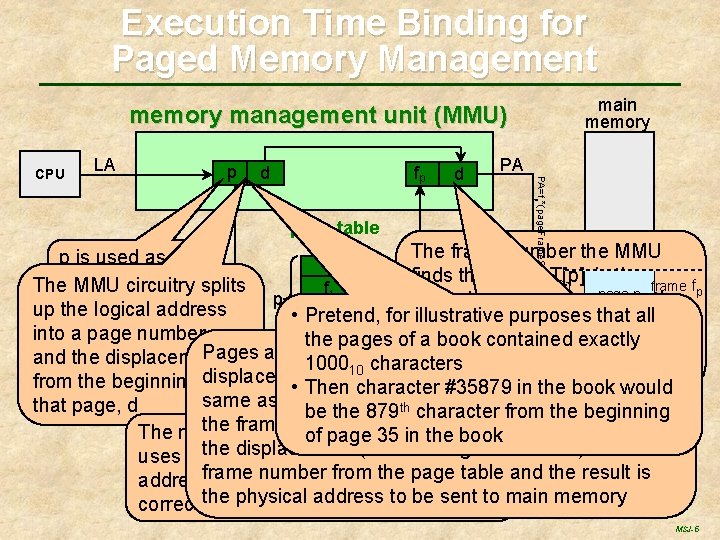

Execution Time Binding for Paged Memory Management main memory management unit (MMU) LA p d fp d PA PA=fp*(page. Frame. Size)+d CPU page table (PT) The frame number the MMU f 0 finds there, in PT[p], is the frame f d f 1 p page p p frame in main memory that the f 2 • Pretend, for OS illustrative purposes that allp of assigned to hold page p is used as offsetcircuitry into splits Thean. MMU up the page logicaltable address into a page number, p, the⁞ pages ofthe a book contained exactly process’s logical address f Pages and frames are the same size so the p and the displacement 100010 characters space displacement from the beginning of a page is the from the beginning of • Then character #35879 in the book would same as the displacement from the base address of that page, d be the 879 th character from the beginning the frame that holdsunit that page, so the MMU appends The memory management of page 35 in(MMU) the book the displacement (from the logical address) to the uses the page table to bind each logical number the addressframe emitted by thefrom CPU topage the table and the result is physical address to bememory sent to main memory correct the physical address in main MSJ-5

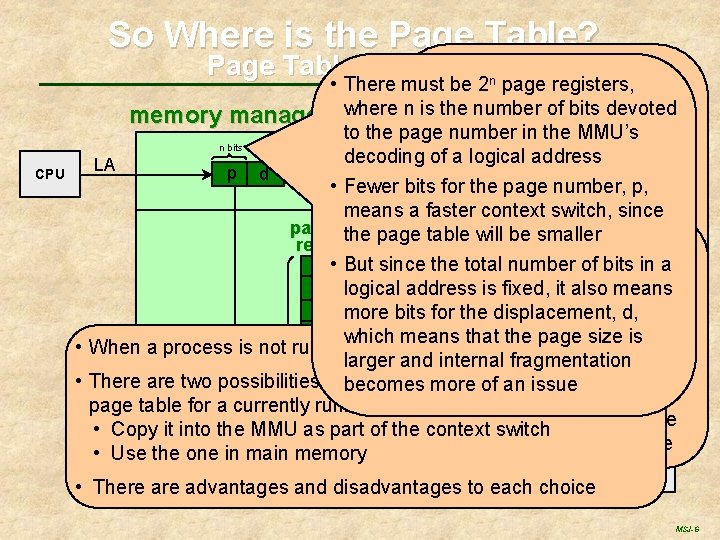

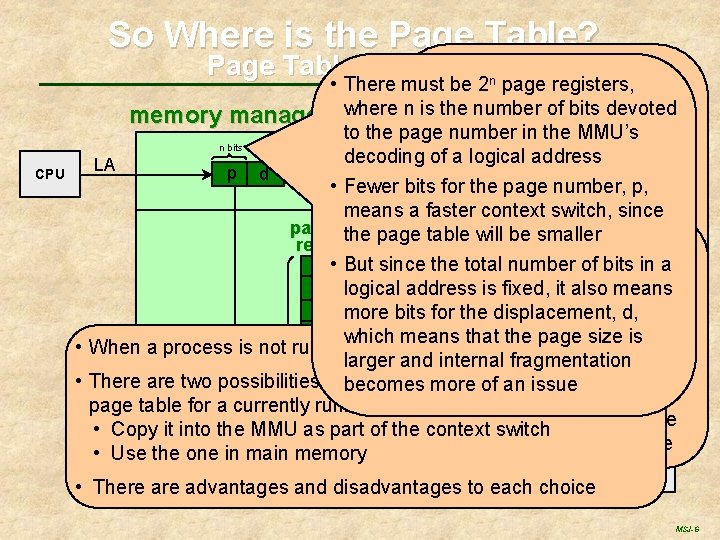

So Where is the Page Table? Page Table in the MMU • Each page register also n CPU • There must be 2 page registers, needs an extra bit to indicate where n is the number of bits devoted memory management unitwhether (MMU) or not it is valid to the page number in the MMU’s main memory n bits • So, example, for a process decoding of afor logical address LA PA p d fpwhose dp logical address space • Fewer bits for the page number, p, only 5 pages, onlysince the means a was faster context switch, page table first 5 will page registers would be the page table be smaller • If marked the pagevalid table for the running registers (PT) • But the total number in a v since process is going to of bebits in the • A CPU reference to an invalid v logical address fixed, also MMU, it is must beitread inmeans to what page would the d, MMU v bits more forcalled the displacement, are the cause MMU page v fp which to generate apage hardware 2 n page means thatasthe sizecontext istrap registers part of the • When a process is not running, vits page table is kept in memory registers and the OS would larger and internal fragmentation switch whenever theterminate process is i the process • There are two possibilities forbecomes how the MMU willanaccess more of issue the dispatched i page table for a currently running process: i • The bigger the page table, the • Copy it into the MMU as part of the context switch longer the context switch time • Use the one in main memory • There advantages and disadvantages to each choice MSJ-6

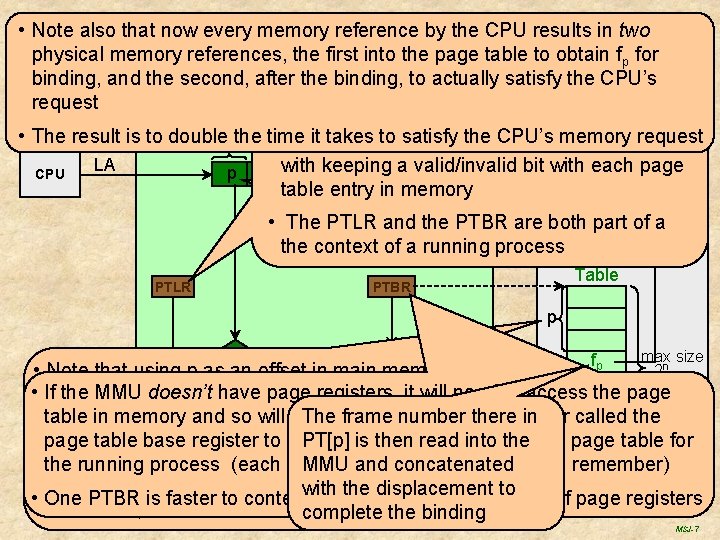

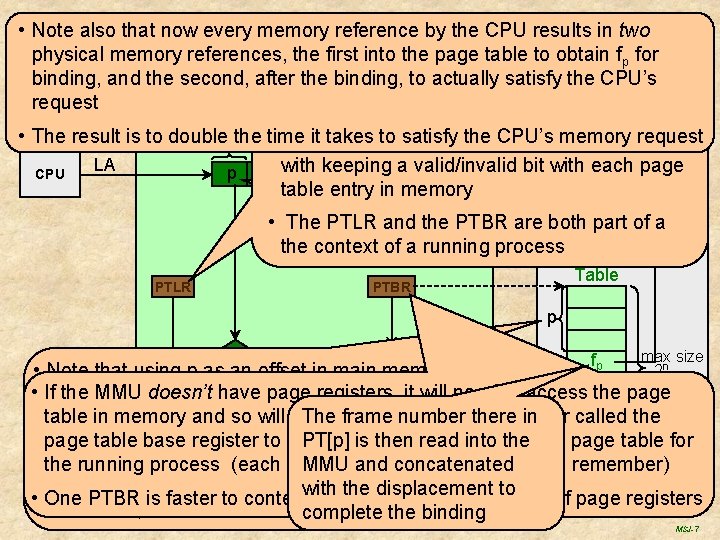

• Note also that now every memory reference by the CPU results in two physical memory references, the first into the page table to obtain fp for binding, and the second, after the binding, to actually satisfy the CPU’s request memory management • A page tableunit limit(MMU) register (PTLR) in the MMU • The result is to doublen bitsthe time takes toto satisfy the CPU’s memory request To find the physical address inmemory canitbe used avoid (fairly obvious) problems main memory of desired in LA PAbitentry a valid/invalid with each page p d with keeping fp the CPU d the page table, the page number table entry in memory is simply added to the PTBR • The PTLR and the PTBR are both part of a the context of a running process Page Table Only in Main Memory PTLR Page Table PTBR p yes p + • Note that using p as an ? offset in main memory means p ≤ PTLR fp maxn size 2 entries • Ifthat thethe MMU doesn’t registers, init memory will need to access the page table have must be contiguous no page The a frame number there in table in memory and so will need special purpose register called the • If the largest possible page table fits into a single trap to contain PT[p] is then read into the page table base register base address of the page table for to OS of course, the frame, that’s guaranteed, since memory MMU and the running process (each process hasconcatenated its own page table, remember) within a frame is contiguous the than displacement to • One PTBR is faster to contextwith switch a whole bunch of page registers • Otherwise, it will be necessary to pagethe thebinding page table! complete MSJ-7

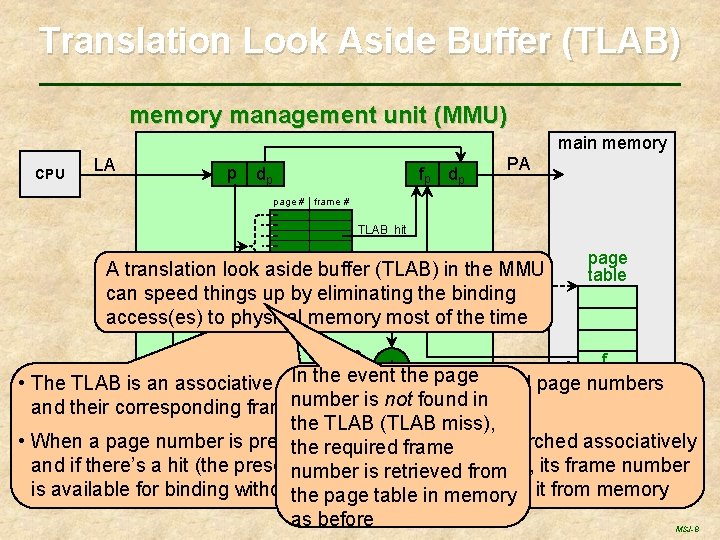

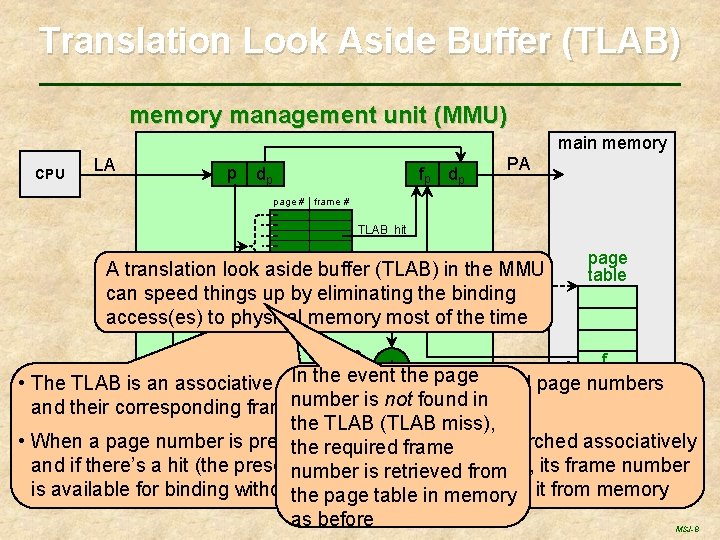

Translation Look Aside Buffer (TLAB) memory management unit (MMU) main memory CPU LA p dp f p dp PA page # frame # TLAB hit A translation look aside buffer (TLAB) in the MMU PTLR PTBR TLABup TLAB can speed things by eliminating the binding miss access(es) to physical memory most of the time p ≤ PTLR yes p + the page In the event page table fp ? • The TLAB is an associative cache of recently referenced page numbers is not found in and their correspondingnoframenumbers the TLAB (TLAB miss), trap • When a page numbertois. OSpresented to the TLAB, the required frame it is searched associatively and if there’s a hit (the presented pageisnumber found), its frame number retrievedis from is available for binding withoutthe thepage necessity of memory retrieving it from memory table in as before MSJ-8

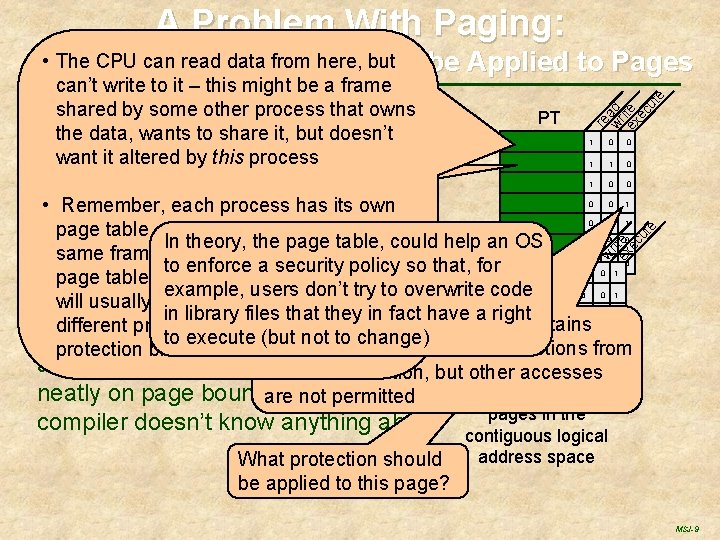

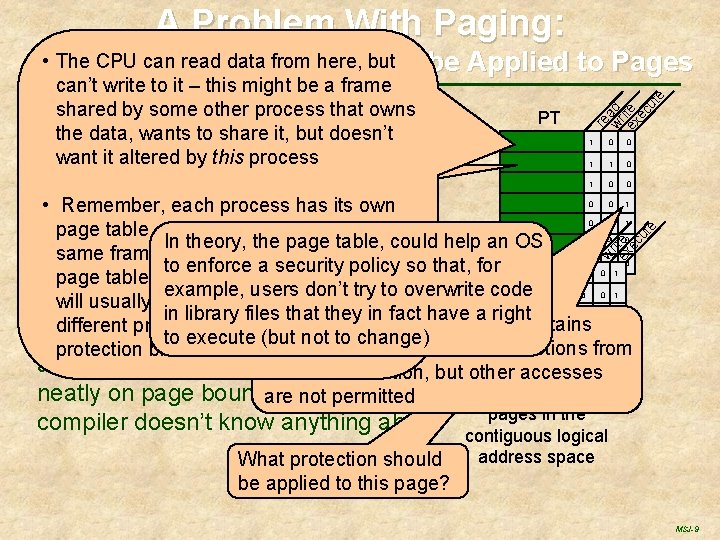

A Problem With Paging: PT 1 0 0 1 1 0 0 0 0 1 re wrad ex ite ec ut to each entry in the page table, so to share memory, the In theory, the page table, could help an OS But theframe program’s address same numberlogical can appear in the to enforce a security policy so that, for page table of multiple by processes and space as produced the compiler example, users don’t try to overwrite code will usually be in different pages in the and linker isincontiguous andthey thein fact have a right library files that This page/frame different processes, each with its own looks like it contains ? ? ? boundaries between the various code to execute (but not to change) code; the CPU can fetch instructions from protection bits data and data structures usually fall but here forwon’t execution, other accesses neatly on page boundaries the are notthat permitted pages in the compiler doesn’t know anything about e re wrad ex ite ec ut can’t write to it ‒ this might be a frame shared by some other process that owns the data, wants to share it, but doesn’t want an it altered this process From MMUbydesign standpoint, it’s Data stored here can be both easy enough: justwritten add protection bits read and by this process • Remember, each process has its own e • The CPU can. Bits read data from here, but Protection Cannot Really be Applied to Pages 1 1 1 What protection should be applied to this page? 0 0 0 1 1 1 0 contiguous logical address space MSJ-9

Roadmap • Contiguous memory management and its limitations • Paged memory management • Segmented memory management • Motivation and overview • The segment table MSJ-10

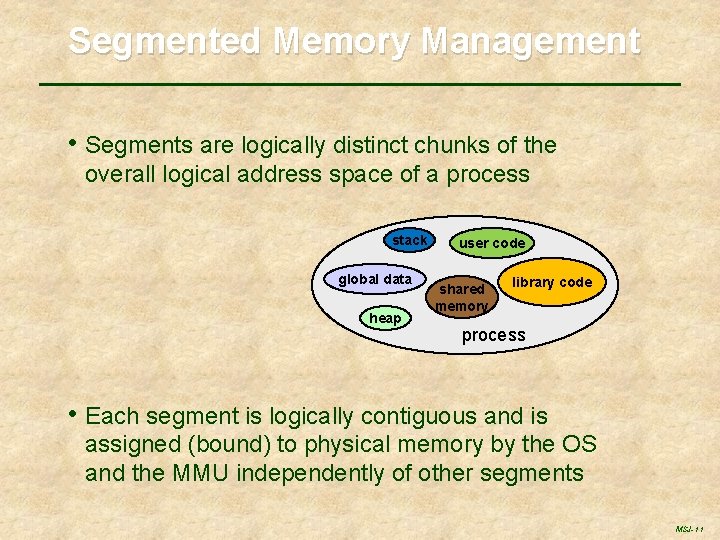

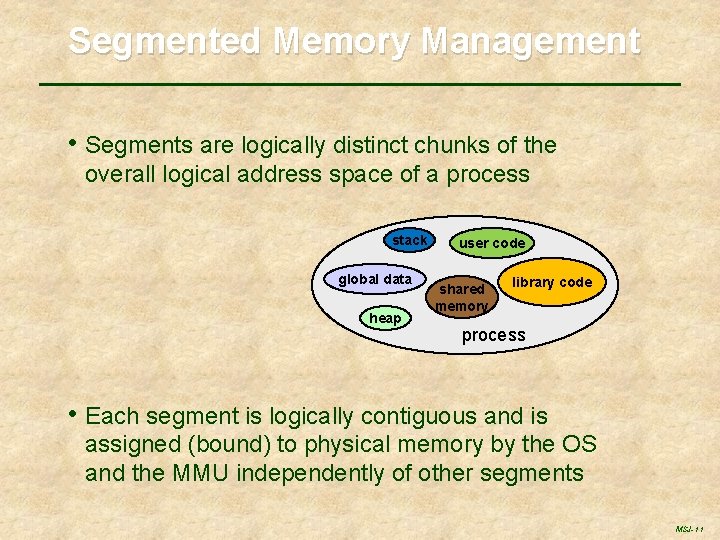

Segmented Memory Management • Segments are logically distinct chunks of the overall logical address space of a process stack global data heap user code shared memory library code process • Each segment is logically contiguous and is assigned (bound) to physical memory by the OS and the MMU independently of other segments MSJ-11

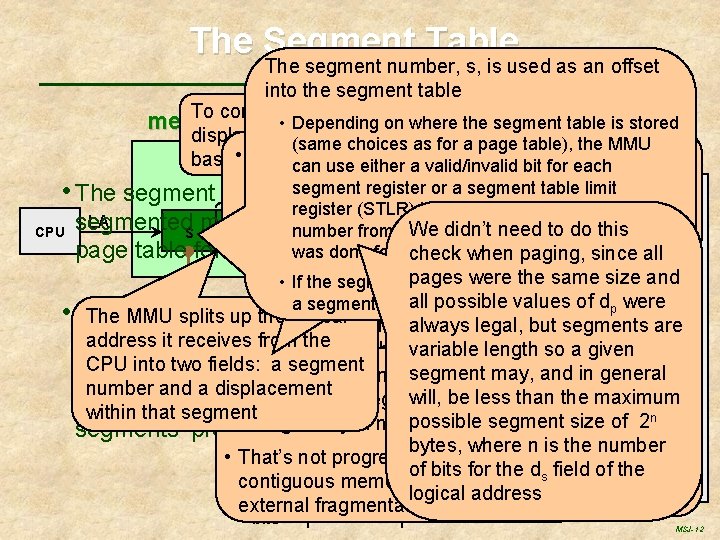

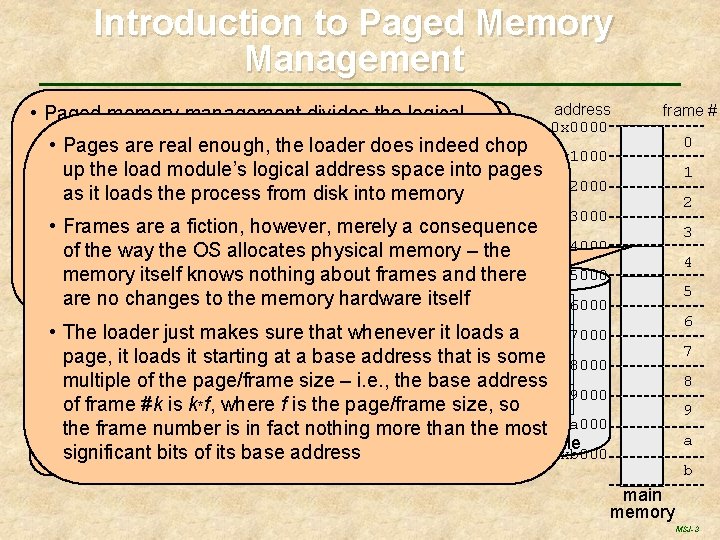

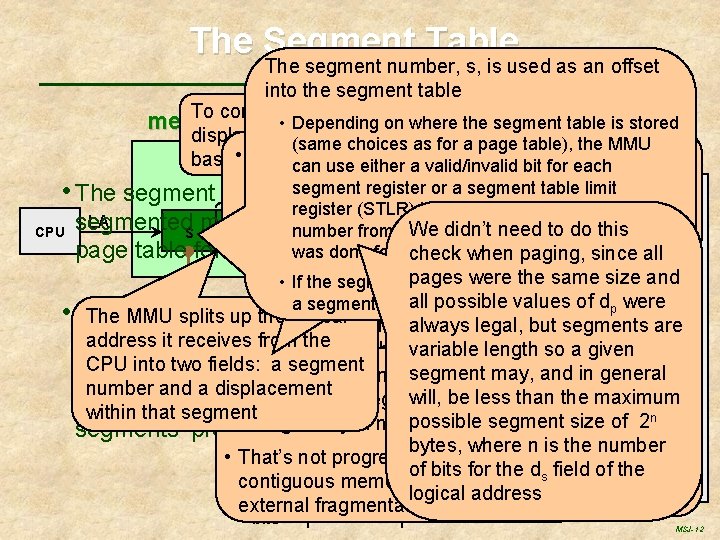

The Segment Table The segment number, s, is used as an offset into the segment table To complete the binding, the • Depending onunit where(MMU) the segment table is stored memory management displacement is added to the (same choices as for a page table), the MMUmain • For a valid segment, the protection bits are then segmentation error, base address ofuse the segment can either a valid/invalid bit for each memory core dumped checked to determine ifathe operation requested segment register or segment table limit n bits • The segment table is the key data structure used by no by the CPU is legal to fordetermine that segment register (STLR) if the segment ds didn’t LA management, analogous to PA needistovalid, dothe this CPU segmented number fromraises a. We logical address just as s memory ds< MMU limit • d. If a protection violation trap s not, the yes ? done formanagmement the pagewhen number by a paging page table for pagedwas memory check paging, since MMU all the same sizeraises and • If the segment pages numberwere is invalid, the MMU possible of dp were a segmentationallerror trap tovalues OS segment table • It. The is where the up protection applicable to each MMU splits the logicalbits. The displacement within always legal, but segments are address it receives from the segment are stored – in fact, the that’s onelength ofentry a in segment, dindicator variable so. Each a given s, is then ? ? a ? CPU into two fields: segment: Something that coherent inmay, terms of its checked against the size segment and insegment general the • Note that thisis binding mechanism ds number and a displacement limit of the from will, besegment less the maximum table records means thatand a segment must be than stored protection requirements independent of other within that segment n the segment table possible segment size of 2 the protection contiguously in main memory! segments’ protection requirements bytes, where n is the number • That’s not progress; we’re back to bits, size, and of bits for the ds field the baseofaddress memory management and rcontiguous w e segment base logical address for a segment protection size address external fragmentation again! + bits MSJ-12

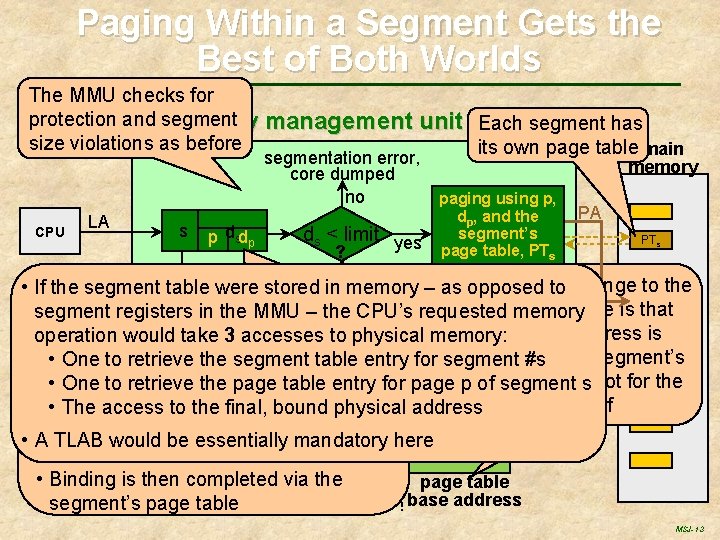

Paging Within a Segment Gets the Best of Both Worlds The MMU checks for protection and segment memory management unit (MMU) Each segment has size violations as before its own page table main segmentation error, core dumped no CPU LA s p dsdp ds < limit yes ? memory paging using p, dp, and the segment’s page table, PTs PA PTs The only • If the segment table were stored in memory – as opposed to change to the • Once the legalityin ofthe the. MMU logical– address segment table is that segment registers the CPU’s requested memory segment table and the CPU’s requested operation are the base address is operation would take 3 accesses to physical memory: the displacement withinentry for segment now#s for the segment’s • determined, One to retrieve the segment table ds, is then twoentry for page p ofpage table, s not for the • segment, One to retrieve the split pageinto table segment a page to number within the physical address segment itself • fields, The access the final, bound segment and a displacement within the • A page TLAB would be essentially mandatory here • Binding is then completed via the protection segment page table size base address segment’s page table bits MSJ-13