Ro VLAB 3000 n BaseBoard8 3 Ro VLAB

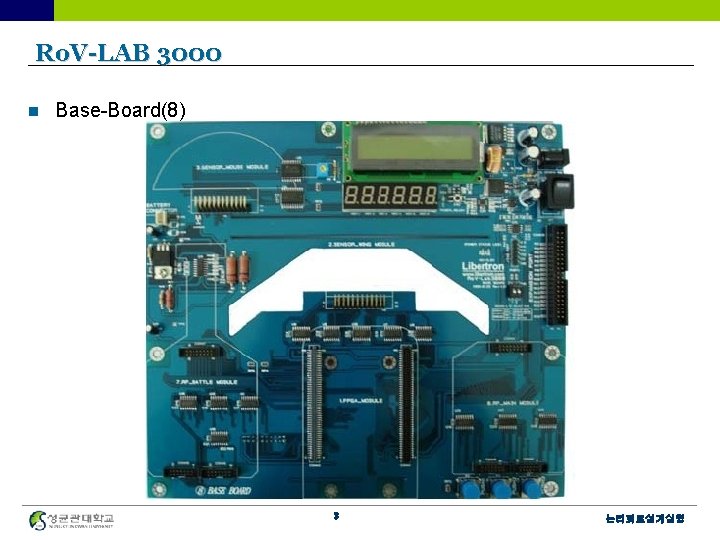

Ro. V-LAB 3000 n Base-Board(8) 3 논리회로설계실험

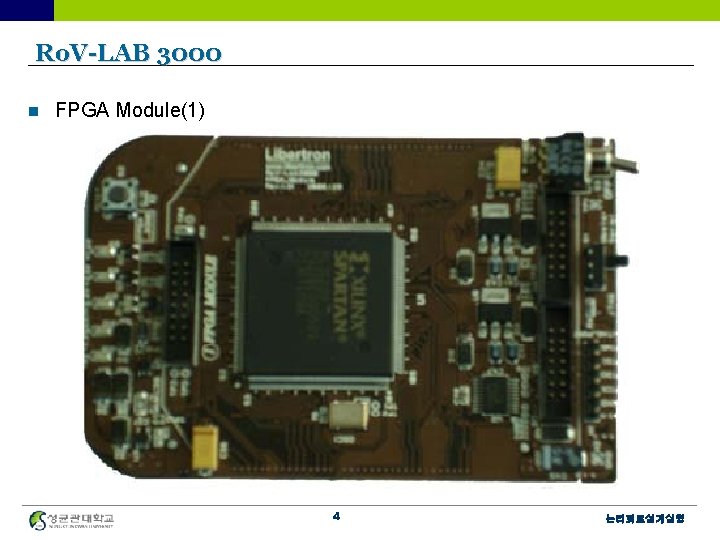

Ro. V-LAB 3000 n FPGA Module(1) 4 논리회로설계실험

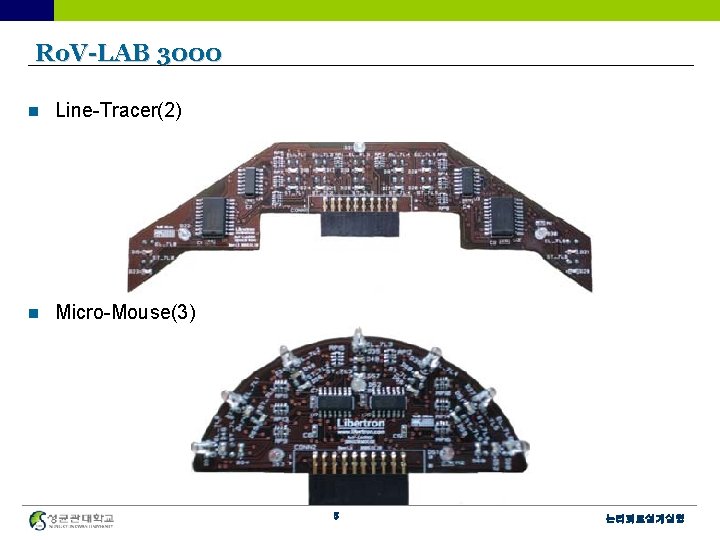

Ro. V-LAB 3000 n Line-Tracer(2) n Micro-Mouse(3) 5 논리회로설계실험

Ro. V-LAB 3000 n Motor Module(4+5) 6 논리회로설계실험

Ro. V-LAB 3000 n RF Main(6) 7 논리회로설계실험

Ro. V-LAB 3000 n RF Battle(7) 8 논리회로설계실험

Ro. V-LAB 3000 n RF 송신부 n JTAG Cable 9 논리회로설계실험

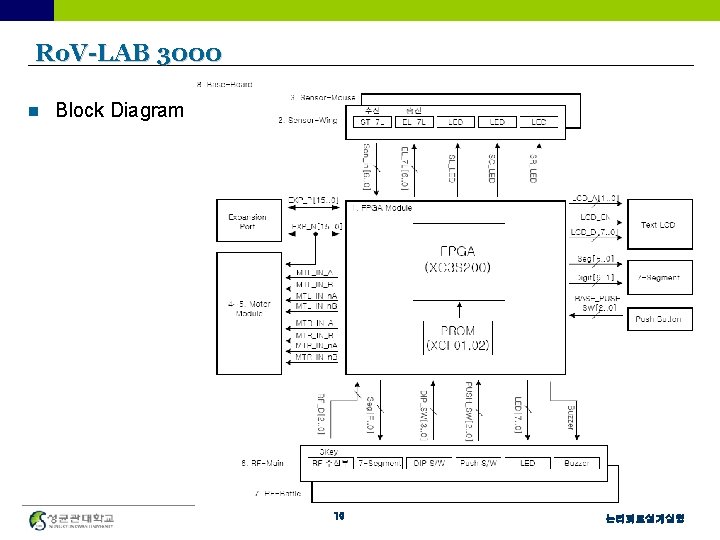

Ro. V-LAB 3000 n Block Diagram 10 논리회로설계실험

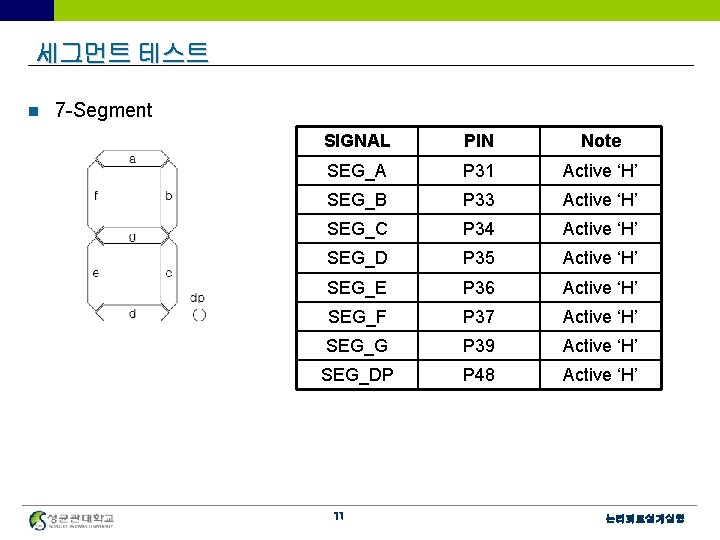

세그먼트 테스트 n 7 -Segment SIGNAL PIN Note SEG_A P 31 Active ‘H’ SEG_B P 33 Active ‘H’ SEG_C P 34 Active ‘H’ SEG_D P 35 Active ‘H’ SEG_E P 36 Active ‘H’ SEG_F P 37 Active ‘H’ SEG_G P 39 Active ‘H’ SEG_DP P 48 Active ‘H’ 11 논리회로설계실험

세그먼트 테스트 n 세그먼트 테스트 동작 DIGIT <= “ 100000”; DIGIT <= “ 001000”; DIGIT <= “ 000010”; SEG <= “ 11111100”; SEG <= “ 0110”; SEG <= “ 11011010”; DIGIT <= “ 000001”; DIGIT <= “ 010000”; DIGIT <= “ 000100”; SEG <= “ 10110110”; SEG <= “ 01100000”; SEG <= “ 11110010”; 14 논리회로설계실험

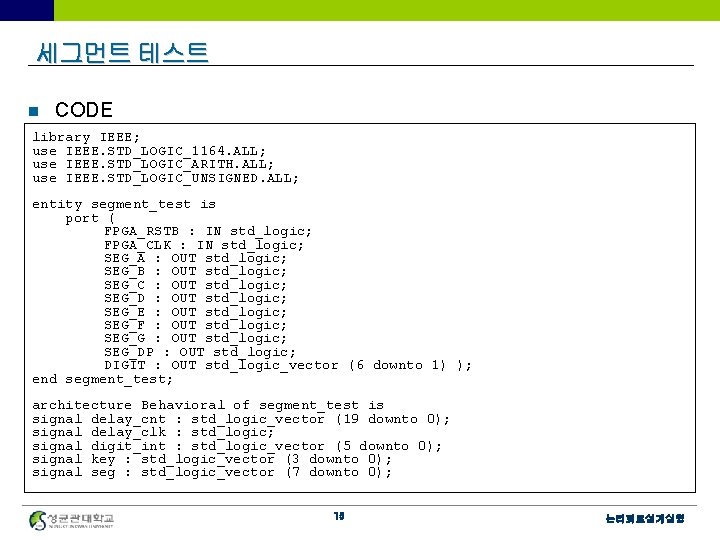

세그먼트 테스트 n CODE library IEEE; use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; entity segment_test is port ( FPGA_RSTB : IN std_logic; FPGA_CLK : IN std_logic; SEG_A : OUT std_logic; SEG_B : OUT std_logic; SEG_C : OUT std_logic; SEG_D : OUT std_logic; SEG_E : OUT std_logic; SEG_F : OUT std_logic; SEG_G : OUT std_logic; SEG_DP : OUT std_logic; DIGIT : OUT std_logic_vector (6 downto 1) ); end segment_test; architecture Behavioral of segment_test is signal delay_cnt : std_logic_vector (19 downto 0); signal delay_clk : std_logic; signal digit_int : std_logic_vector (5 downto 0); signal key : std_logic_vector (3 downto 0); signal seg : std_logic_vector (7 downto 0); 15 논리회로설계실험

세그먼트 테스트 Begin process(FPGA_RSTB, FPGA_CLK) begin if FPGA_RSTB = '0' then delay_cnt <= (others => '0'); elsif rising_edge (FPGA_CLK) then if delay_cnt = X"FFFFF" then delay_cnt <= (others => '0'); delay_clk <= not delay_clk; else delay_cnt <= delay_cnt + 1; delay_clk <= delay_clk; end if; end process; process(FPGA_RSTB, delay_clk) begin if FPGA_RSTB = '0' then digit_int <= "000001"; elsif rising_edge (delay_clk) then digit_int <= digit_int (4 downto 0) & digit_int(5); end if; end process; DIGIT <= digit_int; 16 논리회로설계실험

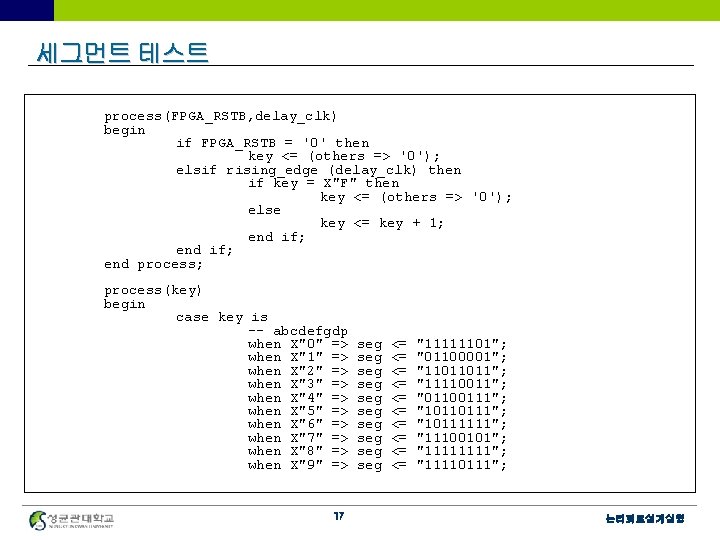

세그먼트 테스트 process(FPGA_RSTB, delay_clk) begin if FPGA_RSTB = '0' then key <= (others => '0'); elsif rising_edge (delay_clk) then if key = X"F" then key <= (others => '0'); else key <= key + 1; end if; end process; process(key) begin case key is -- abcdefgdp when X"0" => when X"1" => when X"2" => when X"3" => when X"4" => when X"5" => when X"6" => when X"7" => when X"8" => when X"9" => 17 seg seg seg <= <= <= "11111101"; "01100001"; "11011011"; "11110011"; "01100111"; "10111111"; "11100101"; "1111"; "11110111"; 논리회로설계실험

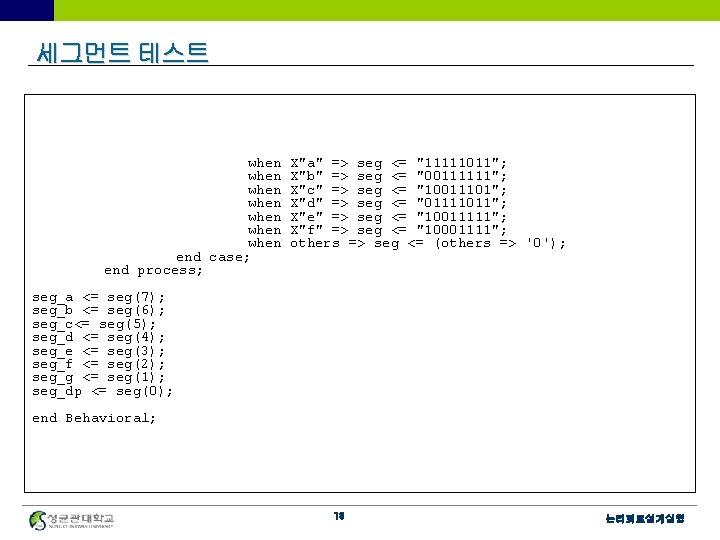

세그먼트 테스트 when when end case; end process; X"a" => seg <= "11111011"; X"b" => seg <= "00111111"; X"c" => seg <= "10011101"; X"d" => seg <= "01111011"; X"e" => seg <= "10011111"; X"f" => seg <= "10001111"; others => seg <= (others => '0'); seg_a <= seg(7); seg_b <= seg(6); seg_c<= seg(5); seg_d <= seg(4); seg_e <= seg(3); seg_f <= seg(2); seg_g <= seg(1); seg_dp <= seg(0); end Behavioral; 18 논리회로설계실험

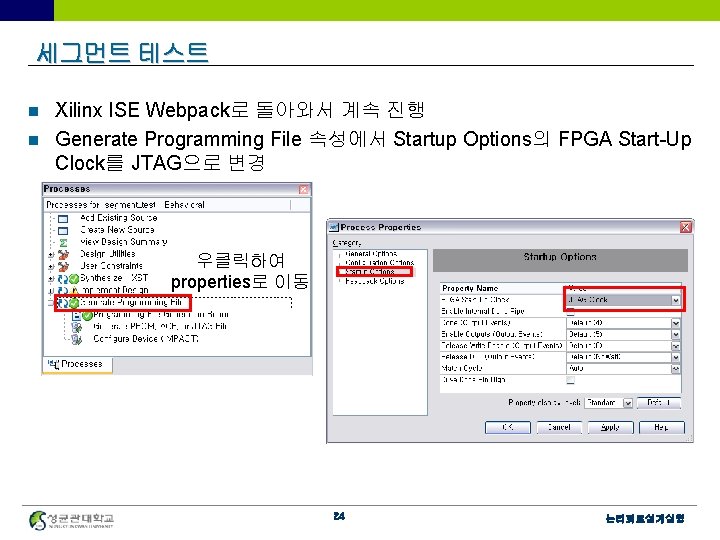

세그먼트 테스트 Xilinx ISE Webpack로 돌아와서 계속 진행 n Generate Programming File 속성에서 Startup Options의 FPGA Start-Up Clock를 JTAG으로 변경 n 우클릭하여 properties로 이동 24 논리회로설계실험

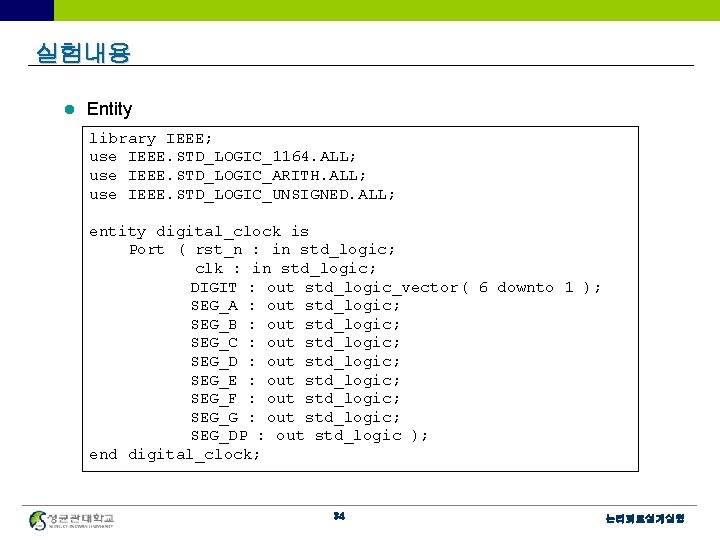

실험내용 l Entity library IEEE; use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; entity digital_clock is Port ( rst_n : in std_logic; clk : in std_logic; DIGIT : out std_logic_vector( 6 downto 1 ); SEG_A : out std_logic; SEG_B : out std_logic; SEG_C : out std_logic; SEG_D : out std_logic; SEG_E : out std_logic; SEG_F : out std_logic; SEG_G : out std_logic; SEG_DP : out std_logic ); end digital_clock; 34 논리회로설계실험

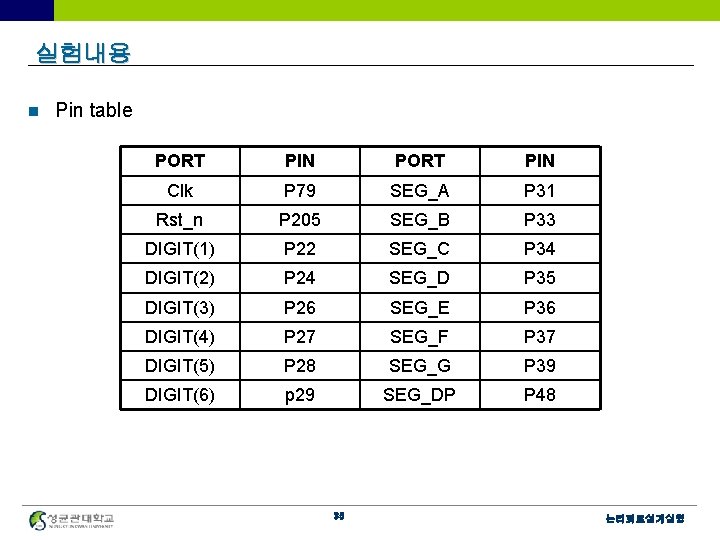

실험내용 n Pin table PORT PIN Clk P 79 SEG_A P 31 Rst_n P 205 SEG_B P 33 DIGIT(1) P 22 SEG_C P 34 DIGIT(2) P 24 SEG_D P 35 DIGIT(3) P 26 SEG_E P 36 DIGIT(4) P 27 SEG_F P 37 DIGIT(5) P 28 SEG_G P 39 DIGIT(6) p 29 SEG_DP P 48 35 논리회로설계실험

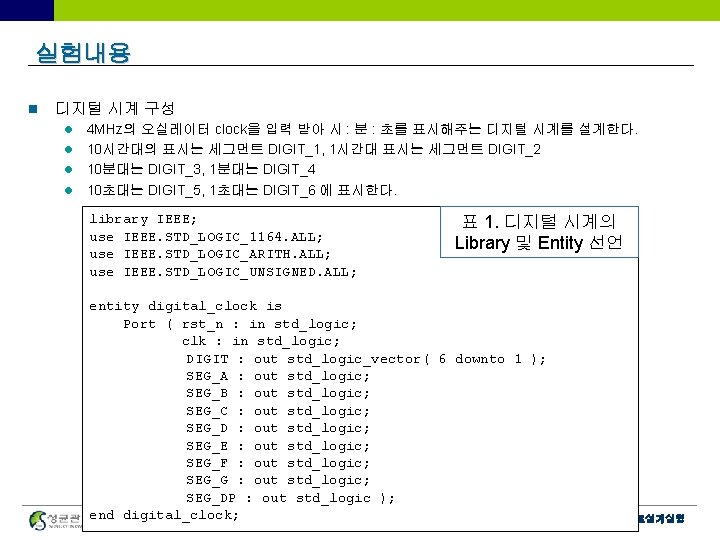

실험내용 n 디지털 시계 구성 4 MHz의 오실레이터 clock을 입력 받아 시 : 분 : 초를 표시해주는 디지털 시계를 설계한다. l 10시간대의 표시는 세그먼트 DIGIT_1, 1시간대 표시는 세그먼트 DIGIT_2 l 10분대는 DIGIT_3, 1분대는 DIGIT_4 l 10초대는 DIGIT_5, 1초대는 DIGIT_6 에 표시한다. l library IEEE; use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; 표 1. 디지털 시계의 Library 및 Entity 선언 entity digital_clock is Port ( rst_n : in std_logic; clk : in std_logic; DIGIT : out std_logic_vector( 6 downto 1 ); SEG_A : out std_logic; SEG_B : out std_logic; SEG_C : out std_logic; SEG_D : out std_logic; SEG_E : out std_logic; SEG_F : out std_logic; SEG_G : out std_logic; SEG_DP : out std_logic ); end digital_clock; 36 논리회로설계실험

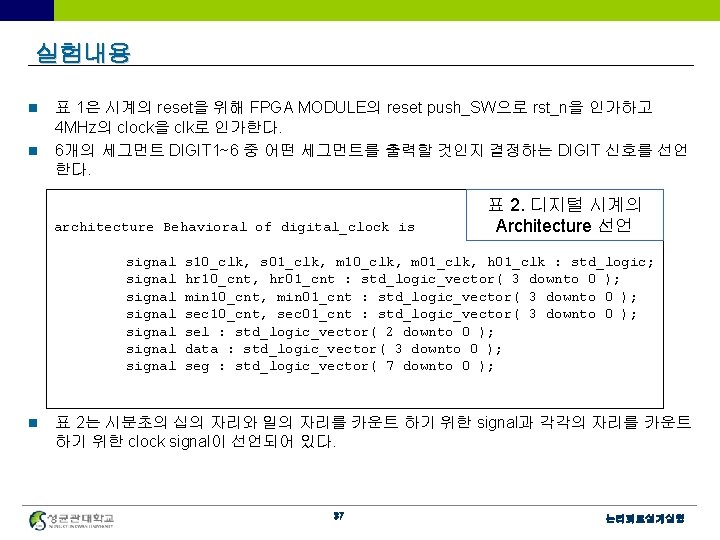

실험내용 n n 표 1은 시계의 reset을 위해 FPGA MODULE의 reset push_SW으로 rst_n을 인가하고 4 MHz의 clock을 clk로 인가한다. 6개의 세그먼트 DIGIT 1~6 중 어떤 세그먼트를 출력할 것인지 결정하는 DIGIT 신호를 선언 한다. architecture Behavioral of digital_clock is signal signal n 표 2. 디지털 시계의 Architecture 선언 s 10_clk, s 01_clk, m 10_clk, m 01_clk, h 01_clk : std_logic; hr 10_cnt, hr 01_cnt : std_logic_vector( 3 downto 0 ); min 10_cnt, min 01_cnt : std_logic_vector( 3 downto 0 ); sec 10_cnt, sec 01_cnt : std_logic_vector( 3 downto 0 ); sel : std_logic_vector( 2 downto 0 ); data : std_logic_vector( 3 downto 0 ); seg : std_logic_vector( 7 downto 0 ); 표 2는 시분초의 십의 자리와 일의 자리를 카운트 하기 위한 signal과 각각의 자리를 카운트 하기 위한 clock signal이 선언되어 있다. 37 논리회로설계실험

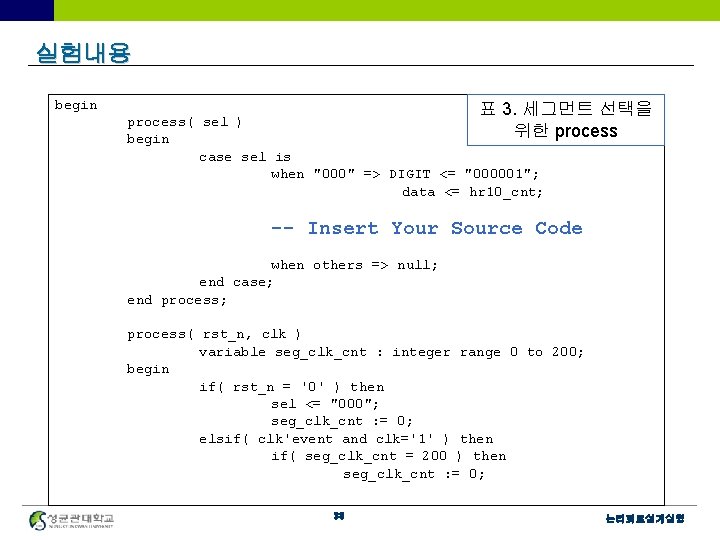

실험내용 begin 표 3. 세그먼트 선택을 process( sel ) 위한 begin case sel is when "000" => DIGIT <= "000001"; data <= hr 10_cnt; -- Insert Your Source Code when others => null; end case; end process; process( rst_n, clk ) variable seg_clk_cnt : integer range 0 to 200; begin if( rst_n = '0' ) then sel <= "000"; seg_clk_cnt : = 0; elsif( clk'event and clk='1' ) then if( seg_clk_cnt = 200 ) then seg_clk_cnt : = 0; 38 논리회로설계실험

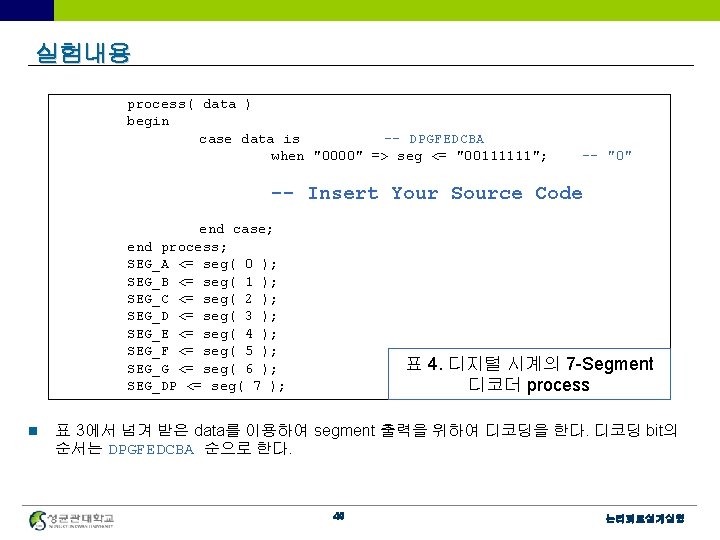

실험내용 process( data ) begin case data is -- DPGFEDCBA when "0000" => seg <= "00111111"; -- "0" -- Insert Your Source Code end case; end process; SEG_A <= seg( 0 ); SEG_B <= seg( 1 ); SEG_C <= seg( 2 ); SEG_D <= seg( 3 ); SEG_E <= seg( 4 ); SEG_F <= seg( 5 ); SEG_G <= seg( 6 ); SEG_DP <= seg( 7 ); n 표 4. 디지털 시계의 7 -Segment 디코더 process 표 3에서 넘겨 받은 data를 이용하여 segment 출력을 위하여 디코딩을 한다. 디코딩 bit의 순서는 DPGFEDCBA 순으로 한다. 40 논리회로설계실험

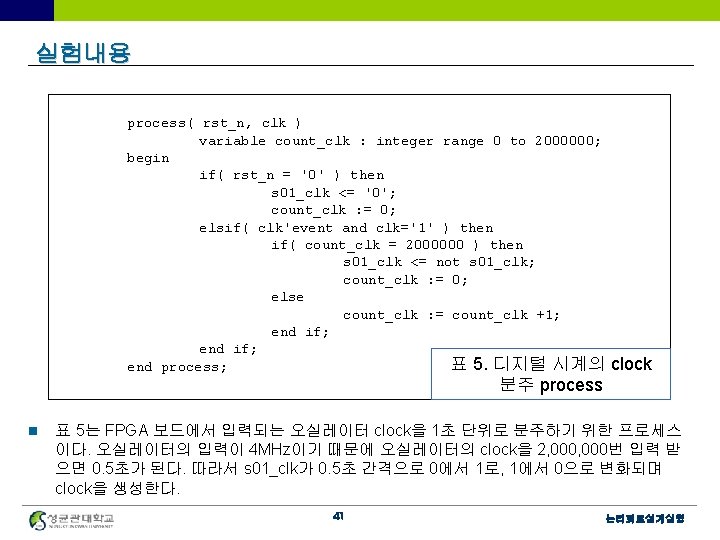

실험내용 process( rst_n, clk ) variable count_clk : integer range 0 to 2000000; begin if( rst_n = '0' ) then s 01_clk <= '0'; count_clk : = 0; elsif( clk'event and clk='1' ) then if( count_clk = 2000000 ) then s 01_clk <= not s 01_clk; count_clk : = 0; else count_clk : = count_clk +1; end if; 표 5. 디지털 시계의 end process; clock 분주 process n 표 5는 FPGA 보드에서 입력되는 오실레이터 clock을 1초 단위로 분주하기 위한 프로세스 이다. 오실레이터의 입력이 4 MHz이기 때문에 오실레이터의 clock을 2, 000번 입력 받 으면 0. 5초가 된다. 따라서 s 01_clk가 0. 5초 간격으로 0에서 1로, 1에서 0으로 변화되며 clock을 생성한다. 41 논리회로설계실험

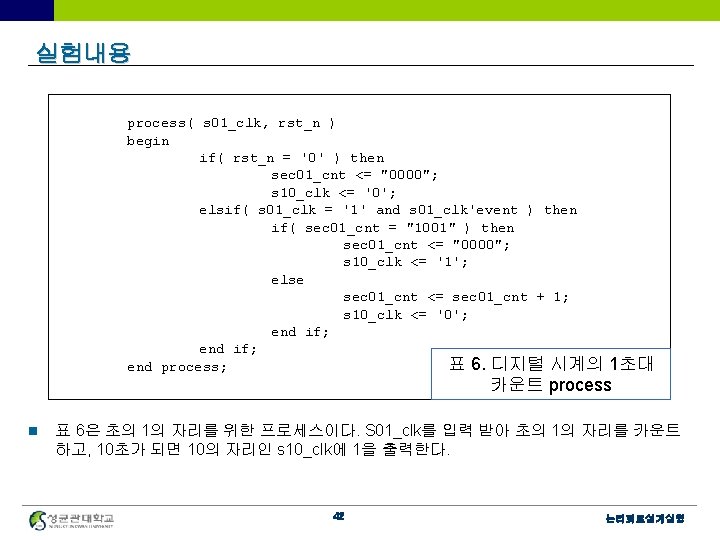

실험내용 process( s 01_clk, rst_n ) begin if( rst_n = '0' ) then sec 01_cnt <= "0000"; s 10_clk <= '0'; elsif( s 01_clk = '1' and s 01_clk'event ) then if( sec 01_cnt = "1001" ) then sec 01_cnt <= "0000"; s 10_clk <= '1'; else sec 01_cnt <= sec 01_cnt + 1; s 10_clk <= '0'; end if; 표 6. 디지털 시계의 end process; 1초대 카운트 process n 표 6은 초의 1의 자리를 위한 프로세스이다. S 01_clk를 입력 받아 초의 1의 자리를 카운트 하고, 10초가 되면 10의 자리인 s 10_clk에 1을 출력한다. 42 논리회로설계실험

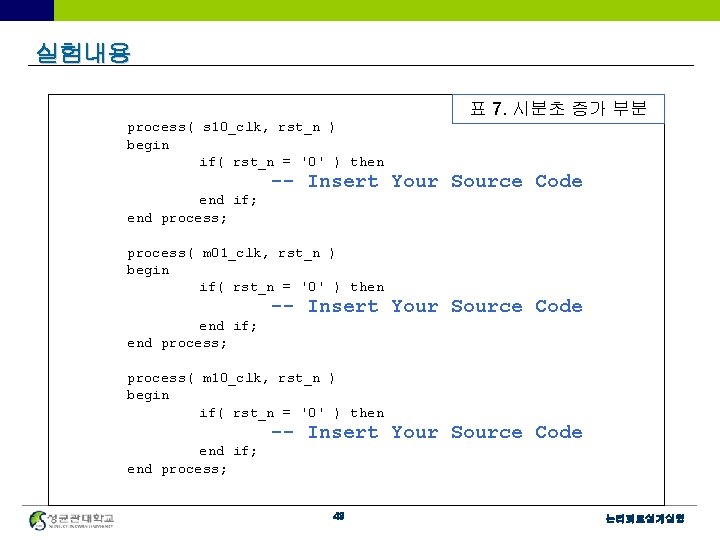

실험내용 표 7. 시분초 증가 부분 process( s 10_clk, rst_n ) begin if( rst_n = '0' ) then end if; end process; -- Insert Your Source Code process( m 01_clk, rst_n ) begin if( rst_n = '0' ) then end if; end process; -- Insert Your Source Code process( m 10_clk, rst_n ) begin if( rst_n = '0' ) then end if; end process; -- Insert Your Source Code 43 논리회로설계실험

- Slides: 44