RMO 4 C2 A LowNoise 40 GSs ContinuousTime

- Slides: 20

RMO 4 C-2 A Low-Noise 40 -GS/s Continuous-Time Bandpass ΔΣ ADC Centered at 2 GHz Theo Chalvatzis and Sorin P. Voinigescu The Edward S. Rogers Sr. Department of Electrical and Computer Engineering University of Toronto, Canada RFIC - San Francisco June 11 -13, 2006

Outline • Motivation • ADC system level architecture • Circuit design • Measurements • Conclusion RFIC - San Francisco June 11 -13, 2006 2

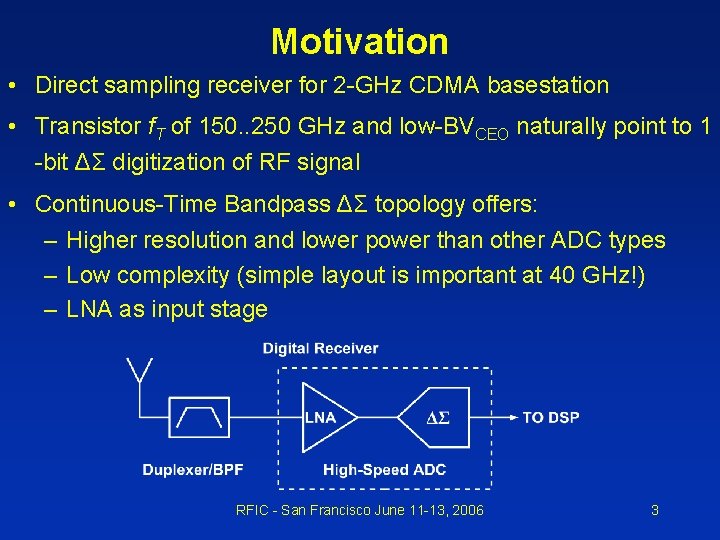

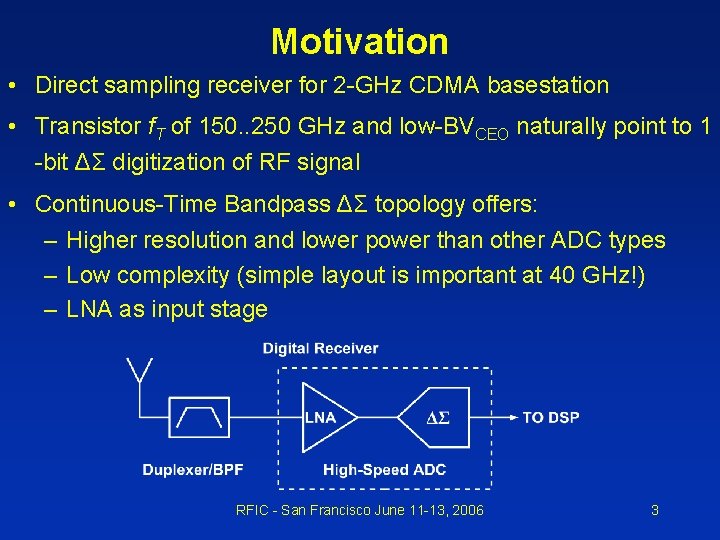

Motivation • Direct sampling receiver for 2 -GHz CDMA basestation • Transistor f. T of 150. . 250 GHz and low-BVCEO naturally point to 1 -bit ΔΣ digitization of RF signal • Continuous-Time Bandpass ΔΣ topology offers: – Higher resolution and lower power than other ADC types – Low complexity (simple layout is important at 40 GHz!) – LNA as input stage RFIC - San Francisco June 11 -13, 2006 3

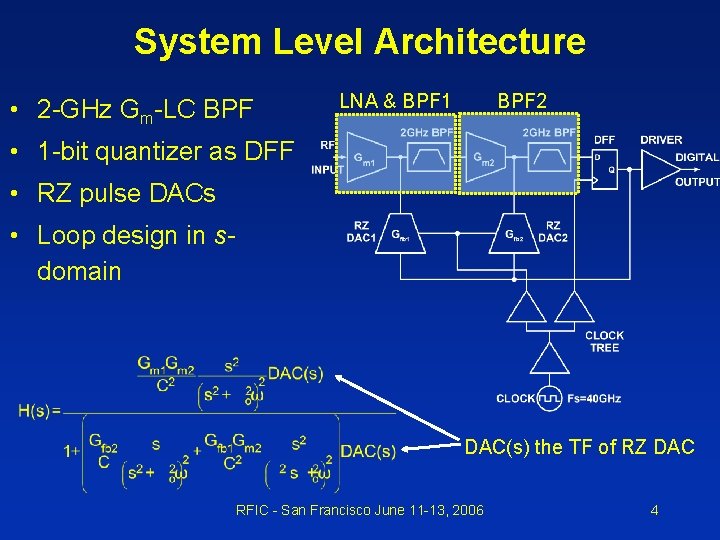

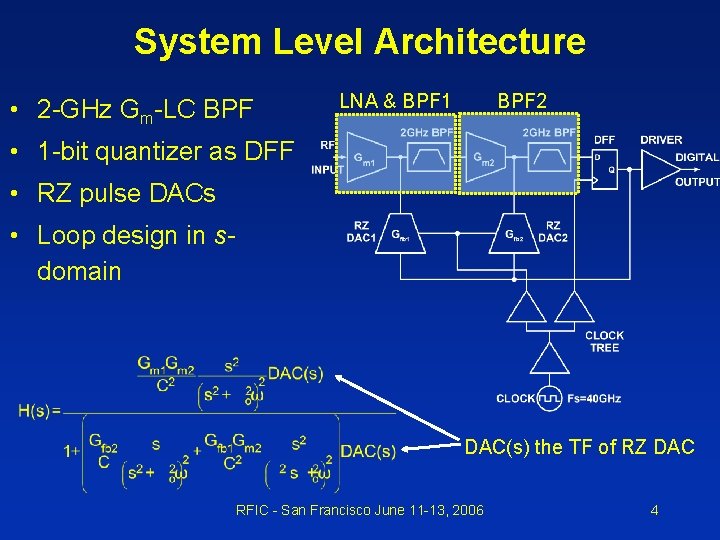

System Level Architecture • 2 -GHz Gm-LC BPF 2 LNA & BPF 1 • 1 -bit quantizer as DFF • RZ pulse DACs • Loop design in sdomain DAC(s) the TF of RZ DAC RFIC - San Francisco June 11 -13, 2006 4

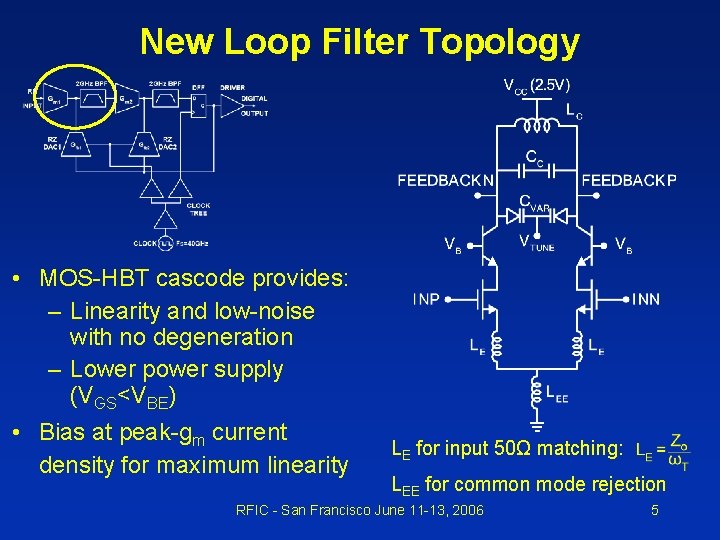

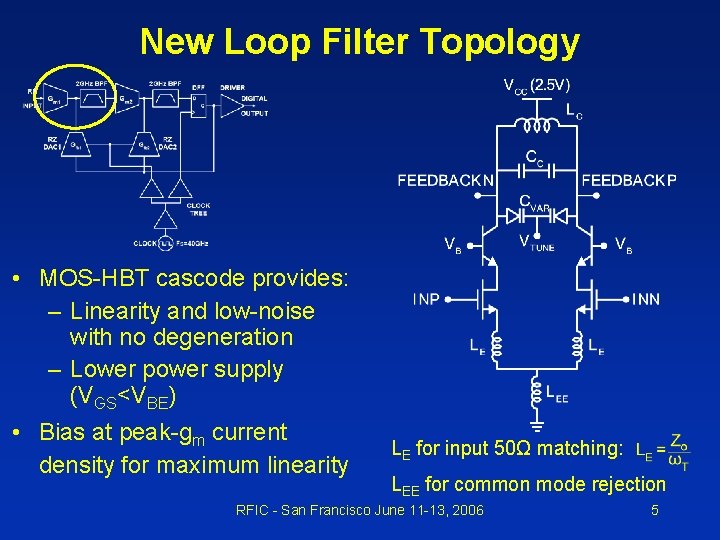

New Loop Filter Topology • MOS-HBT cascode provides: – Linearity and low-noise with no degeneration – Lower power supply (VGS<VBE) • Bias at peak-gm current density for maximum linearity LE for input 50Ω matching: LEE for common mode rejection RFIC - San Francisco June 11 -13, 2006 5

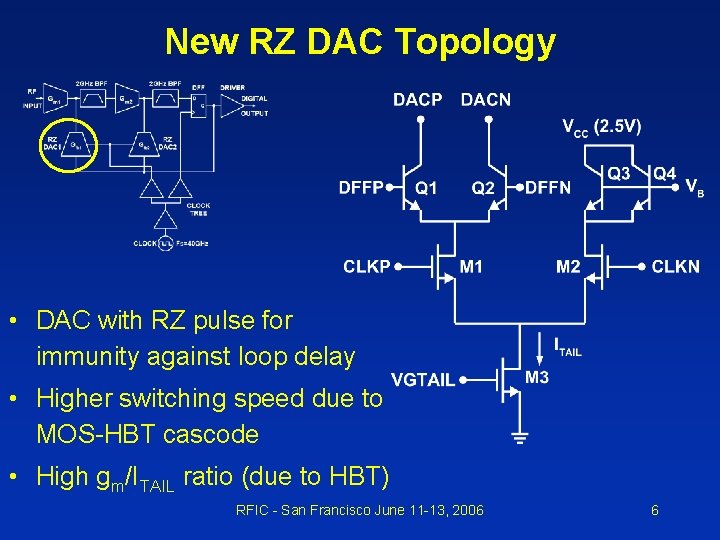

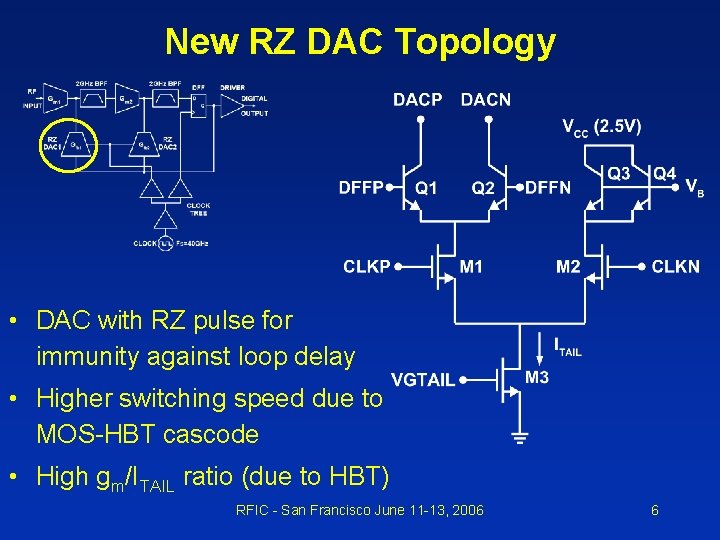

New RZ DAC Topology • DAC with RZ pulse for immunity against loop delay • Higher switching speed due to MOS-HBT cascode • High gm/ITAIL ratio (due to HBT) RFIC - San Francisco June 11 -13, 2006 6

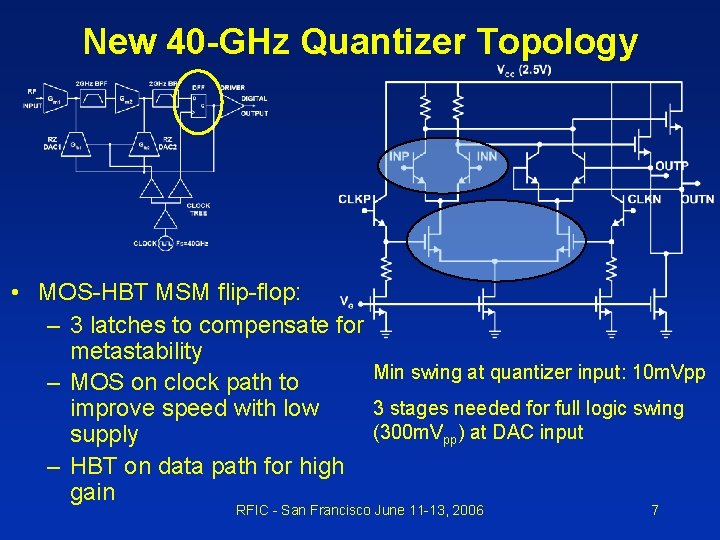

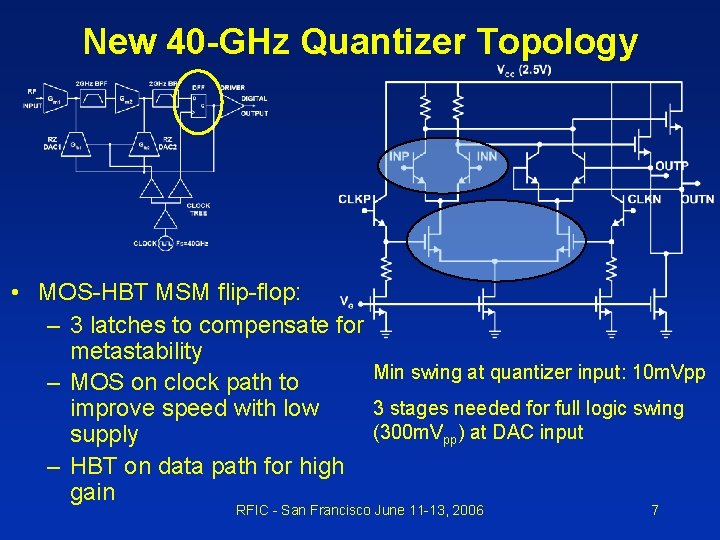

New 40 -GHz Quantizer Topology • MOS-HBT MSM flip-flop: – 3 latches to compensate for metastability Min swing at quantizer input: 10 m. Vpp – MOS on clock path to 3 stages needed for full logic swing improve speed with low (300 m. Vpp) at DAC input supply – HBT on data path for high gain RFIC - San Francisco June 11 -13, 2006 7

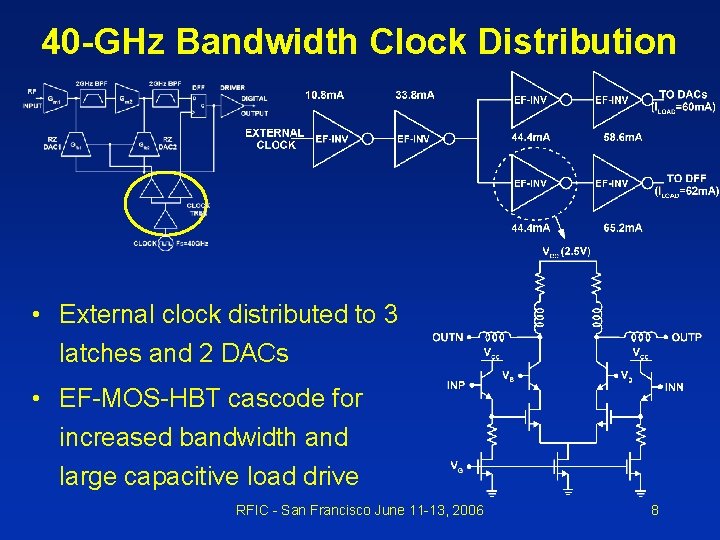

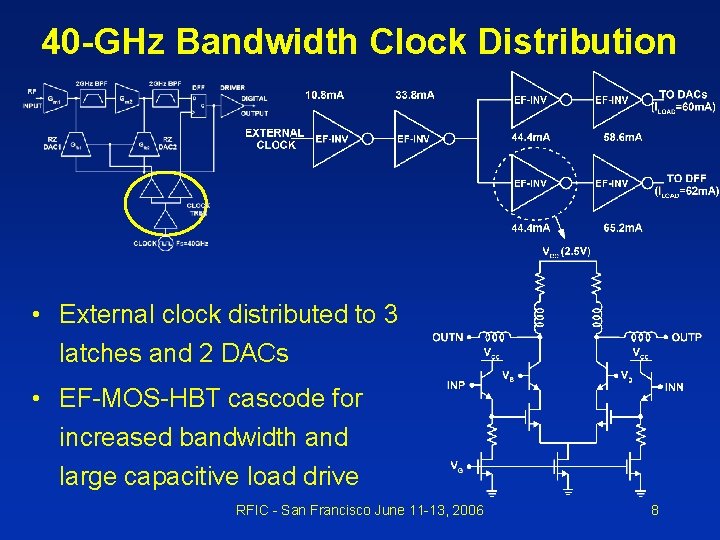

40 -GHz Bandwidth Clock Distribution • External clock distributed to 3 latches and 2 DACs • EF-MOS-HBT cascode for increased bandwidth and large capacitive load drive RFIC - San Francisco June 11 -13, 2006 8

Fabrication and Characterization of loop filter breakout and ADC RFIC - San Francisco June 11 -13, 2006 9

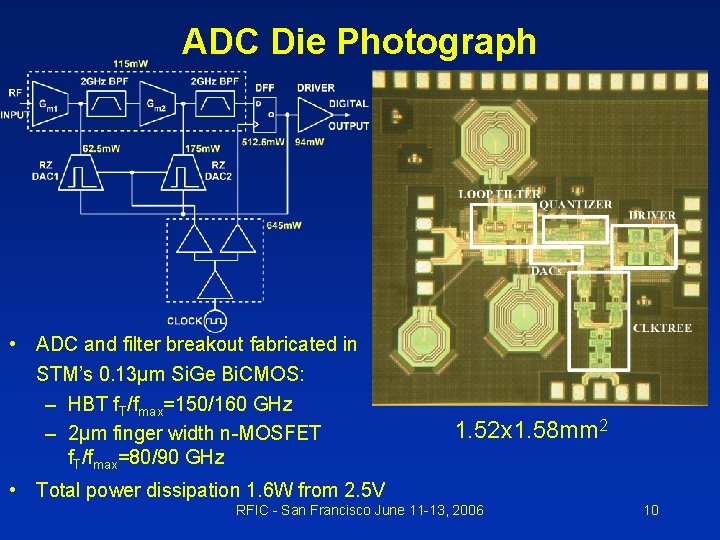

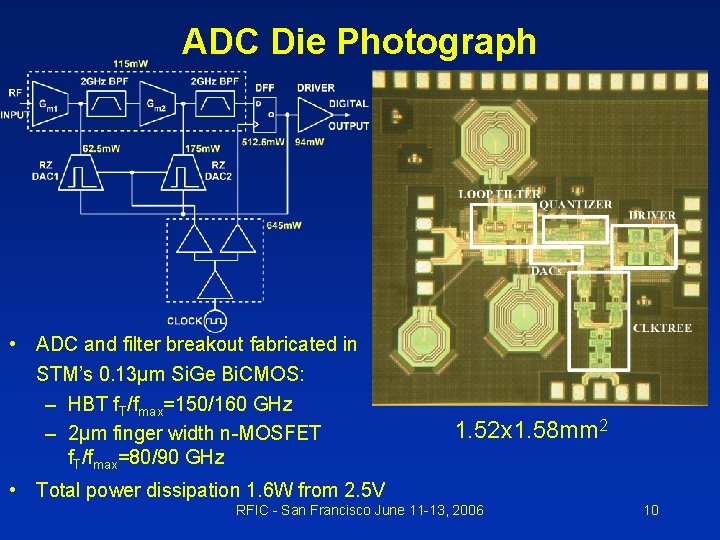

ADC Die Photograph • ADC and filter breakout fabricated in STM’s 0. 13μm Si. Ge Bi. CMOS: – HBT f. T/fmax=150/160 GHz – 2μm finger width n-MOSFET f. T/fmax=80/90 GHz 1. 52 x 1. 58 mm 2 • Total power dissipation 1. 6 W from 2. 5 V RFIC - San Francisco June 11 -13, 2006 10

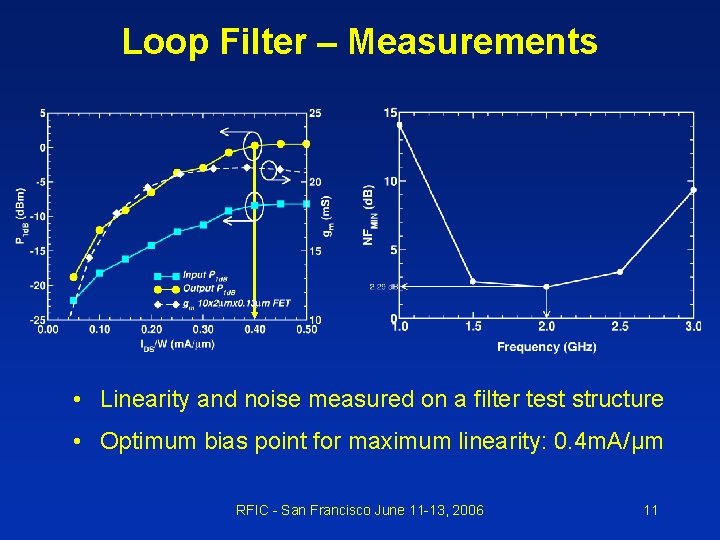

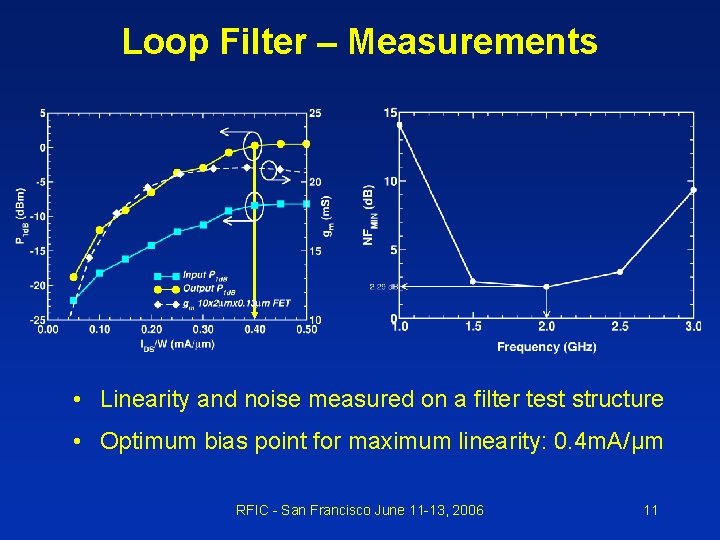

Loop Filter – Measurements • Linearity and noise measured on a filter test structure • Optimum bias point for maximum linearity: 0. 4 m. A/μm RFIC - San Francisco June 11 -13, 2006 11

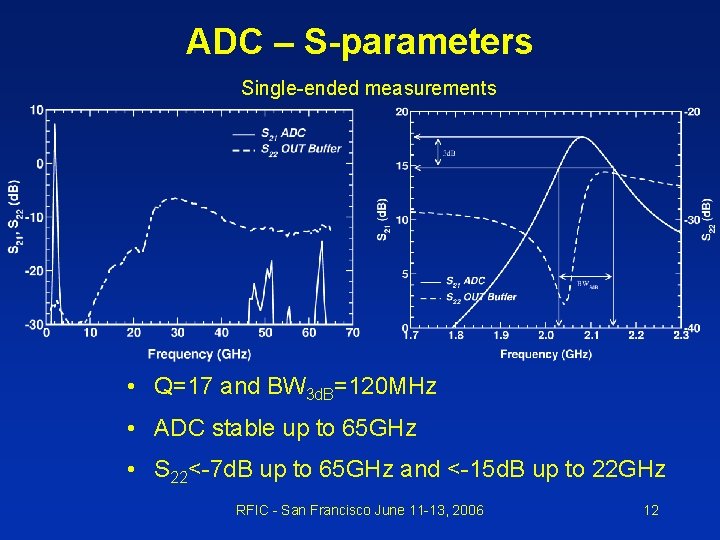

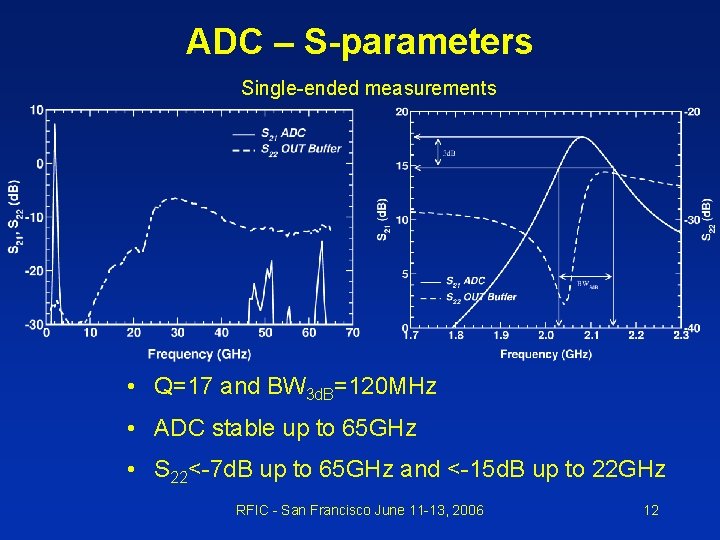

ADC – S-parameters Single-ended measurements • Q=17 and BW 3 d. B=120 MHz • ADC stable up to 65 GHz • S 22<-7 d. B up to 65 GHz and <-15 d. B up to 22 GHz RFIC - San Francisco June 11 -13, 2006 12

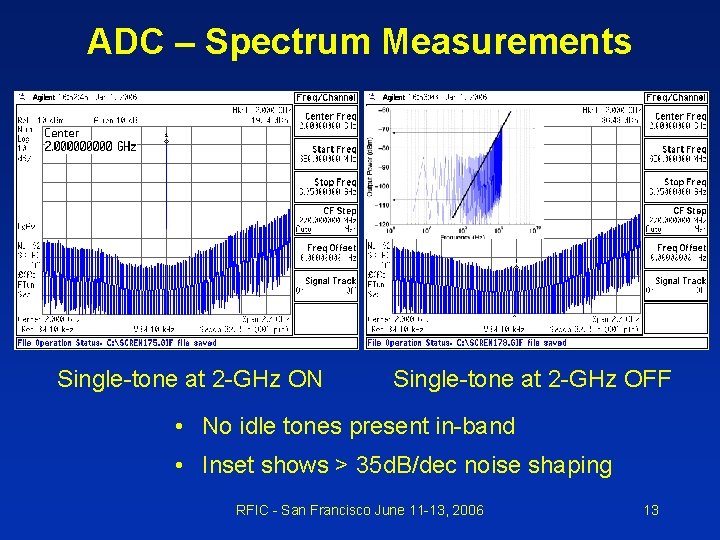

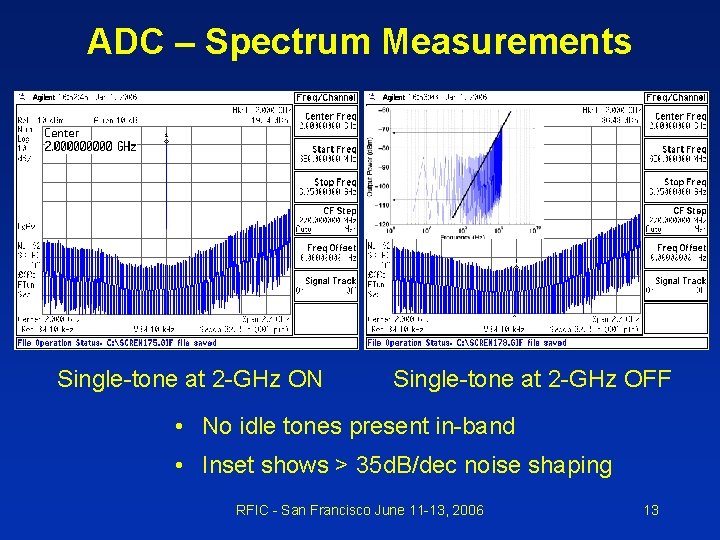

ADC – Spectrum Measurements Single-tone at 2 -GHz ON Single-tone at 2 -GHz OFF • No idle tones present in-band • Inset shows > 35 d. B/dec noise shaping RFIC - San Francisco June 11 -13, 2006 13

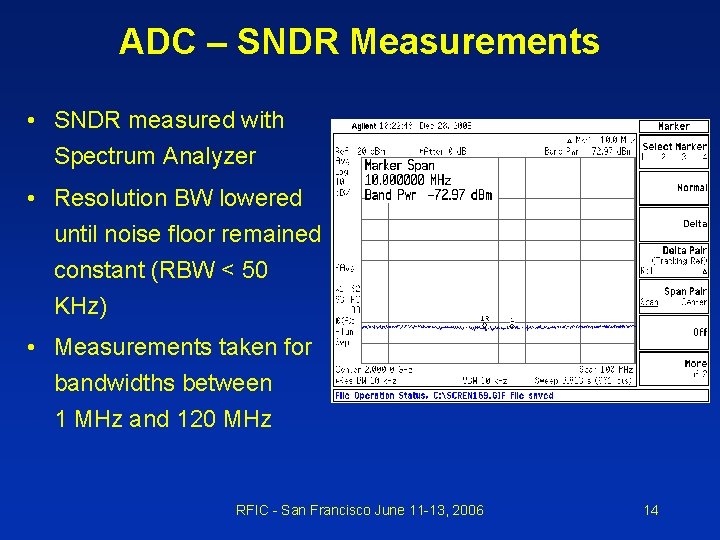

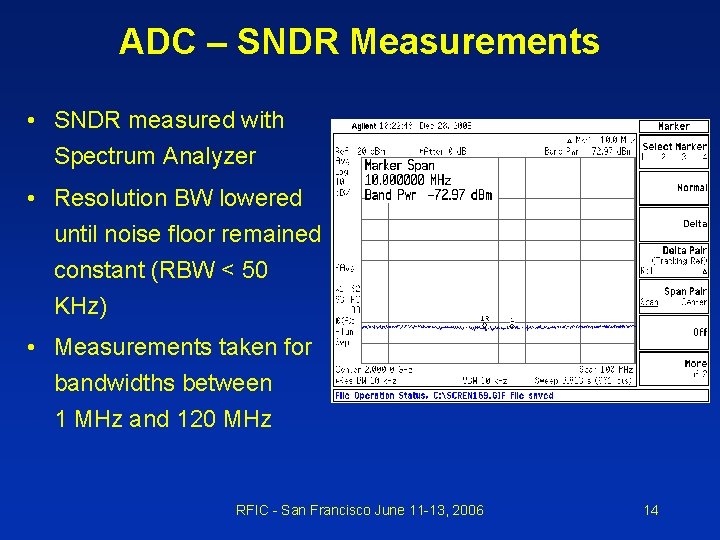

ADC – SNDR Measurements • SNDR measured with Spectrum Analyzer • Resolution BW lowered until noise floor remained constant (RBW < 50 KHz) • Measurements taken for bandwidths between 1 MHz and 120 MHz RFIC - San Francisco June 11 -13, 2006 14

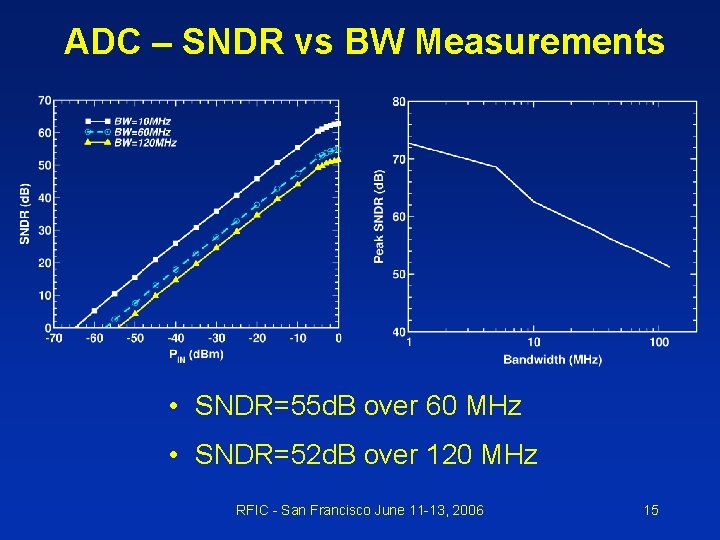

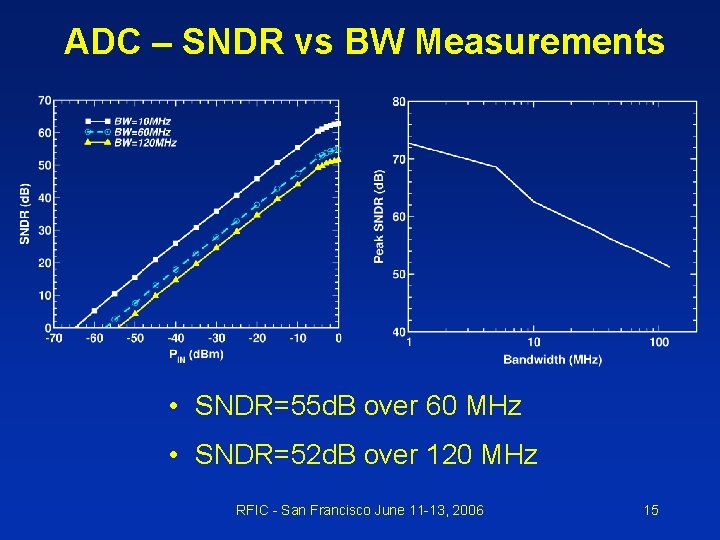

ADC – SNDR vs BW Measurements • SNDR=55 d. B over 60 MHz • SNDR=52 d. B over 120 MHz RFIC - San Francisco June 11 -13, 2006 15

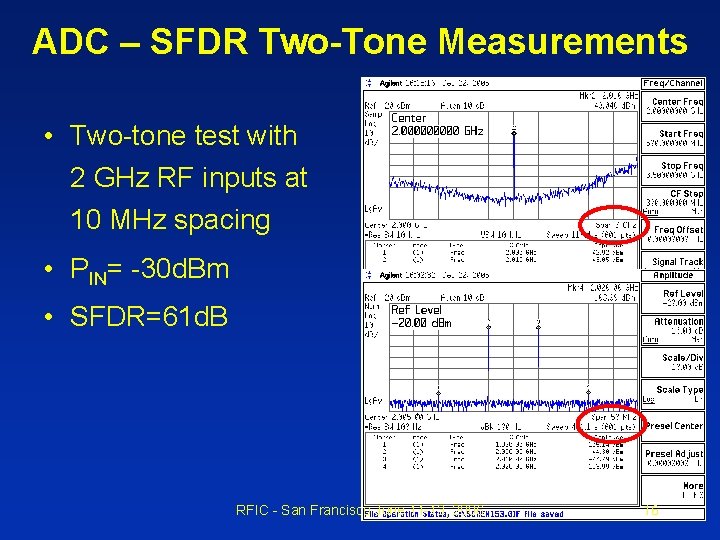

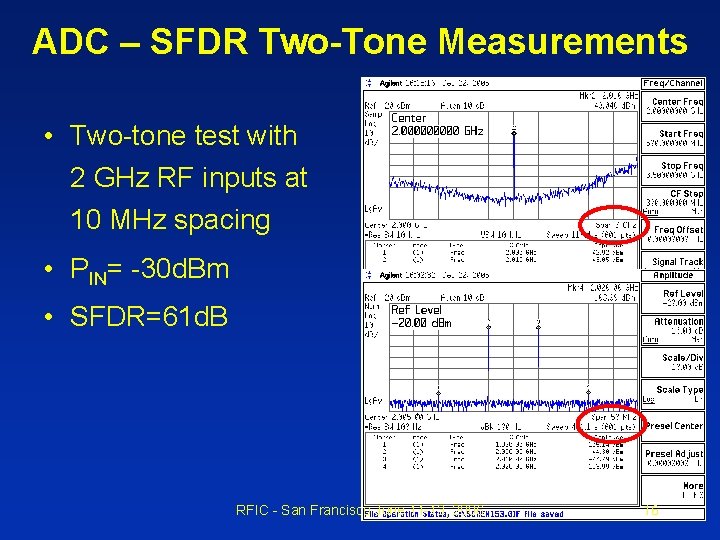

ADC – SFDR Two-Tone Measurements • Two-tone test with 2 GHz RF inputs at 10 MHz spacing • PIN= -30 d. Bm • SFDR=61 d. B RFIC - San Francisco June 11 -13, 2006 16

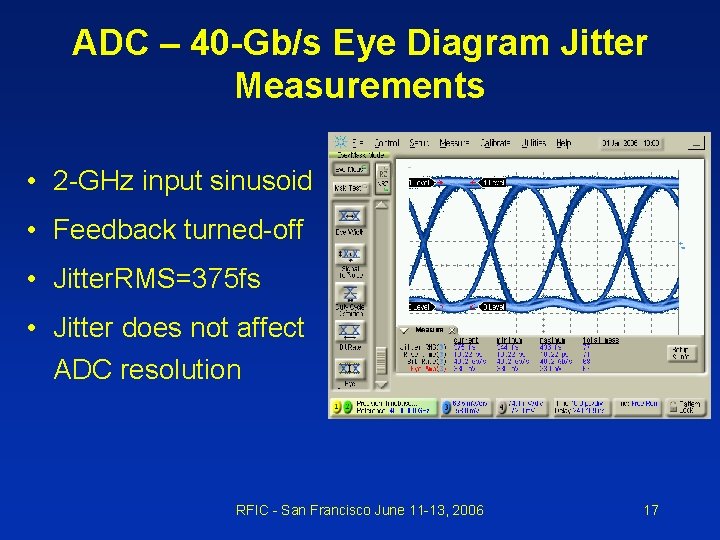

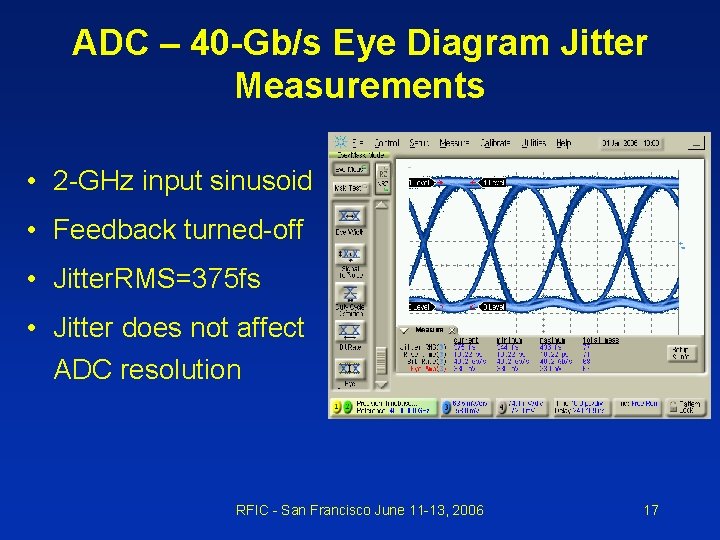

ADC – 40 -Gb/s Eye Diagram Jitter Measurements • 2 -GHz input sinusoid • Feedback turned-off • Jitter. RMS=375 fs • Jitter does not affect ADC resolution RFIC - San Francisco June 11 -13, 2006 17

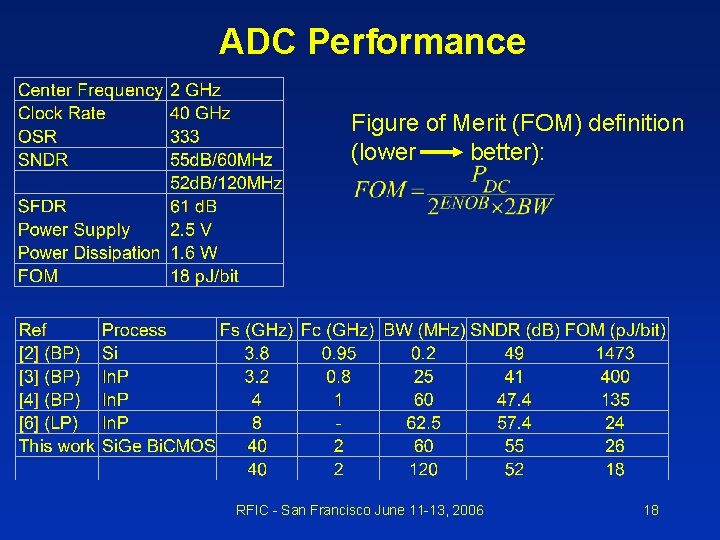

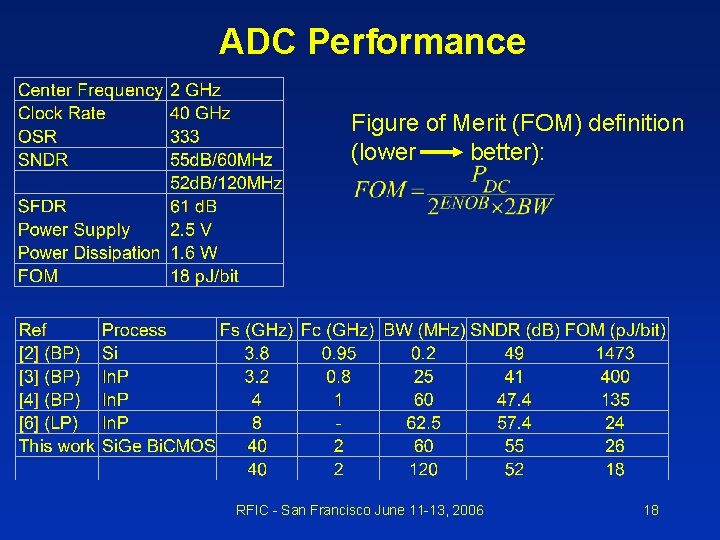

ADC Performance Figure of Merit (FOM) definition (lower better): RFIC - San Francisco June 11 -13, 2006 18

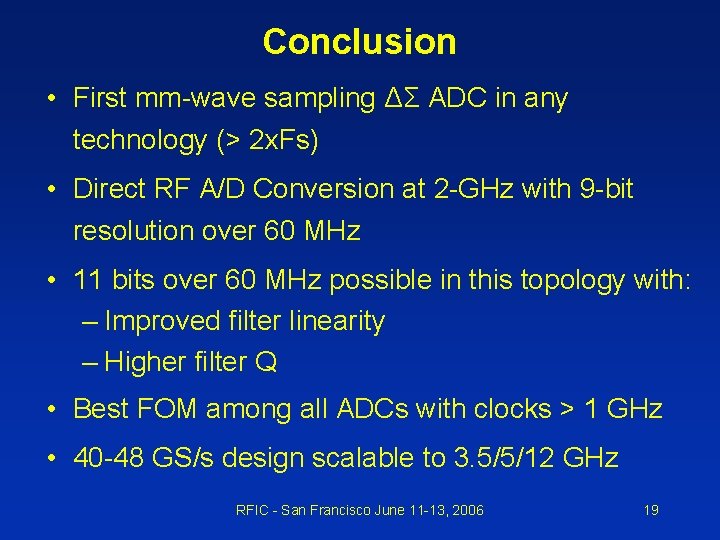

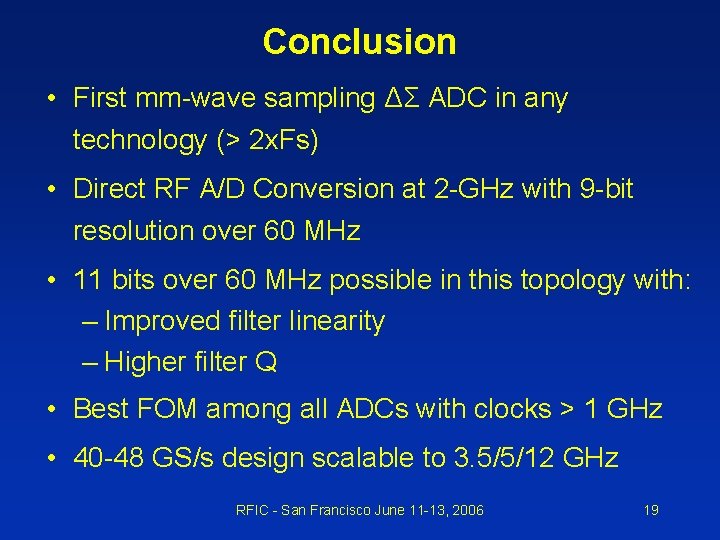

Conclusion • First mm-wave sampling ΔΣ ADC in any technology (> 2 x. Fs) • Direct RF A/D Conversion at 2 -GHz with 9 -bit resolution over 60 MHz • 11 bits over 60 MHz possible in this topology with: – Improved filter linearity – Higher filter Q • Best FOM among all ADCs with clocks > 1 GHz • 40 -48 GS/s design scalable to 3. 5/5/12 GHz RFIC - San Francisco June 11 -13, 2006 19

Acknowledgements • Eric Gagnon and Morris Repeta for system performance specifications • Nortel Networks for funding support • STMicroelectronics for chip fabrication • ECTI for lab access • CMC for CAD tools RFIC - San Francisco June 11 -13, 2006 20