Rise and rise again until lambs become lions

Rise and rise again until lambs become lions Logic Design LAB 8 授課老師:伍紹勳 課程助教:邱麟凱、江長庭

Outlines Sequential logic circuits – Memory and Clock SR latch D Flip-Flop Lab Rise and rise again until lambs become lions

Sequential logic circuits Rise and rise again until lambs become lions Combinational logic circuits – depends only on current inputs Sequential logic circuits – depends on past and current inputs Memory and Clock!!

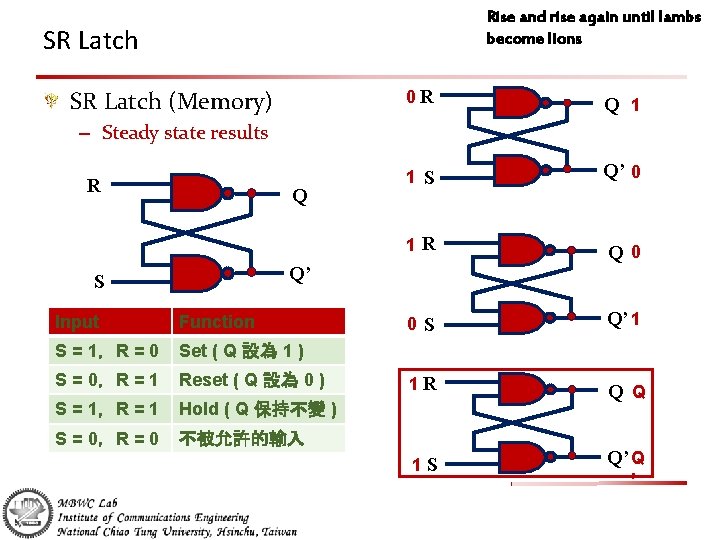

Rise and rise again until lambs become lions SR Latch (Memory) 0 R Q 1 1 S Q’ 0 1 R Q 0 0 S Q’ 1 1 R QQ 1 S Q’ Q – Steady state results R Q Q’ S Input Function S = 1,R = 0 Set ( Q 設為 1 ) S = 0,R = 1 Reset ( Q 設為 0 ) S = 1,R = 1 Hold ( Q 保持不變 ) S = 0,R = 0 不被允許的輸入 ’

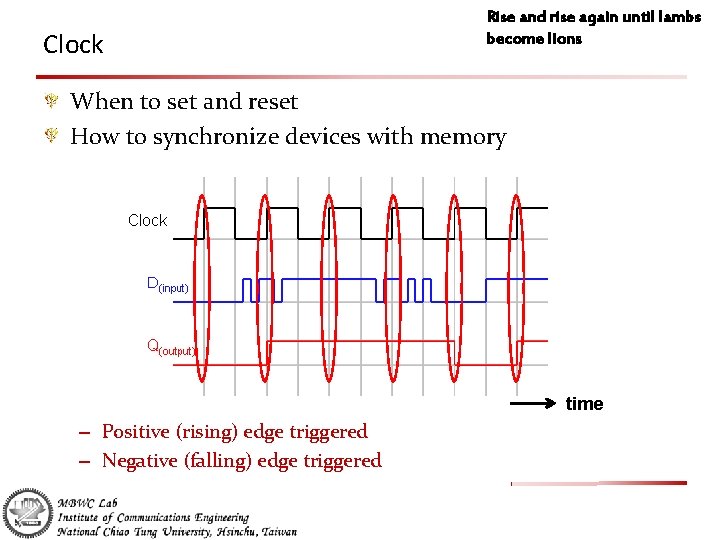

Clock Rise and rise again until lambs become lions When to set and reset How to synchronize devices with memory time – Positive (rising) edge triggered – Negative (falling) edge triggered

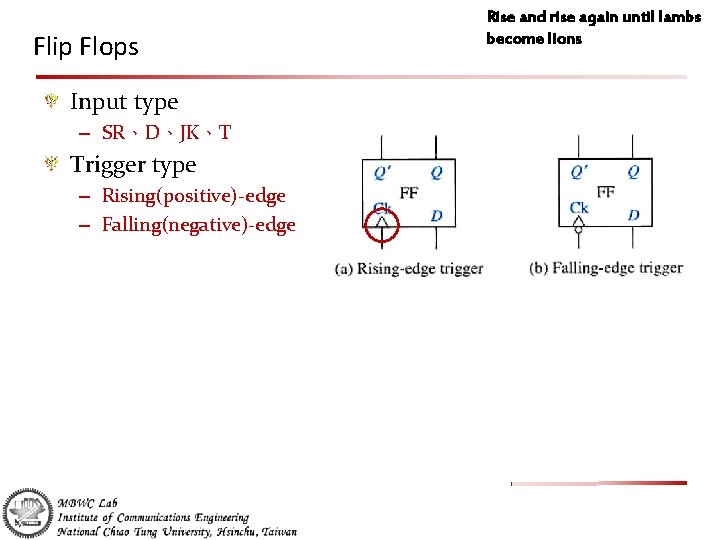

Flip Flops Input type – SR、D、JK、T Trigger type – Rising(positive)-edge – Falling(negative)-edge Rise and rise again until lambs become lions

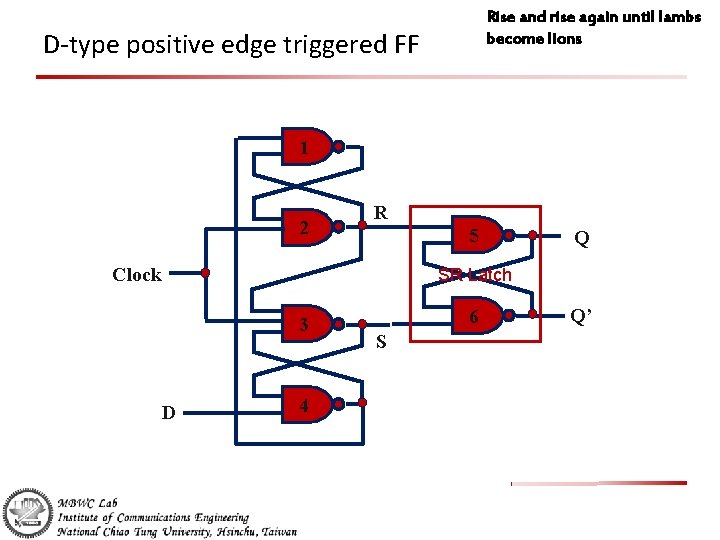

Rise and rise again until lambs become lions D-type positive edge triggered FF 1 2 R 5 Clock SR Latch 3 D Q 4 6 S Q’

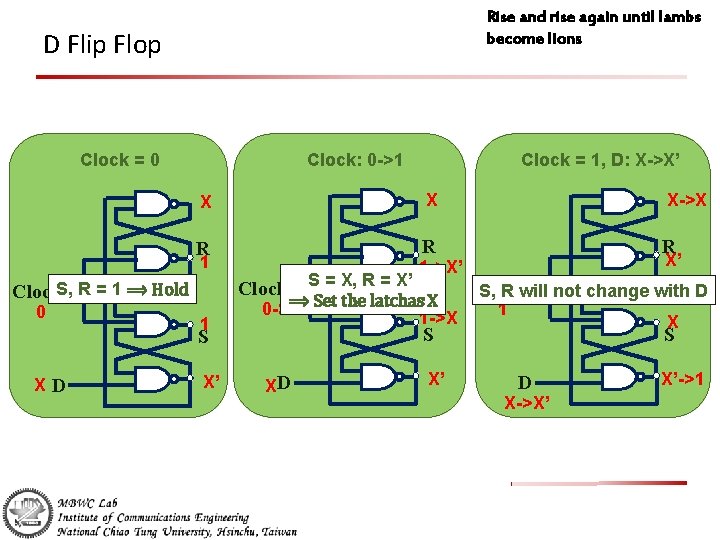

Rise and rise again until lambs become lions D Flip Flop Clock = 0 Clock: 0 ->1 X X X->X R R R 1 1 S = X, R = X’ ⟹ Set the latchas X 0 ->1 1 ->X X’ XD S XD X’ 1 ->X’ Clock. S, R = 1 ⟹ Hold 0 Clock = 1, D: X->X’ Clock S, R will not change with D 1 X S X’ S D X->X’ X’->1

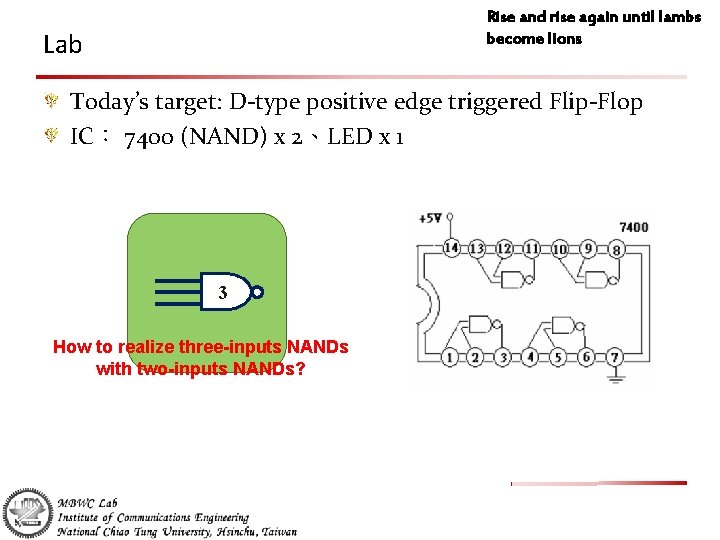

Rise and rise again until lambs become lions Lab Today’s target: D-type positive edge triggered Flip-Flop IC: 7400 (NAND) x 2、LED x 1 3 How to realize three-inputs NANDs with two-inputs NANDs?

- Slides: 9