RIEPILOGO GENERALE Sistemi Elettronici Programmabili 1 Very Large

RIEPILOGO GENERALE Sistemi Elettronici Programmabili 1

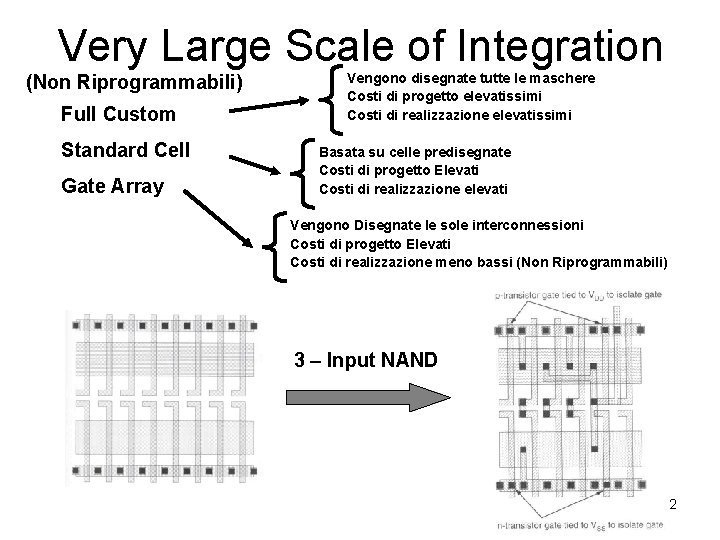

Very Large Scale of Integration (Non Riprogrammabili) Full Custom Standard Cell Gate Array Vengono disegnate tutte le maschere Costi di progetto elevatissimi Costi di realizzazione elevatissimi Basata su celle predisegnate Costi di progetto Elevati Costi di realizzazione elevati Vengono Disegnate le sole interconnessioni Costi di progetto Elevati Costi di realizzazione meno bassi (Non Riprogrammabili) 3 – Input NAND 2

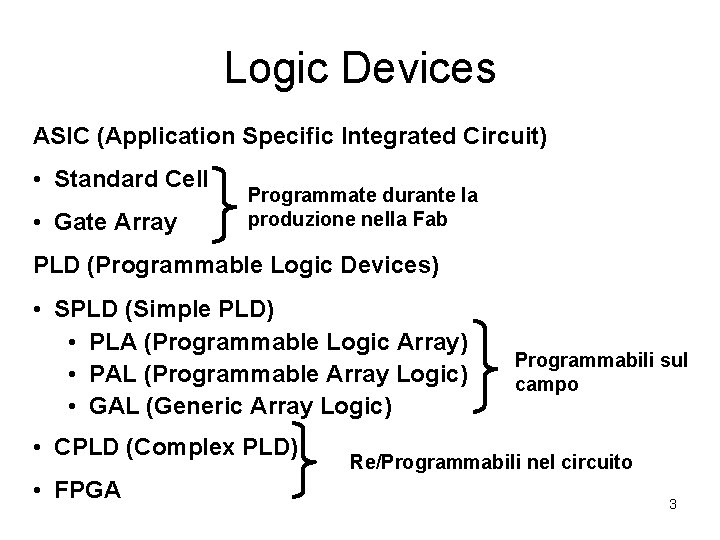

Logic Devices ASIC (Application Specific Integrated Circuit) • Standard Cell • Gate Array Programmate durante la produzione nella Fab PLD (Programmable Logic Devices) • SPLD (Simple PLD) • PLA (Programmable Logic Array) • PAL (Programmable Array Logic) • GAL (Generic Array Logic) • CPLD (Complex PLD) • FPGA Programmabili sul campo Re/Programmabili nel circuito 3

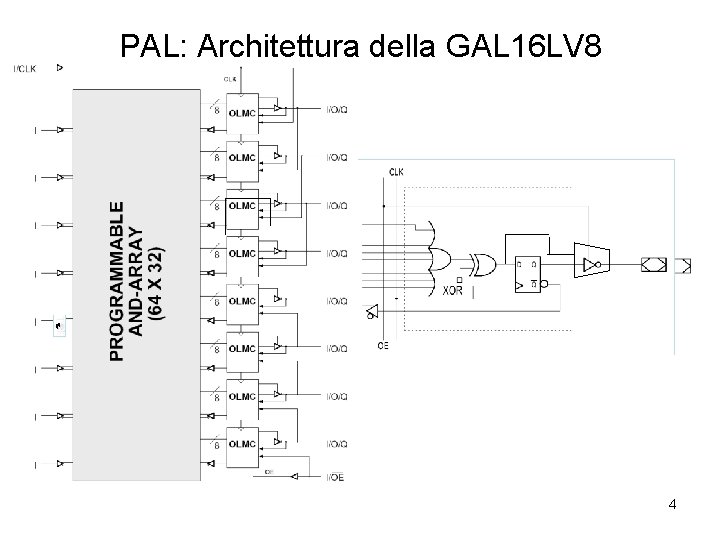

PAL: Architettura della GAL 16 LV 8 Output Logic Macro Cell 4

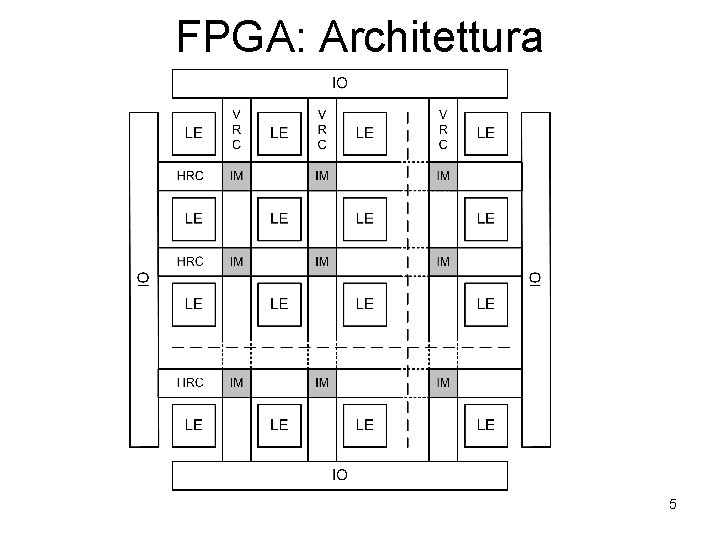

FPGA: Architettura 5

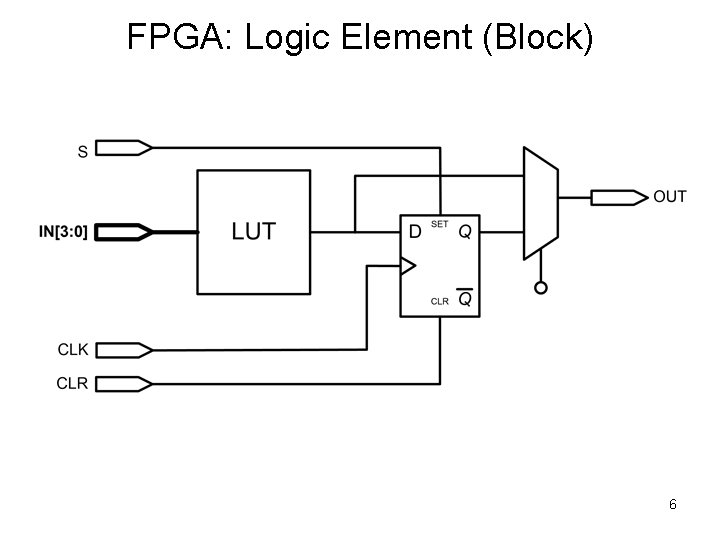

FPGA: Logic Element (Block) 6

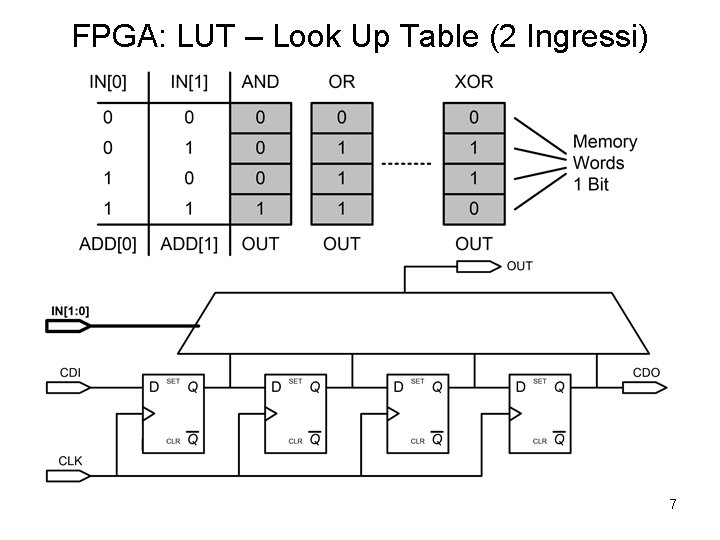

FPGA: LUT – Look Up Table (2 Ingressi) 7

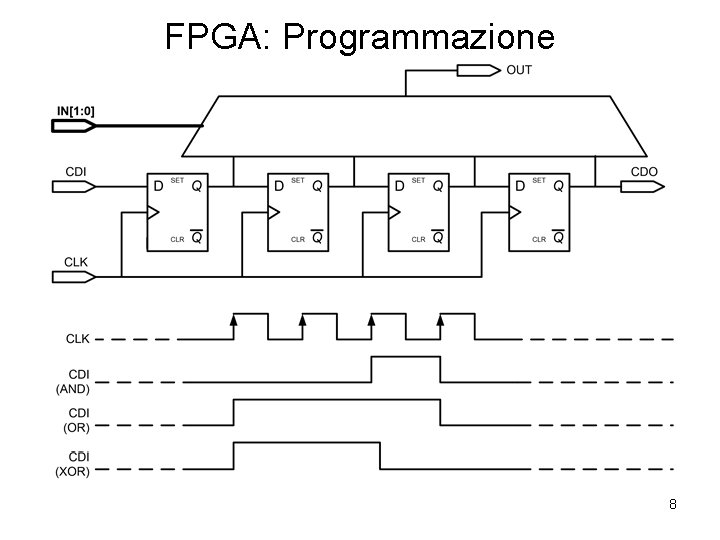

FPGA: Programmazione 8

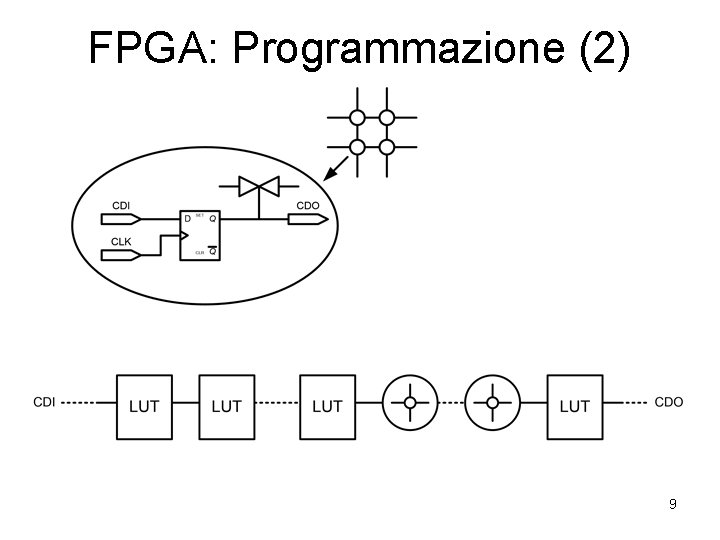

FPGA: Programmazione (2) 9

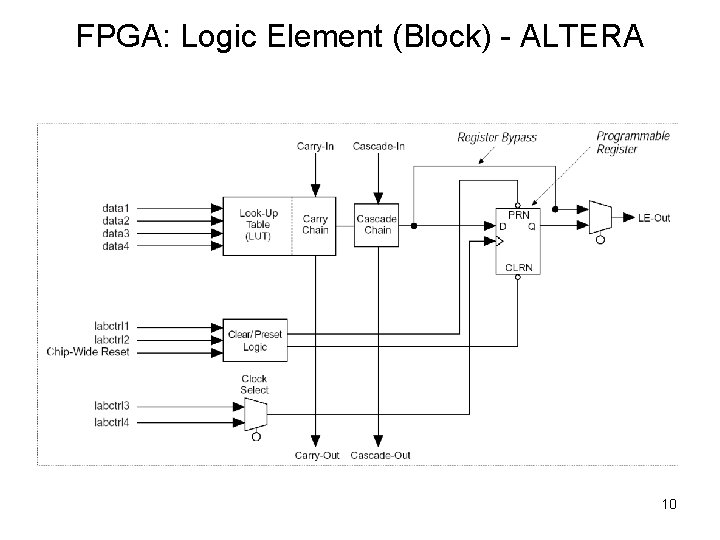

FPGA: Logic Element (Block) - ALTERA 10

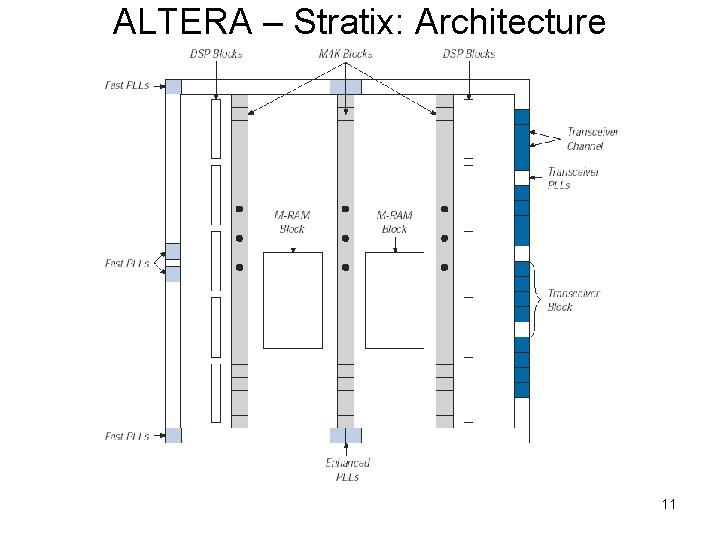

ALTERA – Stratix: Architecture 11

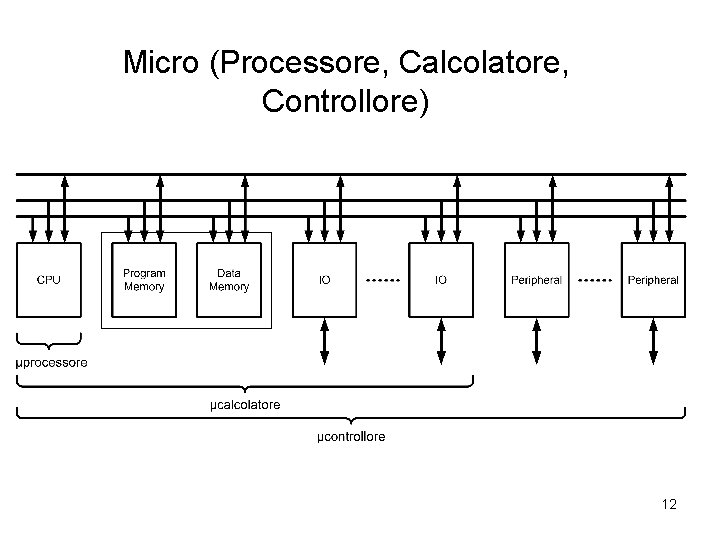

Micro (Processore, Calcolatore, Controllore) 12

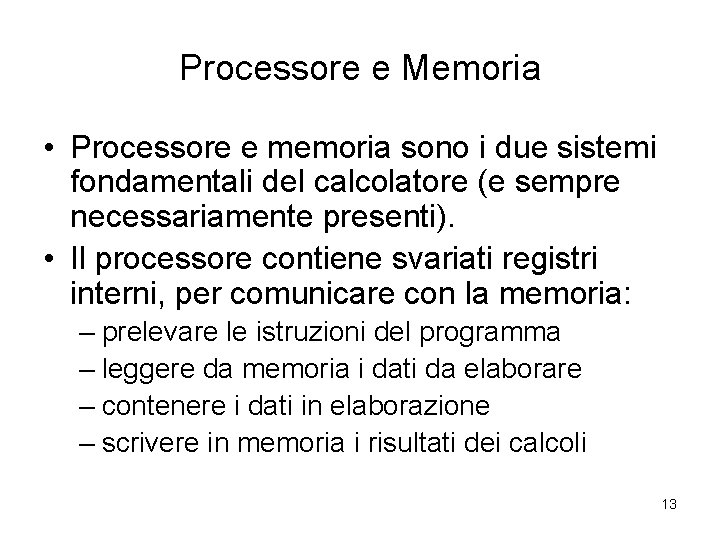

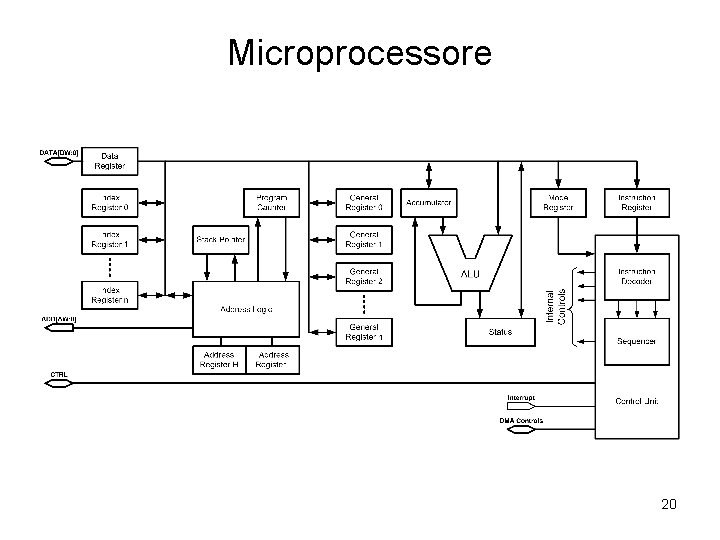

Processore e Memoria • Processore e memoria sono i due sistemi fondamentali del calcolatore (e sempre necessariamente presenti). • Il processore contiene svariati registri interni, per comunicare con la memoria: – prelevare le istruzioni del programma – leggere da memoria i dati da elaborare – contenere i dati in elaborazione – scrivere in memoria i risultati dei calcoli 13

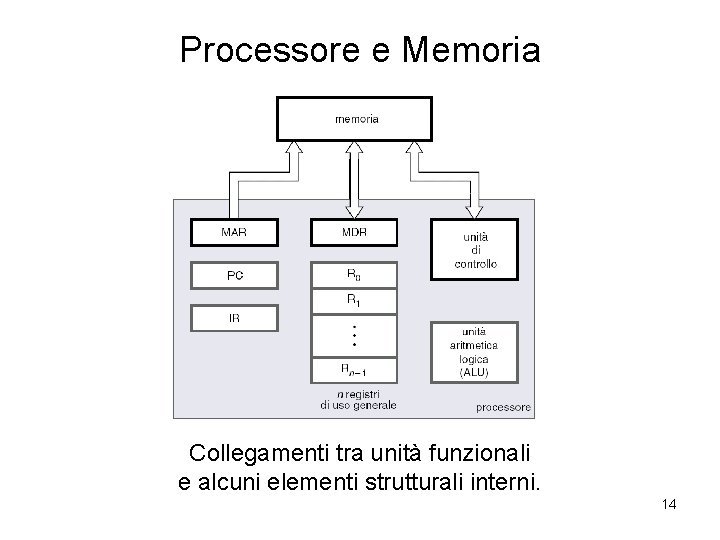

Processore e Memoria Collegamenti tra unità funzionali e alcuni elementi strutturali interni. 14

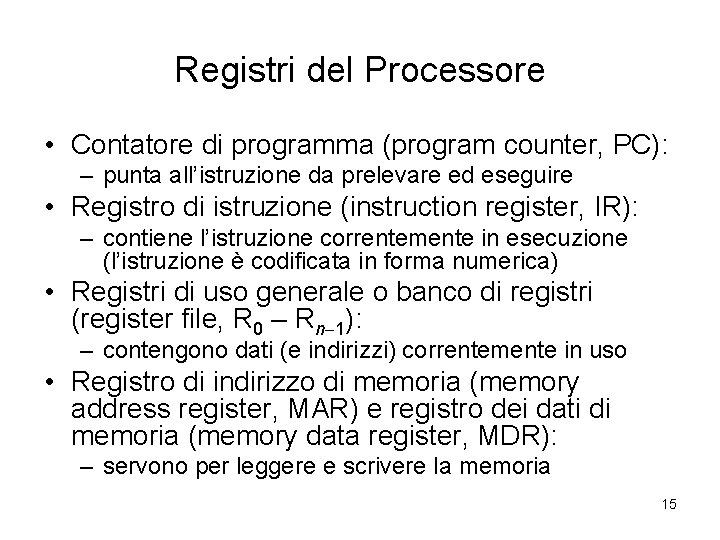

Registri del Processore • Contatore di programma (program counter, PC): – punta all’istruzione da prelevare ed eseguire • Registro di istruzione (instruction register, IR): – contiene l’istruzione correntemente in esecuzione (l’istruzione è codificata in forma numerica) • Registri di uso generale o banco di registri (register file, R 0 – Rn 1): – contengono dati (e indirizzi) correntemente in uso • Registro di indirizzo di memoria (memory address register, MAR) e registro dei dati di memoria (memory data register, MDR): – servono per leggere e scrivere la memoria 15

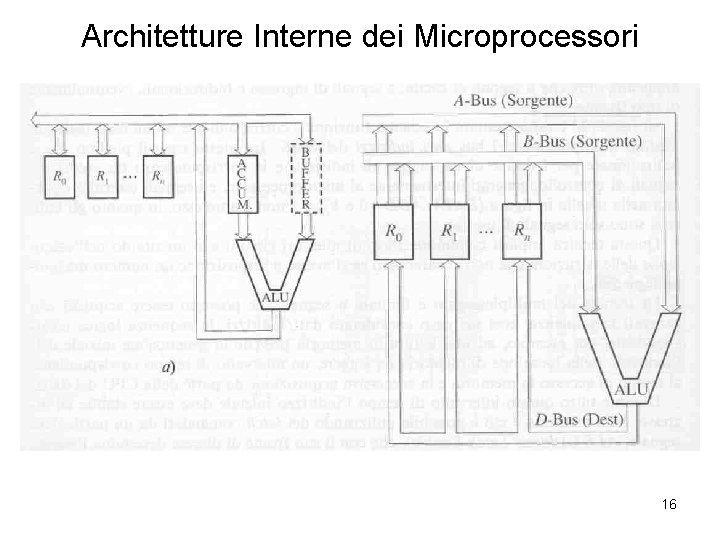

Architetture Interne dei Microprocessori 16

Ruolo del Sistema Operativo • Normalmente il calcolatore è equipaggiato con un sistema operativo (SO). • Il SO è un complesso di programmi che danno al calcolatore funzionalità minimali: – caricare e attivare uno o più programmi – gestire le unità funzionali di memoria e I/O – permettere l’esecuzione simultanea di due o più programmi (processi): concorrenza – permettere la compresenza di più utenti – garantire affidabilità e sicurezza del calcolatore. 17

CARATTERISTICHE SOFTWARE • Set di istruzioni – Architettura – Gruppi • Modi di indirizzamento – Inerente – Immediato – Diretto – Indiretto – Implicito – indicizzato 18

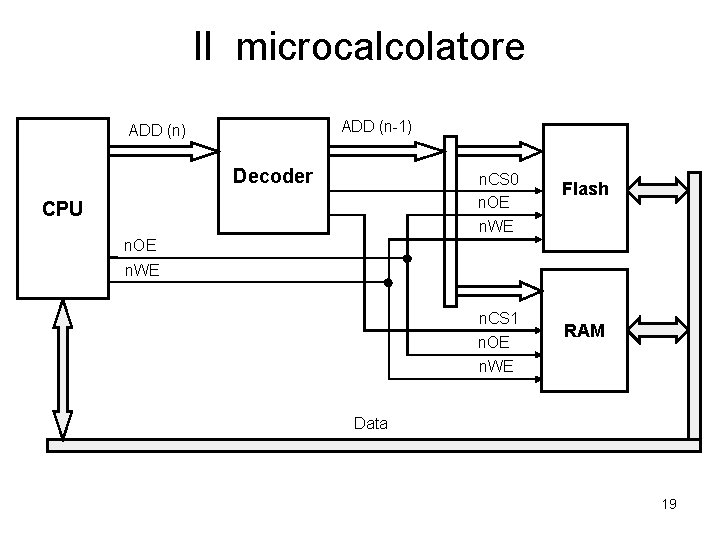

Il microcalcolatore ADD (n-1) ADD (n) Decoder n. CS 0 n. OE CPU Flash n. WE n. OE n. WE n. CS 1 n. OE RAM n. WE Data 19

Microprocessore 20

Gruppi di istruzioni • • Caricamento (MOV, LD, ST) Aritmetiche (ADD, SUB, INC, DEC) Logiche (AND, OR) Salto condizionato o incondizionato (JMP) Controllo (NOP, HALT) Scorrimento (SR, SL, RR, RL) Set e reset di bit 21

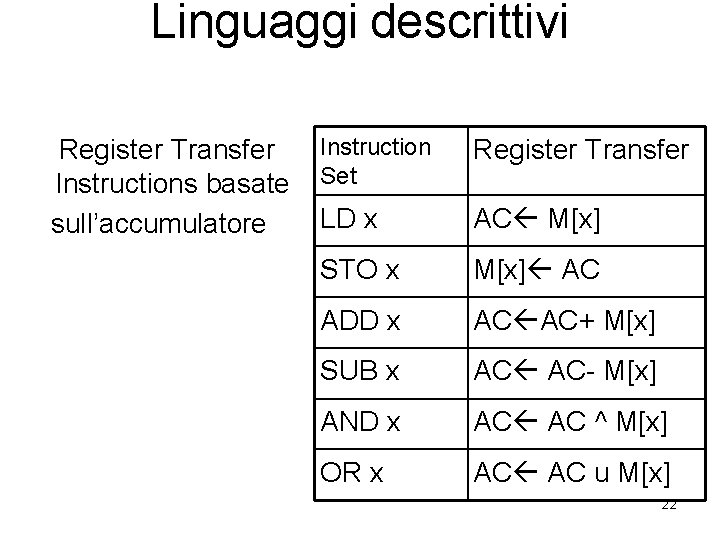

Linguaggi descrittivi Register Transfer Instructions basate sull’accumulatore Instruction Set Register Transfer LD x AC M[x] STO x M[x] AC ADD x AC AC+ M[x] SUB x AC AC- M[x] AND x AC AC ^ M[x] OR x AC AC u M[x] 22

Istruzione Macchina • Il linguaggio macchina in forma simbolica è chiamato anche linguaggio assemblatore o assembly language. • L’assemblatore (assembler) è uno strumento SW che esamina il programma in linguaggio macchina simbolico. • Se non ha errori, lo traduce (o assembla) generandone la forma numerica corrispondente. • Di seguito si danno le caratteristiche fondamentali che si trovano nelle istruzioni di ogni linguaggio macchina, per un tipo di processore classico con registri interni. 23

Modello di Processore • La maggior parte dei processori è costituita da alcuni registri interni e un’unità aritmetica-logica: – banco di registri di uso generale: servono per i dati – registri di uso speciale: servono per il controllo • I registri interni contengono i dati da elaborare correntemente e varie informazioni di controllo necessarie per eseguire il programma. • Molti dei registri interni del processore registri sono visibili da parte del programmatore in linguaggio macchina, e si possono nominare nelle istruzioni macchina stesse. 24

Registri di Uso Speciale • Contatore di programma o PC (program counter): – contiene l’indirizzo dell’istruzione macchina da prelevare ed eseguire • Puntatore alla pila o SP (stack pointer): – contiene l’indirizzo della cima della pila (stack), e si usa per la gestione del sottoprogramma (routine) • Registro di stato o SR (status register, talvolta indicato come PSW, program status word): – contiene vari bit che indicano lo stato del processore (modo utente-sistema, bit di esito, controllo di interruzione, e simili) 25

Forma Simbolica • Il programmatore denota l’istruzione macchina in forma simbolica, facilmente leggibile, come per esempio: NOME arg 1, arg 2, … commento • Il nome (o codice mnemonico) indica l’operazione: MOVE (carica, memorizza o copia dato), ADD (addiziona dato), SUB (sottrai), ecc • Gli elementi arg 1, arg 2, ecc, sono gli argomenti e indicano i dati da elaborare o dove scrivere il risultato, o anche, nelle istruzioni di salto, dove reperire la prossima istruzione da eseguire. • Il commento è solo ad uso del programmatore … 26

Istruzione a Due Argomenti • Istruzione a due argomenti o binaria: NOME arg 1, arg 2 • Esempio: ADD R 1, R 2 – addiziona i contenuti di R 1 e R 2 e scrivi la somma in R 2, sovrascrivendone il contenuto precedente – R 1 è sorgente, R 2 è sia sorgente sia destinazione 27

Simbologia di Base • L’operatore freccia verso sinistra “ ” funziona in sostanza come operatore di assegnamento: destinazione valore origine valore • Tipicamente l’origine del valore è una costante, un numero contenuto in un registro, una parola di memoria o un’espressione aritmetica tra oggetti di tale genere. 28

Operatore di Riferimento • L’indirizzo è un numero (positivo o al minimo nullo) e anche il dato lo è, o lo si può facilmente ridurre a numero (carattere – codice ASCII). • Come distinguere tra un numero inteso come dato o come riferimento a un contenitore di dato (parola di memoria o registro) ? Cioè, come capire se il numero è dato o indirizzo ? • Per indicare che un numero sia da intendere come indirizzo (che si riferisce indirettamente a un dato) e non direttamente come dato da elaborare, racchiudilo tra parentesi quadre [ e ]. 29

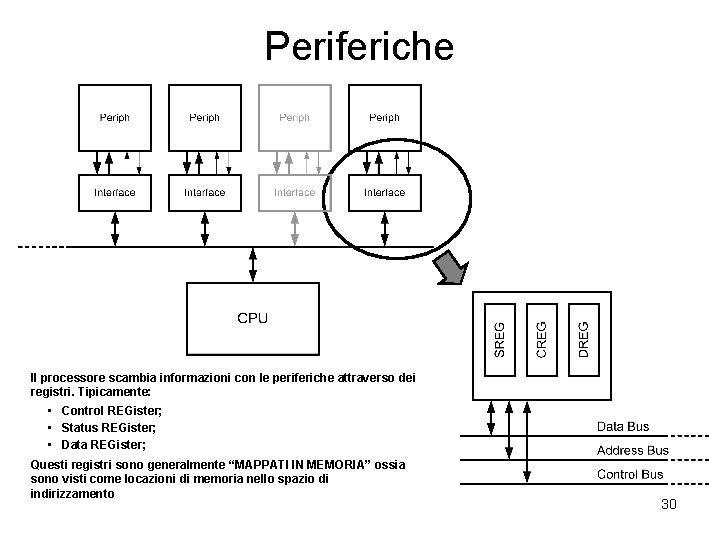

Periferiche Il processore scambia informazioni con le periferiche attraverso dei registri. Tipicamente: • Control REGister; • Status REGister; • Data REGister; Questi registri sono generalmente “MAPPATI IN MEMORIA” ossia sono visti come locazioni di memoria nello spazio di indirizzamento 30

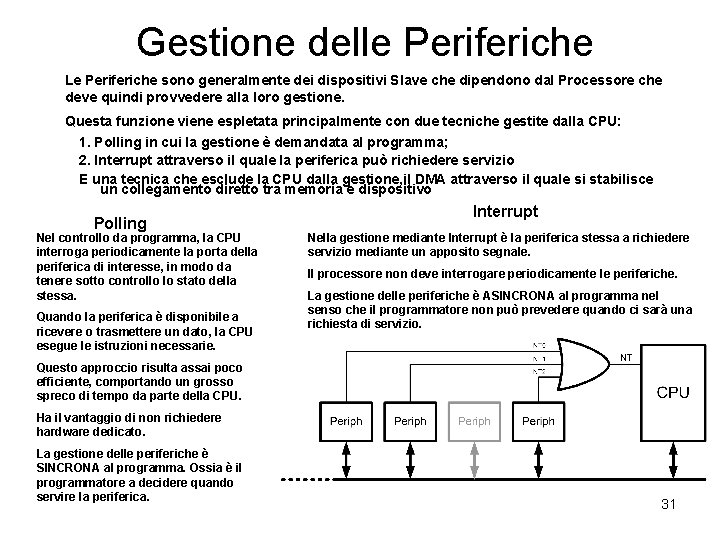

Gestione delle Periferiche Le Periferiche sono generalmente dei dispositivi Slave che dipendono dal Processore che deve quindi provvedere alla loro gestione. Questa funzione viene espletata principalmente con due tecniche gestite dalla CPU: 1. Polling in cui la gestione è demandata al programma; 2. Interrupt attraverso il quale la periferica può richiedere servizio E una tecnica che esclude la CPU dalla gestione, il DMA attraverso il quale si stabilisce un collegamento diretto tra memoria e dispositivo Polling Nel controllo da programma, la CPU interroga periodicamente la porta della periferica di interesse, in modo da tenere sotto controllo lo stato della stessa. Quando la periferica è disponibile a ricevere o trasmettere un dato, la CPU esegue le istruzioni necessarie. Interrupt Nella gestione mediante Interrupt è la periferica stessa a richiedere servizio mediante un apposito segnale. Il processore non deve interrogare periodicamente le periferiche. La gestione delle periferiche è ASINCRONA al programma nel senso che il programmatore non può prevedere quando ci sarà una richiesta di servizio. Questo approccio risulta assai poco efficiente, comportando un grosso spreco di tempo da parte della CPU. Ha il vantaggio di non richiedere hardware dedicato. La gestione delle periferiche è SINCRONA al programma. Ossia è il programmatore a decidere quando servire la periferica. 31

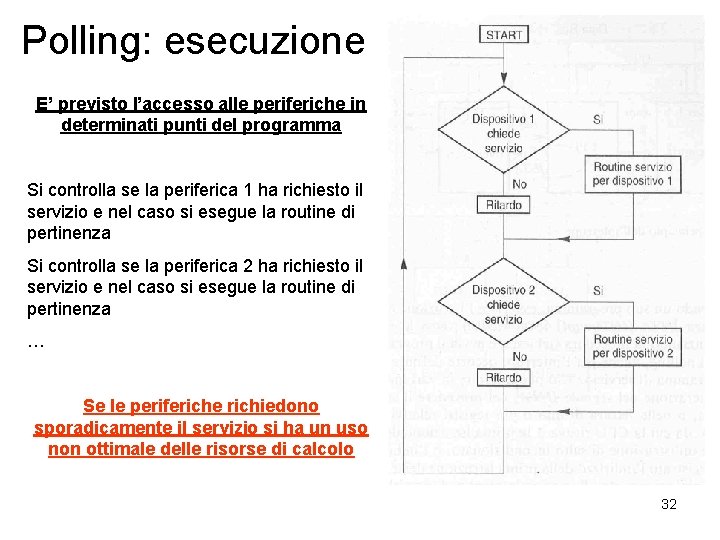

Polling: esecuzione E’ previsto l’accesso alle periferiche in determinati punti del programma Si controlla se la periferica 1 ha richiesto il servizio e nel caso si esegue la routine di pertinenza Si controlla se la periferica 2 ha richiesto il servizio e nel caso si esegue la routine di pertinenza … Se le periferiche richiedono sporadicamente il servizio si ha un uso non ottimale delle risorse di calcolo 32

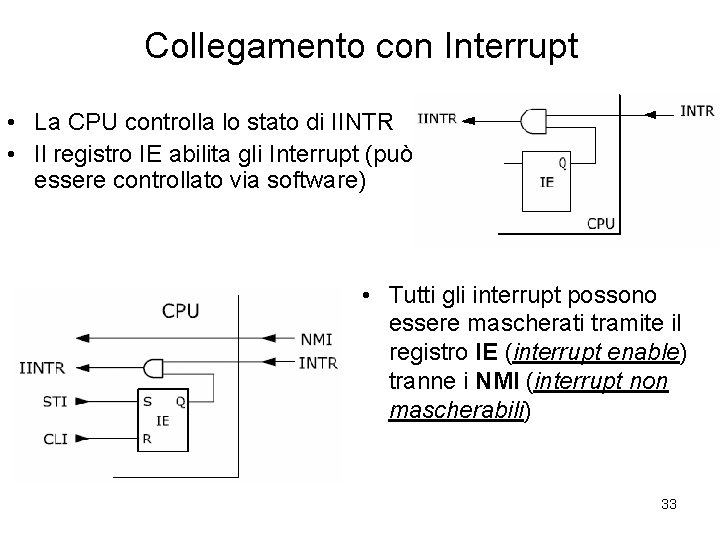

Collegamento con Interrupt • La CPU controlla lo stato di IINTR • Il registro IE abilita gli Interrupt (può essere controllato via software) • Tutti gli interrupt possono essere mascherati tramite il registro IE (interrupt enable) tranne i NMI (interrupt non mascherabili) 33

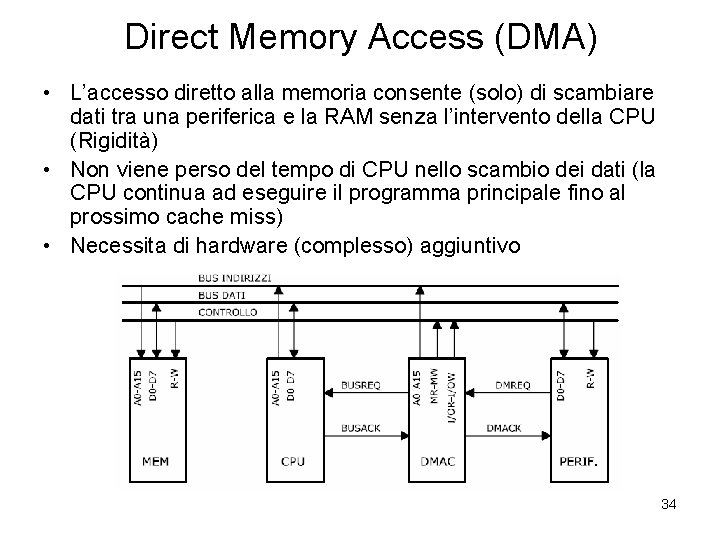

Direct Memory Access (DMA) • L’accesso diretto alla memoria consente (solo) di scambiare dati tra una periferica e la RAM senza l’intervento della CPU (Rigidità) • Non viene perso del tempo di CPU nello scambio dei dati (la CPU continua ad eseguire il programma principale fino al prossimo cache miss) • Necessita di hardware (complesso) aggiuntivo 34

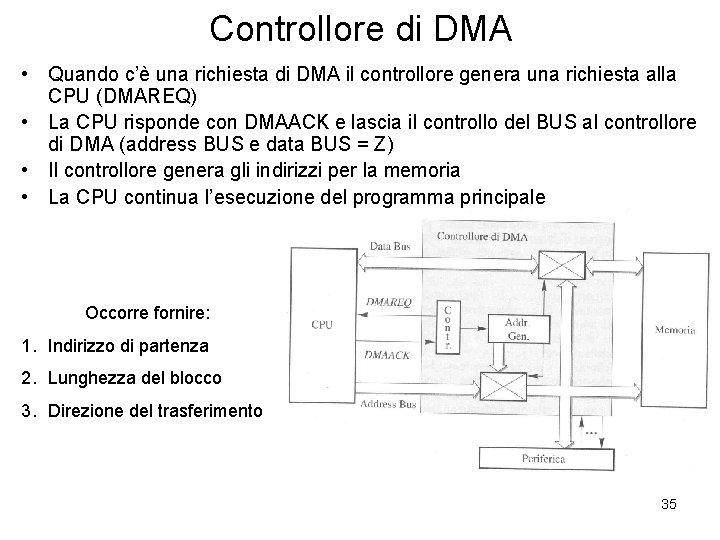

Controllore di DMA • Quando c’è una richiesta di DMA il controllore genera una richiesta alla CPU (DMAREQ) • La CPU risponde con DMAACK e lascia il controllo del BUS al controllore di DMA (address BUS e data BUS = Z) • Il controllore genera gli indirizzi per la memoria • La CPU continua l’esecuzione del programma principale Occorre fornire: 1. Indirizzo di partenza 2. Lunghezza del blocco 3. Direzione del trasferimento 35

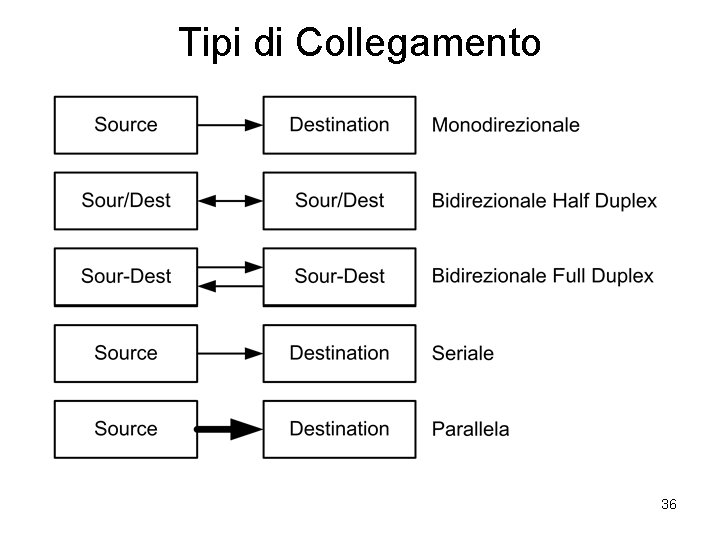

Tipi di Collegamento 36

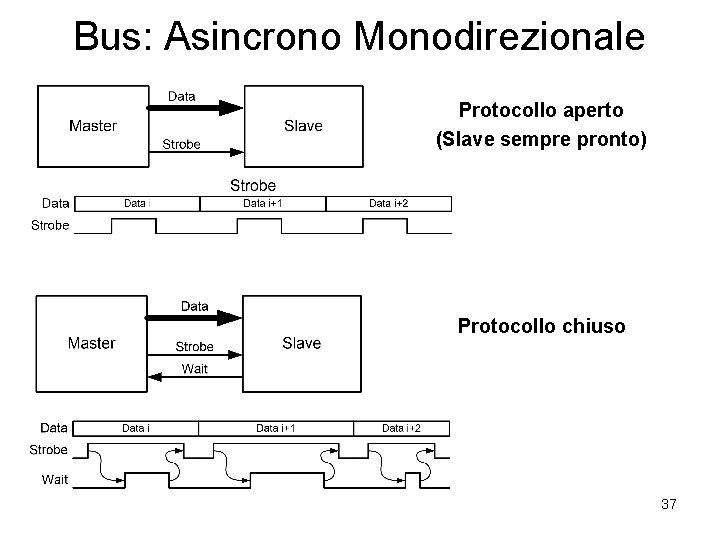

Bus: Asincrono Monodirezionale Protocollo aperto (Slave sempre pronto) Protocollo chiuso 37

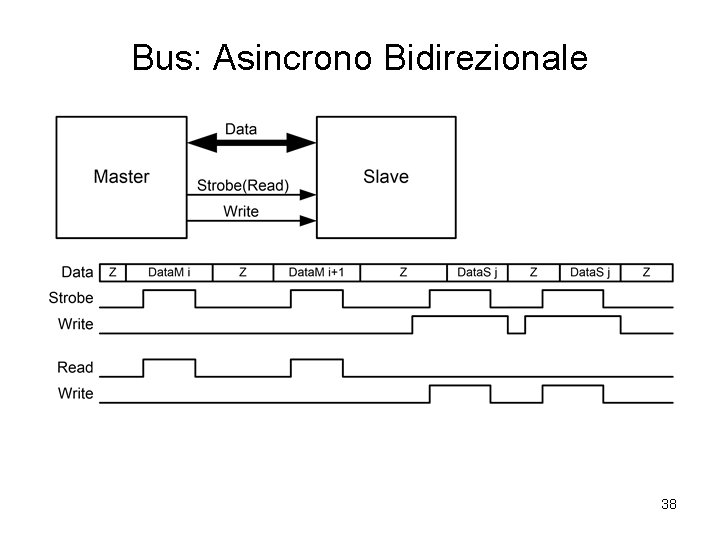

Bus: Asincrono Bidirezionale 38

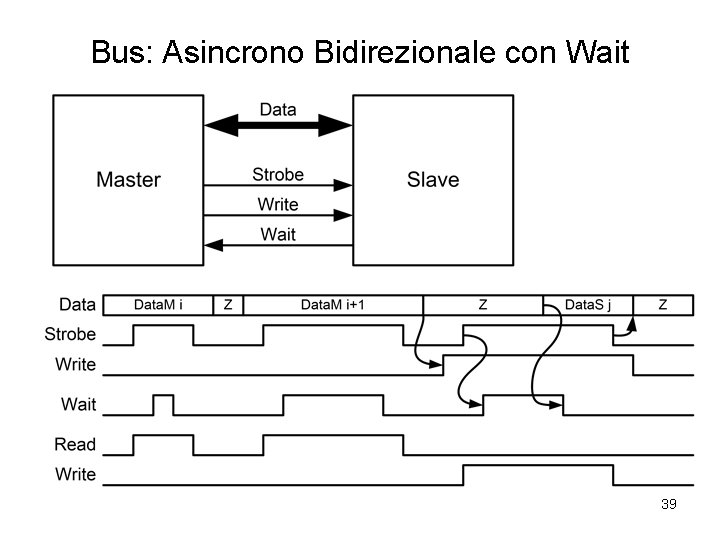

Bus: Asincrono Bidirezionale con Wait 39

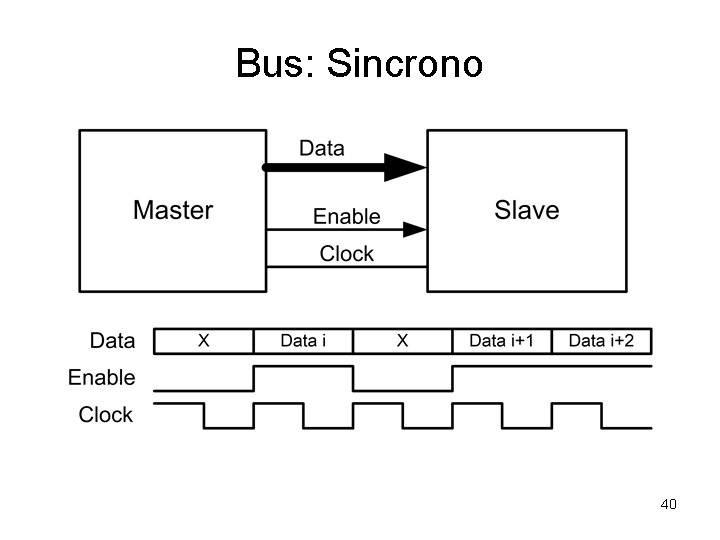

Bus: Sincrono 40

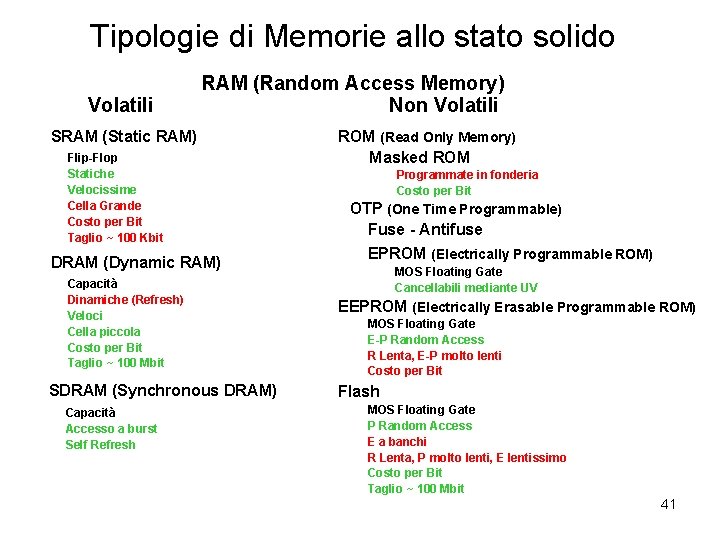

Tipologie di Memorie allo stato solido Volatili RAM (Random Access Memory) Non Volatili SRAM (Static RAM) Flip-Flop Statiche Velocissime Cella Grande Costo per Bit Taglio ~ 100 Kbit DRAM (Dynamic RAM) Capacità Dinamiche (Refresh) Veloci Cella piccola Costo per Bit Taglio ~ 100 Mbit SDRAM (Synchronous DRAM) Capacità Accesso a burst Self Refresh ROM (Read Only Memory) Masked ROM Programmate in fonderia Costo per Bit OTP (One Time Programmable) Fuse - Antifuse EPROM (Electrically Programmable ROM) MOS Floating Gate Cancellabili mediante UV EEPROM (Electrically Erasable Programmable ROM) MOS Floating Gate E-P Random Access R Lenta, E-P molto lenti Costo per Bit Flash MOS Floating Gate P Random Access E a banchi R Lenta, P molto lenti, E lentissimo Costo per Bit Taglio ~ 100 Mbit 41

42

- Slides: 42