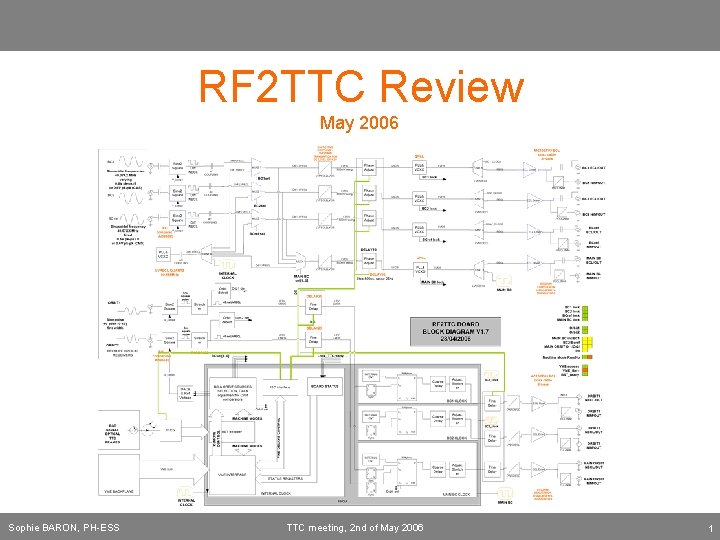

RF 2 TTC Review May 2006 Sophie BARON

RF 2 TTC Review May 2006 Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 1

§ § Sophie BARON, PH-ESS Receiver Crate Functionalities Design AOB TTC meeting, 2 nd of May 2006 2

![RECEIVER CRATE [Overview] Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 3 RECEIVER CRATE [Overview] Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 3](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-3.jpg)

RECEIVER CRATE [Overview] Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 3

![RECEIVER CRATE [Location] Magnetic field: Radiations: Total dose: Ch Hadrons >20 Me. V fluency: RECEIVER CRATE [Location] Magnetic field: Radiations: Total dose: Ch Hadrons >20 Me. V fluency:](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-4.jpg)

RECEIVER CRATE [Location] Magnetic field: Radiations: Total dose: Ch Hadrons >20 Me. V fluency: Neutrons>20 Me. V: <100 gauss 1. 4 rad/10 yrs 1. 5 106/10 yrs/cm-2 3. 1 106/10 yrs/cm-2 TTClab (build 4) Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 4

![RECEIVER CRATE [Crates] § ATLAS, CMS, LHCb: o 1 LHC standard 6 U VME RECEIVER CRATE [Crates] § ATLAS, CMS, LHCb: o 1 LHC standard 6 U VME](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-5.jpg)

RECEIVER CRATE [Crates] § ATLAS, CMS, LHCb: o 1 LHC standard 6 U VME crate per experiment o Power supply type OP 06. 0710 (+3. 3 V/100 A, +5 V/100 A, +-12 V/10 A, 48 V/12 A) § ALICE: o 1 ALICE Trigger standard 6 U VME crate (water cooled) o Power supply type changed from 0 P 17. 0711 to 0 P 17. 0701 (+3. 3 V/100 A, +5 V/100 A, +/-12 V/10 A) § TTC lab: o 1 LHC standard 6 U VME crate per experiment o Power supply type OP 06. 0710 (+3. 3 V/100 A, +5 V/100 A, +-12 V/10 A, 48 V/12 A) § RF: o Use VME 64 crates (no P 3 V 3). Þ RF 2 TTC and fanout modules use +3 V 3, +5 V and +-12 V Þ RF_Tx and RF_Rx use only +5 V and +-12 V Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 5

![RECEIVER CRATE [Crate Controllers] § ALICE: o Standard VP 315/317 from CCT § ATLAS: RECEIVER CRATE [Crate Controllers] § ALICE: o Standard VP 315/317 from CCT § ATLAS:](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-6.jpg)

RECEIVER CRATE [Crate Controllers] § ALICE: o Standard VP 315/317 from CCT § ATLAS: o Standard VP 110 from CCT § CMS: o CAEN PCI-controller card A 2818 + V 2718 VME-PCI optical bridge § LHCb: o CAEN V 1718 VME-USB bridge All these modules are POOL items. One of each will be reserved as from August 06. The TTClab is equipped with a VP 110. Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 6

![RECEIVER CRATE [RF Analog Links] § Analog Modules o Transmitter module: RF_Tx_A (EDA-01331) o RECEIVER CRATE [RF Analog Links] § Analog Modules o Transmitter module: RF_Tx_A (EDA-01331) o](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-7.jpg)

RECEIVER CRATE [RF Analog Links] § Analog Modules o Transmitter module: RF_Tx_A (EDA-01331) o Receiver module: RF_Rx_A (EDA-01332) § Miteq links validated • Specs: – Freq max: 3 GHz (typ) – Vin: 10 d. Bm (max) – Vout: 10 d. Bm (max) • Measured Phase Noise: – 400 MHz -> 0. 4 ps (pkpk) – 40 MHz -> 0. 4 ps (pkpk) – 10 MHz -> 13 ps (pkpk) More results in the evaluation report • Typical output levels: – Bunch Clock = 0 d. Bm continuous sinewave – Orbit = 1 Vpk pulse on 50 Ohms • Quantities: – 10 links have been ordered in November 05 – 10 to be ordered soon => Enough to work until 2007 Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 7

![RECEIVER CRATE [RF Analog Links] § 6 U 4 TE VME (VME 64 x RECEIVER CRATE [RF Analog Links] § 6 U 4 TE VME (VME 64 x](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-8.jpg)

RECEIVER CRATE [RF Analog Links] § 6 U 4 TE VME (VME 64 x and VME 64 compatible) o 3 internal registers • Power warning led threshold (RW) • CH 1 Power monitoring (Read Only) • CH 2 Power monitoring (Read Only) o o Manual or geographical addresses Emi Filters on each laser power pin FPGA programmed using VHDL/ Visual Elite to match the AB/RF requirements Heat sink required to keep the Miteq Rx and Tx at about 35 C Deg. Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 8

![RECEIVER CRATE [RF Analog Links] § Power consumption: +5 V +12 V -12 V RECEIVER CRATE [RF Analog Links] § Power consumption: +5 V +12 V -12 V](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-9.jpg)

RECEIVER CRATE [RF Analog Links] § Power consumption: +5 V +12 V -12 V Tx 0. 7 A 0. 2 A Rx 0. 7 A 0 § Component price/ dual module MITEQ Others Total Tx 3174 178 6 527 CHF Rx 5079 190 10 348 CHF Sophie BARON, PH-ESS • Some layout changes on-going following the review done with AB/RF • PCB manufacture to begin this week TTC meeting, 2 nd of May 2006 9

![RECEIVER CRATE [RF Digital Links] § Digital Modules (RF_Tx_D and RF_Rx_D) o First test RECEIVER CRATE [RF Digital Links] § Digital Modules (RF_Tx_D and RF_Rx_D) o First test](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-10.jpg)

RECEIVER CRATE [RF Digital Links] § Digital Modules (RF_Tx_D and RF_Rx_D) o First test boards made with PHOTON 155 Mbps/TRR-1 B 43 pair • Performance evaluated on the same setup than the analog links • Results available in the test report • AB/RF agreed that this could be a cheaper solution for 70% of the links, including the TTC • If the final results are as good as expected, they will use this solution for these 70% and maintain the boards the same way. o Optical components identified and ordered • Photon getting obsolete • AMS components pin compatible components • Price: – Orbit, 10 MHz, 40 MHz: 156 Mbps links – 400 MHz: 1. 2 Gbps o Design on-going (PH/ESS). Tx Rx 156 Mbps PHOTON 197 97 156 Mbps AMS 313 227 1. 2 Gbps AMS 635 295 • Close to the analog boards, but higher density. Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 10

![RECEIVER CRATE [Client modules] Standard TTC modules: Coupling Termination BC in AC 50 to RECEIVER CRATE [Client modules] Standard TTC modules: Coupling Termination BC in AC 50 to](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-11.jpg)

RECEIVER CRATE [Client modules] Standard TTC modules: Coupling Termination BC in AC 50 to vbb A in DC NECL 120/82 (=-2. 1 VDC) BC out AC 120/82 (=-2. 1 VDC) L 1 a_in AC 240/62 (=-1. 1 VDC) BC_in AC 240/62 (=-1. 1 VDC) Orbit_in AC 240/62 (=-1. 1 VDC) ECL_out DC NECL 560 to -5 V 2 BC in AC 240/62 (=-1. 1 VDC) A_in DC NECL 120/82 (=-2. 1 VDC) BC_in AC 120/82 (=-2. 1 VDC) BC_out AC 120/82 (=-2. 1 VDC) Sig_in AC 120/82 (=-2. 1 VDC) Sig_out AC 150 to GND (PECL) TTCex Custom modules: o ATLAS CTP o TTCci o. . TTCvi TTCvx TTCClk. Gen TTCFanout Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 To have a full compatibility with all the client modules, • The BC_out signals can be ECL AC coupled • The Orbit_out signals need to be NECL DC coupled 11

![RECEIVER CRATE [TTC Clock fanout] § TTC Clock fanout (EDA-01240 -V 1, PH/MIC) o RECEIVER CRATE [TTC Clock fanout] § TTC Clock fanout (EDA-01240 -V 1, PH/MIC) o](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-12.jpg)

RECEIVER CRATE [TTC Clock fanout] § TTC Clock fanout (EDA-01240 -V 1, PH/MIC) o o o Dual 1: 18 ECL fanout 4 NIM outputs per input (ALICE requirement) 1 status led per input (presence of clock). Maximum density The 2 dual modules can be daisy chained. Fully AC coupled Prototype produced § § § Power: 5 V-5 A, Jitter: In/Out skew=8 ps rms, Cy 2 Cy=11 ps rms Skew between outputs: a few ps Design needs to be adjusted to be ‘orbit-compliant’ (AC -> DC coupling) Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 12

§ § Sophie BARON, PH-ESS Receiver Crate Functionalities Design AOB TTC meeting, 2 nd of May 2006 13

![FUNCTIONALITIES [Inputs/Outputs] § VME 6 U module § 1 slot if possible § Inputs FUNCTIONALITIES [Inputs/Outputs] § VME 6 U module § 1 slot if possible § Inputs](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-14.jpg)

FUNCTIONALITIES [Inputs/Outputs] § VME 6 U module § 1 slot if possible § Inputs o 3 BC inputs (SMA or Lemo 00) (RF signals) o 2 Orbit inputs (RF signals) o 1 Optical input for the BST signals § Outputs (can be discussed) o 4 ECL BC outputs (BC 1, BC 2, BCref, Main. BC) • AC coupled o 4 NIM copies o 3 NECL Orbit outputs (Orb 1, Orb 2, Main. Orb) • DC coupled • Synchronised respectively to BC 1, BC 2, Main. BC o 3 NIM copies § Status leds Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 14

![FUNCTIONALITIES [Block Diagram] Adjustable Reset possible Monitored via a VME register Status Led Sophie FUNCTIONALITIES [Block Diagram] Adjustable Reset possible Monitored via a VME register Status Led Sophie](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-15.jpg)

FUNCTIONALITIES [Block Diagram] Adjustable Reset possible Monitored via a VME register Status Led Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 15

![FUNCTIONALITIES [VME Interface] § VME Interface o D 32/A 32 access mode (AM 0 FUNCTIONALITIES [VME Interface] § VME Interface o D 32/A 32 access mode (AM 0](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-16.jpg)

FUNCTIONALITIES [VME Interface] § VME Interface o D 32/A 32 access mode (AM 0 x 09) o 8 bits of board address (A 31 -A 24) (2 rotary switches). o Geographical addresses usable if the manual address is 0 x 00 (reloaded at power up or by sysreset) o Interrupts are possible, but have to remain optional. They may not be handled by every types of VME controllers. Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 16

![FUNCTIONALITIES [Signal Adjustments] § Adjustable parameters (via VME registers) o BC 1, BC 2, FUNCTIONALITIES [Signal Adjustments] § Adjustable parameters (via VME registers) o BC 1, BC 2,](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-17.jpg)

FUNCTIONALITIES [Signal Adjustments] § Adjustable parameters (via VME registers) o BC 1, BC 2, BCref • Adjustable level on the comparator input • Multiplexing between each input and the internal 40. 078 MHz clock • Adjustable phase shift (steps of 0. 5 ns) o Main BC • Multiplexing between BC 1, BC 2, BCref and internal clock • Adjustable phase shift (steps of 0. 5 ns) o Orbit 1 and Orbit 2 • • • Adjustable level on the comparator input to match various types of signals Adjustable phase shift before the latching with the corresponding BC Multiplexing between each input and an internal counter Adjustable length Adjustable coarse delay (steps of 25 ns) Adjustable phase shift (steps of 0. 5 ns) before the output o Main Orbit • • Multiplexing between the two orbit sources and an internal counter Adjustable length Adjustable coarse delay (steps of 25 ns) Adjustable phase shift (steps of 0. 5 ns) before the output Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 17

![FUNCTIONALITIES [Status & Remote Control] § Board status data o Read only registers: Orbit FUNCTIONALITIES [Status & Remote Control] § Board status data o Read only registers: Orbit](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-18.jpg)

FUNCTIONALITIES [Status & Remote Control] § Board status data o Read only registers: Orbit available, QPLL lock, TTC ready, machine mode o Leds: selected signals, QPLL lock, available orbit, VME access, VME berr, BST signal ready. . . § Remote control of the adjustments o Orbit comparator level/ orbit dephasing: FIFO containing the 128 last BC counts between two consecutive Orbit signals (ideally 3564 each). The content of this FIFO can indicate a bad level on the comparator, a dephasing, a wrong synchronisation. This FIFO is filled at reception of a VME command. o Clock status: QPLL status indicates if the clock is absent or if the comparator level is wrong. Would some other ways being required? o Orbit counter, 32 bits (106 hours). Could be reset, either manually, or at the beginning of a run if required Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 18

![FUNCTIONALITIES [Working modes] § Manual and automatic modes for signal selection o Manual mode: FUNCTIONALITIES [Working modes] § Manual and automatic modes for signal selection o Manual mode:](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-19.jpg)

FUNCTIONALITIES [Working modes] § Manual and automatic modes for signal selection o Manual mode: the source of each output signal is manually selected o Automatic mode: • Change the selected sources according to the machine mode • 2 types of parameters must be configured: – Which machine mode is considered to be ‘run’ (ex: ramping, adjust, collide. . ) or ‘no run’ (beam dump, no beam, …) – Which source for each signal must be selected during ‘run’ or ‘no run’. Example for the Main BC: Internal clock during ‘no run’ periods, and BCref during run periods • 3 different configurations can be defined for the signal selection. o Which means: • • 1 register to define in which mode we are (manual, auto 1, auto 2, auto 3) 1 register to define which machine mode corresponds to which state 1 register to define the sources set when ‘no run’………………… 3 registers to define the sources set when ‘run’ (1 per auto mode)… Beam Dump E(4 V - 50 G e 7 T > e. V ) Beam Dump injection ramping squeeze ~15 min ~28 min ~15 min time physics ~10 -20 H Run/no run Automode 1 Automode 2 Automode 3 Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 19

![FUNCTIONALITIES [State Machine] Beam Dump E(4 V - 50 G e 7 T > FUNCTIONALITIES [State Machine] Beam Dump E(4 V - 50 G e 7 T >](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-20.jpg)

FUNCTIONALITIES [State Machine] Beam Dump E(4 V - 50 G e 7 T > e. V ) Beam Dump injection ramping squeeze ~15 min ~28 min ~15 min time physics ~10 -20 H Run/no run Automode 1 Automode 2 Automode 3 Manual Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 20

![FUNCTIONALITIES [register map -1] Bunch Clocks registers BC# BC 1_COMP_Vref R/W 8 bits Voltage FUNCTIONALITIES [register map -1] Bunch Clocks registers BC# BC 1_COMP_Vref R/W 8 bits Voltage](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-21.jpg)

FUNCTIONALITIES [register map -1] Bunch Clocks registers BC# BC 1_COMP_Vref R/W 8 bits Voltage reference to be compared to the BC 1 input BC 1_QPLL_STATUS R 2 bits Locked, error BC 1_QPLL_MODE R/W 1 bit autorestart or manual restart mode BC 1_FINE_DELAY R/W 7 bits enable the line, and delay adjustment (steps of 0. 5 ps) BC 1_SOURCE_SEL R/W 1 bit BC source can be chosen between the internal 40. 078 MHz and the LHC BC 1 when the selection mode is manual BC 1_RESERVED_# R/W 16 bits Main. BC_QPLL_STATUS R Locked, error Main. BC_QPLL_MODE R/W 1 bit autorestart or manual restart mode Main. BC_FINE_DELAY R/W 7 bits enable the line, and delay adjustment (steps of 0. 5 ps) Main. BC_SOURCE_SEL R/W 2 bits Main. BC source can be chosen between the internal 40. 078 MHz and the LHC BC 1, BC 2 and BCref Main. BC_RESERVED_# R/W 16 bits Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 21

![FUNCTIONALITIES [register map -2] Orbit registers ORBIT# Orb 1_COMP_Vref R/W 8 bits set the FUNCTIONALITIES [register map -2] Orbit registers ORBIT# Orb 1_COMP_Vref R/W 8 bits set the](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-22.jpg)

FUNCTIONALITIES [register map -2] Orbit registers ORBIT# Orb 1_COMP_Vref R/W 8 bits set the threshold value used to latch the Orb signal Orb 1_SOURCE_SEL R/W 1 bit Orb 1 source can be chosen between the Orb 1 Internal counter and the LHC Orb 1_DETECTED R 1 bit shows if the orbit signal is available Orb 1_DETECTED_PERIOD R 12 bits Each read access gives the last number of BCs between 2 Orbit signals stored in a 128 words FIFO (to check the Orbit dephasing). The 4 upper bits give the status of the fifo when the word is read (full, empty, almost full. . ) Orb 1_FINE_IN_DELAY R/W 7 bits enable the line, and delay adjustment (steps of 0. 5 ps) to adjust the phase of the input signal vs the latching BC Orb 1_COARSE_DELAY R/W 12 bits delay adjustment of the Orbit signal in 3564 steps of 25 ns (0 to 88. 924 us) Orb 1_WIDTH R/W 12 bits orbit pulse width adjustment in 3564 steps of 25 ns (0 to 88. 924 us) Orb 1_FINE_OUT_DELAY R/W 7 bits enable the line, and delay adjustment (steps of 0. 5 ps) to adjust the phase of the output signal vs the BC used by the experiments Orb 1_Int_PERIOD R/W 12 bits set the period of the internal orbit (from 0 to 102 us in steps of 25 ns, sync to BC 1) Orb 1_Int_COUNTER R 12 bits Result of the Orbit 1_int counter (counts the BC between 2 orbits). Reset by each new orbit. Orb 1_COUNTER R 32 bits Result of the Orbit 1 counter (counts the Orbit signal, up to 106 hours). Manually reset or by the beginning of a run ? (how? ) Orb 1_RESERVED_# R/W 16 bits Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 22

![FUNCTIONALITIES [register map -3] Orbit registers Main. ORBIT Main. Orb_SOURCE_SEL R/W 2 bits Main. FUNCTIONALITIES [register map -3] Orbit registers Main. ORBIT Main. Orb_SOURCE_SEL R/W 2 bits Main.](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-23.jpg)

FUNCTIONALITIES [register map -3] Orbit registers Main. ORBIT Main. Orb_SOURCE_SEL R/W 2 bits Main. Orb source can be chosen between the internal Main. Orb counter, the LHC Orb 1 and the LHC orb 2 Main. Orb_COARSE_DELAY R/W 12 bits delay adjustment of the Orbit signal in 3564 steps of 25 ns (0 to 88. 924 us) Main. Orb_WIDTH R/W 12 bits orbit pulse width adjustment in 3564 steps of 25 ns (0 to 88. 924 us) Main. Orb_FINE_OUT_DELAY R/W 7 bits enable the line, and delay adjustment (steps of 0. 5 ps) to adjust the phase of the output signal vs the BC used by the experiments Main. Orb_Int_PERIOD R/W 12 bits set the period of the internal orbit (from 0 to 102 us in steps of 25 ns, sync to Main. BC) Main. Orb_Int_COUNTER R 12 bits Result of the Main. Orbit_int counter (counts the BC between 2 orbits). Reset by each new orbit. 32 bits Result of the Main. Orbit counter (counts the Orbit signal, up to 106 hours). Manually reset or by the beginning of a run ? (how? ) Main. Orb_COUNTER Main. Orb_RESERVED_# Sophie BARON, PH-ESS R/W 16 bits TTC meeting, 2 nd of May 2006 23

![FUNCTIONALITIES [register map -4] BST registers TTCrx_CONFIG 1 R/W TTCrx_CONFIG 2 R/W TTCrx_CONFIG 3 FUNCTIONALITIES [register map -4] BST registers TTCrx_CONFIG 1 R/W TTCrx_CONFIG 2 R/W TTCrx_CONFIG 3](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-24.jpg)

FUNCTIONALITIES [register map -4] BST registers TTCrx_CONFIG 1 R/W TTCrx_CONFIG 2 R/W TTCrx_CONFIG 3 R/W TTCrx_STATUS R TTCrx_RESERVED_1 R/W 16 bits BST MESSAGE MACHINE_MODE R 8 bits BST _RESERVED_1 R/W 32 bits Sophie BARON, PH-ESS decode the LHC Machine Mode transmitted by the BST TTC meeting, 2 nd of May 2006 24

![FUNCTIONALITIES [register map -5] General registers GENERAL REGISTERS BOARD ID R/W 8 bits FIRMWARE FUNCTIONALITIES [register map -5] General registers GENERAL REGISTERS BOARD ID R/W 8 bits FIRMWARE](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-25.jpg)

FUNCTIONALITIES [register map -5] General registers GENERAL REGISTERS BOARD ID R/W 8 bits FIRMWARE VERSION R/W 8 bits BC_Delay 25_GCTRL R/W 8 bits general parameters of the delay 25 chip in charge of all the BC fine delay adjustment Orb_In_Delay 25_GCTRL R/W 8 bits general parameters of the delay 25 chip in charge of all the Orb in fine delay adjustment Orb_Out_Delay 25_GCTRL R/W 8 bits general parameters of the delay 25 chip in charge of all the Orb out fine delay adjustment Working Modes R/W 4 bits 0: manual mode 1: automatic mode 1 2: automatic mode 2 3: automatic mode 3 Automatic_config_no_run R/W 9 bits Describes the state of the selection of the signals in automatic modes, out of the run periods. Automatic_config_run_1 R/W 9 bits Describes the state of the selection of the signals in automatic mode 1, during the run. Automatic_config_run_2 R/W 9 bits Describes the state of the selection of the signals in automatic mode 2, during the run. Automatic_config_run_3 R/W 9 bits Describes the state of the selection of the signals in automatic mode 3, during the run. Machine_states_config R/W 32 bits One bit per machine mode. Use automatic_config_0 when bit#=0, use one of the automatic_config 1 to 3 when bit#=1. GNAL_RESERVED_1 R/W 32 bits Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 25

![FUNCTIONALITIES [register map -6] Commands RESET BC 1_QPLL_RESET BC 2_QPLL_RESET BCref_QPLL_RESET Main. BC_QPLL_RESET Delay FUNCTIONALITIES [register map -6] Commands RESET BC 1_QPLL_RESET BC 2_QPLL_RESET BCref_QPLL_RESET Main. BC_QPLL_RESET Delay](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-26.jpg)

FUNCTIONALITIES [register map -6] Commands RESET BC 1_QPLL_RESET BC 2_QPLL_RESET BCref_QPLL_RESET Main. BC_QPLL_RESET Delay 25_RESET Orb 1_counter_fifos_reset Orb_counters_reset BOARD_RESET COMMANDS Orb 1_fifo_fill trig the filling of the FIFO with the periods of 128 consecutive orbit 1 signals Orb 2_fifo_fill trig the filling of the FIFO with the periods of 128 consecutive orbit 1 signals CMD_RESERVED_# Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 26

§ § Sophie BARON, PH-ESS Receiver Crate Functionalities Design AOB TTC meeting, 2 nd of May 2006 27

![DESIGN [Block Diagram] Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 28 DESIGN [Block Diagram] Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 28](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-28.jpg)

DESIGN [Block Diagram] Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 28

![DESIGN [Technology choices] ECL (NECL, PECL, LVPECL) LVDS (2. 5 V) LVCMOSLVTTL (3. 3 DESIGN [Technology choices] ECL (NECL, PECL, LVPECL) LVDS (2. 5 V) LVCMOSLVTTL (3. 3](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-29.jpg)

DESIGN [Technology choices] ECL (NECL, PECL, LVPECL) LVDS (2. 5 V) LVCMOSLVTTL (3. 3 V) LVCMOS (2. 5 V § § Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 ECL/LVDS components LVDS 2 ECL conversion application note 29

![DESIGN [Schematics & Features] See schematics § Coupling considerations § Conversions o o o DESIGN [Schematics & Features] See schematics § Coupling considerations § Conversions o o o](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-30.jpg)

DESIGN [Schematics & Features] See schematics § Coupling considerations § Conversions o o o ECL 2 LVDS 2 PECL 2 NIM NECL 2 NIM ECL 2 CMOS § BC & Orbit inputs o Coupling o Comparator choice o Voltage reference adjustment § Internal clock o Fixed oscillator o ECL differential clock lines § Orbit synchronisation process o Pulse lengthening Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 30

![DESIGN [Schematics & Features] See schematics § Use of CERN ASICS o Delay 25 DESIGN [Schematics & Features] See schematics § Use of CERN ASICS o Delay 25](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-31.jpg)

DESIGN [Schematics & Features] See schematics § Use of CERN ASICS o Delay 25 o QPLL § FPGA o o o Device choice Programming modes Signal levels Pinout and I/o Banks Firmware consideration • VME interface => implemented in the ATLAS TRT-TTC board • Triple logic necessary for critical registers? (working modes, auto_config) § Internal communication busses o I 2 C § ECL output drivers o MC 100 EL 89 coax cable drivers Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 31

![DESIGN [Schematics & Features] See schematics § Power considerations o Estimation o Solutions § DESIGN [Schematics & Features] See schematics § Power considerations o Estimation o Solutions §](http://slidetodoc.com/presentation_image_h2/b68a52eec6a7e2fb6199bdebfbd2ceb0/image-32.jpg)

DESIGN [Schematics & Features] See schematics § Power considerations o Estimation o Solutions § Debugging facilities o Test points o Spare connector o Signal tap § Bugs to be corrected o Missing pull-up resistors § PCB design o Front Panel o Layout § Prototyping o o Price estimation: components about 830 $ Quantities Component procurement Schedules Sophie BARON, PH-ESS TTC meeting, 2 nd of May 2006 32

§ § Sophie BARON, PH-ESS Receiver Crate Functionalities Design AOB TTC meeting, 2 nd of May 2006 33

- Slides: 33