Resonant Boost Converter Design Justin Burkhart April 15

Resonant Boost Converter Design Justin Burkhart April 15, 2009

Presentation Outline • • • Project Goals The Class E Inverter Resonant Rectifier LDMOS Device Model Completed Boost Converter Design

Project Goals • Design a resonant boost converter using TI LBC 5 process LDMOS devices • Targeted at automotive applications with: – 11 -16 Vdc Input – 30 Vdc Output – 10 -20 Watts – Highest possible switching frequency with efficiency >80% (if possible)

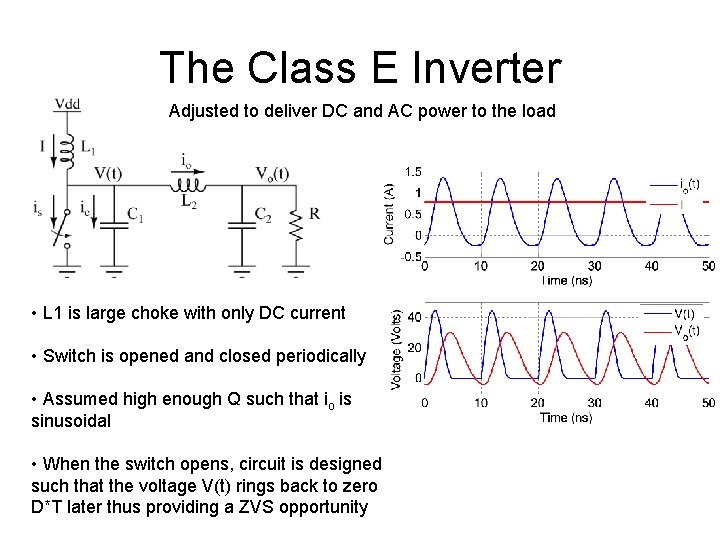

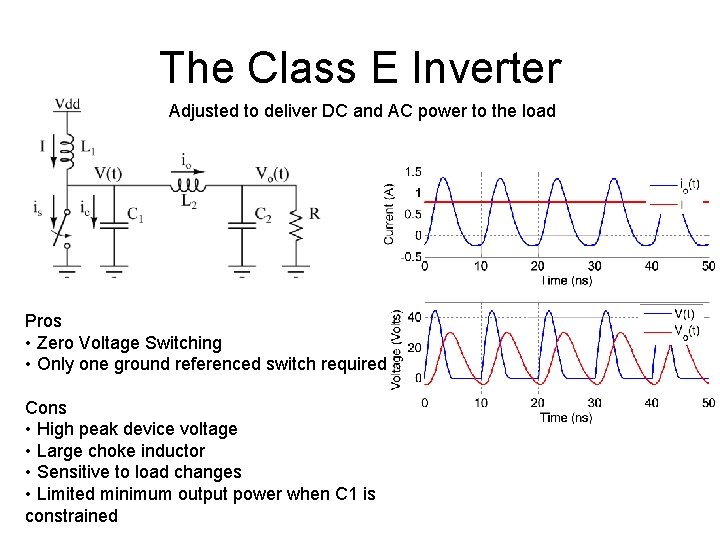

The Class E Inverter Adjusted to deliver DC and AC power to the load • L 1 is large choke with only DC current • Switch is opened and closed periodically • Assumed high enough Q such that io is sinusoidal • When the switch opens, circuit is designed such that the voltage V(t) rings back to zero D*T later thus providing a ZVS opportunity

The Class E Inverter Adjusted to deliver DC and AC power to the load Pros • Zero Voltage Switching • Only one ground referenced switch required Cons • High peak device voltage • Large choke inductor • Sensitive to load changes • Limited minimum output power when C 1 is constrained

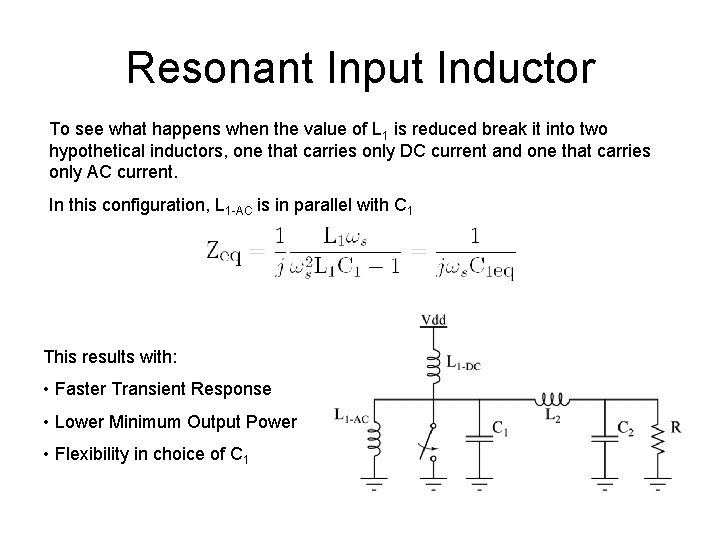

Resonant Input Inductor To see what happens when the value of L 1 is reduced break it into two hypothetical inductors, one that carries only DC current and one that carries only AC current. In this configuration, L 1 -AC is in parallel with C 1 This results with: • Faster Transient Response • Lower Minimum Output Power • Flexibility in choice of C 1

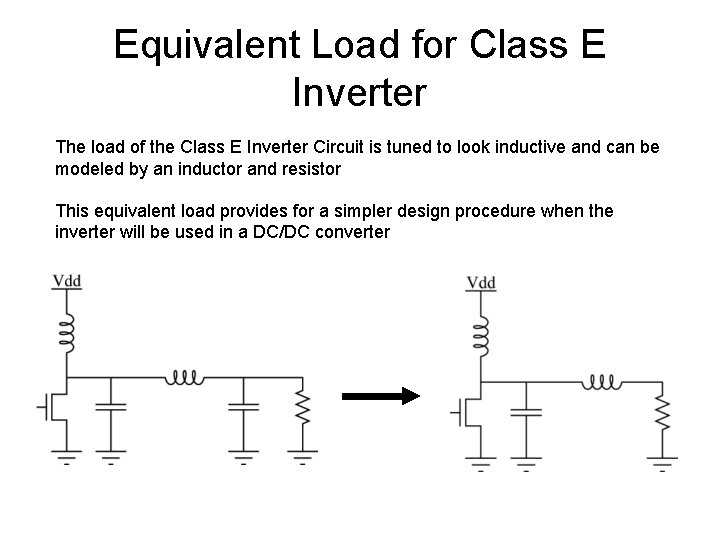

Equivalent Load for Class E Inverter The load of the Class E Inverter Circuit is tuned to look inductive and can be modeled by an inductor and resistor This equivalent load provides for a simpler design procedure when the inverter will be used in a DC/DC converter

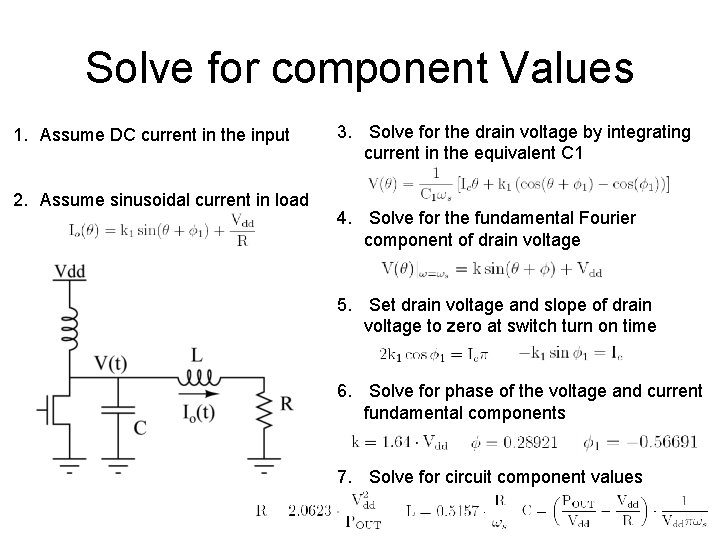

Solve for component Values 1. Assume DC current in the input 2. Assume sinusoidal current in load 3. Solve for the drain voltage by integrating current in the equivalent C 1 4. Solve for the fundamental Fourier component of drain voltage 5. Set drain voltage and slope of drain voltage to zero at switch turn on time 6. Solve for phase of the voltage and current fundamental components 7. Solve for circuit component values

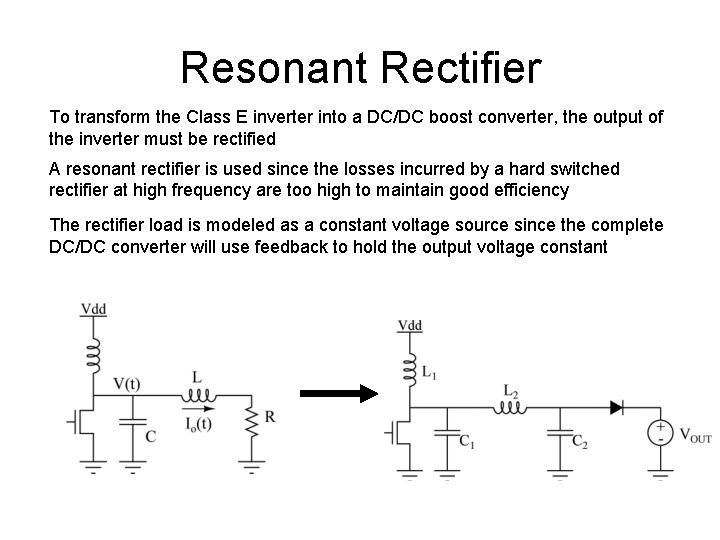

Resonant Rectifier To transform the Class E inverter into a DC/DC boost converter, the output of the inverter must be rectified A resonant rectifier is used since the losses incurred by a hard switched rectifier at high frequency are too high to maintain good efficiency The rectifier load is modeled as a constant voltage source since the complete DC/DC converter will use feedback to hold the output voltage constant

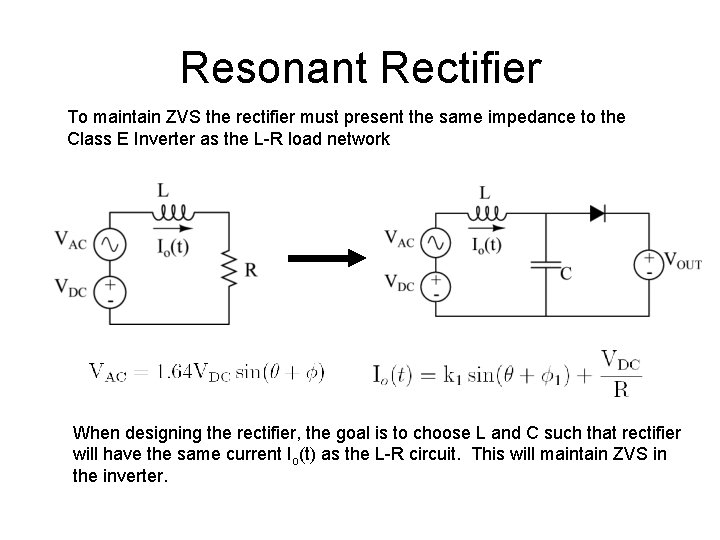

Resonant Rectifier To maintain ZVS the rectifier must present the same impedance to the Class E Inverter as the L-R load network When designing the rectifier, the goal is to choose L and C such that rectifier will have the same current Io(t) as the L-R circuit. This will maintain ZVS in the inverter.

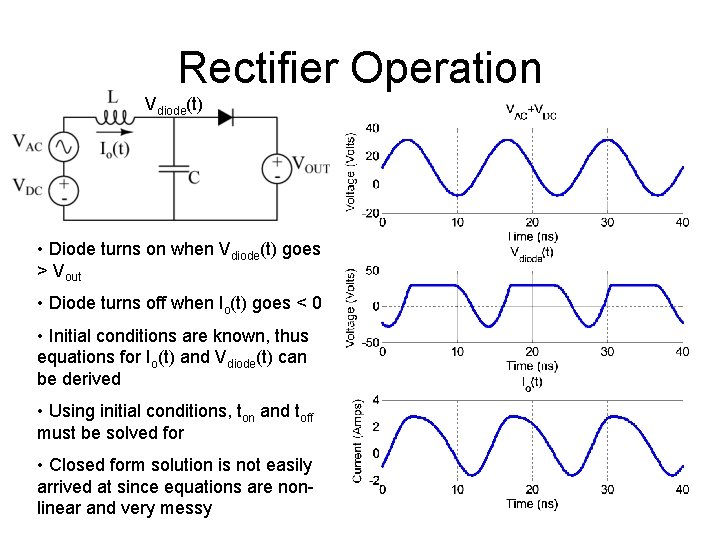

Rectifier Operation Vdiode(t) • Diode turns on when Vdiode(t) goes > Vout • Diode turns off when Io(t) goes < 0 • Initial conditions are known, thus equations for Io(t) and Vdiode(t) can be derived • Using initial conditions, ton and toff must be solved for • Closed form solution is not easily arrived at since equations are nonlinear and very messy

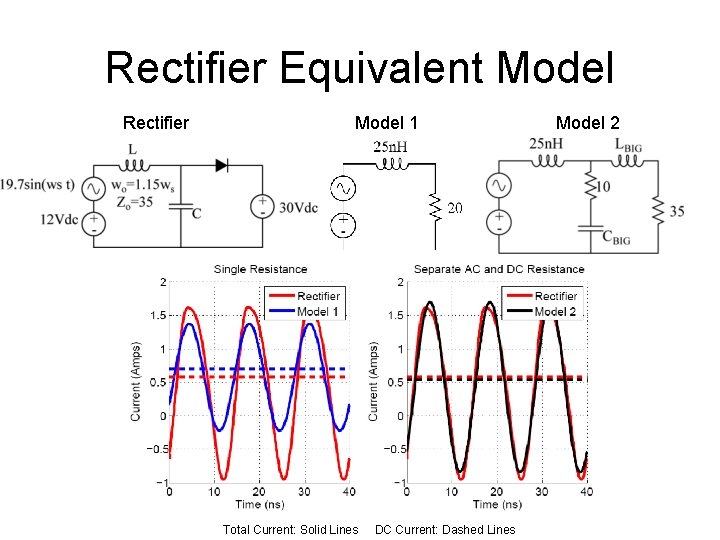

Rectifier Equivalent Model Rectifier Model 1 Total Current: Solid Lines DC Current: Dashed Lines Model 2

Example Of Rectifier Tuning Goal: • Adjust the resonant frequency of the rectifier until the input current has the desired phase Increase Fo • Adjust the characteristic impedance of the rectifier until the desired output power is reached Decrease Zo

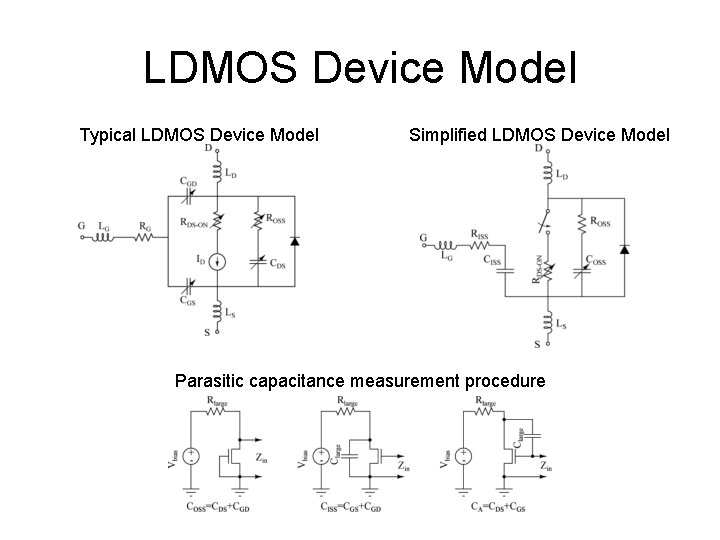

LDMOS Device Model Typical LDMOS Device Model Simplified LDMOS Device Model Parasitic capacitance measurement procedure

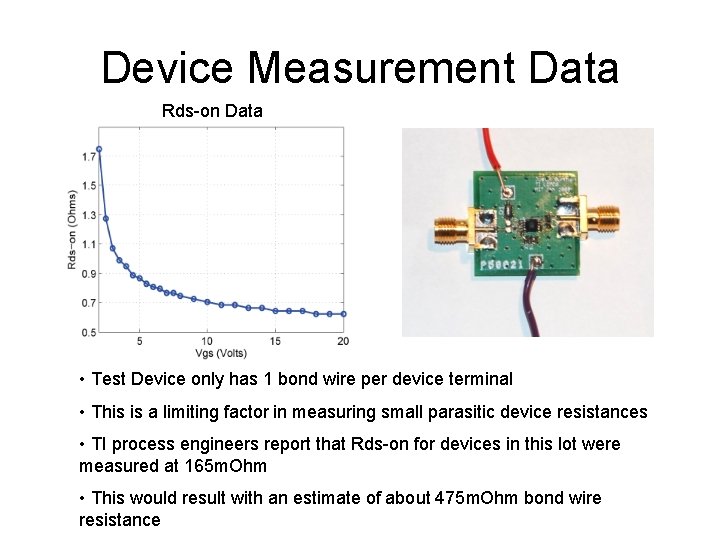

Device Measurement Data Rds-on Data • Test Device only has 1 bond wire per device terminal • This is a limiting factor in measuring small parasitic device resistances • TI process engineers report that Rds-on for devices in this lot were measured at 165 m. Ohm • This would result with an estimate of about 475 m. Ohm bond wire resistance

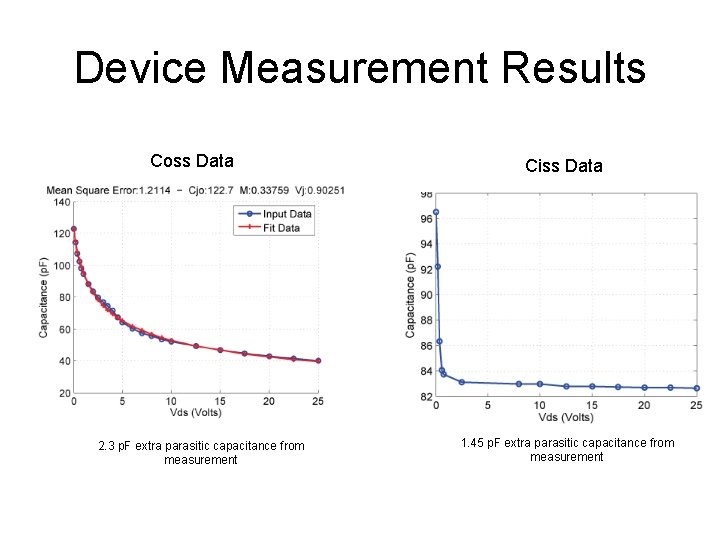

Device Measurement Results Coss Data 2. 3 p. F extra parasitic capacitance from measurement Ciss Data 1. 45 p. F extra parasitic capacitance from measurement

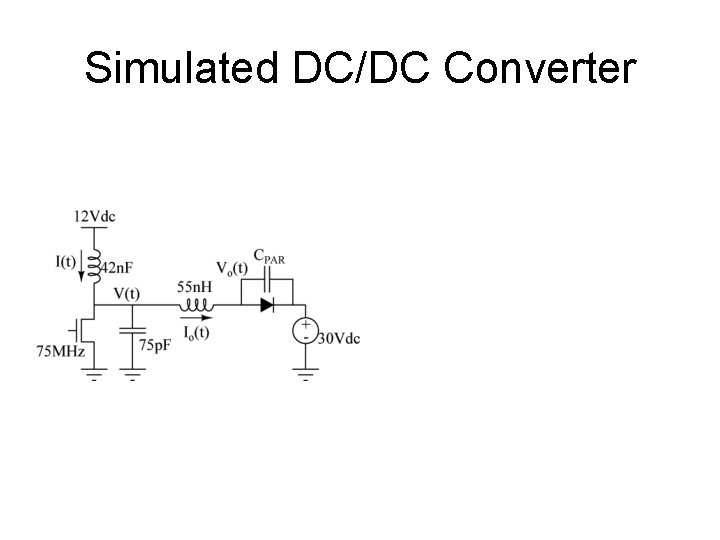

Simulated DC/DC Converter

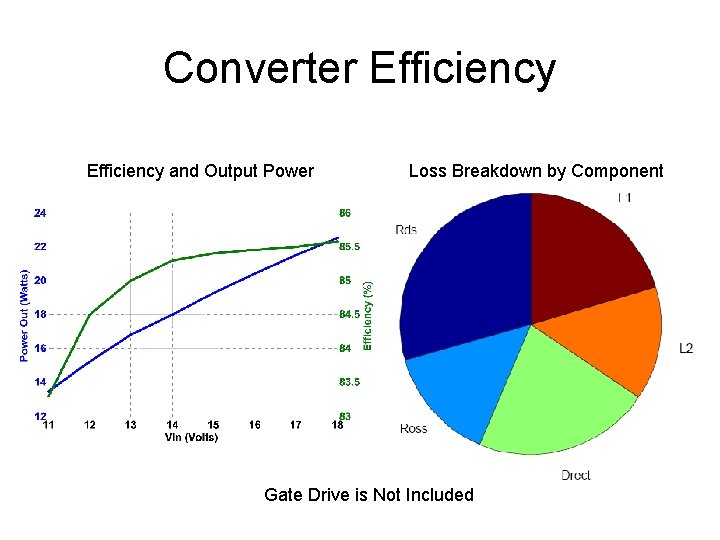

Converter Efficiency and Output Power Loss Breakdown by Component Gate Drive is Not Included

Future Work • Device optimization • Parametric variance analysis • Gate driver • Power section prototype • Integrated controller design • Complete converter

- Slides: 19