Reset Circuit Topologies Reference Analysis of POR Circuit

- Slides: 21

Reset Circuit Topologies Reference: Analysis of POR Circuit Topologies http: //klabs. org/richcontent/fpga_content/Design. Notes/por. htm 2004 MAPLD 1 Reset Circuit Topologies

Introduction The seemingly simple issue of FPGA and ASIC power-on reset circuits is nevertheless often a frequent cause of problems. The discussion in this module will cover both the key issues and a variety of circuits, analyzing their strong and weak points. The discussion will in most cases be general logic design but will deal with some particular issues with Field Programmable Gate Arrays (FPGAs). 2004 MAPLD 2 Reset Circuit Topologies

System Issues None of the circuits discussed in this module are intended to deal with issues of logic devices not starting (e. g. , following their truth table) instantly after the application of power. These system-level issues, based on system-level requirements, must be analyzed and, if necessary, dealt with at the system level and not at the logic level internal to the FPGA or ASIC. 2004 MAPLD 3 Reset Circuit Topologies

Analysis Assumptions 1. The external POR circuitry is properly designed. 2. The clock is generated by a crystal clock oscillator, which takes a certain amount of time to start and then become stable. Additionally, the oscillator may not start clean. 3. The clock is not gated off. If that is not true, such as when areas of the circuit where the clock is gated off for power savings, then additional issues arise. 4. The POR signal is asynchronous to CLK. 5. The period of CLK is large compared with the metastable state resolution time of the flip-flop being used for synchronization. 6. The POR assertion time exceeds the clock oscillator and FPGA start times. 7. The output of the internal POR circuit drives the asynchronous set/reset of flipflops. Since modern FPGAs all have asynchronous flip-flop inputs, this is often used to save logic resources, delay, and power. This is an important consideration since these inputs, unlike D's and ENABLE's, are sensitive to glitches. It is further assumed that timing specifications are met for set/reset distribution including the "removal" time. 8. Noise pulses on the input POR signal is a credible situation. 2004 MAPLD 4 Reset Circuit Topologies

Fully Asynchronous Application Unintended operation or lockup of finite state machines or systems may result if the flip-flops come out of reset during different clock periods. There is a potential for one or more uncontrolled metastable states. Therefore, only reset circuits that [attempt to] remove power-on reset synchronously (PORS) should be considered in hi-rel applications. 2004 MAPLD 5 Reset Circuit Topologies

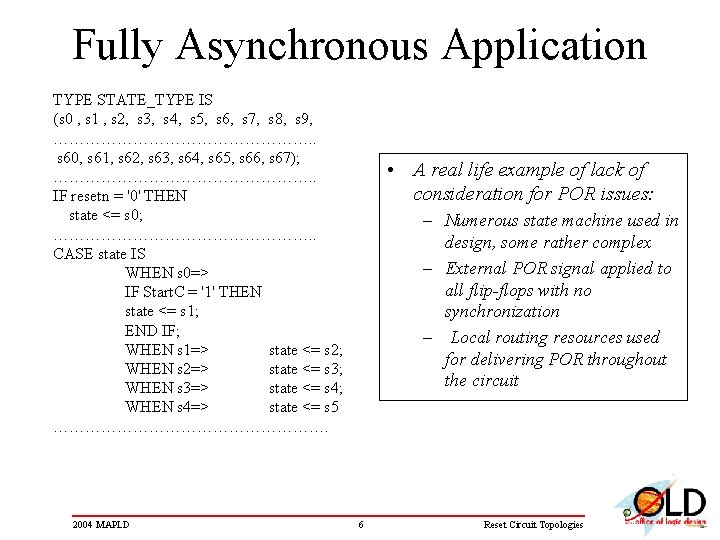

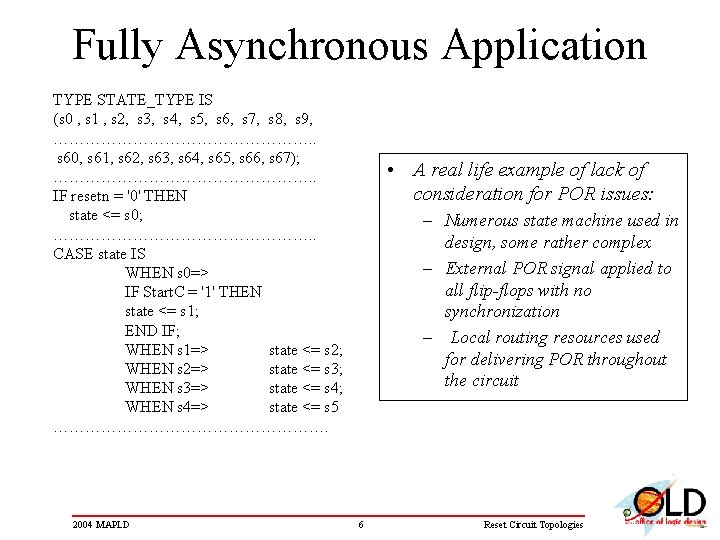

Fully Asynchronous Application TYPE STATE_TYPE IS (s 0 , s 1 , s 2, s 3, s 4, s 5, s 6, s 7, s 8, s 9, ……………………. . s 60, s 61, s 62, s 63, s 64, s 65, s 66, s 67); ……………………. . IF resetn = '0' THEN state <= s 0; ……………………. . CASE state IS WHEN s 0=> IF Start. C = '1' THEN state <= s 1; END IF; WHEN s 1=> state <= s 2; WHEN s 2=> state <= s 3; WHEN s 3=> state <= s 4; WHEN s 4=> state <= s 5 ………………………. 2004 MAPLD • A real life example of lack of consideration for POR issues: – Numerous state machine used in design, some rather complex – External POR signal applied to all flip-flops with no synchronization – Local routing resources used for delivering POR throughout the circuit 6 Reset Circuit Topologies

POR Circuit Selection Significant issues related to the analysis and selection of a poweron reset circuit for a particular application include: – – – 2004 MAPLD Dependence on clock signal being operational Noise immunity Critical timing path impact 7 Reset Circuit Topologies

Synchronously Applied, Synchronously Removed Circuits All circuits of this type need Clock to be operational 2004 MAPLD 8 Reset Circuit Topologies

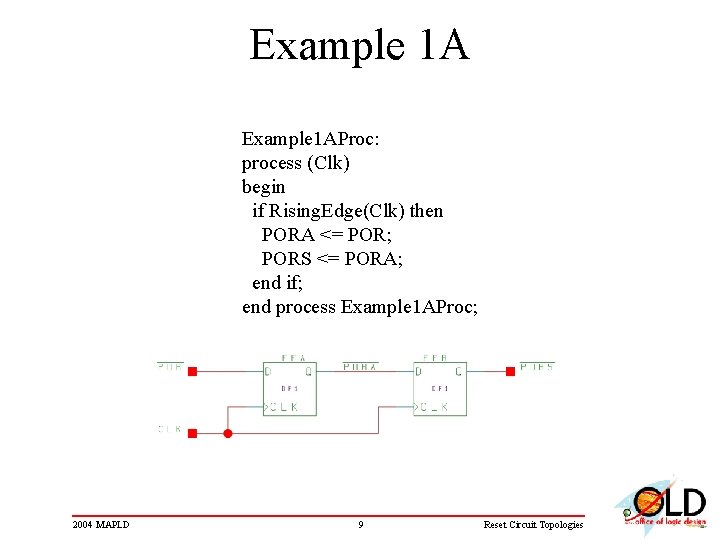

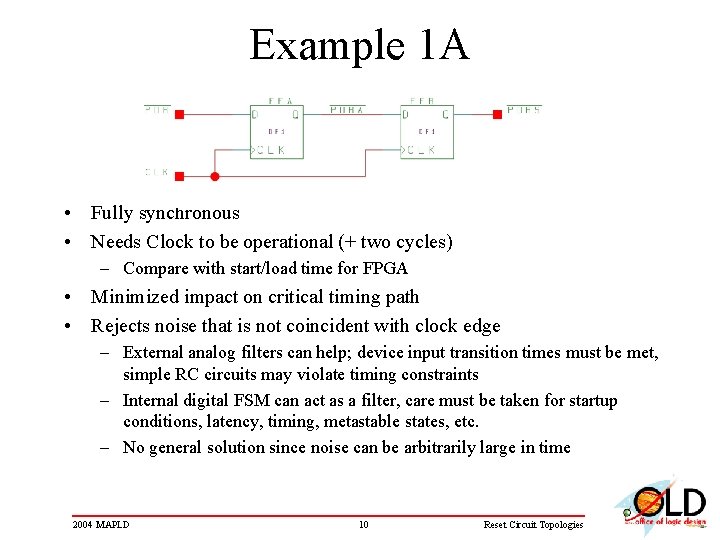

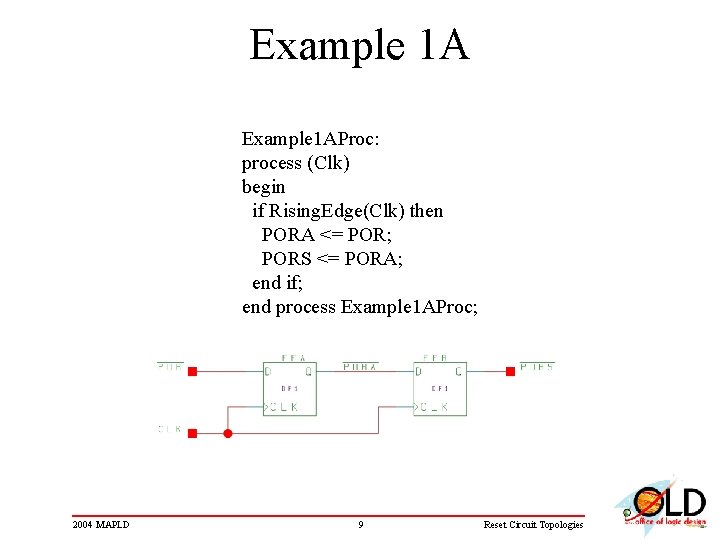

Example 1 AProc: process (Clk) begin if Rising. Edge(Clk) then PORA <= POR; PORS <= PORA; end if; end process Example 1 AProc; 2004 MAPLD 9 Reset Circuit Topologies

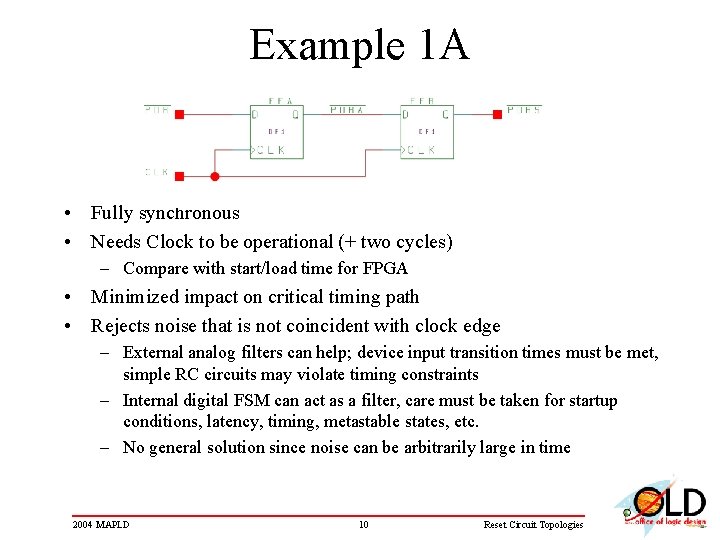

Example 1 A • Fully synchronous • Needs Clock to be operational (+ two cycles) – Compare with start/load time for FPGA • Minimized impact on critical timing path • Rejects noise that is not coincident with clock edge – External analog filters can help; device input transition times must be met, simple RC circuits may violate timing constraints – Internal digital FSM can act as a filter, care must be taken for startup conditions, latency, timing, metastable states, etc. – No general solution since noise can be arbitrarily large in time 2004 MAPLD 10 Reset Circuit Topologies

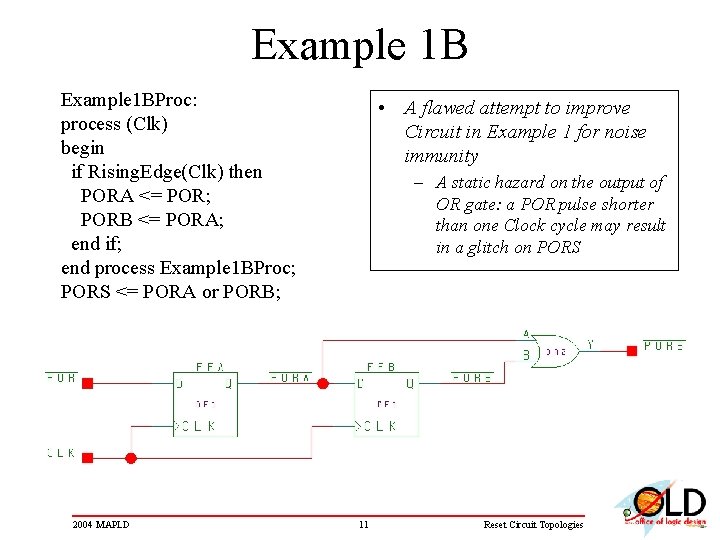

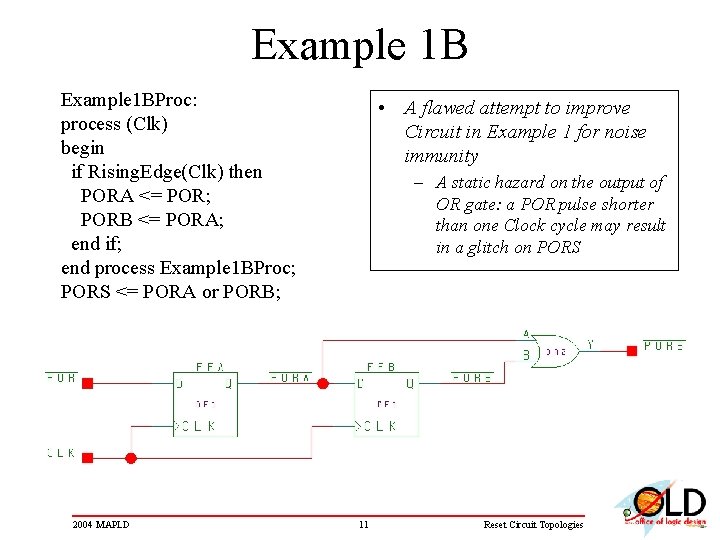

Example 1 BProc: process (Clk) begin if Rising. Edge(Clk) then PORA <= POR; PORB <= PORA; end if; end process Example 1 BProc; PORS <= PORA or PORB; 2004 MAPLD • A flawed attempt to improve Circuit in Example 1 for noise immunity – A static hazard on the output of OR gate: a POR pulse shorter than one Clock cycle may result in a glitch on PORS 11 Reset Circuit Topologies

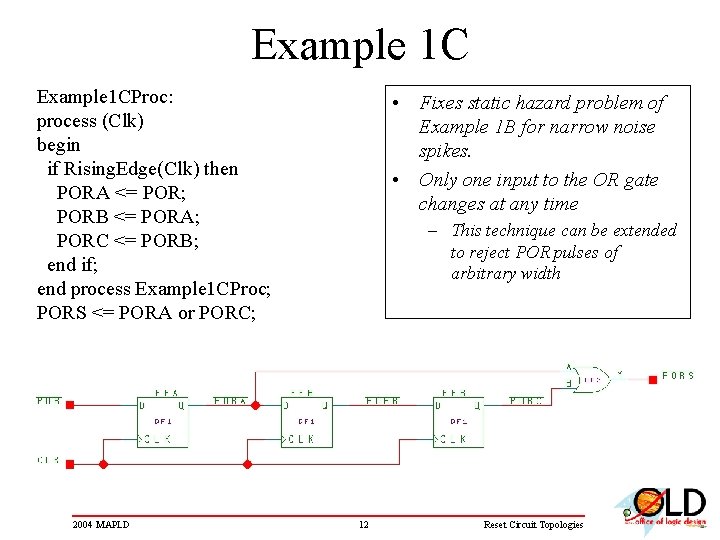

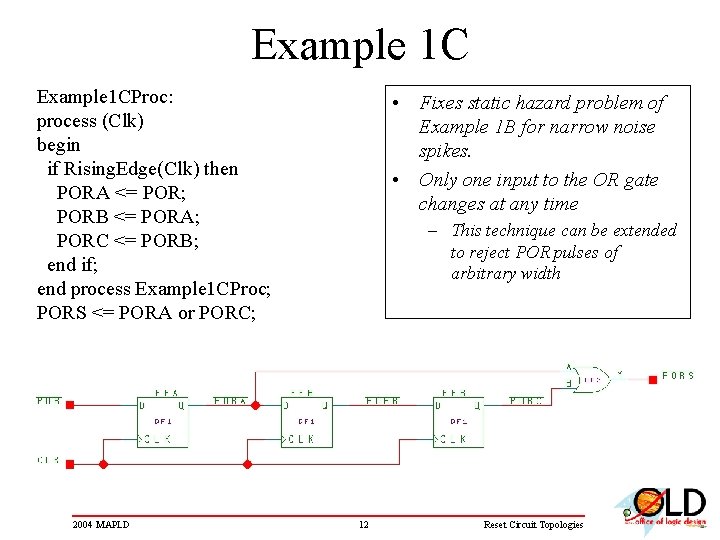

Example 1 CProc: process (Clk) begin if Rising. Edge(Clk) then PORA <= POR; PORB <= PORA; PORC <= PORB; end if; end process Example 1 CProc; PORS <= PORA or PORC; 2004 MAPLD • Fixes static hazard problem of Example 1 B for narrow noise spikes. • Only one input to the OR gate changes at any time – This technique can be extended to reject POR pulses of arbitrary width 12 Reset Circuit Topologies

Asynchronously Applied, Synchronously Removed Circuits Remember, many programmable logic devices will not allow inputs in or outputs out until the device starts. 2004 MAPLD 13 Reset Circuit Topologies

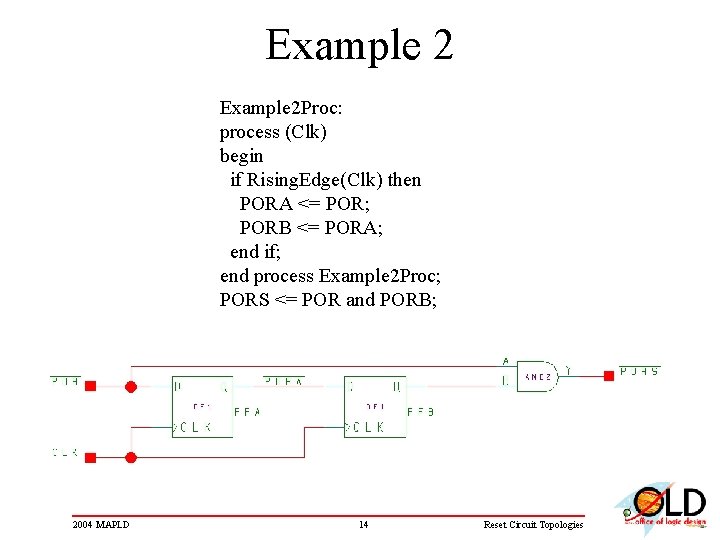

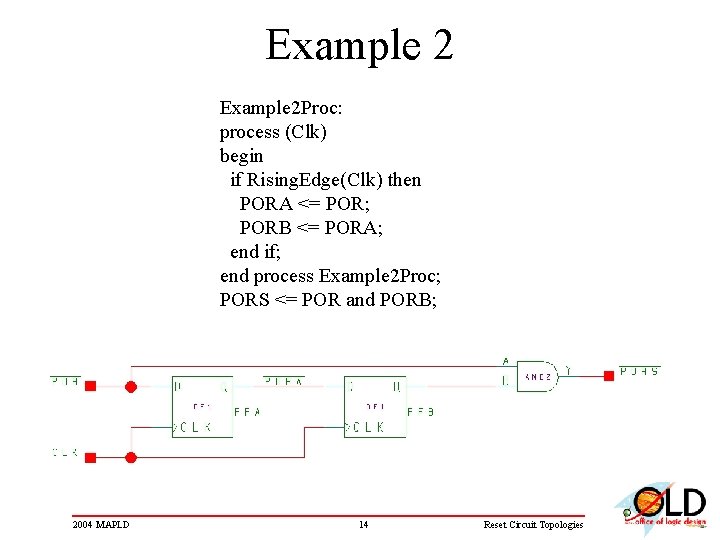

Example 2 Proc: process (Clk) begin if Rising. Edge(Clk) then PORA <= POR; PORB <= PORA; end if; end process Example 2 Proc; PORS <= POR and PORB; 2004 MAPLD 14 Reset Circuit Topologies

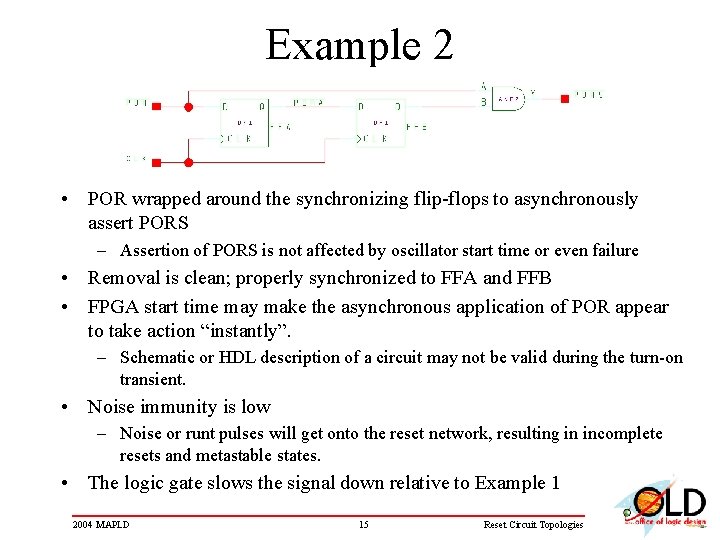

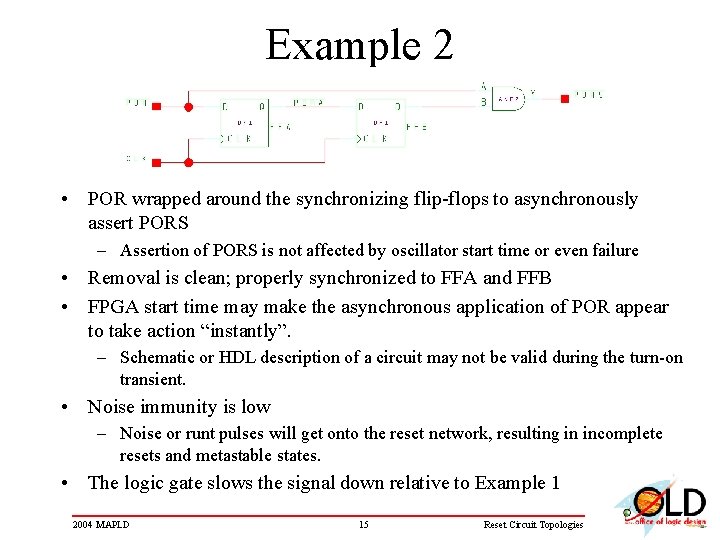

Example 2 • POR wrapped around the synchronizing flip-flops to asynchronously assert PORS – Assertion of PORS is not affected by oscillator start time or even failure • Removal is clean; properly synchronized to FFA and FFB • FPGA start time may make the asynchronous application of POR appear to take action “instantly”. – Schematic or HDL description of a circuit may not be valid during the turn-on transient. • Noise immunity is low – Noise or runt pulses will get onto the reset network, resulting in incomplete resets and metastable states. • The logic gate slows the signal down relative to Example 1 2004 MAPLD 15 Reset Circuit Topologies

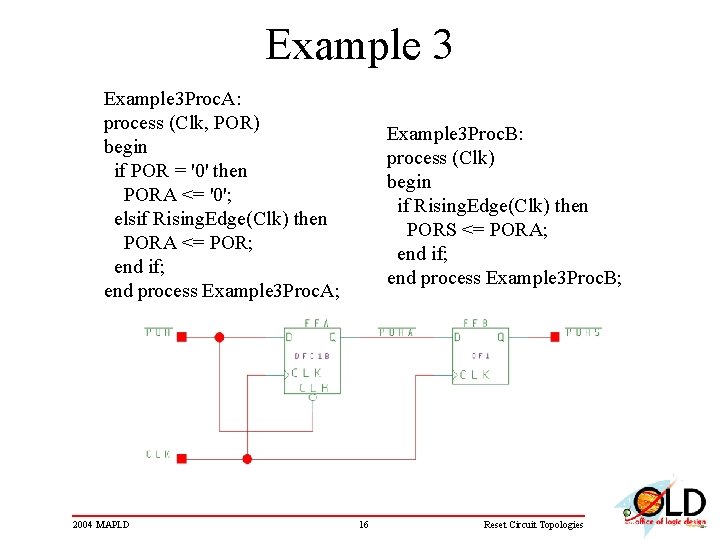

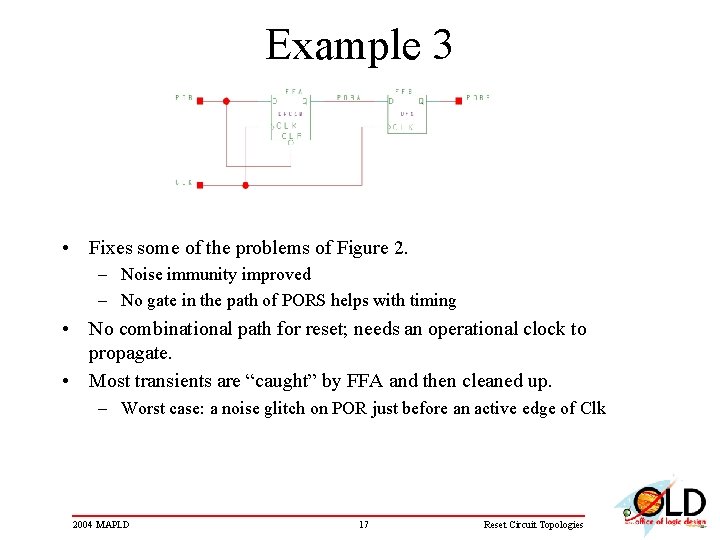

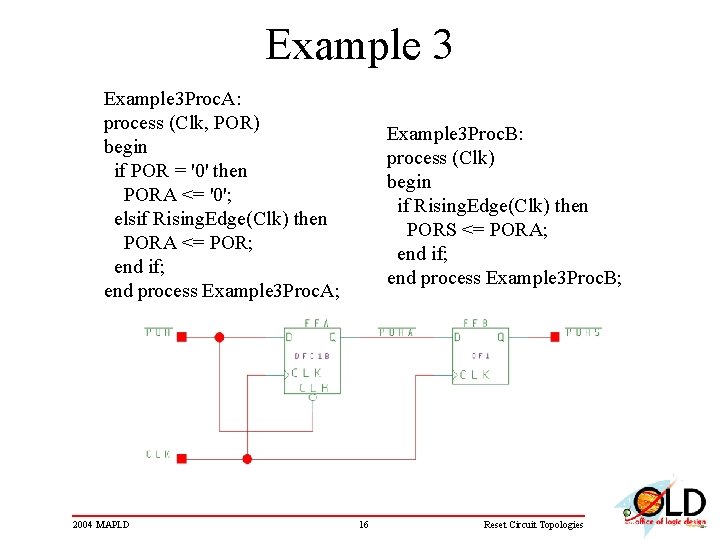

Example 3 Proc. A: process (Clk, POR) begin if POR = '0' then PORA <= '0'; elsif Rising. Edge(Clk) then PORA <= POR; end if; end process Example 3 Proc. A; 2004 MAPLD Example 3 Proc. B: process (Clk) begin if Rising. Edge(Clk) then PORS <= PORA; end if; end process Example 3 Proc. B; 16 Reset Circuit Topologies

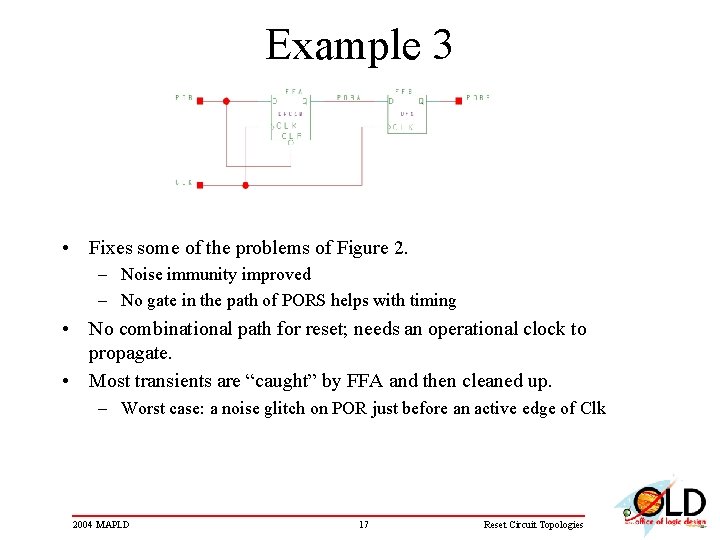

Example 3 • Fixes some of the problems of Figure 2. – Noise immunity improved – No gate in the path of PORS helps with timing • No combinational path for reset; needs an operational clock to propagate. • Most transients are “caught” by FFA and then cleaned up. – Worst case: a noise glitch on POR just before an active edge of Clk 2004 MAPLD 17 Reset Circuit Topologies

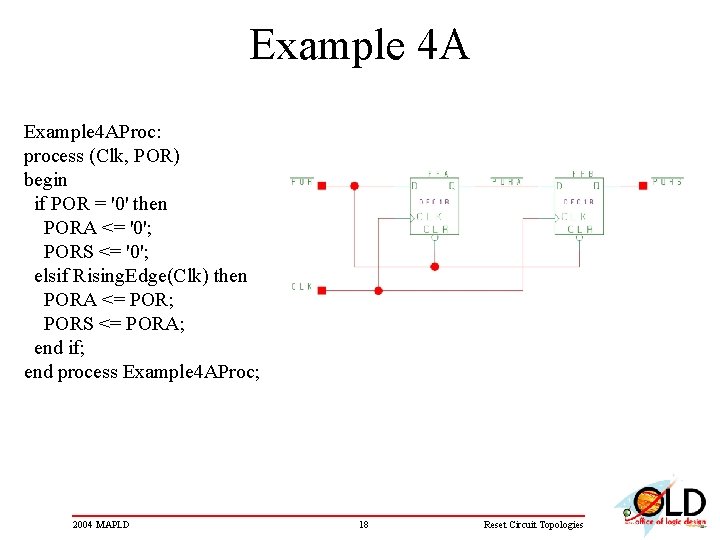

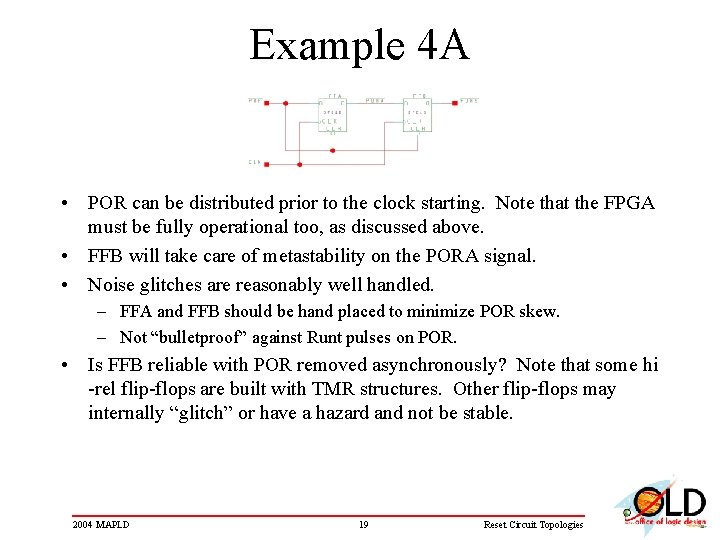

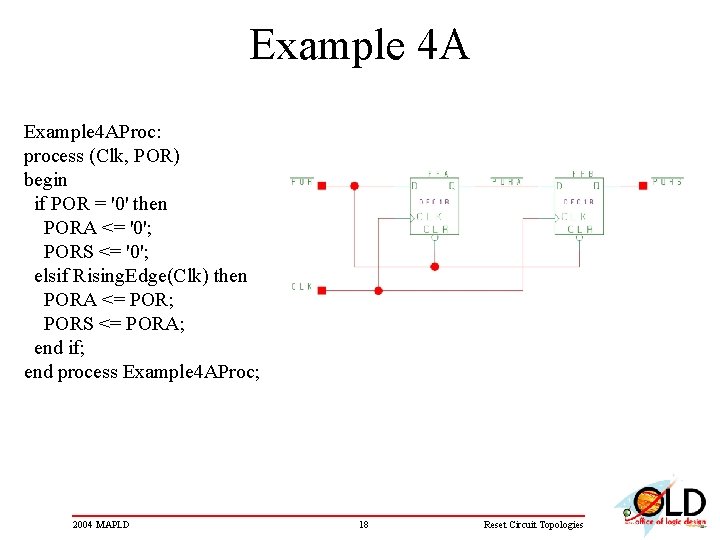

Example 4 AProc: process (Clk, POR) begin if POR = '0' then PORA <= '0'; PORS <= '0'; elsif Rising. Edge(Clk) then PORA <= POR; PORS <= PORA; end if; end process Example 4 AProc; 2004 MAPLD 18 Reset Circuit Topologies

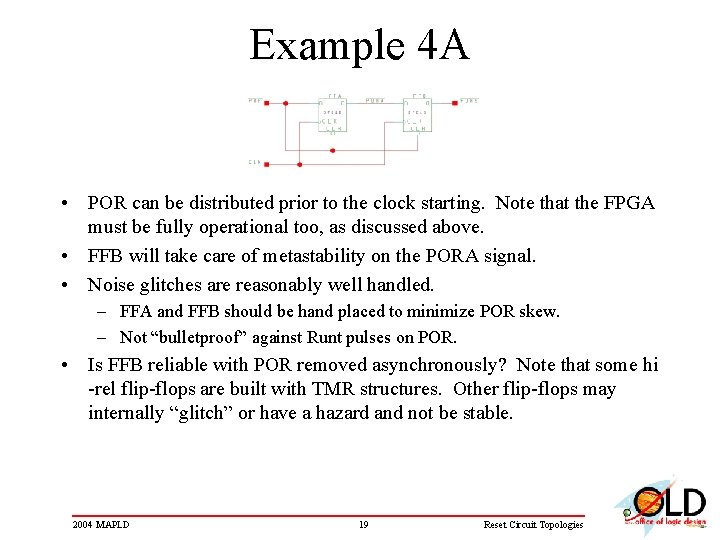

Example 4 A • POR can be distributed prior to the clock starting. Note that the FPGA must be fully operational too, as discussed above. • FFB will take care of metastability on the PORA signal. • Noise glitches are reasonably well handled. – FFA and FFB should be hand placed to minimize POR skew. – Not “bulletproof” against Runt pulses on POR. • Is FFB reliable with POR removed asynchronously? Note that some hi -rel flip-flops are built with TMR structures. Other flip-flops may internally “glitch” or have a hazard and not be stable. 2004 MAPLD 19 Reset Circuit Topologies

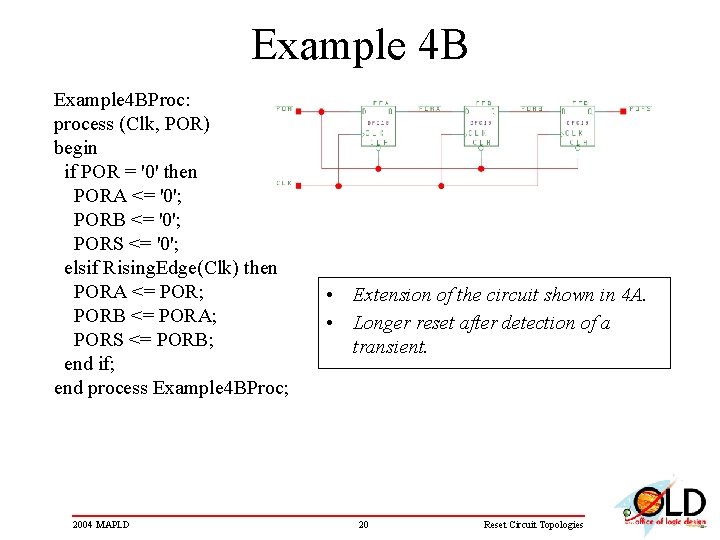

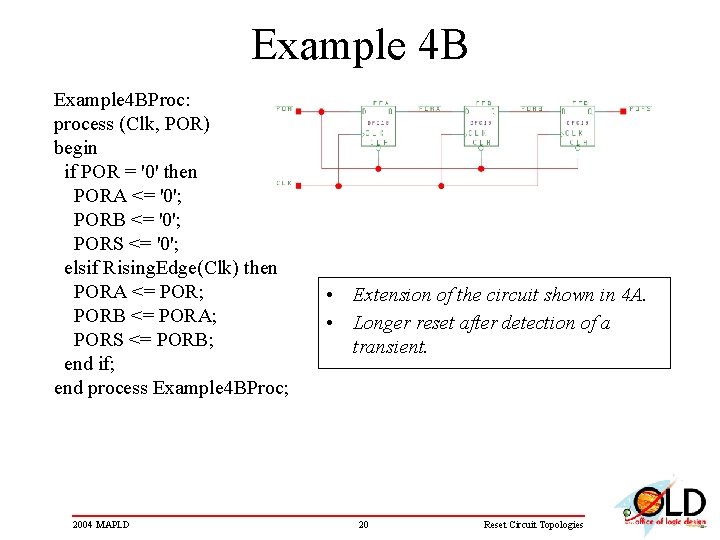

Example 4 BProc: process (Clk, POR) begin if POR = '0' then PORA <= '0'; PORB <= '0'; PORS <= '0'; elsif Rising. Edge(Clk) then PORA <= POR; PORB <= PORA; PORS <= PORB; end if; end process Example 4 BProc; 2004 MAPLD • Extension of the circuit shown in 4 A. • Longer reset after detection of a transient. 20 Reset Circuit Topologies

Notes and References 1. "Some Characteristics of Crystal Clock Oscillators During the Turn-On Transient. " This application note discusses and shows what the output of an oscillator may be during the turn-on transient. Examples shows include runt pulses of various sizes and polarities. http: //klabs. org/richcontent/General_Application_Notes/oscillator/osc_start_up_note/index. htm 2. "Asynchronous & Synchronous Reset Design Techniques - Part Deux“ http: //klabs. org/richcontent/General_Application_Notes/reset_sync_async_v 2. pdf 3. "Small Explorer WIRE Failure Investigation Report. " This is Appendix F of the WIRE Mishap Investigation Board Report, June 8, 1999. http: //klabs. org/richcontent/Reports/WIRE_Report. PDF 4. "Startup Transient, " from Advanced Design: Designing for Reliability, 2001 MAPLD International Conference, Laurel, MD, September 10, 2001. http: //klabs. org/richcontent/Tutorial/Mini. Courses/reliable_design_mapld 2001/D_Startup. Transient. ppt 5. "Current Radiation Issues for Programmable Elements and Devices, " IEEE Transactions on Nuclear Science, December 1998. http: //klabs. org/richcontent/Papers/NSREC 98_Paper. pdf 6. "RH 1020 Single Event Clock Upset Summary Report, " Richard B. Katz and J. J. Wang, March 5, 1998 http: //klabs. org/richcontent/fpga_content/Act_1/rh 1020_clk_upset_White_paper. PDF 7. Thanks to Melanie Berg of Ball for the helpful comments and suggesting to add notes about the extra delay in the reset path when using topologies such as those shown in Figure 2. 8. "Hazard Analysis, " from Design Guidelines and Criteria for Space Flight Digital Electronics. http: //klabs. org/DEI/References/design_guidelines/nasa_guidelines/hazards. htm and http: //klabs. org/DEI/References/design_guidelines/nasa_guidelines/index. htm 9. Timing Analysis of Asynchronous Signals http: //klabs. org/richcontent/General_Application_Notes/parts/removal_time. htm 2004 MAPLD 21 Reset Circuit Topologies