Research Update Alan Mishchenko Department of EECS UC

- Slides: 11

Research Update Alan Mishchenko Department of EECS UC Berkeley

Overview l l l SAT-based synthesis in general Remapping of standard cells for area Fact extract and division algorithms Improved SAT sweeping Scaling synthesis to millions of nodes 2

SAT-based synthesis in general l Several flavors of SAT-based synthesis l l l “Exact minimum circuit” synthesis Don’t-care-based synthesis Structural synthesis

Remapping of standard cells for area l l l This is related to a new SAT-based synthesis project started a year ago The main idea is to represent the care-set of a node as a circuit and use it in the SAT solver as a constrain Results are encouraging

Fact extract and division algorithms l l l A new implementation of “fast_extract” has been developed, which has a linear complexity in terms of cubes (rather than quadratic) The main idea is to use a hash-table to find shared divisors (rather than cube-pair enumeration) Results are good l The same quality but improved runtime for large test-cases

Improved SAT sweeping l SAT sweeping is important in synthesis and verification l l l Difficulty is how to combine SAT and simulation The new idea is to perform SAT and simulation in a wave -front manner l l Not only for netlist reduction, but also for choice computation Update wave-front with new sim patterns Incrementally simulation while moving wave-front by one node May be combined with several custom SAT features Should be faster and more scalable

Scaling synthesis to millions of nodes l Scalability is a moving target l l l “How long it will take you to synthesize/map 1 B AIG nodes? ” Partitioning can be used, but why partition with singlethreaded implementation can be made faster Basically, need to rethink all algorithms from the point of view of their “scalability for 1 B AIG nodes”

Additional Slides

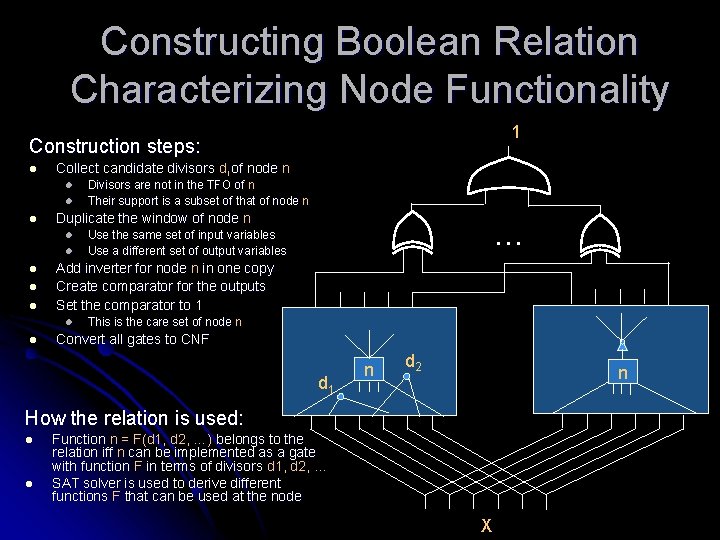

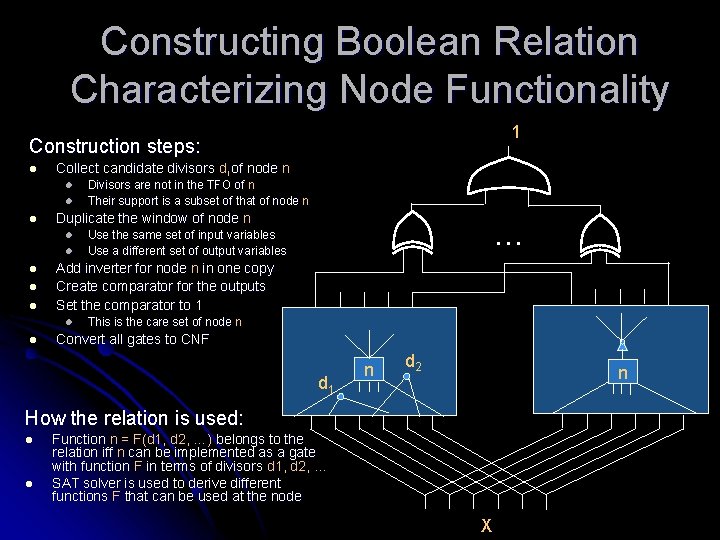

Constructing Boolean Relation Characterizing Node Functionality 1 Construction steps: l Collect candidate divisors di of node n l l l Duplicate the window of node n l l l … Use the same set of input variables Use a different set of output variables Add inverter for node n in one copy Create comparator for the outputs Set the comparator to 1 l l Divisors are not in the TFO of n Their support is a subset of that of node n This is the care set of node n Convert all gates to CNF d 1 n d 2 n How the relation is used: l l Function n = F(d 1, d 2, …) belongs to the relation iff n can be implemented as a gate with function F in terms of divisors d 1, d 2, … SAT solver is used to derive different functions F that can be used at the node X

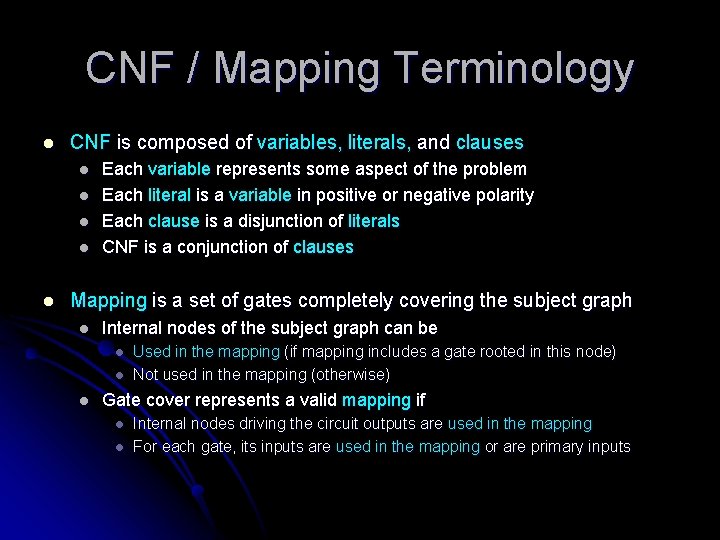

CNF / Mapping Terminology l CNF is composed of variables, literals, and clauses l l l Each variable represents some aspect of the problem Each literal is a variable in positive or negative polarity Each clause is a disjunction of literals CNF is a conjunction of clauses Mapping is a set of gates completely covering the subject graph l Internal nodes of the subject graph can be l l l Used in the mapping (if mapping includes a gate rooted in this node) Not used in the mapping (otherwise) Gate cover represents a valid mapping if l l Internal nodes driving the circuit outputs are used in the mapping For each gate, its inputs are used in the mapping or are primary inputs

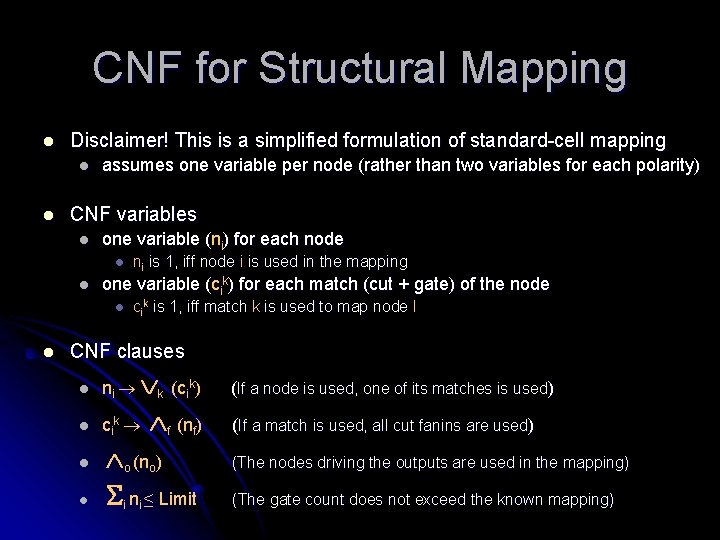

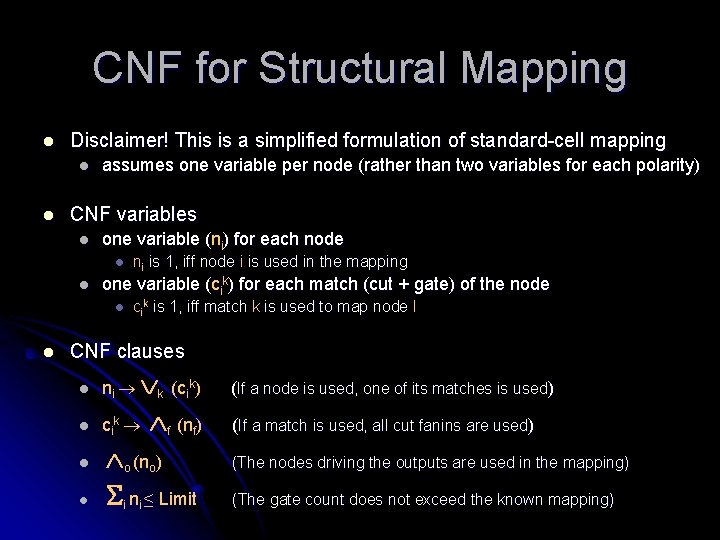

CNF for Structural Mapping l Disclaimer! This is a simplified formulation of standard-cell mapping l l assumes one variable per node (rather than two variables for each polarity) CNF variables l one variable (ni) for each node l l one variable (cik) for each match (cut + gate) of the node l l ni is 1, iff node i is used in the mapping cik is 1, iff match k is used to map node I CNF clauses l ni k (cik) l cik l l f (nf) o (no) i ni ≤ Limit (If a node is used, one of its matches is used) (If a match is used, all cut fanins are used) (The nodes driving the outputs are used in the mapping) (The gate count does not exceed the known mapping)