Reliability Enhancement via Sleep Transistors Frank Sill Torres

Reliability Enhancement via Sleep Transistors Frank Sill Torres+, Claas Cornelius*, Dirk Timmermann* + Department of Electronic Engineering, Federal University of Minas Gerais, Belo Horizonte, Brazil * Inst. of Applied Microelectronics and Computer Engineering, University of Rostock, Germany

Focus / Main ideas 1. Approach for extension of expected lifetime 2. Application of simulation environment for MTTF estimation Sill Torres et al. – Reliability w/ Sleep Transistors 2

Outline § Motivation § Preliminaries § Reliability Enhancement via Sleep Transistors § Simulation Environment § Results § Conclusion Sill Torres et al. – Reliability w/ Sleep Transistors 3

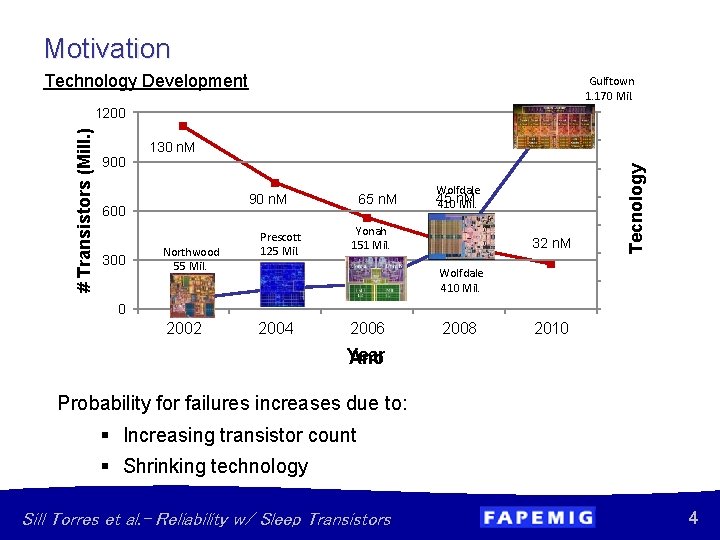

Motivation Technology Development Gulftown 1. 170 Mil. 900 140 n. M 100 n. M 90 n. M 600 300 120 n. M 130 n. M Tecnologia Tecnology # Transistors (Mill. ) 1200 Northwood 55 Mil. Prescott 125 Mil. 65 n. M Wolfdale 45 410 n. M Mil. 80 n. M 60 n. M Yonah 151 Mil. 32 n. M Wolfdale 410 Mil. 40 n. M 2002 2004 2006 2008 2010 Year Ano Probability for failures increases due to: § Increasing transistor count § Shrinking technology Sill Torres et al. – Reliability w/ Sleep Transistors 4

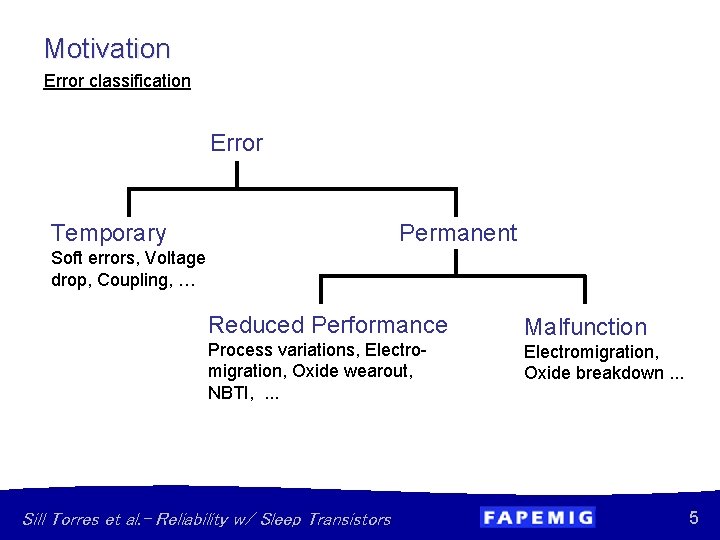

Motivation Error classification Error Permanent Temporary Soft errors, Voltage drop, Coupling, … Reduced Performance Process variations, Electromigration, Oxide wearout, NBTI, . . . Sill Torres et al. – Reliability w/ Sleep Transistors Malfunction Electromigration, Oxide breakdown. . . 5

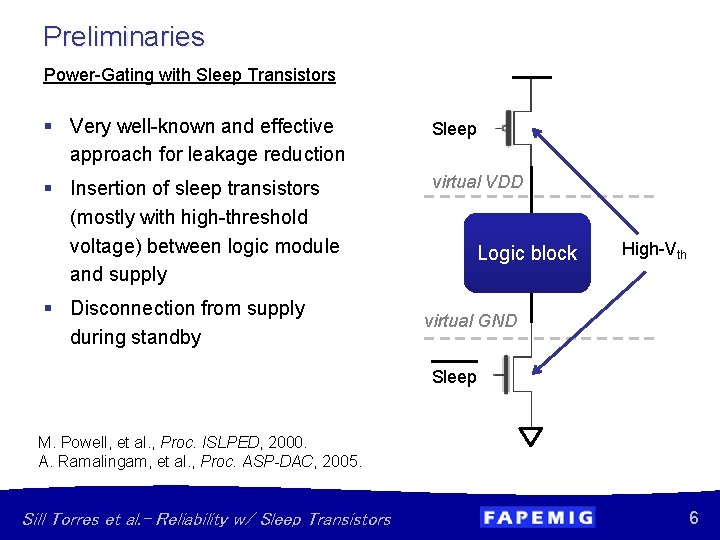

Preliminaries Power-Gating with Sleep Transistors § Very well-known and effective approach for leakage reduction Sleep § Insertion of sleep transistors (mostly with high-threshold voltage) between logic module and supply virtual VDD § Disconnection from supply during standby Logic block High-Vth virtual GND Sleep M. Powell, et al. , Proc. ISLPED, 2000. A. Ramalingam, et al. , Proc. ASP-DAC, 2005. Sill Torres et al. – Reliability w/ Sleep Transistors 6

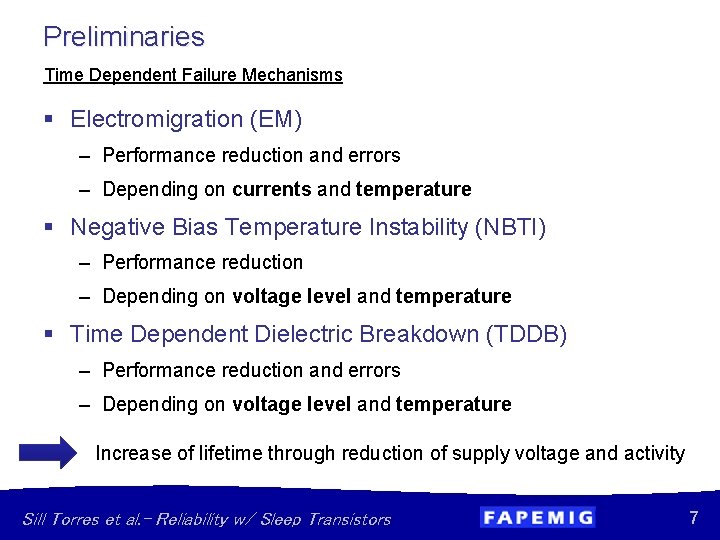

Preliminaries Time Dependent Failure Mechanisms § Electromigration (EM) – Performance reduction and errors – Depending on currents and temperature § Negative Bias Temperature Instability (NBTI) – Performance reduction – Depending on voltage level and temperature § Time Dependent Dielectric Breakdown (TDDB) – Performance reduction and errors – Depending on voltage level and temperature Increase of lifetime through reduction of supply voltage and activity Sill Torres et al. – Reliability w/ Sleep Transistors 7

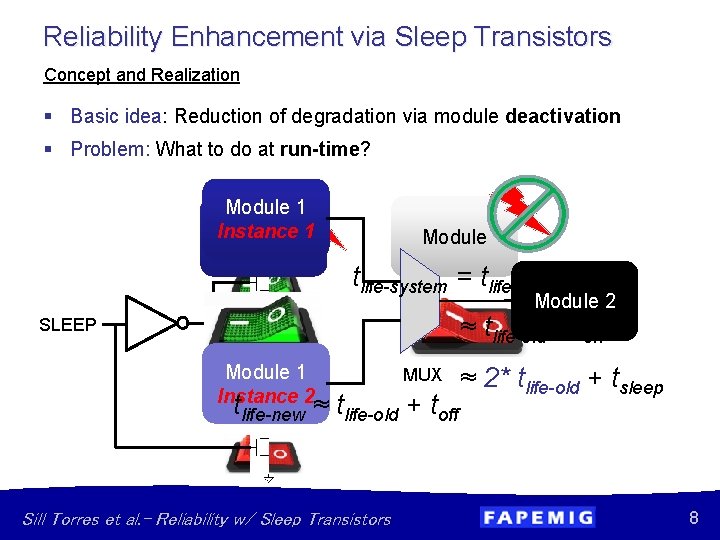

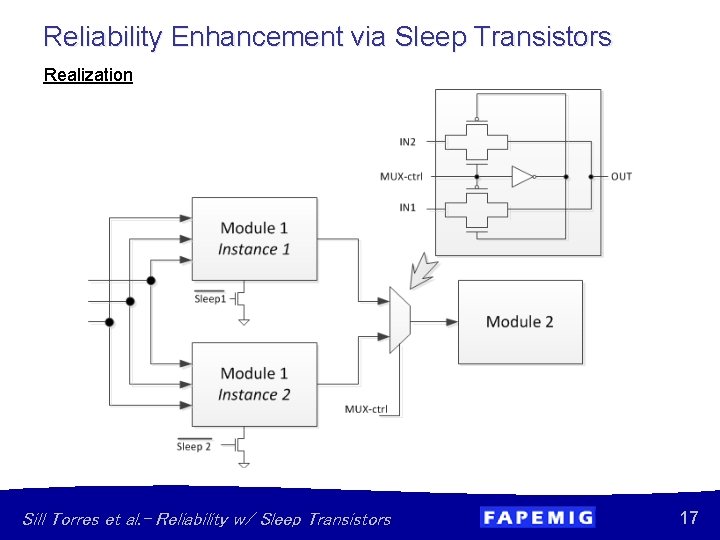

Reliability Enhancement via Sleep Transistors Concept and Realization § Basic idea: Reduction of degradation via module deactivation § Problem: What to do at run-time? Module 1 Instance Module 1 Module tlife-system = tlife-module Module 2 ≈ tlife-old + toff SLEEP Module 1 Instance 2 MUX tlife-new ≈ tlife-old + toff Sill Torres et al. – Reliability w/ Sleep Transistors ≈ 2* tlife-old + tsleep 8

Reliability Enhancement via Sleep Transistors Expectations § Lifetime – Increase by more than factor 2 (not linear relation between effective voltage and failure mechanisms) § Area – Increase by slightly more than factor 2 – Ca. 50 % less than Triple Modular Redundancy (TMR) § Power dissipation – Slight increase of dynamic power dissipation – Increase of leakage by ca. factor 2 § Delay – Slight increase through multiplexer delays Sill Torres et al. – Reliability w/ Sleep Transistors 9

Reliability Enhancement via Sleep Transistors Comments § Application – Limited improvements for devices with long standby times (mobiles, home PCs) – High improvements for high availability applications (server, aerospace equipment, mobile communication nodes) § Multiplexer – Problem: no deactivation of multiplexer – Solution: use of transmission gates (less vulnerable) § Control signals (for sleep transistor, multiplexer) – Logic for control signal generation must be reliable too – Hence: reliable implementation (High. Tox, wire widening, …) – More research required Sill Torres et al. – Reliability w/ Sleep Transistors 10

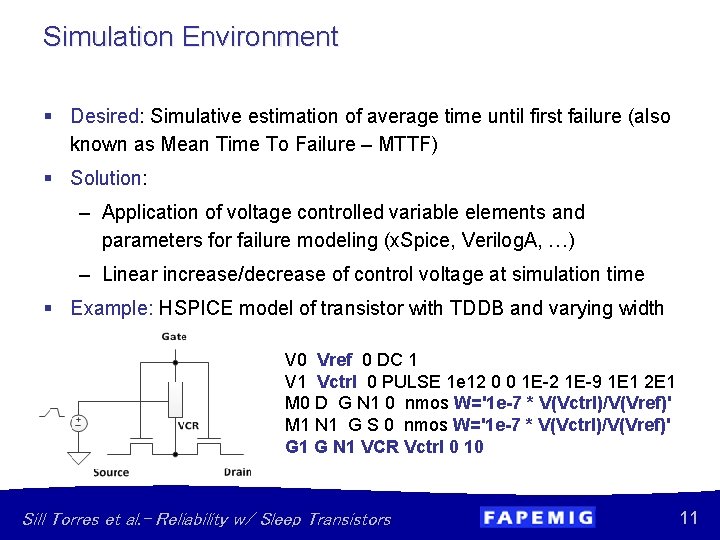

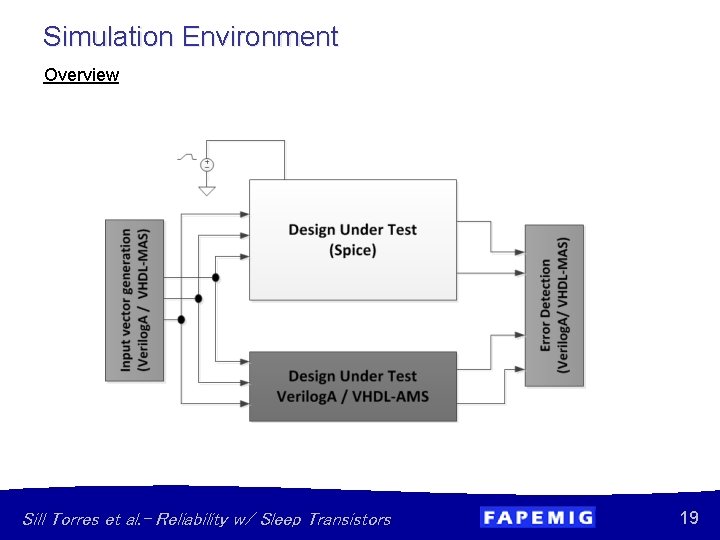

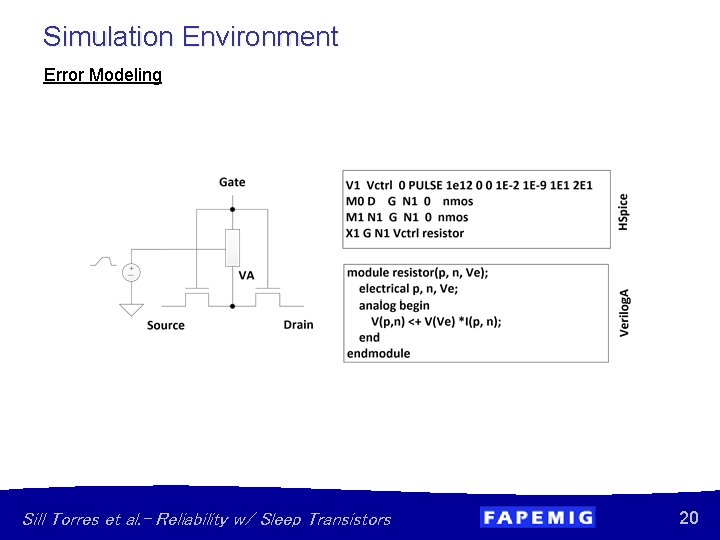

Simulation Environment § Desired: Simulative estimation of average time until first failure (also known as Mean Time To Failure – MTTF) § Solution: – Application of voltage controlled variable elements and parameters for failure modeling (x. Spice, Verilog. A, …) – Linear increase/decrease of control voltage at simulation time § Example: HSPICE model of transistor with TDDB and varying width V 0 Vref 0 DC 1 Vctrl 0 PULSE 1 e 12 0 0 1 E-2 1 E-9 1 E 1 2 E 1 M 0 D G N 1 0 nmos W='1 e-7 * V(Vctrl)/V(Vref)' M 1 N 1 G S 0 nmos W='1 e-7 * V(Vctrl)/V(Vref)' G 1 G N 1 VCR Vctrl 0 10 Sill Torres et al. – Reliability w/ Sleep Transistors 11

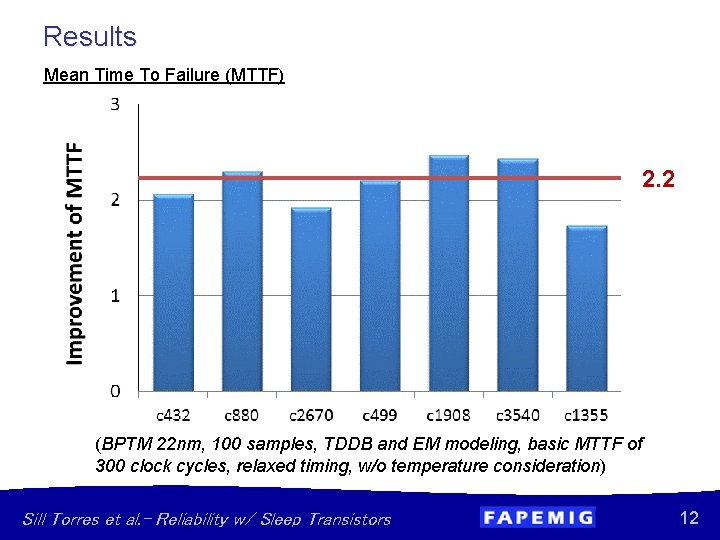

Results Mean Time To Failure (MTTF) 2. 2 (BPTM 22 nm, 100 samples, TDDB and EM modeling, basic MTTF of 300 clock cycles, relaxed timing, w/o temperature consideration) Sill Torres et al. – Reliability w/ Sleep Transistors 12

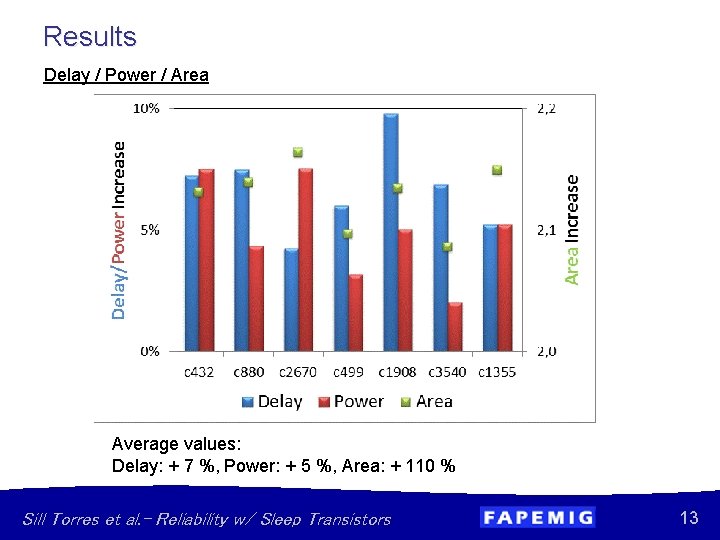

Results Delay / Power / Area Average values: Delay: + 7 %, Power: + 5 %, Area: + 110 % Sill Torres et al. – Reliability w/ Sleep Transistors 13

Conclusion § Progressing susceptibility of current technologies against severe failure mechanisms § Extension of expected lifetime by alternating (de-)activation of redundant blocks via sleep transistors § Environment for simulation of time-dependent degradation of design components § Increase of MTTF by more than factor 2 through proposed approach § Factor 1. 2 for relation of average increase of MTTF and area § Future tasks: – Application of selective redundancy techniques – Merging with approaches on system level – Analysis of control logic Sill Torres et al. – Reliability w/ Sleep Transistors 14

Thank you! franksill@ufmg. br claas. cornelius@uni-rostock. de Sill Torres et al. – Reliability w/ Sleep Transistors 15

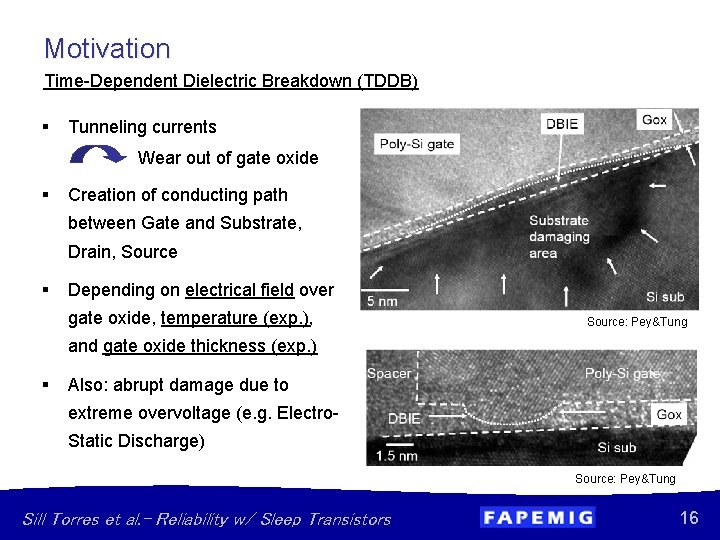

Motivation Time-Dependent Dielectric Breakdown (TDDB) § Tunneling currents Wear out of gate oxide § Creation of conducting path between Gate and Substrate, Drain, Source § Depending on electrical field over gate oxide, temperature (exp. ), Source: Pey&Tung and gate oxide thickness (exp. ) § Also: abrupt damage due to extreme overvoltage (e. g. Electro. Static Discharge) Source: Pey&Tung Sill Torres et al. – Reliability w/ Sleep Transistors 16

Reliability Enhancement via Sleep Transistors Realization Sill Torres et al. – Reliability w/ Sleep Transistors 17

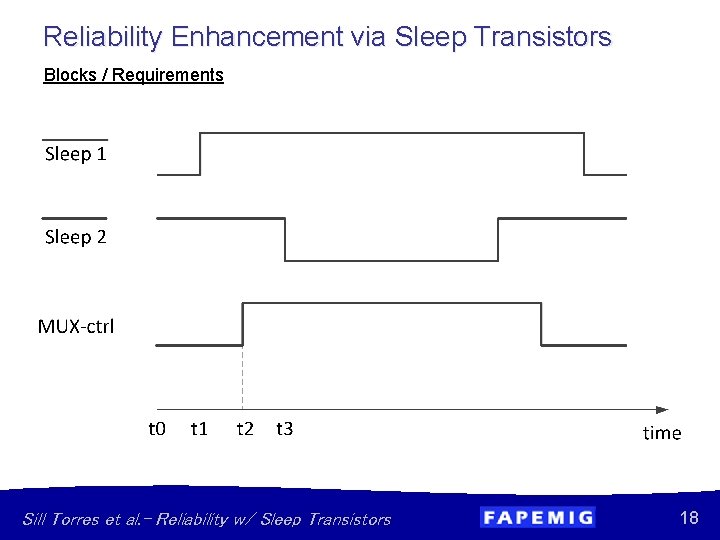

Reliability Enhancement via Sleep Transistors Blocks / Requirements Sill Torres et al. – Reliability w/ Sleep Transistors 18

Simulation Environment Overview Sill Torres et al. – Reliability w/ Sleep Transistors 19

Simulation Environment Error Modeling Sill Torres et al. – Reliability w/ Sleep Transistors 20

- Slides: 20