Registers and Counters COE 202 Digital Logic Design

- Slides: 32

Registers and Counters COE 202 Digital Logic Design Dr. Muhamed Mudawar King Fahd University of Petroleum and Minerals

Presentation Outline v Registers v Shift Registers and their Applications v Ripple Counters v Synchronous Counters Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 2

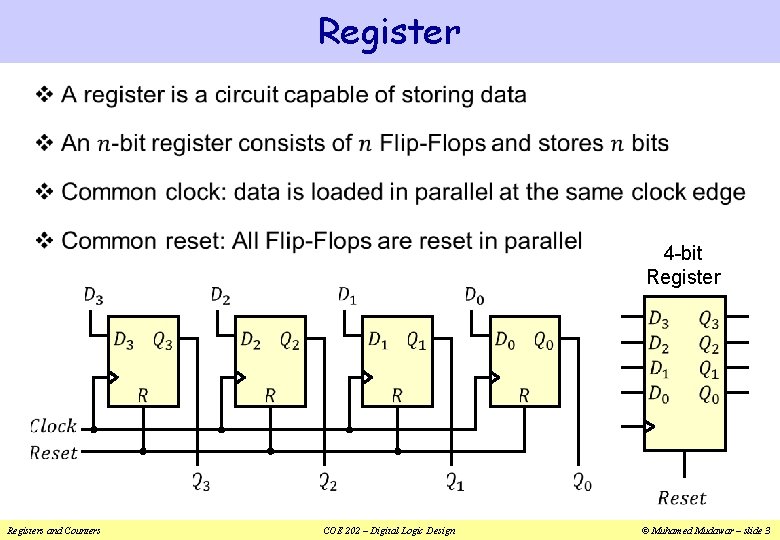

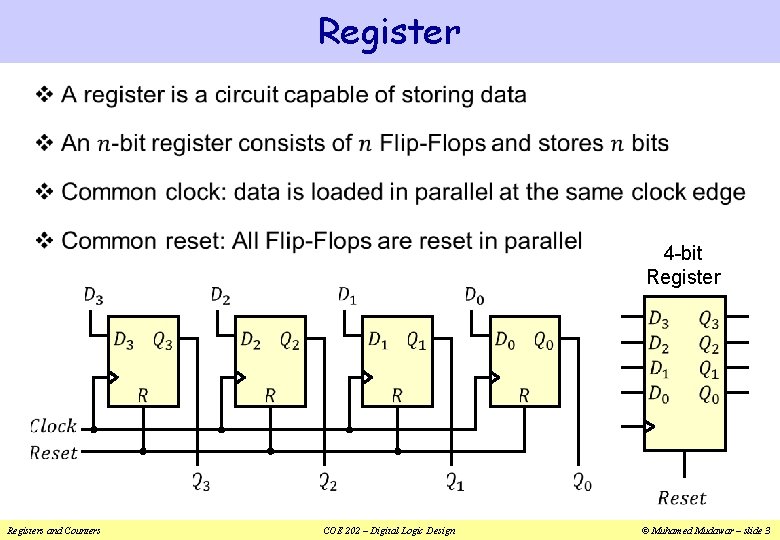

Register v 4 -bit Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 3

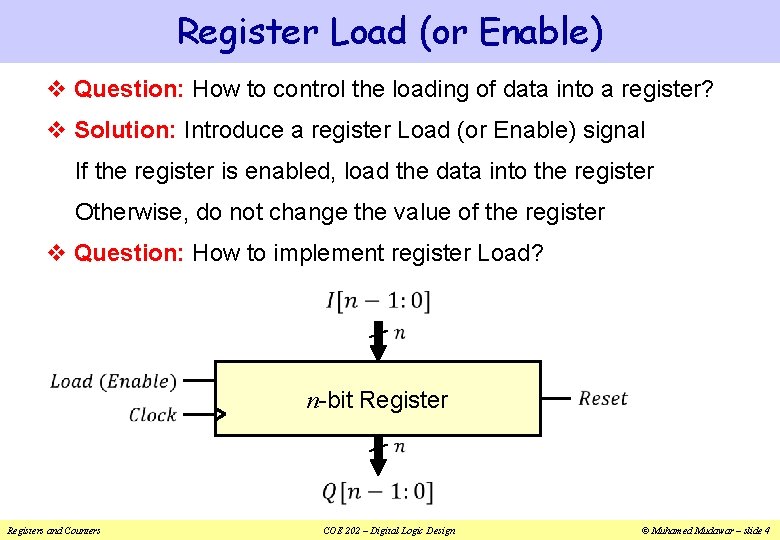

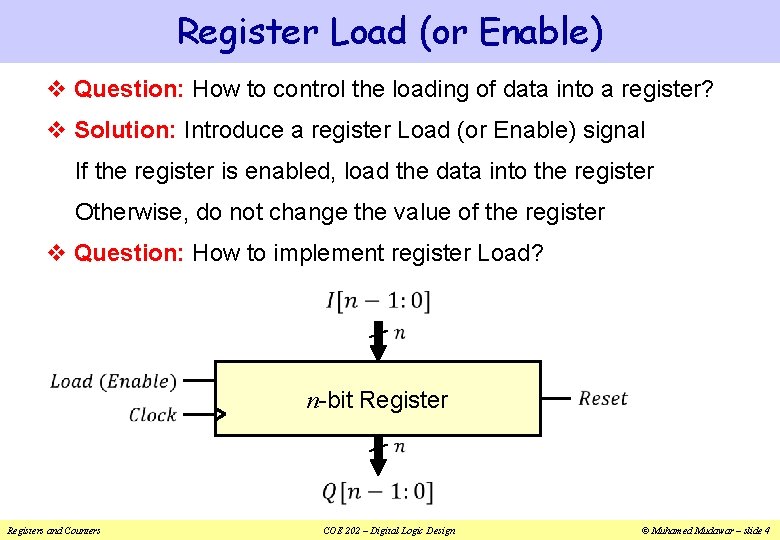

Register Load (or Enable) v Question: How to control the loading of data into a register? v Solution: Introduce a register Load (or Enable) signal If the register is enabled, load the data into the register Otherwise, do not change the value of the register v Question: How to implement register Load? n-bit Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 4

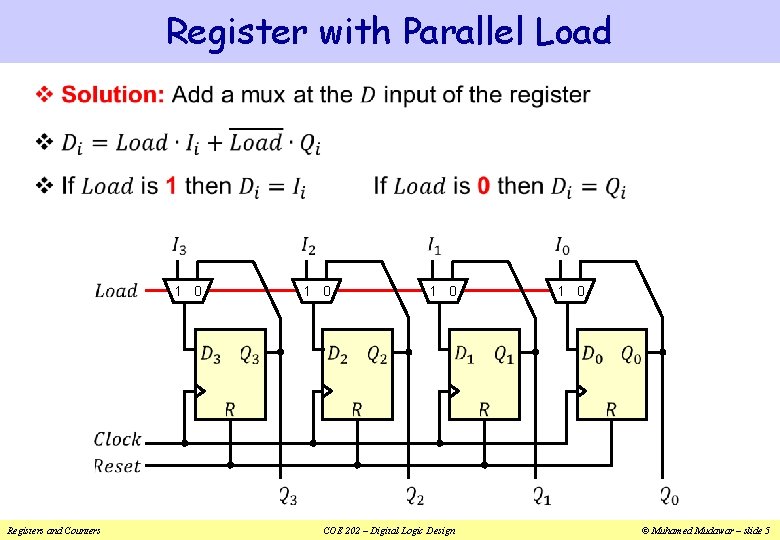

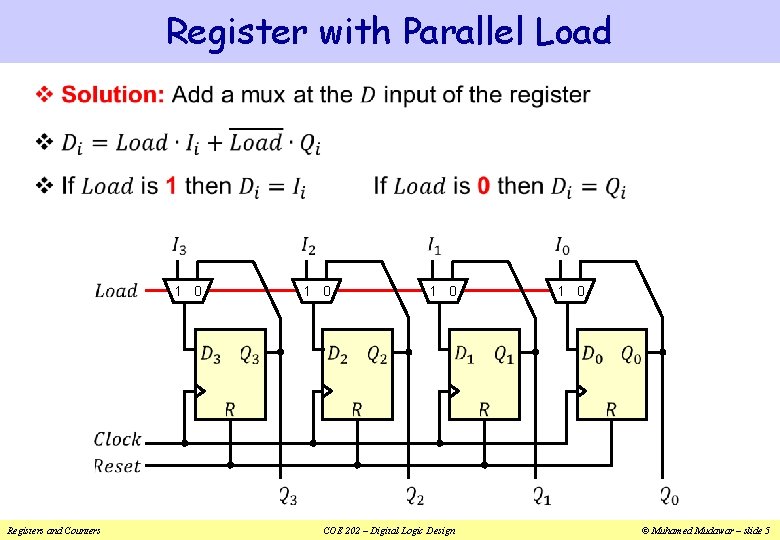

Register with Parallel Load v 1 0 Registers and Counters 1 0 COE 202 – Digital Logic Design 1 0 © Muhamed Mudawar – slide 5

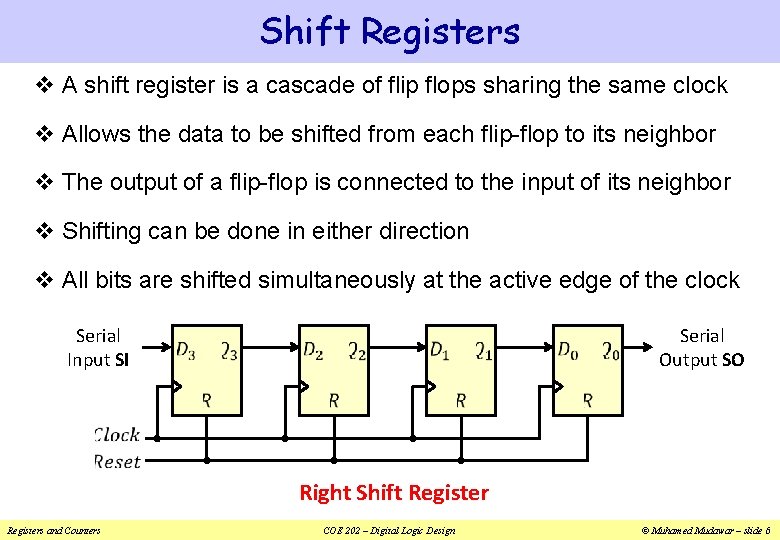

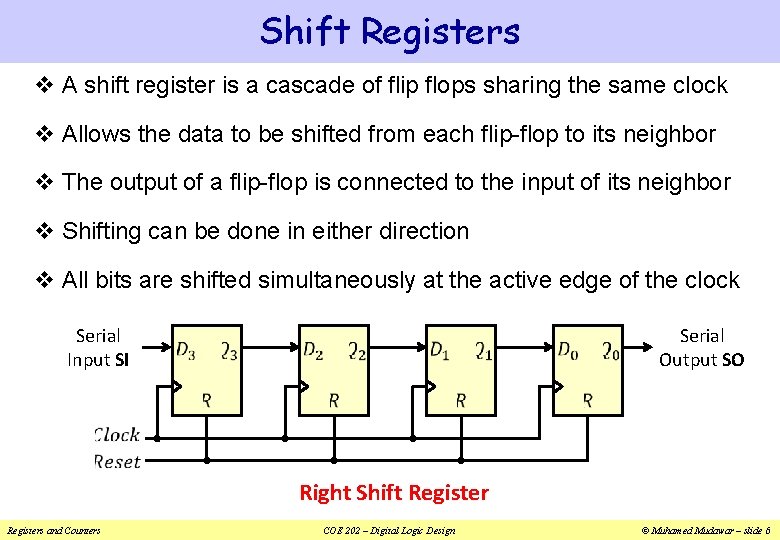

Shift Registers v A shift register is a cascade of flip flops sharing the same clock v Allows the data to be shifted from each flip-flop to its neighbor v The output of a flip-flop is connected to the input of its neighbor v Shifting can be done in either direction v All bits are shifted simultaneously at the active edge of the clock Serial Input SI Serial Output SO Right Shift Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 6

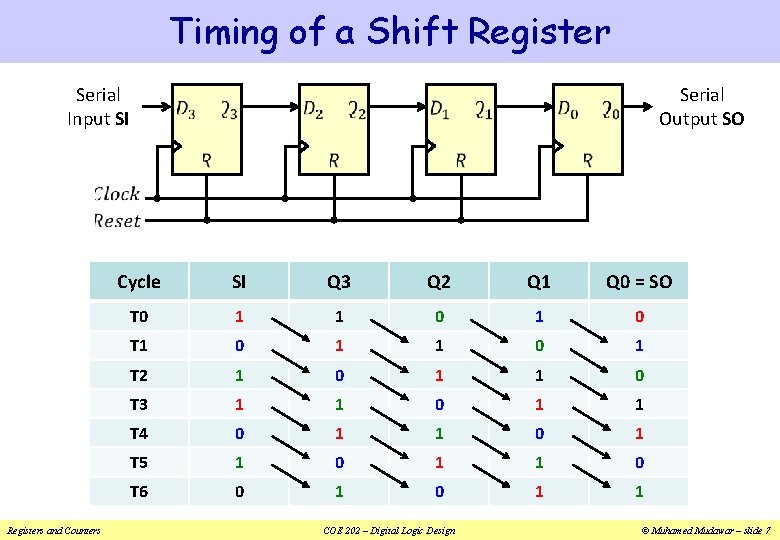

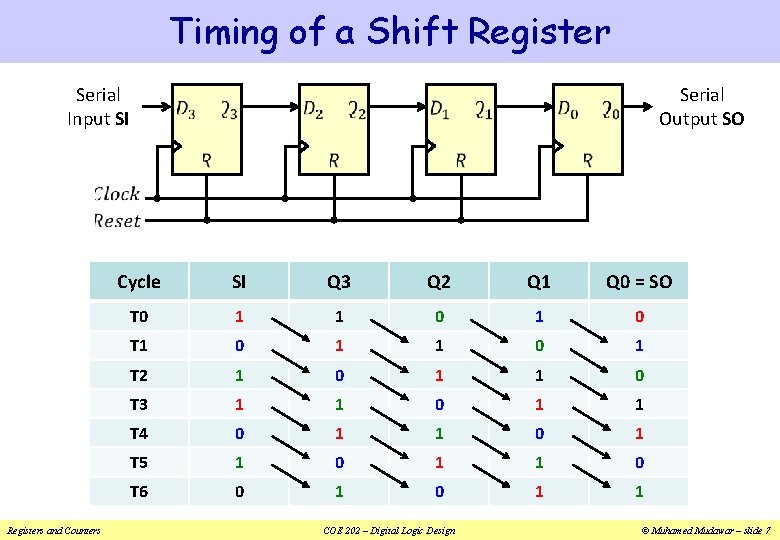

Timing of a Shift Register Serial Input SI Registers and Counters Serial Output SO Cycle SI Q 3 Q 2 Q 1 Q 0 = SO T 0 1 1 0 T 1 0 1 T 2 1 0 1 1 0 T 3 1 1 0 1 1 T 4 0 1 1 0 1 T 5 1 0 1 1 0 T 6 0 1 1 COE 202 – Digital Logic Design © Muhamed Mudawar – slide 7

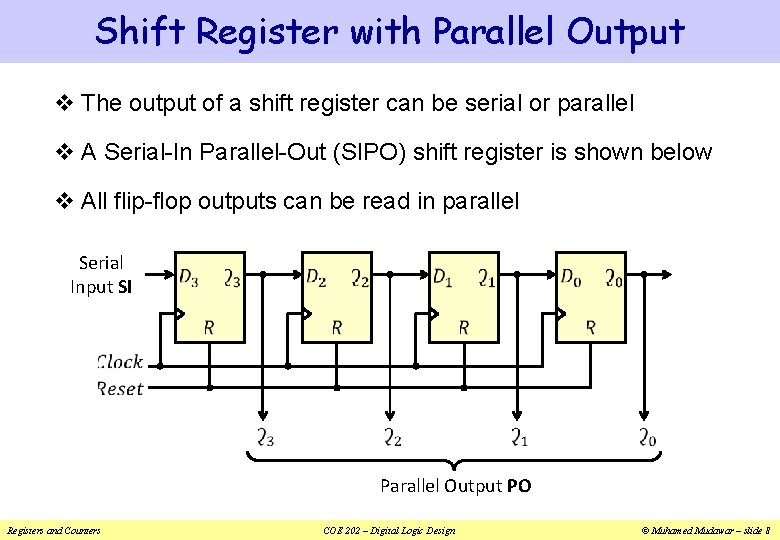

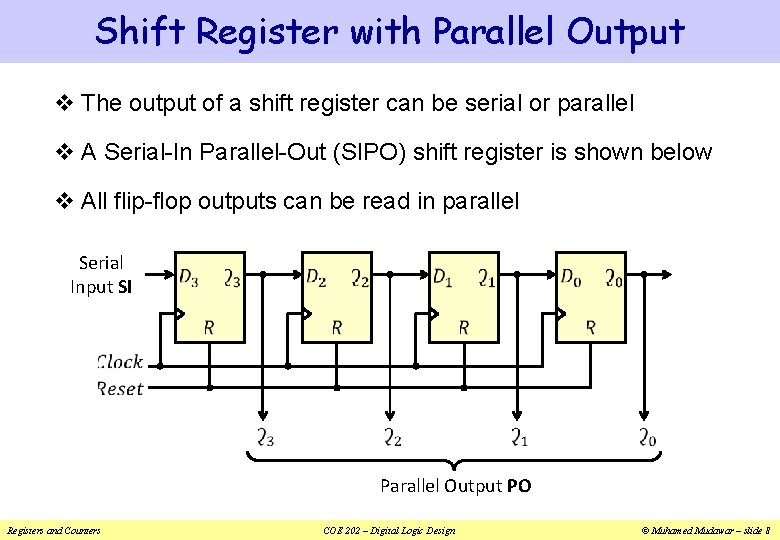

Shift Register with Parallel Output v The output of a shift register can be serial or parallel v A Serial-In Parallel-Out (SIPO) shift register is shown below v All flip-flop outputs can be read in parallel Serial Input SI Parallel Output PO Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 8

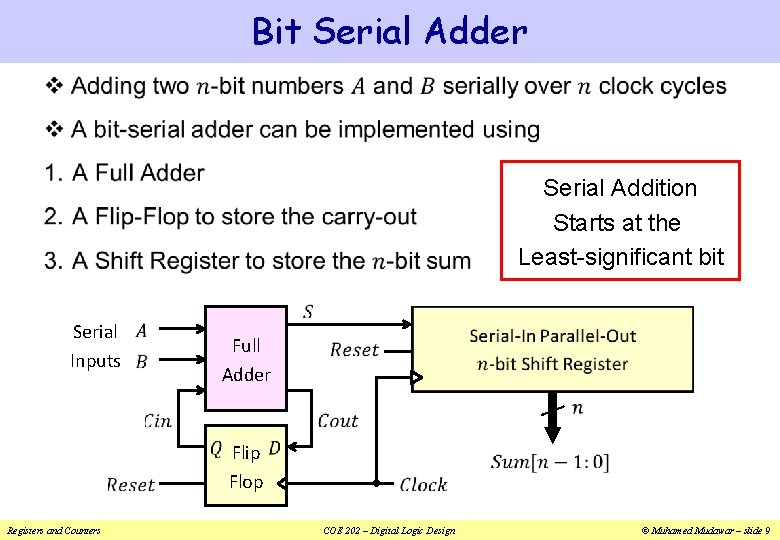

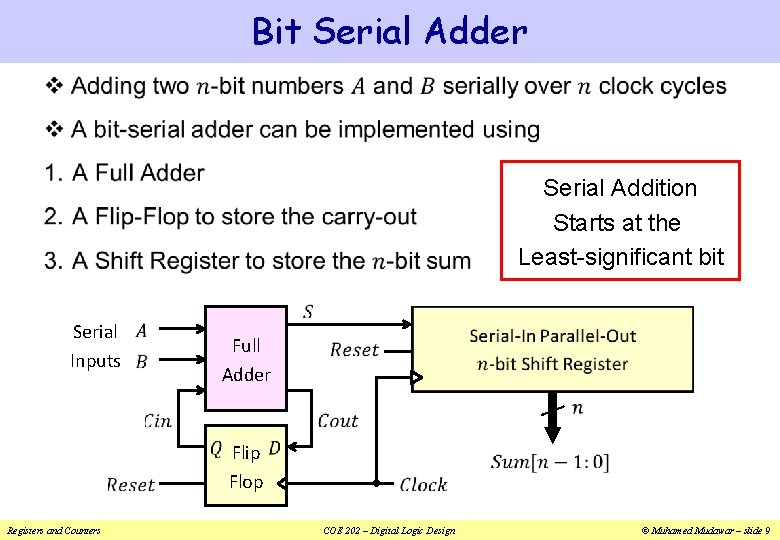

Bit Serial Adder v Serial Addition Starts at the Least-significant bit Serial Inputs Full Adder Flip Flop Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 9

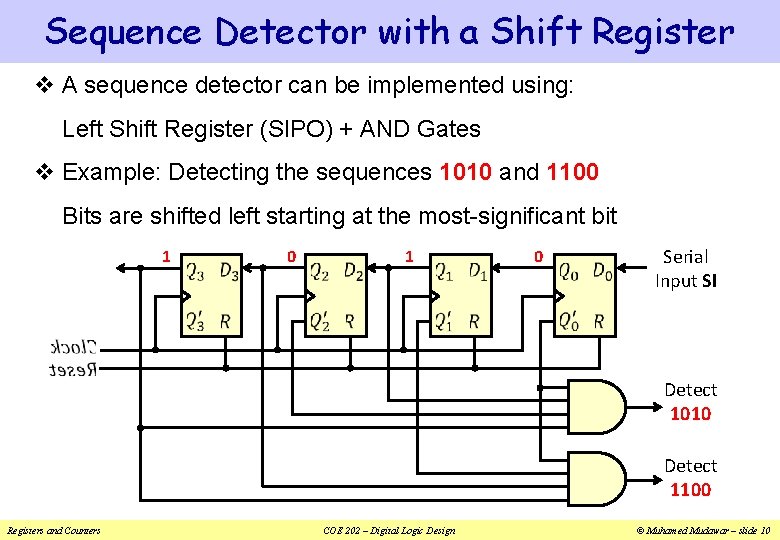

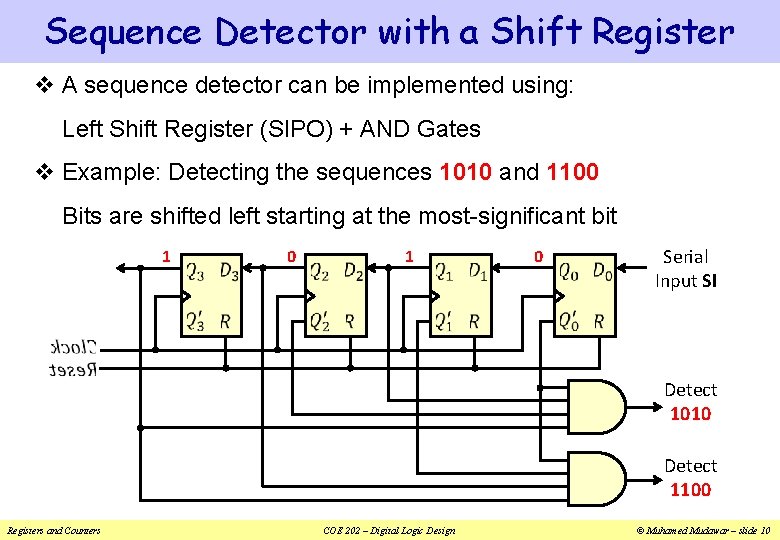

Sequence Detector with a Shift Register v A sequence detector can be implemented using: Left Shift Register (SIPO) + AND Gates v Example: Detecting the sequences 1010 and 1100 Bits are shifted left starting at the most-significant bit 1 0 Serial Input SI Detect 1010 Detect 1100 Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 10

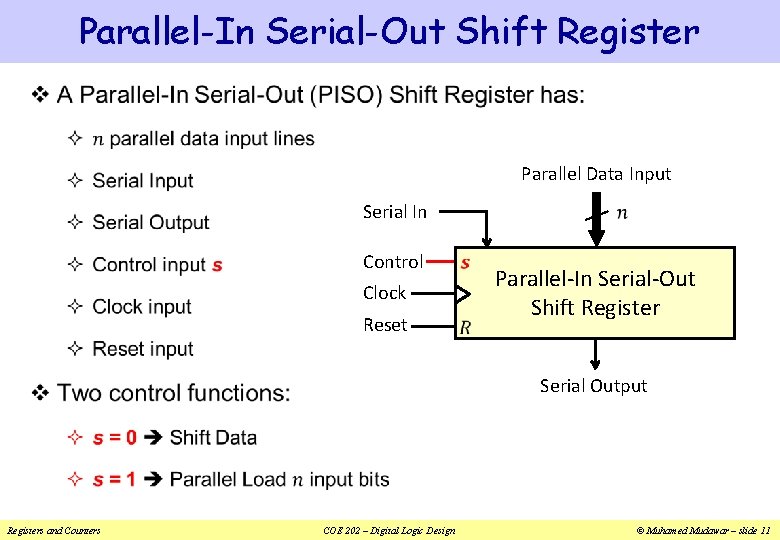

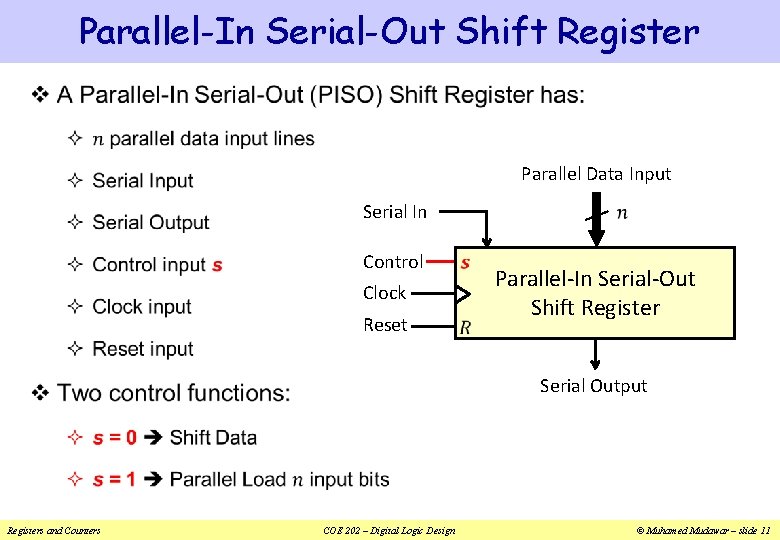

Parallel-In Serial-Out Shift Register v Parallel Data Input Serial In Control Clock Reset Parallel-In Serial-Out Shift Register Serial Output Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 11

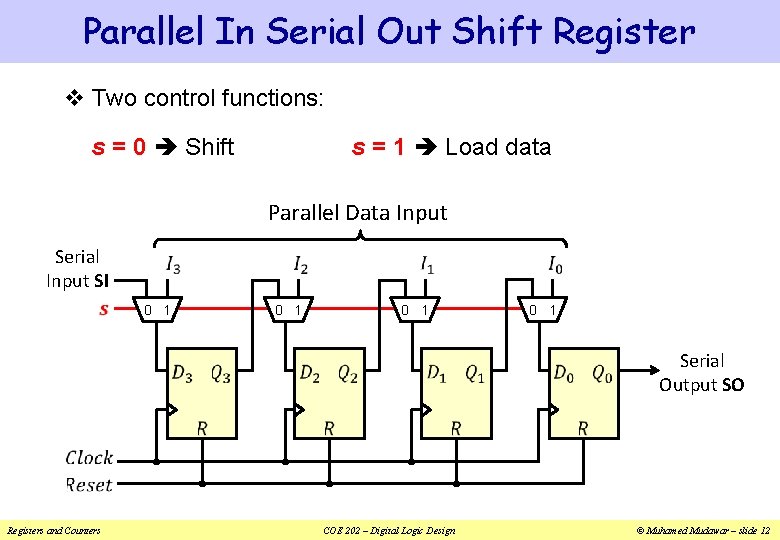

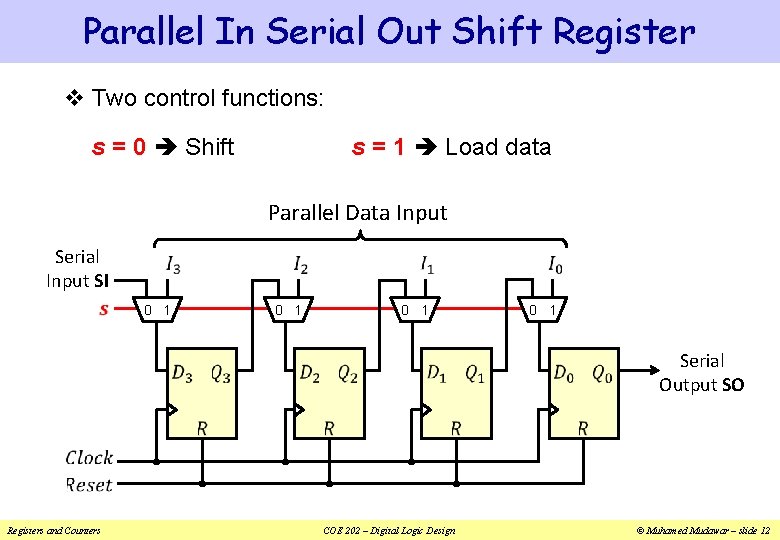

Parallel In Serial Out Shift Register v Two control functions: s = 0 Shift s = 1 Load data Parallel Data Input Serial Input SI 0 1 0 1 Serial Output SO Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 12

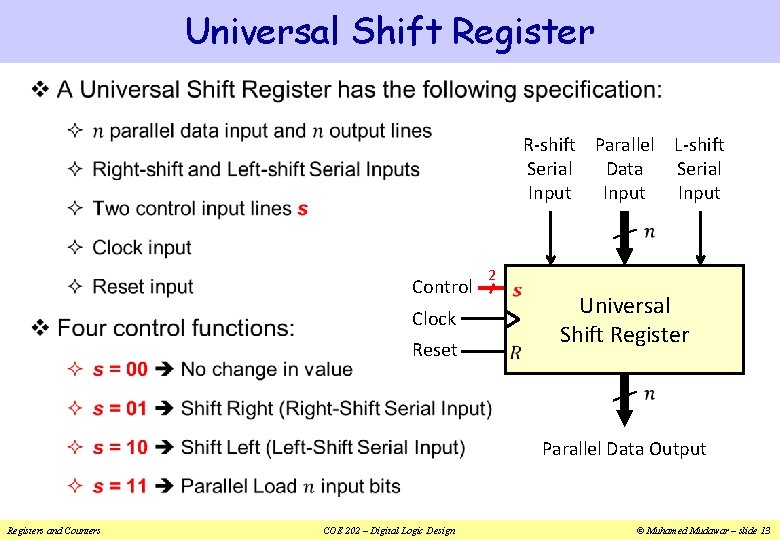

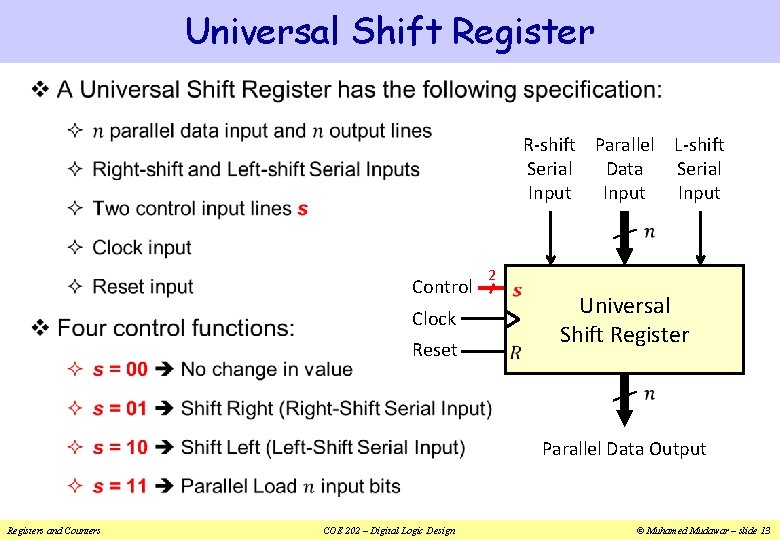

Universal Shift Register v R-shift Parallel L-shift Serial Data Serial Input Control Clock Reset 2 Universal Shift Register Parallel Data Output Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 13

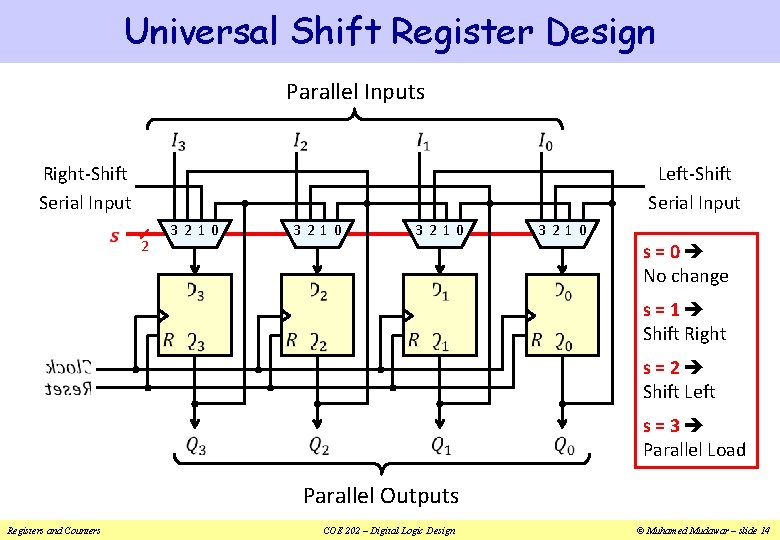

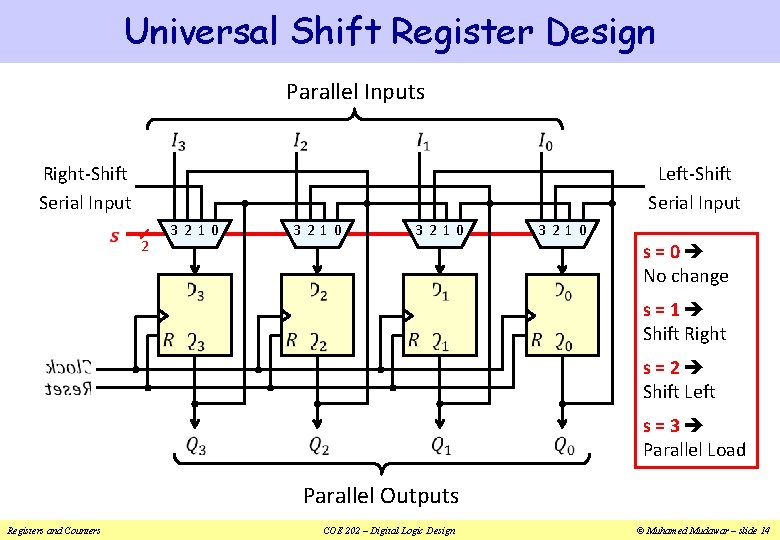

Universal Shift Register Design Parallel Inputs Right-Shift Serial Input Left-Shift Serial Input 2 3210 s=0 No change s=1 Shift Right s=2 Shift Left s=3 Parallel Load Parallel Outputs Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 14

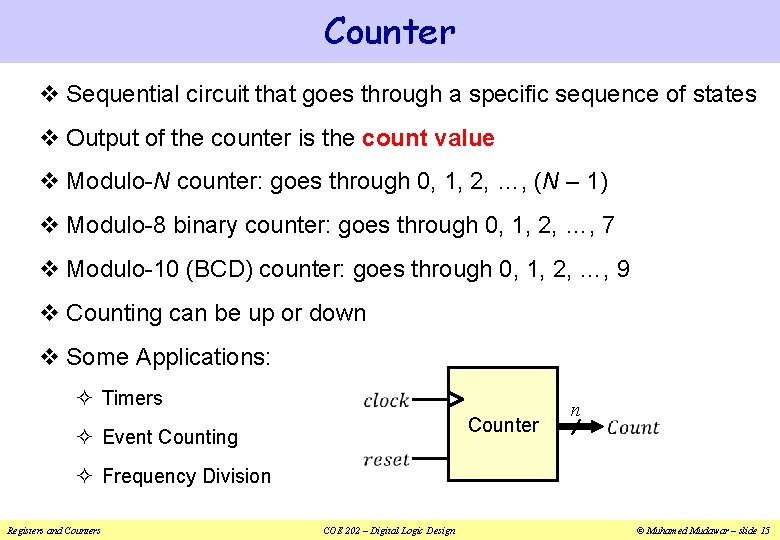

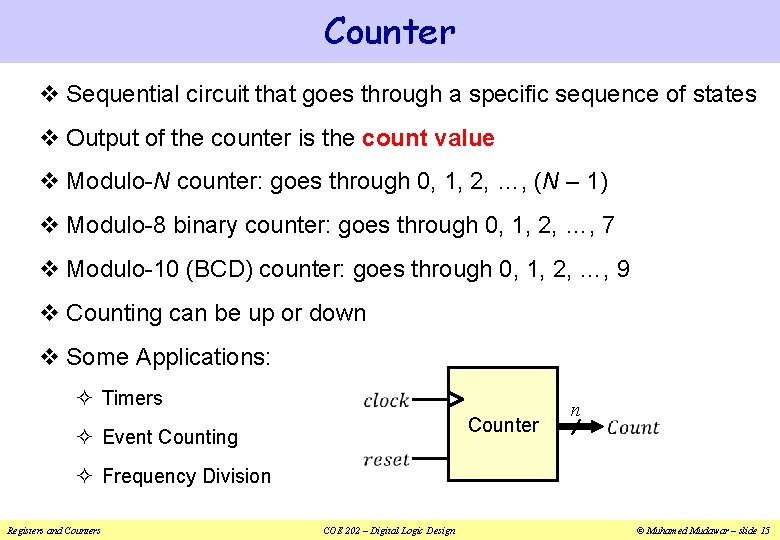

Counter v Sequential circuit that goes through a specific sequence of states v Output of the counter is the count value v Modulo-N counter: goes through 0, 1, 2, …, (N – 1) v Modulo-8 binary counter: goes through 0, 1, 2, …, 7 v Modulo-10 (BCD) counter: goes through 0, 1, 2, …, 9 v Counting can be up or down v Some Applications: ² Timers Counter ² Event Counting n ² Frequency Division Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 15

Implementing Counters Two Basic Approaches: 1. Ripple Counters ² The system clock is connected to the clock input of the first flip-flop (LSB) ² Each flip-flop output connects to the clock input of the next flip-flop ² Advantage: simple circuit and low power consumption ² Disadvantage: The counter is not truly synchronous ² No common clock to all flip-flops ² Ripple propagation delay as the clock signal propagates to the MSB 2. Synchronous Counters ² The system clock is connected to the clock input of ALL flip-flops ² Combinational logic is used to implement the desired state sequence Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 16

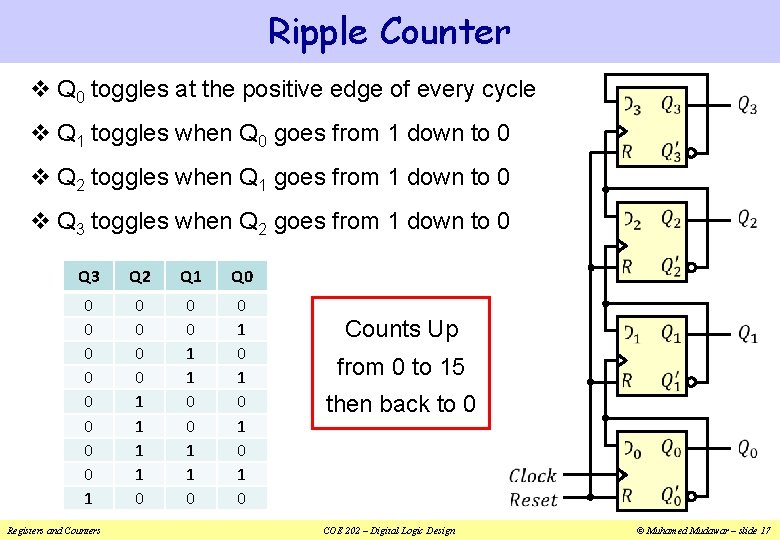

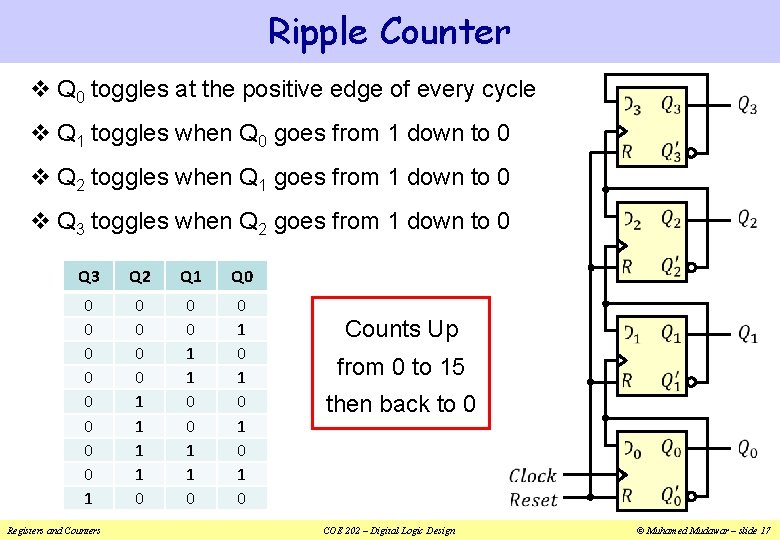

Ripple Counter v Q 0 toggles at the positive edge of every cycle v Q 1 toggles when Q 0 goes from 1 down to 0 v Q 2 toggles when Q 1 goes from 1 down to 0 v Q 3 toggles when Q 2 goes from 1 down to 0 Q 3 Q 2 Q 1 Q 0 0 0 0 0 1 1 0 0 0 1 1 0 0 1 0 1 0 Registers and Counters Counts Up from 0 to 15 then back to 0 COE 202 – Digital Logic Design © Muhamed Mudawar – slide 17

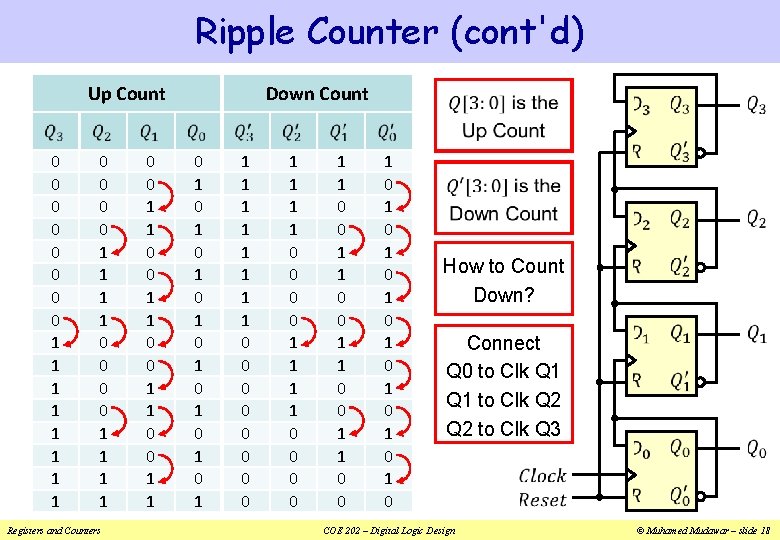

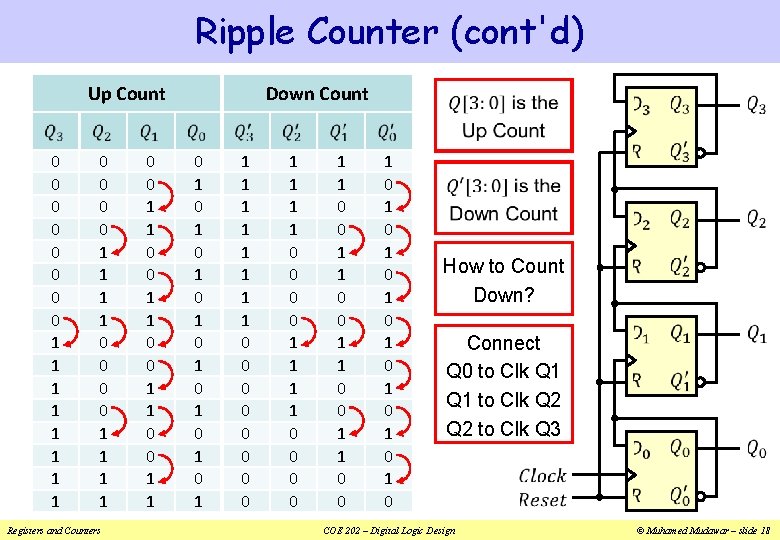

Ripple Counter (cont'd) Up Count 0 0 0 0 1 1 1 1 Registers and Counters 0 0 1 1 Down Count 0 1 0 1 1 1 1 1 0 0 0 0 1 1 0 0 1 0 1 0 How to Count Down? Connect Q 0 to Clk Q 1 to Clk Q 2 to Clk Q 3 COE 202 – Digital Logic Design © Muhamed Mudawar – slide 18

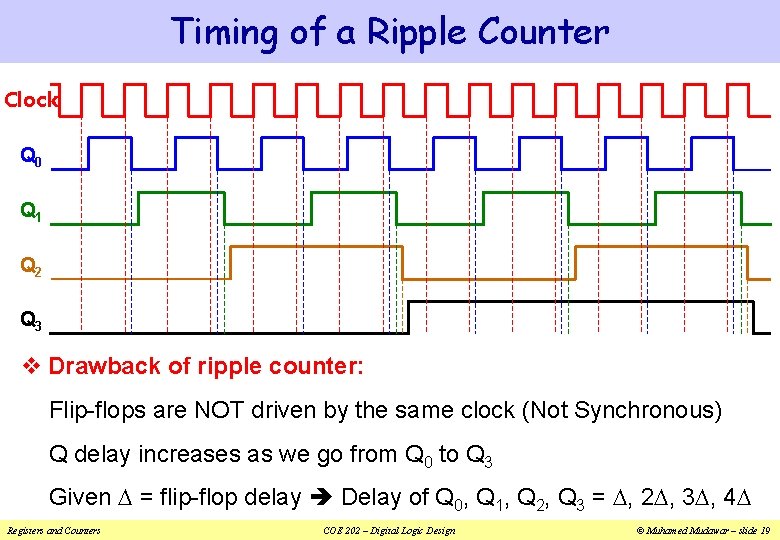

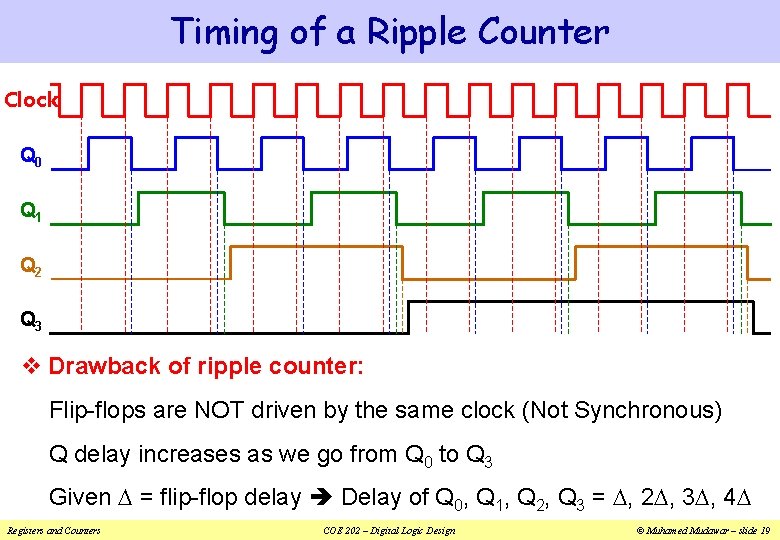

Timing of a Ripple Counter Clock Q 0 Q 1 Q 2 Q 3 v Drawback of ripple counter: Flip-flops are NOT driven by the same clock (Not Synchronous) Q delay increases as we go from Q 0 to Q 3 Given = flip-flop delay Delay of Q 0, Q 1, Q 2, Q 3 = , 2 , 3 , 4 Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 19

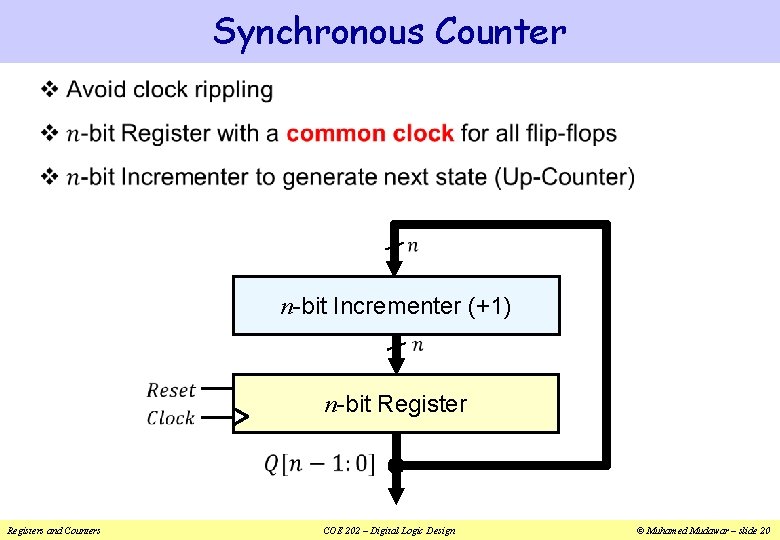

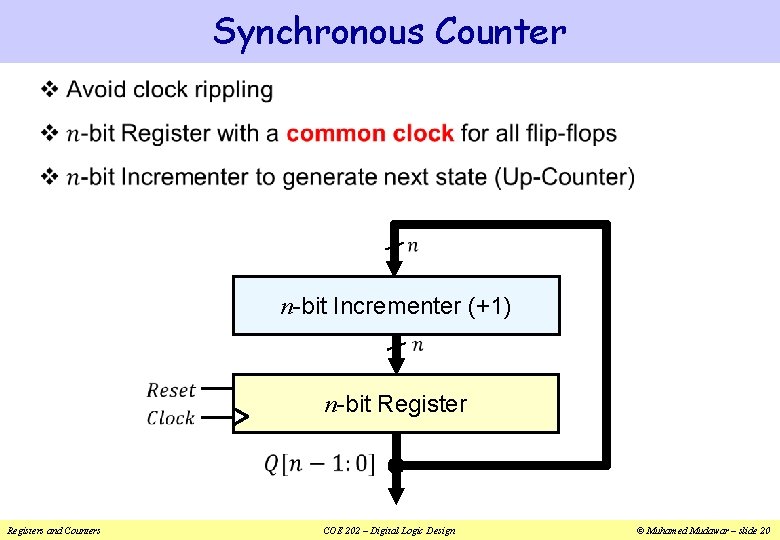

Synchronous Counter v n-bit Incrementer (+1) n-bit Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 20

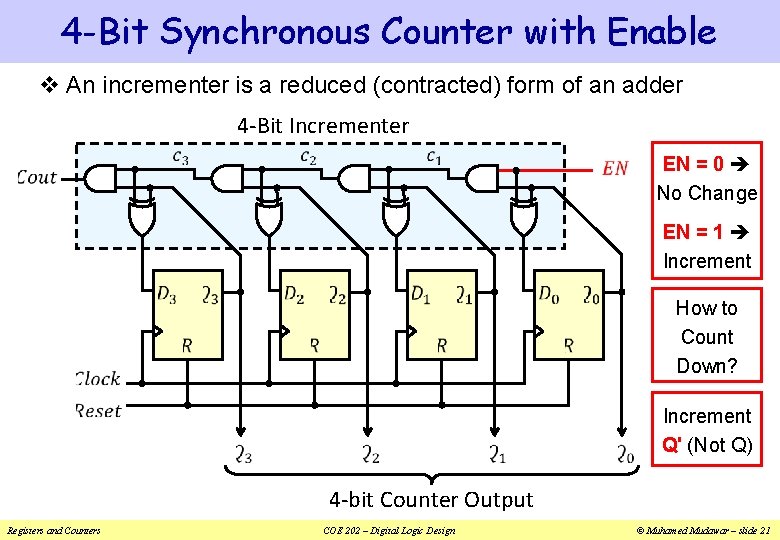

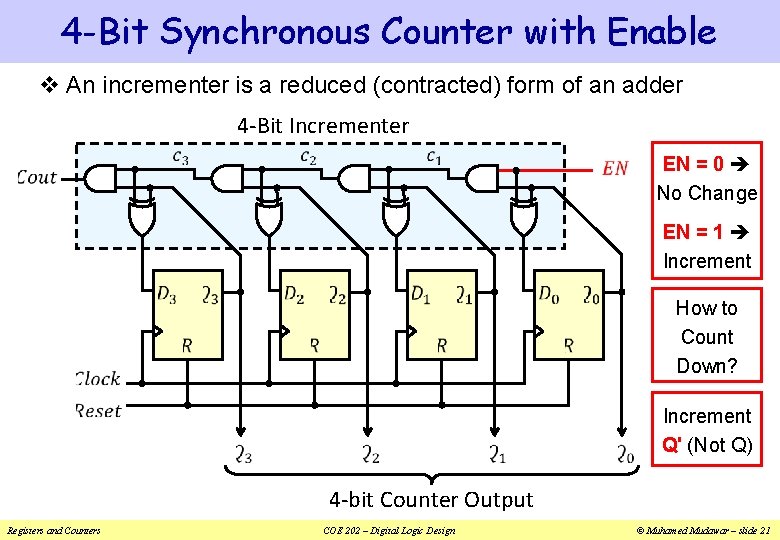

4 -Bit Synchronous Counter with Enable v An incrementer is a reduced (contracted) form of an adder 4 -Bit Incrementer EN = 0 No Change EN = 1 Increment How to Count Down? Increment Q' (Not Q) 4 -bit Counter Output Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 21

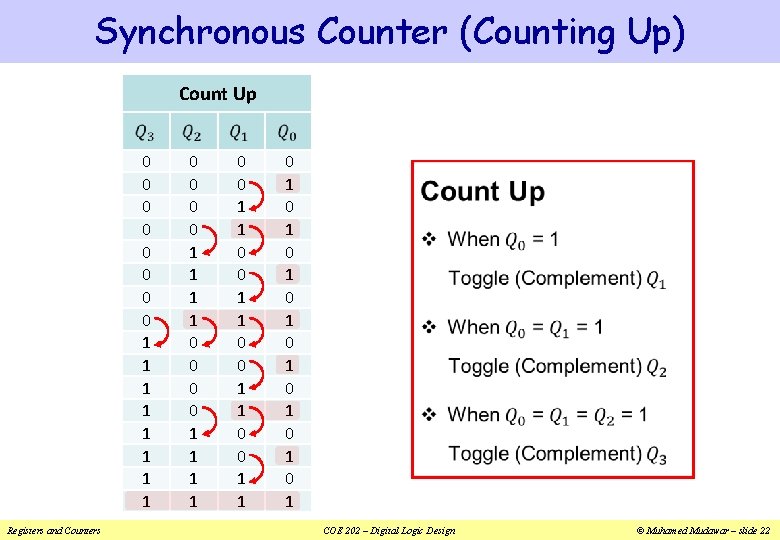

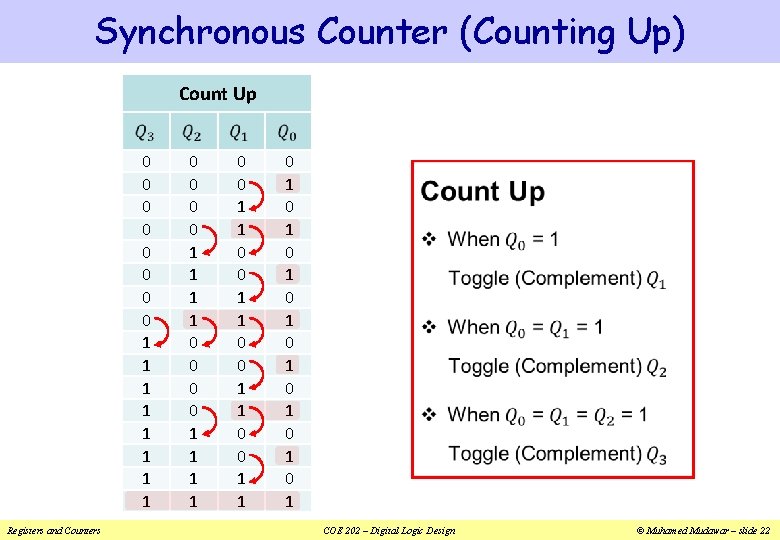

Synchronous Counter (Counting Up) Count Up 0 0 0 0 1 1 1 1 Registers and Counters 0 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 v COE 202 – Digital Logic Design © Muhamed Mudawar – slide 22

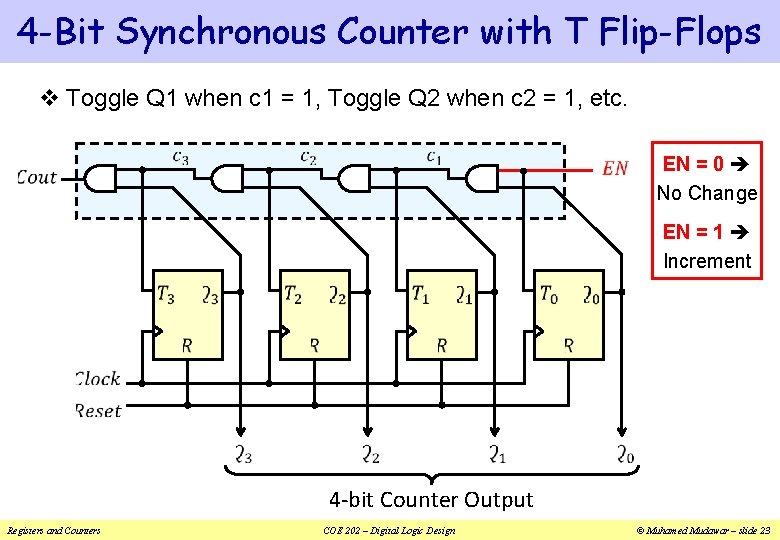

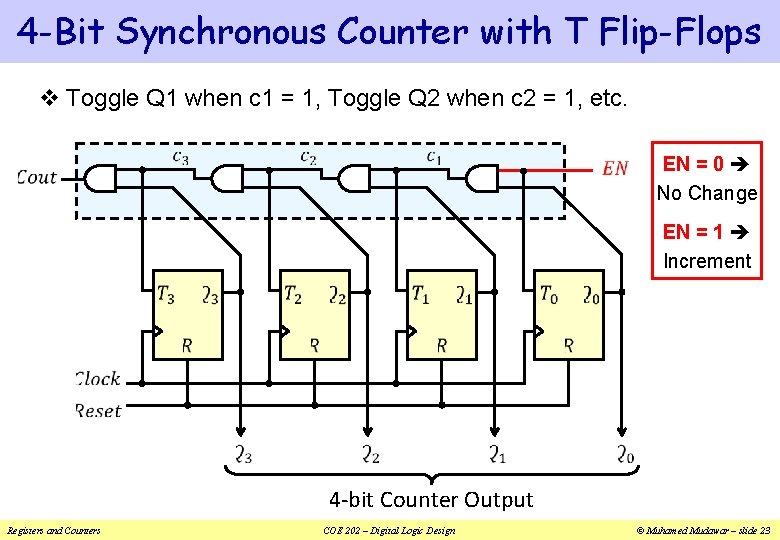

4 -Bit Synchronous Counter with T Flip-Flops v Toggle Q 1 when c 1 = 1, Toggle Q 2 when c 2 = 1, etc. EN = 0 No Change EN = 1 Increment 4 -bit Counter Output Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 23

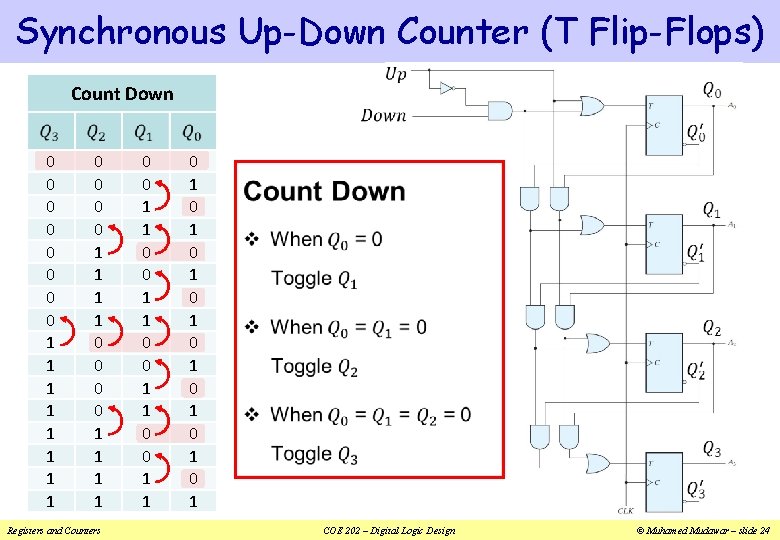

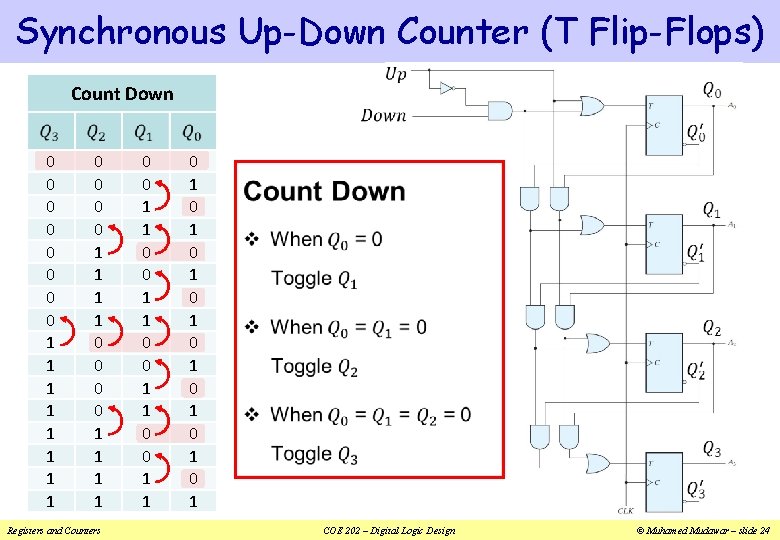

Synchronous Up-Down Counter (T Flip-Flops) Count Down 0 0 0 0 1 1 1 1 Registers and Counters 0 0 1 1 0 1 0 1 v COE 202 – Digital Logic Design © Muhamed Mudawar – slide 24

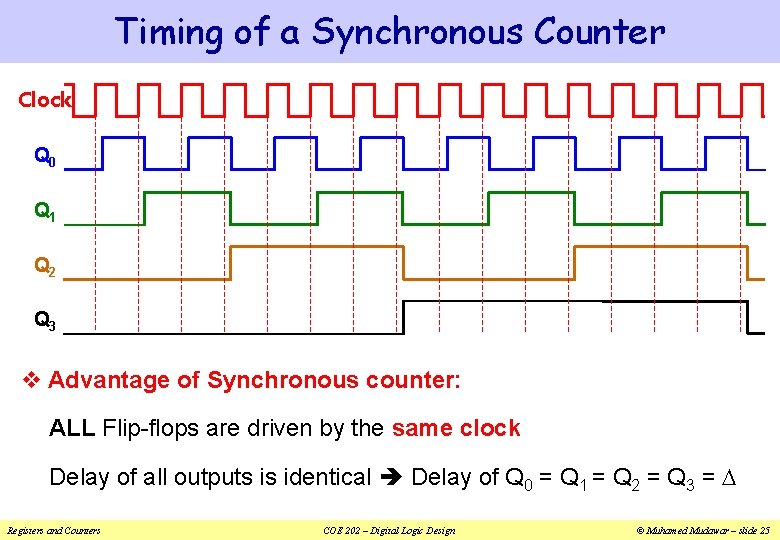

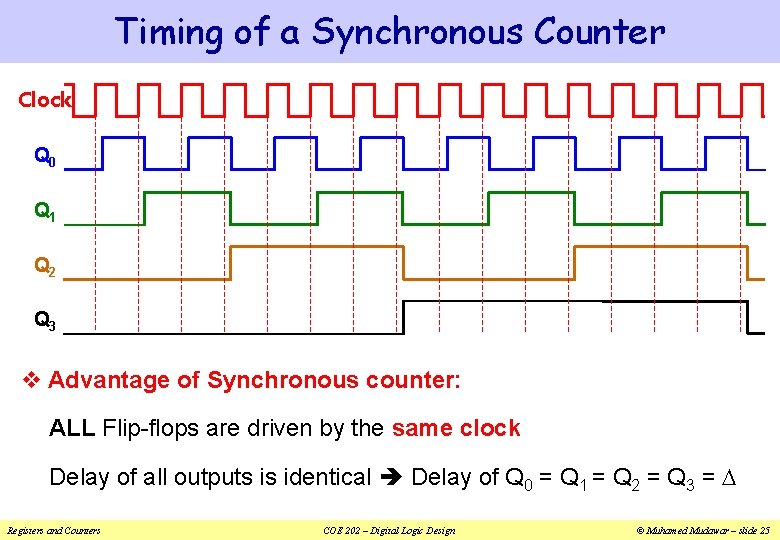

Timing of a Synchronous Counter Clock Q 0 Q 1 Q 2 Q 3 v Advantage of Synchronous counter: ALL Flip-flops are driven by the same clock Delay of all outputs is identical Delay of Q 0 = Q 1 = Q 2 = Q 3 = Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 25

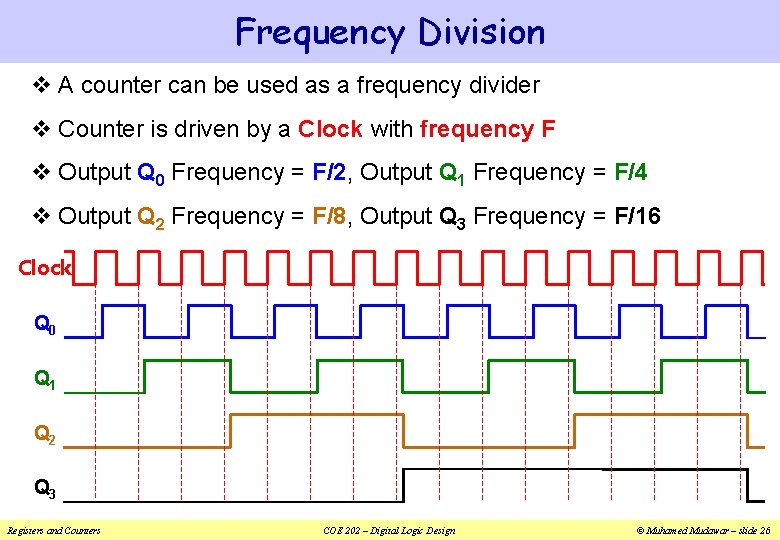

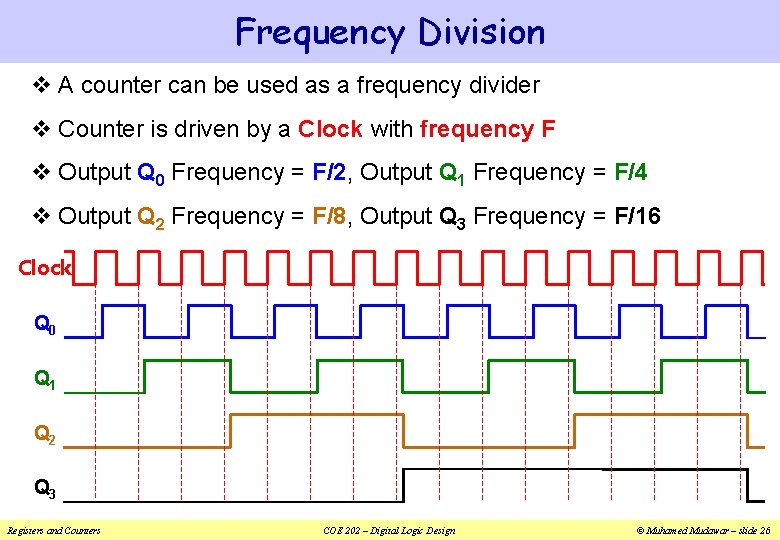

Frequency Division v A counter can be used as a frequency divider v Counter is driven by a Clock with frequency F v Output Q 0 Frequency = F/2, Output Q 1 Frequency = F/4 v Output Q 2 Frequency = F/8, Output Q 3 Frequency = F/16 Clock Q 0 Q 1 Q 2 Q 3 Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 26

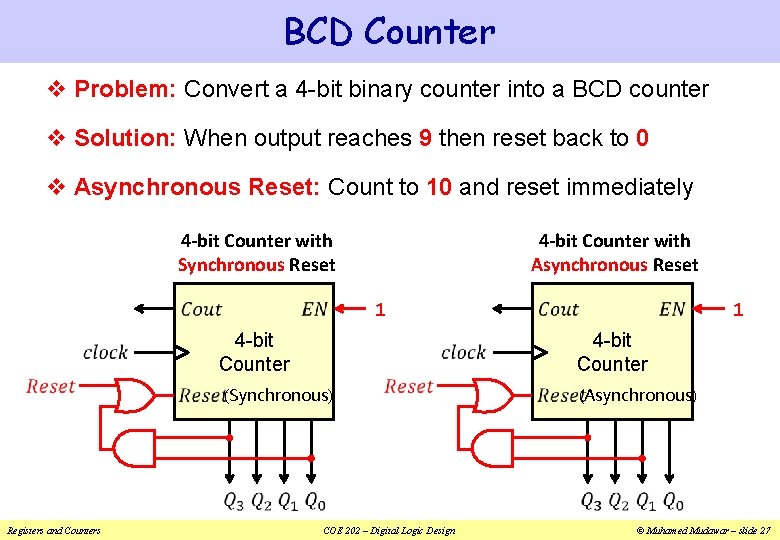

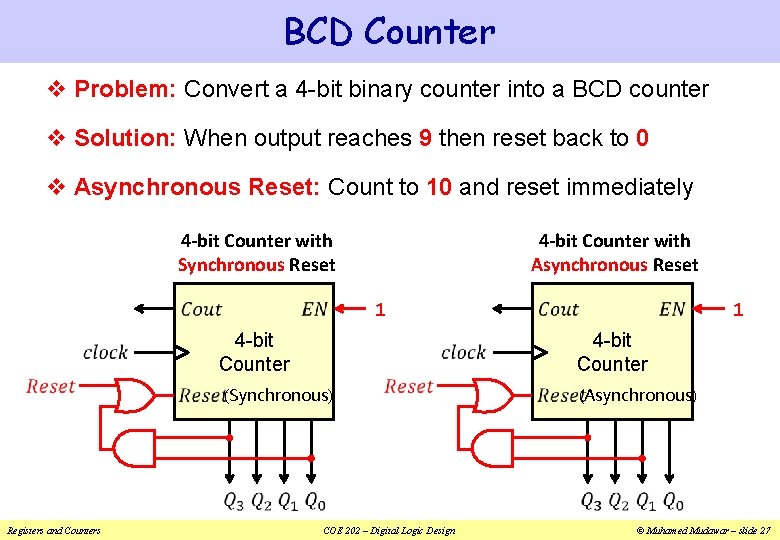

BCD Counter v Problem: Convert a 4 -bit binary counter into a BCD counter v Solution: When output reaches 9 then reset back to 0 v Asynchronous Reset: Count to 10 and reset immediately 4 -bit Counter with Synchronous Reset 4 -bit Counter with Asynchronous Reset 1 4 -bit Counter (Synchronous) Registers and Counters 1 COE 202 – Digital Logic Design (Asynchronous) © Muhamed Mudawar – slide 27

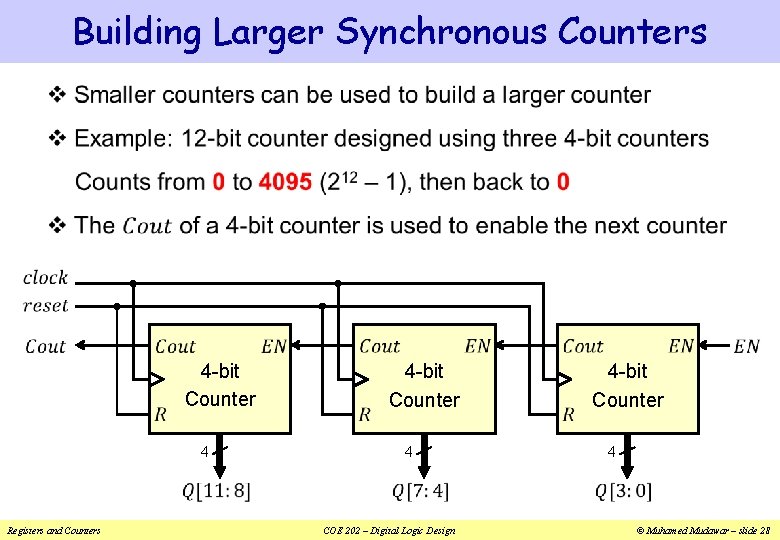

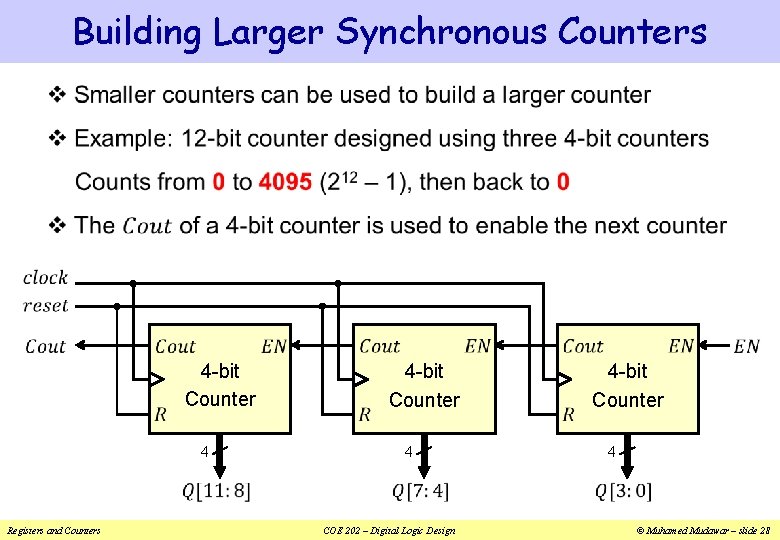

Building Larger Synchronous Counters v 4 -bit Counter 4 Registers and Counters 4 -bit Counter 4 COE 202 – Digital Logic Design 4 -bit Counter 4 © Muhamed Mudawar – slide 28

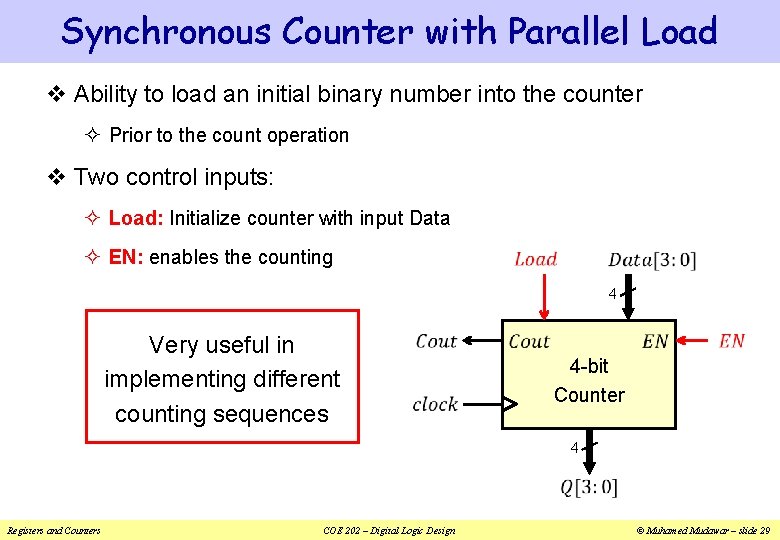

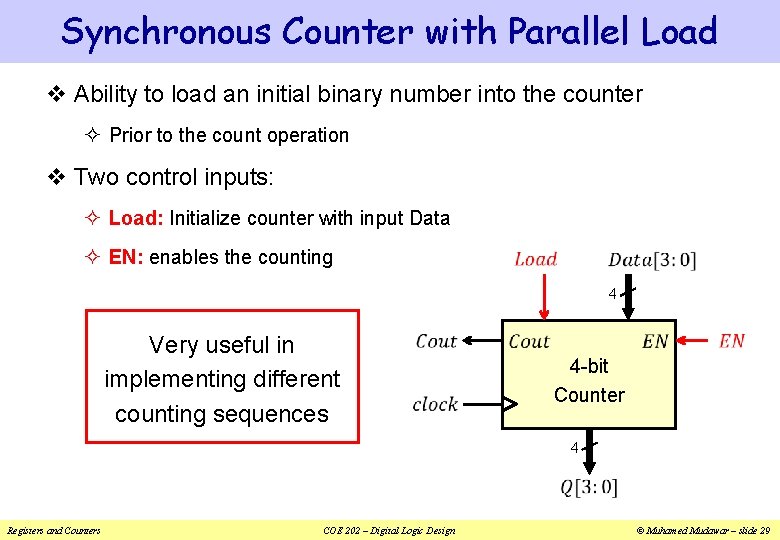

Synchronous Counter with Parallel Load v Ability to load an initial binary number into the counter ² Prior to the count operation v Two control inputs: ² Load: Initialize counter with input Data ² EN: enables the counting 4 Very useful in implementing different counting sequences 4 -bit Counter 4 Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 29

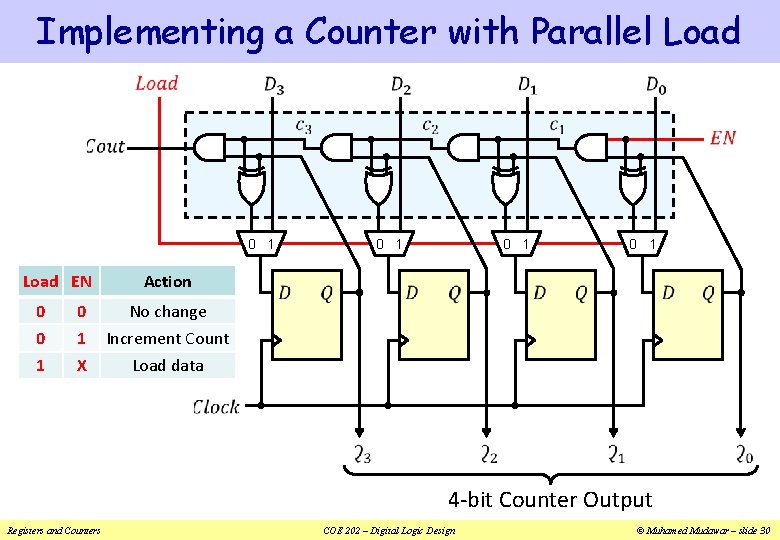

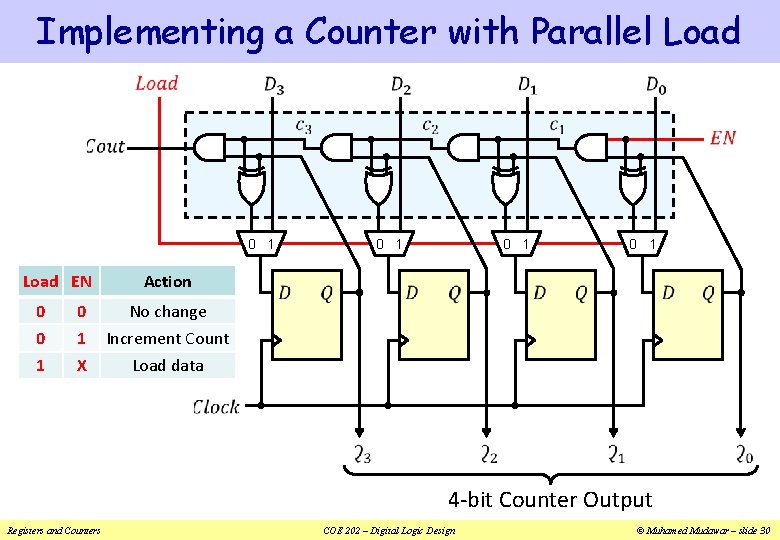

Implementing a Counter with Parallel Load 0 1 Load EN 0 1 0 1 Action 0 0 No change 0 1 Increment Count 1 X Load data 4 -bit Counter Output Registers and Counters COE 202 – Digital Logic Design © Muhamed Mudawar – slide 30

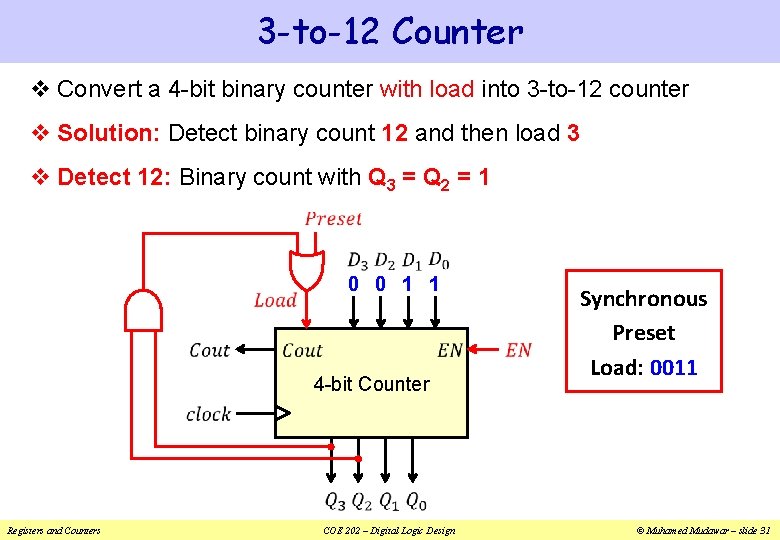

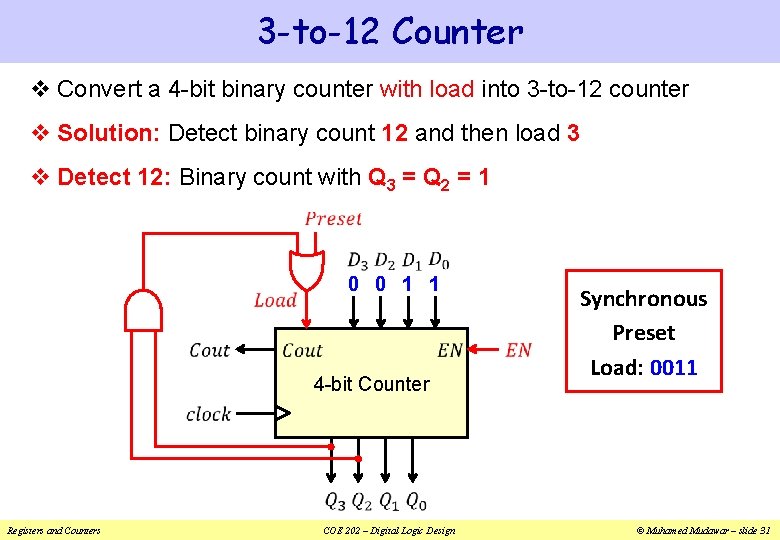

3 -to-12 Counter v Convert a 4 -bit binary counter with load into 3 -to-12 counter v Solution: Detect binary count 12 and then load 3 v Detect 12: Binary count with Q 3 = Q 2 = 1 0 0 1 1 4 -bit Counter Registers and Counters COE 202 – Digital Logic Design Synchronous Preset Load: 0011 © Muhamed Mudawar – slide 31

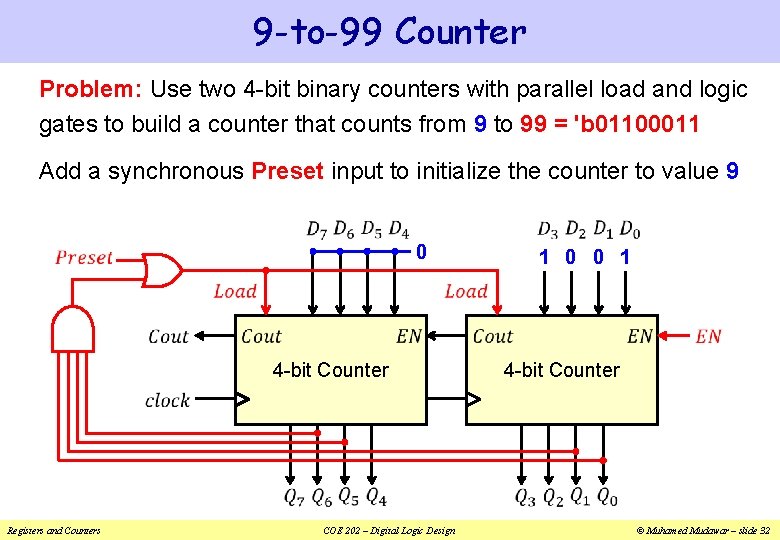

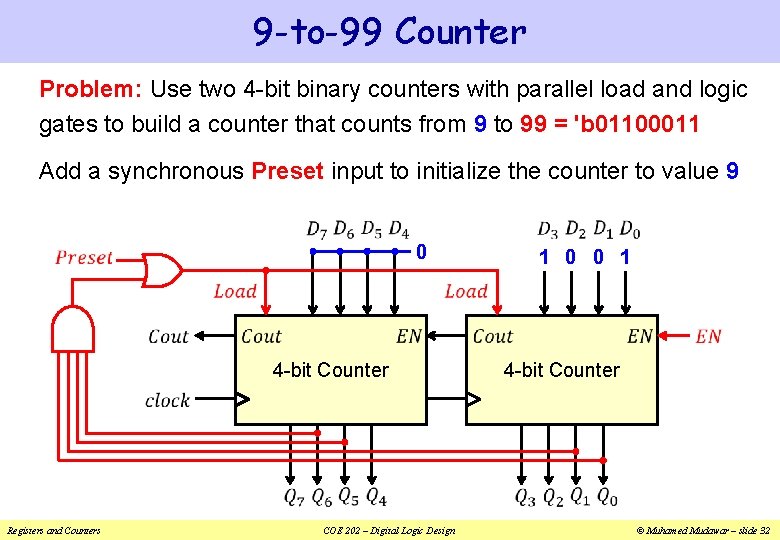

9 -to-99 Counter Problem: Use two 4 -bit binary counters with parallel load and logic gates to build a counter that counts from 9 to 99 = 'b 01100011 Add a synchronous Preset input to initialize the counter to value 9 0 4 -bit Counter Registers and Counters COE 202 – Digital Logic Design 1 0 0 1 4 -bit Counter © Muhamed Mudawar – slide 32