Registermemory 80386 ABC Registerregister load store 1980 Load

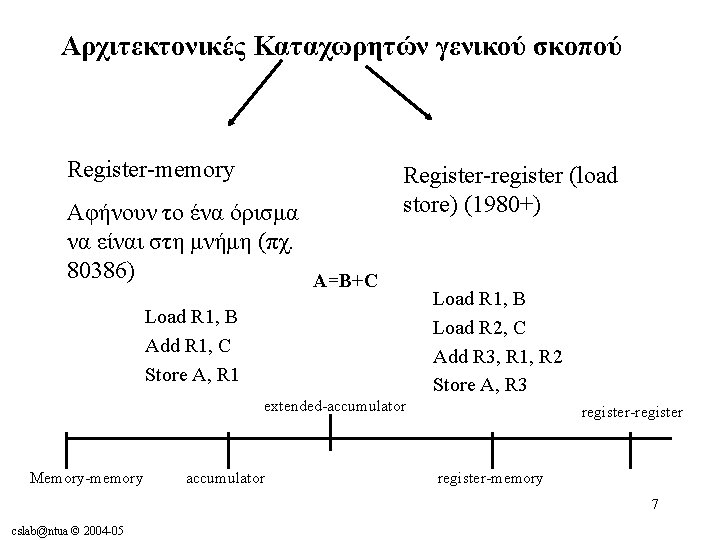

Αρχιτεκτονικές Καταχωρητών γενικού σκοπού Register-memory Αφήνουν το ένα όρισμα να είναι στη μνήμη (πχ. 80386) A=B+C Register-register (load store) (1980+) Load R 1, B Add R 1, C Store A, R 1 Load R 1, B Load R 2, C Add R 3, R 1, R 2 Store A, R 3 extended-accumulator Memory-memory accumulator register-register-memory 7 cslab@ntua © 2004 -05

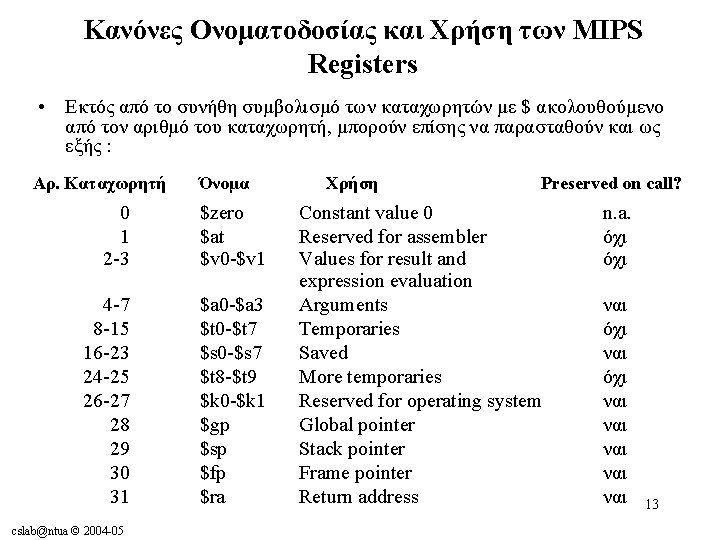

Κανόνες Ονοματοδοσίας και Χρήση των MIPS Registers • Εκτός από το συνήθη συμβολισμό των καταχωρητών με $ ακολουθούμενο από τον αριθμό του καταχωρητή, μπορούν επίσης να παρασταθούν και ως εξής : Αρ. Καταχωρητή Όνομα 0 1 2 -3 $zero $at $v 0 -$v 1 4 -7 8 -15 16 -23 24 -25 26 -27 28 29 30 31 $a 0 -$a 3 $t 0 -$t 7 $s 0 -$s 7 $t 8 -$t 9 $k 0 -$k 1 $gp $sp $fp $ra cslab@ntua © 2004 -05 Χρήση Preserved on call? Constant value 0 Reserved for assembler Values for result and expression evaluation Arguments Temporaries Saved More temporaries Reserved for operating system Global pointer Stack pointer Frame pointer Return address n. a. όχι ναι ναι ναι 13

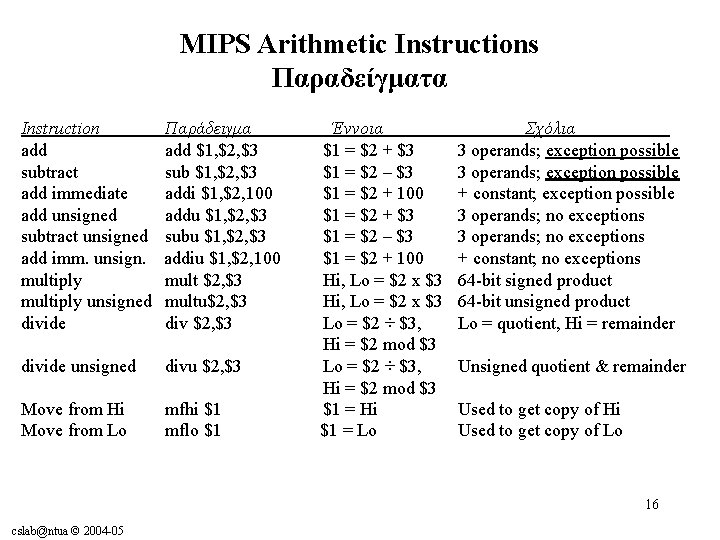

MIPS Arithmetic Instructions Παραδείγματα Instruction add subtract add immediate add unsigned subtract unsigned add imm. unsign. multiply unsigned divide Παράδειγμα add $1, $2, $3 sub $1, $2, $3 addi $1, $2, 100 addu $1, $2, $3 subu $1, $2, $3 addiu $1, $2, 100 mult $2, $3 multu$2, $3 divide unsigned divu $2, $3 Move from Hi Move from Lo mfhi $1 mflo $1 Έννοια $1 = $2 + $3 $1 = $2 – $3 $1 = $2 + 100 Hi, Lo = $2 x $3 Lo = $2 ÷ $3, Hi = $2 mod $3 $1 = Hi $1 = Lo Σχόλια 3 operands; exception possible + constant; exception possible 3 operands; no exceptions + constant; no exceptions 64 -bit signed product 64 -bit unsigned product Lo = quotient, Hi = remainder Unsigned quotient & remainder Used to get copy of Hi Used to get copy of Lo 16 cslab@ntua © 2004 -05

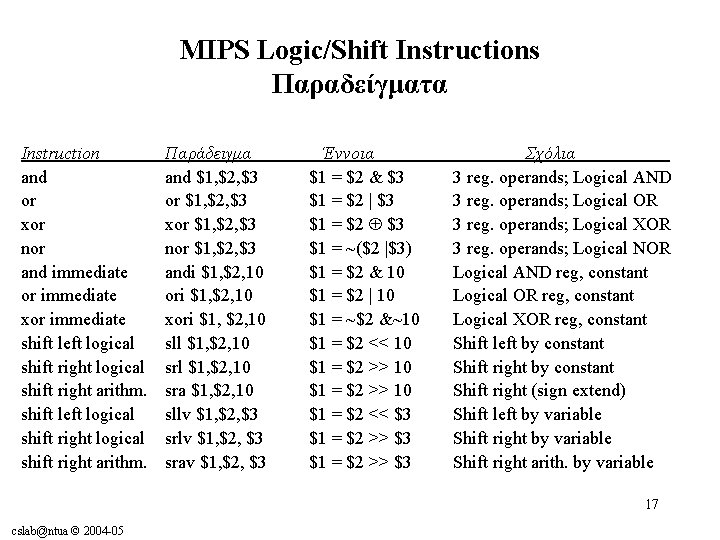

MIPS Logic/Shift Instructions Παραδείγματα Instruction and or xor nor and immediate or immediate xor immediate shift left logical shift right arithm. Παράδειγμα and $1, $2, $3 or $1, $2, $3 xor $1, $2, $3 nor $1, $2, $3 andi $1, $2, 10 ori $1, $2, 10 xori $1, $2, 10 sll $1, $2, 10 sra $1, $2, 10 sllv $1, $2, $3 srav $1, $2, $3 Έννοια $1 = $2 & $3 $1 = $2 | $3 $1 = $2 $3 $1 = ~($2 |$3) $1 = $2 & 10 $1 = $2 | 10 $1 = ~$2 &~10 $1 = $2 << 10 $1 = $2 >> 10 $1 = $2 << $3 $1 = $2 >> $3 Σχόλια 3 reg. operands; Logical AND 3 reg. operands; Logical OR 3 reg. operands; Logical XOR 3 reg. operands; Logical NOR Logical AND reg, constant Logical OR reg, constant Logical XOR reg, constant Shift left by constant Shift right (sign extend) Shift left by variable Shift right arith. by variable 17 cslab@ntua © 2004 -05

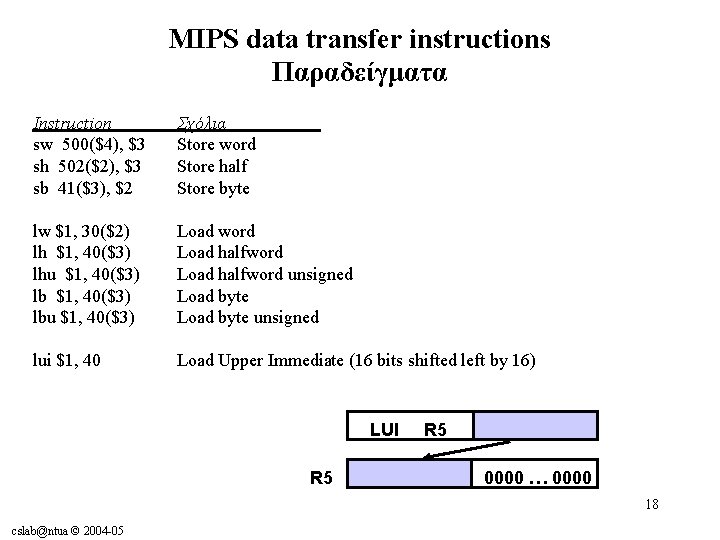

MIPS data transfer instructions Παραδείγματα Instruction sw 500($4), $3 sh 502($2), $3 sb 41($3), $2 Σχόλια Store word Store half Store byte lw $1, 30($2) lh $1, 40($3) lhu $1, 40($3) lbu $1, 40($3) Load word Load halfword unsigned Load byte unsigned lui $1, 40 Load Upper Immediate (16 bits shifted left by 16) LUI R 5 0000 … 0000 18 cslab@ntua © 2004 -05

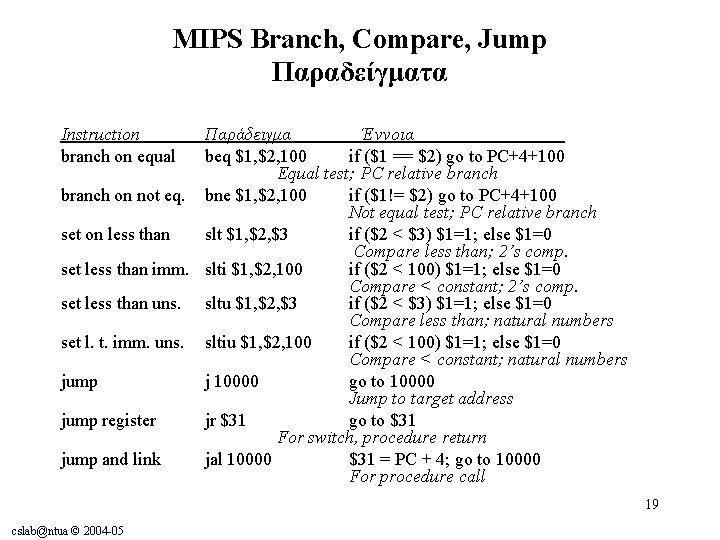

MIPS Branch, Compare, Jump Παραδείγματα Instruction branch on equal Παράδειγμα Έννοια beq $1, $2, 100 if ($1 == $2) go to PC+4+100 Equal test; PC relative branch on not eq. bne $1, $2, 100 if ($1!= $2) go to PC+4+100 Not equal test; PC relative branch set on less than slt $1, $2, $3 if ($2 < $3) $1=1; else $1=0 Compare less than; 2’s comp. set less than imm. slti $1, $2, 100 if ($2 < 100) $1=1; else $1=0 Compare < constant; 2’s comp. set less than uns. sltu $1, $2, $3 if ($2 < $3) $1=1; else $1=0 Compare less than; natural numbers set l. t. imm. uns. sltiu $1, $2, 100 if ($2 < 100) $1=1; else $1=0 Compare < constant; natural numbers jump j 10000 go to 10000 Jump to target address jump register jr $31 go to $31 For switch, procedure return jump and link jal 10000 $31 = PC + 4; go to 10000 For procedure call 19 cslab@ntua © 2004 -05

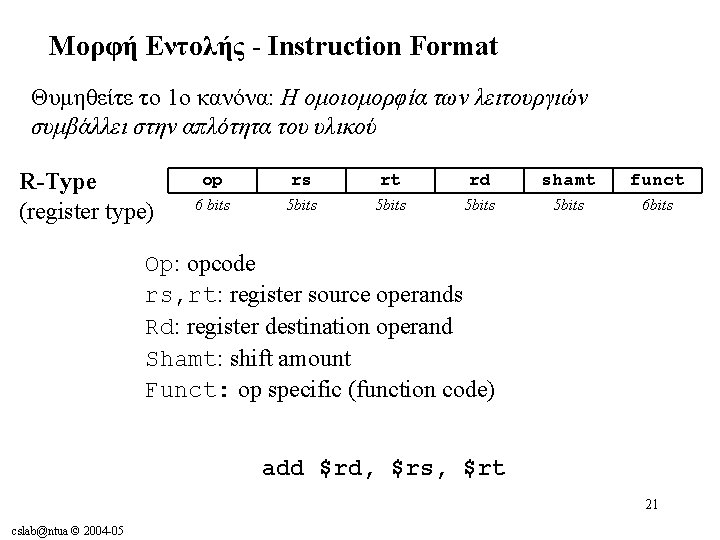

Μορφή Εντολής - Instruction Format Θυμηθείτε το 1ο κανόνα: Η ομοιομορφία των λειτουργιών συμβάλλει στην απλότητα του υλικού R-Type (register type) op rs rt rd shamt funct 6 bits 5 bits 6 bits Op: opcode rs, rt: register source operands Rd: register destination operand Shamt: shift amount Funct: op specific (function code) add $rd, $rs, $rt 21 cslab@ntua © 2004 -05

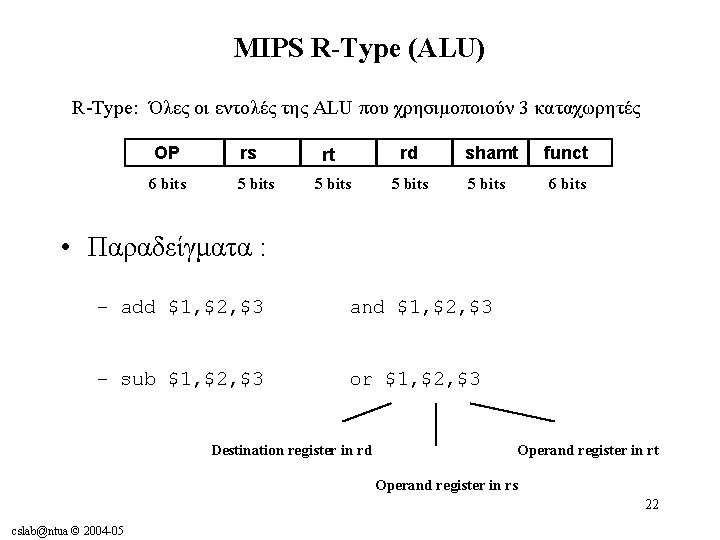

MIPS R-Type (ALU) R-Type: Όλες οι εντολές της ALU που χρησιμοποιούν 3 καταχωρητές OP 6 bits rs 5 bits rt rd shamt funct 5 bits 6 bits • Παραδείγματα : – add $1, $2, $3 and $1, $2, $3 – sub $1, $2, $3 or $1, $2, $3 Destination register in rd Operand register in rt Operand register in rs 22 cslab@ntua © 2004 -05

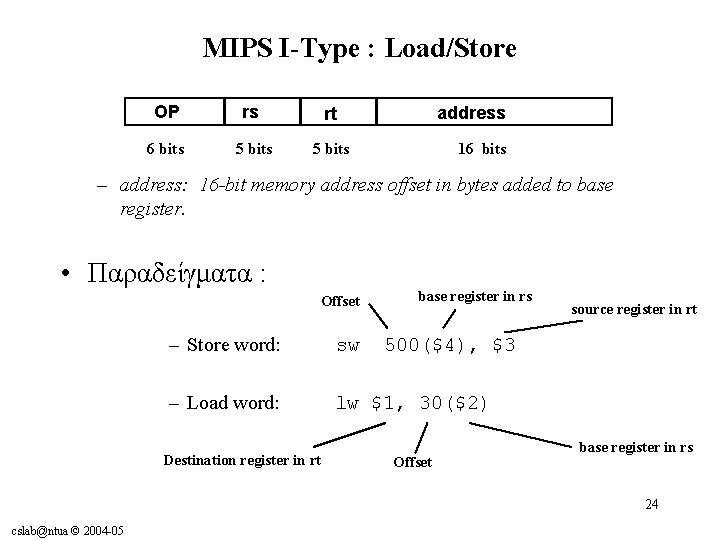

MIPS I-Type : Load/Store OP rs rt 6 bits 5 bits address 16 bits – address: 16 -bit memory address offset in bytes added to base register. • Παραδείγματα : Offset base register in rs – Store word: sw – Load word: lw $1, 30($2) Destination register in rt source register in rt 500($4), $3 Offset base register in rs 24 cslab@ntua © 2004 -05

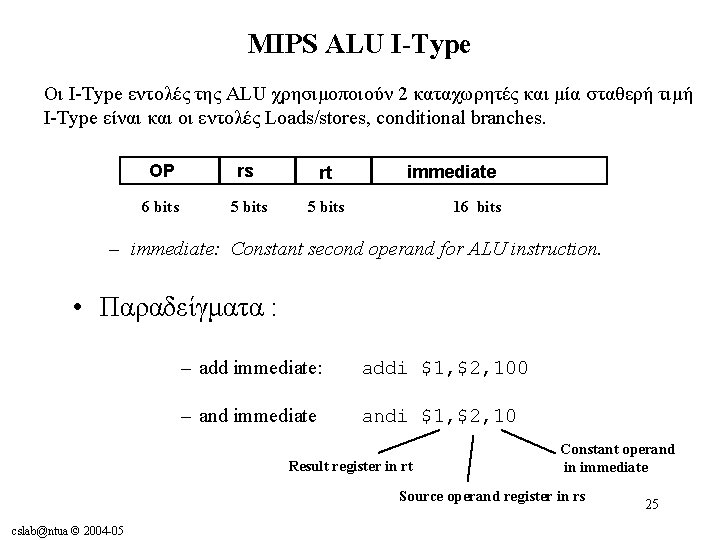

MIPS ALU I-Type Οι I-Type εντολές της ALU χρησιμοποιούν 2 καταχωρητές και μία σταθερή τιμή I-Type είναι και οι εντολές Loads/stores, conditional branches. OP rs rt 6 bits 5 bits immediate 16 bits – immediate: Constant second operand for ALU instruction. • Παραδείγματα : – add immediate: addi $1, $2, 100 – and immediate andi $1, $2, 10 Result register in rt Constant operand in immediate Source operand register in rs cslab@ntua © 2004 -05 25

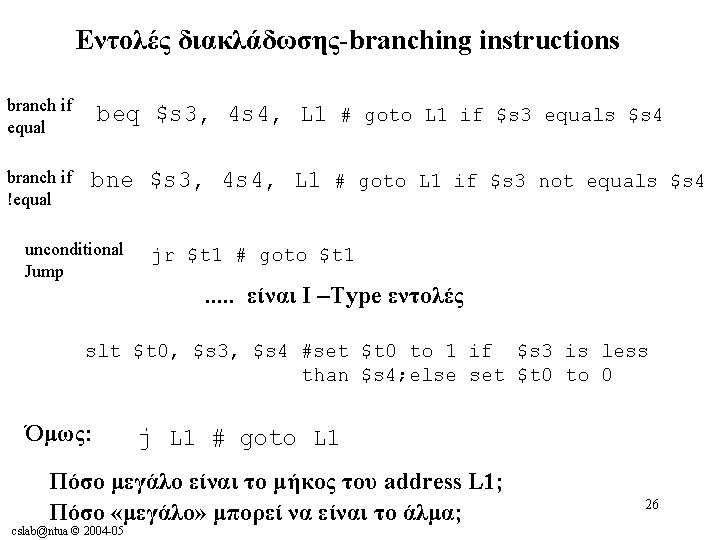

Εντολές διακλάδωσης-branching instructions branch if equal branch if !equal beq $s 3, 4 s 4, L 1 # goto L 1 if $s 3 equals $s 4 bne $s 3, 4 s 4, L 1 # goto L 1 if $s 3 not equals $s 4 unconditional Jump jr $t 1 # goto $t 1 . . . είναι I –Type εντολές slt $t 0, $s 3, $s 4 #set $t 0 to 1 if $s 3 is less than $s 4; else set $t 0 to 0 Όμως: j L 1 # goto L 1 Πόσο μεγάλο είναι το μήκος του address L 1; Πόσο «μεγάλο» μπορεί να είναι το άλμα; cslab@ntua © 2004 -05 26

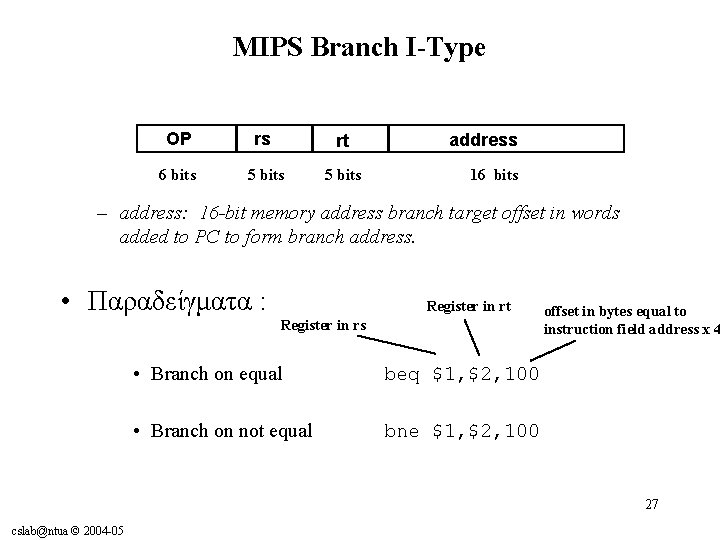

MIPS Branch I-Type OP rs rt 6 bits 5 bits address 16 bits – address: 16 -bit memory address branch target offset in words added to PC to form branch address. • Παραδείγματα : Register in rt Register in rs • Branch on equal beq $1, $2, 100 • Branch on not equal bne $1, $2, 100 offset in bytes equal to instruction field address x 4 27 cslab@ntua © 2004 -05

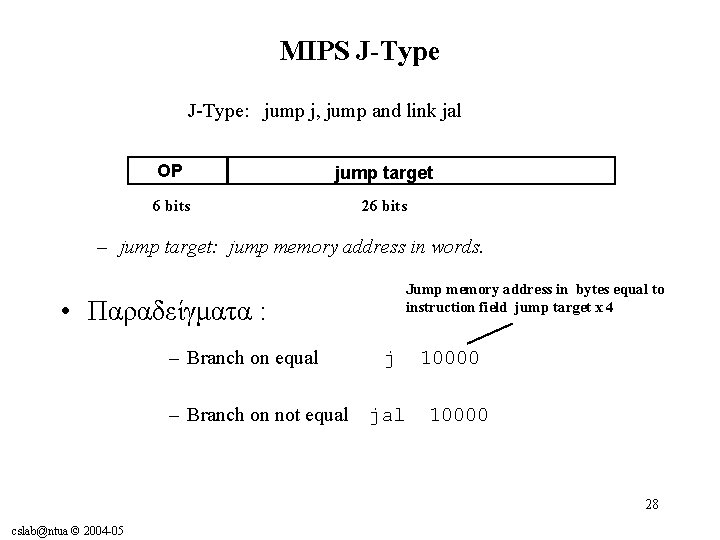

MIPS J-Type: jump j, jump and link jal OP jump target 6 bits 26 bits – jump target: jump memory address in words. Jump memory address in bytes equal to instruction field jump target x 4 • Παραδείγματα : – Branch on equal j – Branch on not equal jal 10000 28 cslab@ntua © 2004 -05

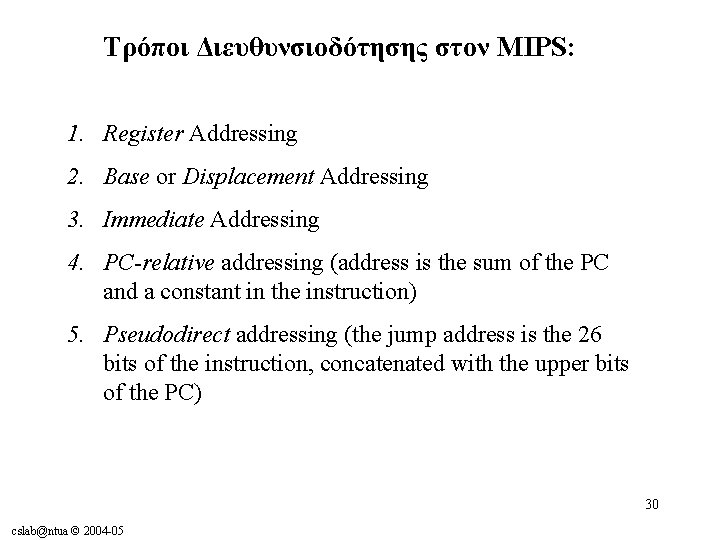

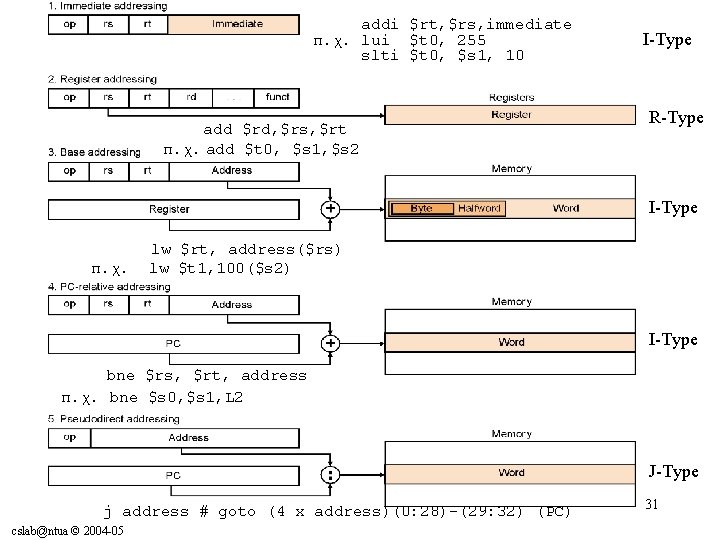

Τρόποι Διευθυνσιοδότησης στον MIPS: 1. Register Addressing 2. Base or Displacement Addressing 3. Immediate Addressing 4. PC-relative addressing (address is the sum of the PC and a constant in the instruction) 5. Pseudodirect addressing (the jump address is the 26 bits of the instruction, concatenated with the upper bits of the PC) 30 cslab@ntua © 2004 -05

addi $rt, $rs, immediate π. χ. lui $t 0, 255 slti $t 0, $s 1, 10 add $rd, $rs, $rt π. χ. add $t 0, $s 1, $s 2 I-Type R-Type I-Type π. χ. lw $rt, address($rs) lw $t 1, 100($s 2) I-Type bne $rs, $rt, address π. χ. bne $s 0, $s 1, L 2 J-Type j address # goto (4 x address)(0: 28)-(29: 32) (PC) cslab@ntua © 2004 -05 31

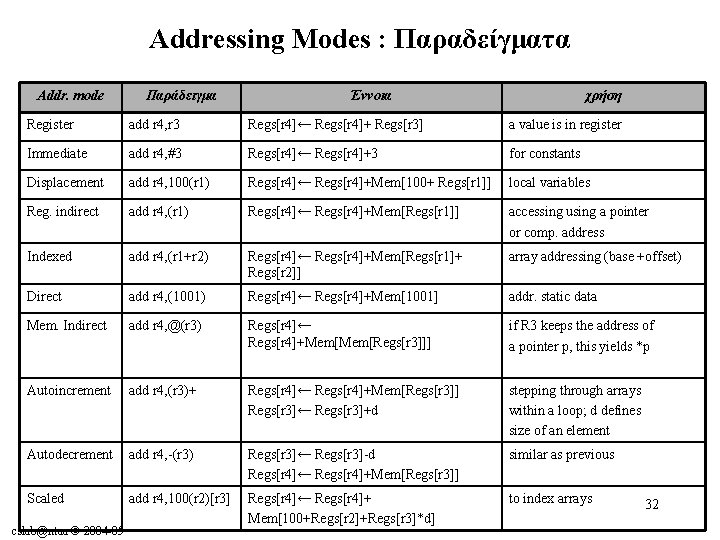

Addressing Modes : Παραδείγματα Addr. mode Παράδειγμα Έννοια χρήση Register add r 4, r 3 Regs[r 4]← Regs[r 4]+ Regs[r 3] a value is in register Immediate add r 4, #3 Regs[r 4]← Regs[r 4]+3 for constants Displacement add r 4, 100(r 1) Regs[r 4]← Regs[r 4]+Mem[100+ Regs[r 1]] local variables Reg. indirect add r 4, (r 1) Regs[r 4]← Regs[r 4]+Mem[Regs[r 1]] accessing using a pointer or comp. address Indexed add r 4, (r 1+r 2) Regs[r 4]← Regs[r 4]+Mem[Regs[r 1]+ Regs[r 2]] array addressing (base +offset) Direct add r 4, (1001) Regs[r 4]← Regs[r 4]+Mem[1001] addr. static data Mem. Indirect add r 4, @(r 3) Regs[r 4]← Regs[r 4]+Mem[Regs[r 3]]] if R 3 keeps the address of a pointer p, this yields *p Autoincrement add r 4, (r 3)+ Regs[r 4]← Regs[r 4]+Mem[Regs[r 3]] Regs[r 3]← Regs[r 3]+d stepping through arrays within a loop; d defines size of an element Autodecrement add r 4, -(r 3) Regs[r 3]← Regs[r 3]-d Regs[r 4]← Regs[r 4]+Mem[Regs[r 3]] similar as previous Scaled add r 4, 100(r 2)[r 3] Regs[r 4]← Regs[r 4]+ Mem[100+Regs[r 2]+Regs[r 3]*d] to index arrays cslab@ntua © 2004 -05 32

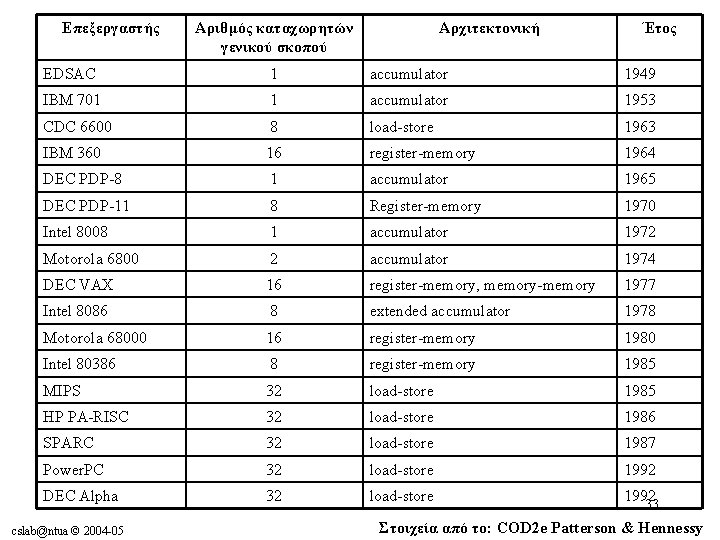

Επεξεργαστής Αριθμός καταχωρητών γενικού σκοπού Αρχιτεκτονική Έτος EDSAC 1 accumulator 1949 IBM 701 1 accumulator 1953 CDC 6600 8 load-store 1963 IBM 360 16 register-memory 1964 DEC PDP-8 1 accumulator 1965 DEC PDP-11 8 Register-memory 1970 Intel 8008 1 accumulator 1972 Motorola 6800 2 accumulator 1974 DEC VAX 16 register-memory, memory-memory 1977 Intel 8086 8 extended accumulator 1978 Motorola 68000 16 register-memory 1980 Intel 80386 8 register-memory 1985 MIPS 32 load-store 1985 HP PA-RISC 32 load-store 1986 SPARC 32 load-store 1987 Power. PC 32 load-store 1992 DEC Alpha 32 load-store 1992 33 cslab@ntua © 2004 -05 Στοιχεία από το: COD 2 e Patterson & Hennessy

- Slides: 33