Register transfer Notation Register transfer Notation l l

![• Contents of location is indicated by using square brackets [ ] • • Contents of location is indicated by using square brackets [ ] •](https://slidetodoc.com/presentation_image_h2/65b811562dc636e713c863e8c20f9fc3/image-8.jpg)

![Examples of RTN statements l R 2 [LOCN] l R 4 [R 3] +[R Examples of RTN statements l R 2 [LOCN] l R 4 [R 3] +[R](https://slidetodoc.com/presentation_image_h2/65b811562dc636e713c863e8c20f9fc3/image-9.jpg)

![Assembly Language Notation Structure C= A+B C [A]+[B] ADD A, B Operation Source , Assembly Language Notation Structure C= A+B C [A]+[B] ADD A, B Operation Source ,](https://slidetodoc.com/presentation_image_h2/65b811562dc636e713c863e8c20f9fc3/image-15.jpg)

![Examples MOV B, C C [B] Examples MOV B, C C [B]](https://slidetodoc.com/presentation_image_h2/65b811562dc636e713c863e8c20f9fc3/image-16.jpg)

- Slides: 28

Register transfer Notation

Register transfer Notation l l l Names for the address of memory location may be LOC, PLACE, A, VAR 2 Processor register may be R 0, R 5 I/O register names DATAIN, OUTSTATUS Example 1. R 1 [LOC] (Memory location LOC are trasnferred into processor register R 1. )

Register transfer Notation l Example 2 : RTN (Register Transfer Notation) R 3 [R 1]+ [R 2]

Interrupt An interrupt is a signal to the processor emitted by hardware or software indicating an event that needs immediate attention. An interrupt alerts the processor to a high-priority condition requiring the interruption of the current code the processor is executing. The processor responds by suspending its current activities, saving its state, and executing a function called an interrupt handler (or an interrupt service routine, ISR) to deal with the event. This interruption is temporary, and, after the interrupt handler finishes, the processor resumes normal activities. There are two types of interrupts: hardware interrupts and software interrupts.

Instruction and Instruction Sequencing

l 4 TYPES OF OPERATION: l Data transfer between memory and processor register l Arithmetic and logic operation l Program sequencing and control l I/O transfer

Transfer between processor registers & memory, between processor register & I/O devices Memory locations, registers and I/O register names are identified by a symbolic name in uppercase alphabets

![Contents of location is indicated by using square brackets • Contents of location is indicated by using square brackets [ ] •](https://slidetodoc.com/presentation_image_h2/65b811562dc636e713c863e8c20f9fc3/image-8.jpg)

• Contents of location is indicated by using square brackets [ ] • RHS of RTN always denotes a values, and is called Source • LHS of RTN always denotes a symbolic name where value is to be stored and is called destination • Source contents are not modified • Destination contents are overwritten

![Examples of RTN statements l R 2 LOCN l R 4 R 3 R Examples of RTN statements l R 2 [LOCN] l R 4 [R 3] +[R](https://slidetodoc.com/presentation_image_h2/65b811562dc636e713c863e8c20f9fc3/image-9.jpg)

Examples of RTN statements l R 2 [LOCN] l R 4 [R 3] +[R 2]

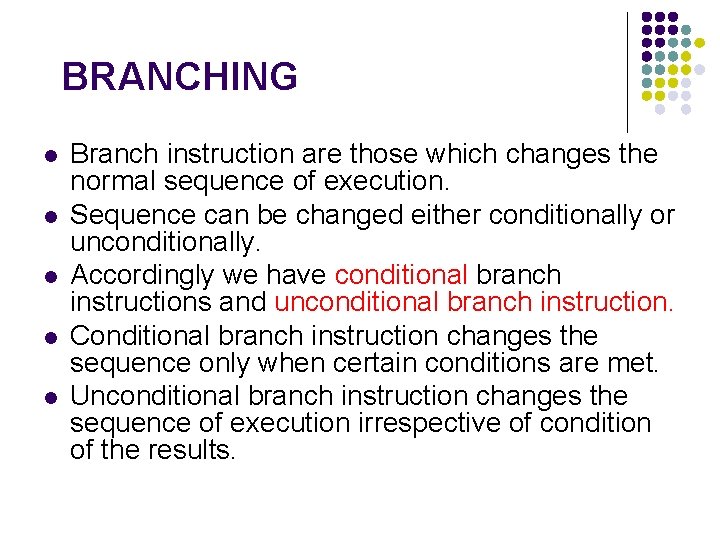

ASSEMBLY LANGUAGE NOTATION (ALN) l l 1. 2. RTN is easy to understand but cannot be used to represent machine instructions Mnemonics can be converted to machine language, which processor understands using assembler Eg: MOVE LOCN, R 2 ADD R 3, R 2, R 4

TYPE OF INSTRUCTION Ø Three address instruction • Syntax: Operation source 1, source 2, destination • Eg: ADD D, E, F where D, E, F are memory location • Advantage: Single instruction can perform the complete operation • Disadvantage : Instruction code will be too large to fit in one word location in memory

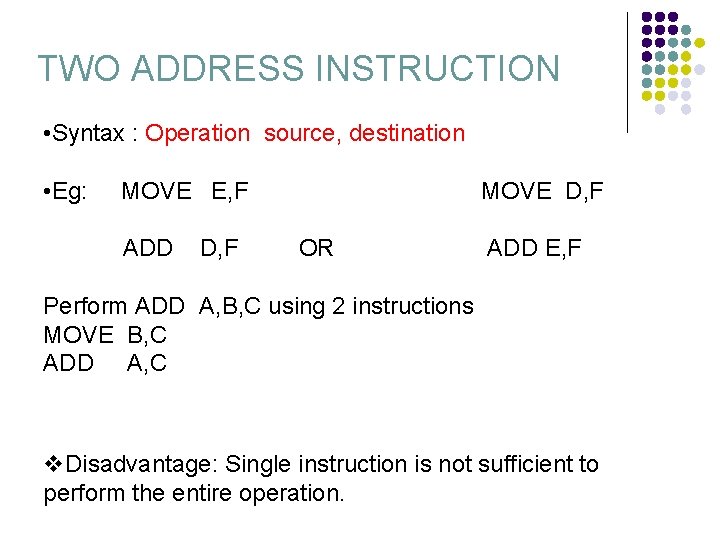

TWO ADDRESS INSTRUCTION • Syntax : Operation source, destination • Eg: MOVE E, F ADD D, F MOVE D, F OR ADD E, F Perform ADD A, B, C using 2 instructions MOVE B, C ADD A, C v. Disadvantage: Single instruction is not sufficient to perform the entire operation.

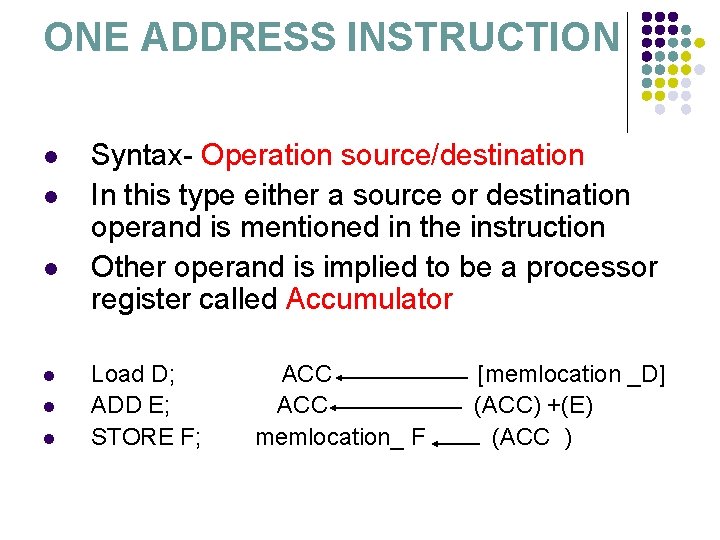

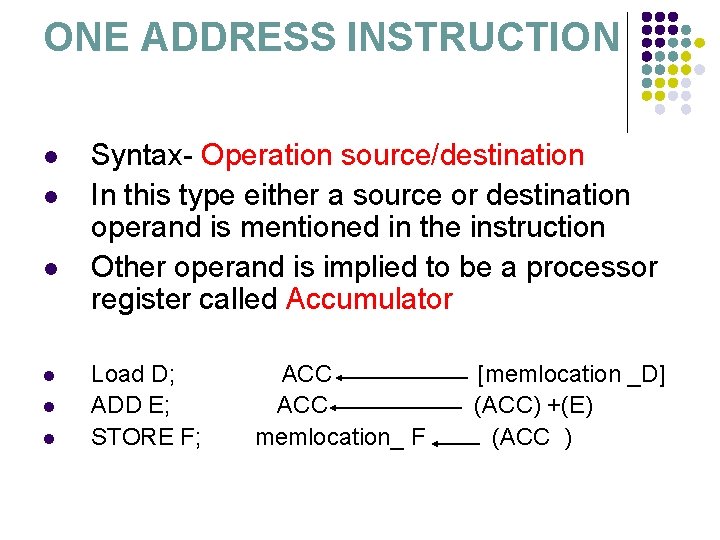

ONE ADDRESS INSTRUCTION l l l Syntax- Operation source/destination In this type either a source or destination operand is mentioned in the instruction Other operand is implied to be a processor register called Accumulator Load D; ADD E; STORE F; ACC memlocation_ F [memlocation _D] (ACC) +(E) (ACC )

Zero address instruction l Location of all operands are defined implicitly l Operands are stored in a structure called pushdown stack

![Assembly Language Notation Structure C AB C AB ADD A B Operation Source Assembly Language Notation Structure C= A+B C [A]+[B] ADD A, B Operation Source ,](https://slidetodoc.com/presentation_image_h2/65b811562dc636e713c863e8c20f9fc3/image-15.jpg)

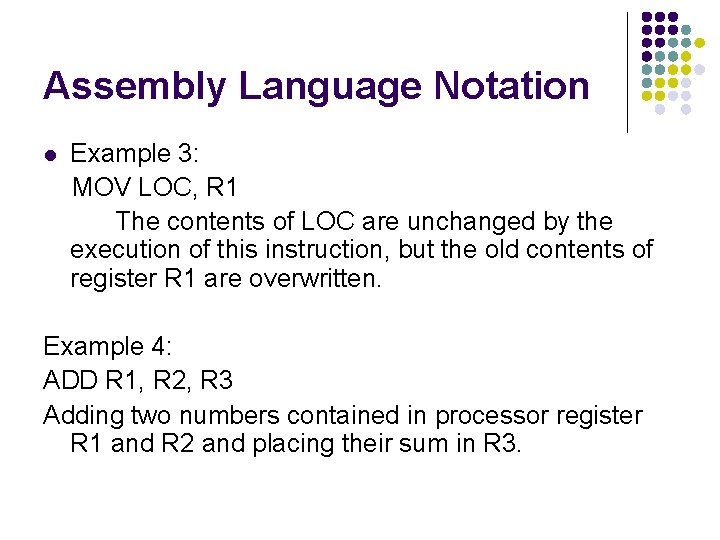

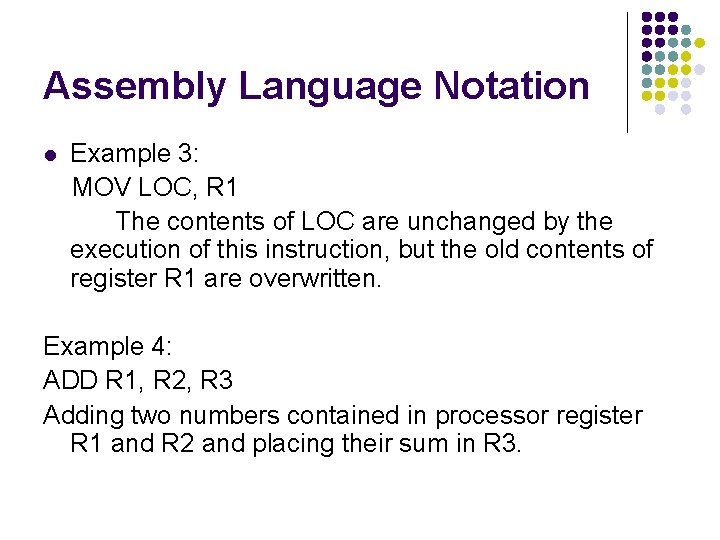

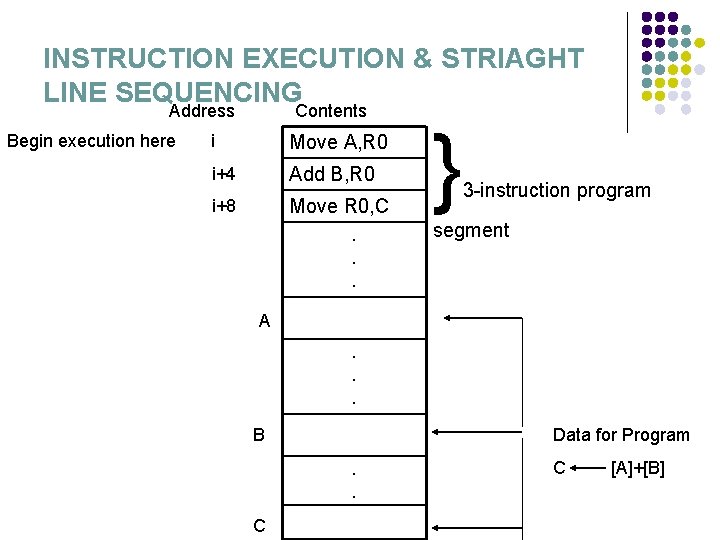

Assembly Language Notation Structure C= A+B C [A]+[B] ADD A, B Operation Source , Destination B [A] + [B] ADD A, B, C Operation Source 1, Source 2, Destination C [A]+[B]

![Examples MOV B C C B Examples MOV B, C C [B]](https://slidetodoc.com/presentation_image_h2/65b811562dc636e713c863e8c20f9fc3/image-16.jpg)

Examples MOV B, C C [B]

Assembly Language Notation l Example 3: MOV LOC, R 1 The contents of LOC are unchanged by the execution of this instruction, but the old contents of register R 1 are overwritten. Example 4: ADD R 1, R 2, R 3 Adding two numbers contained in processor register R 1 and R 2 and placing their sum in R 3.

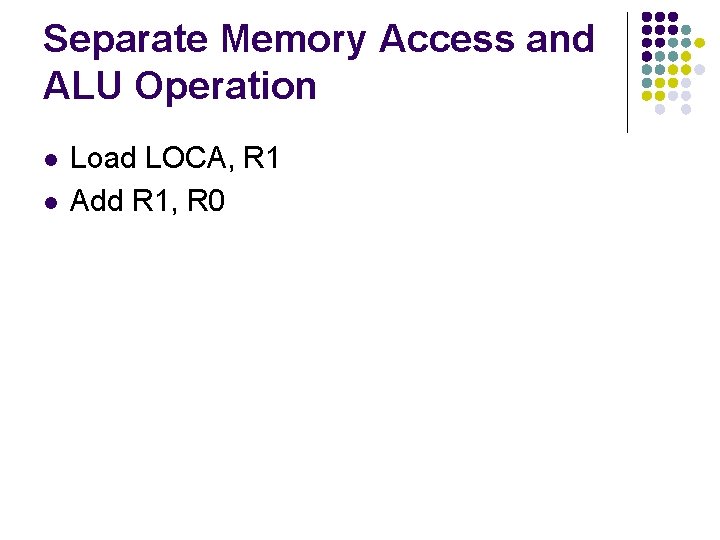

Separate Memory Access and ALU Operation l l Load LOCA, R 1 Add R 1, R 0

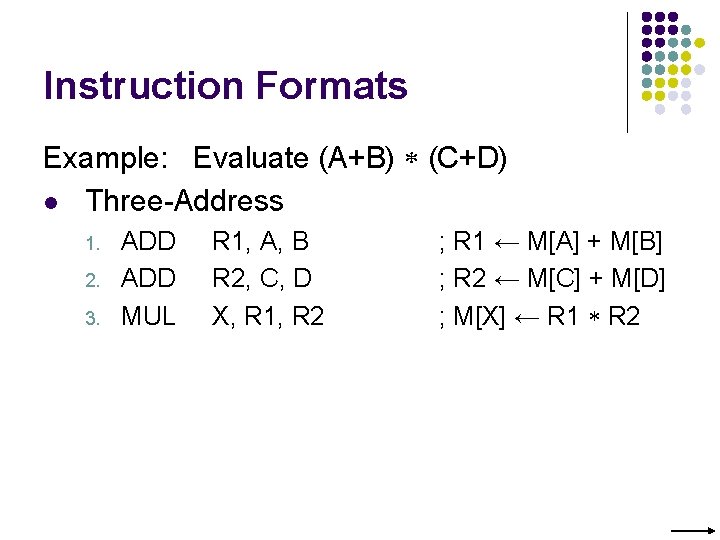

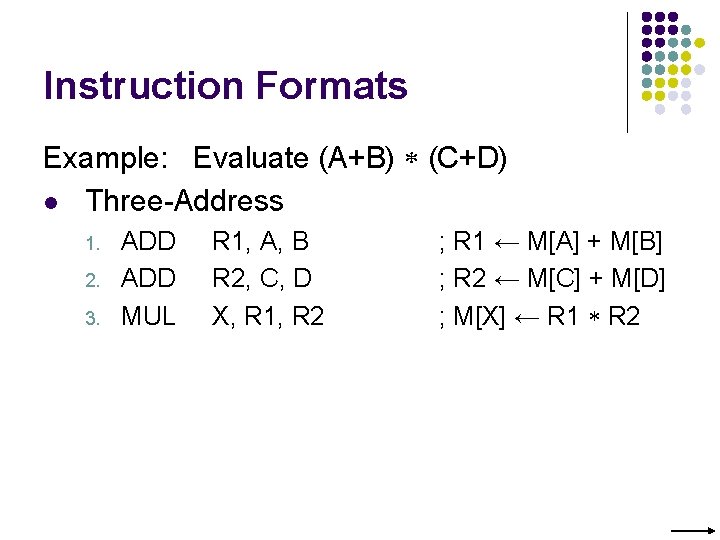

Instruction Formats Example: Evaluate (A+B) (C+D) l Three-Address 1. 2. 3. ADD MUL R 1, A, B R 2, C, D X, R 1, R 2 ; R 1 ← M[A] + M[B] ; R 2 ← M[C] + M[D] ; M[X] ← R 1 R 2

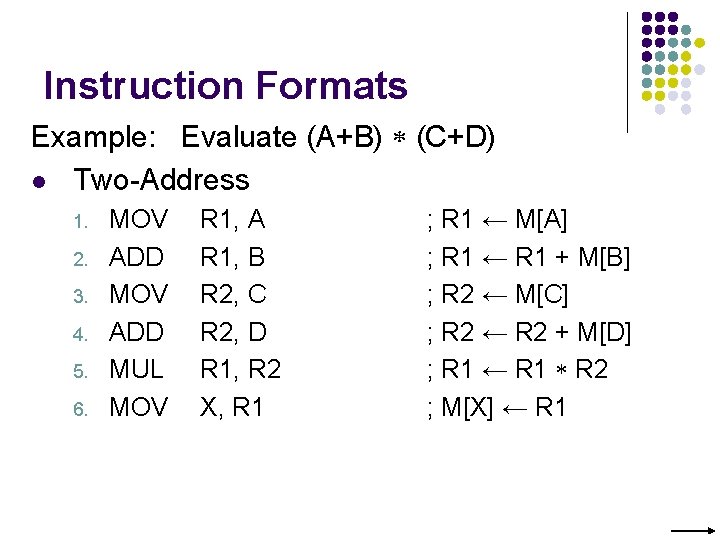

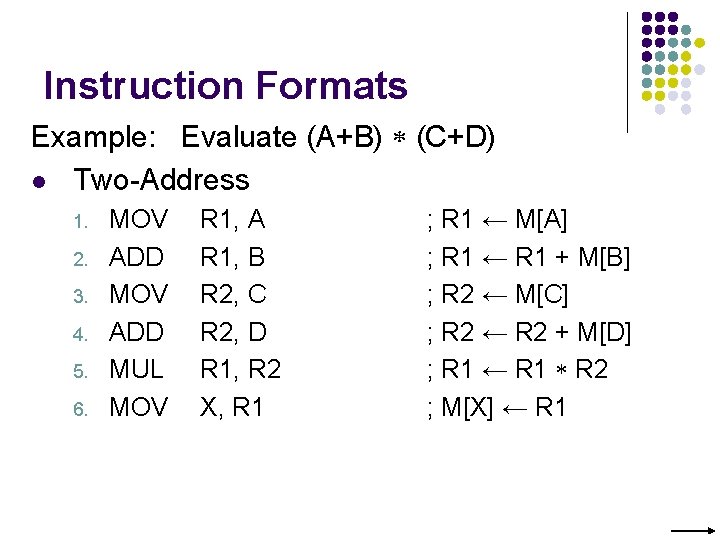

Instruction Formats Example: Evaluate (A+B) (C+D) l Two-Address 1. 2. 3. 4. 5. 6. MOV ADD MUL MOV R 1, A R 1, B R 2, C R 2, D R 1, R 2 X, R 1 ; R 1 ← M[A] ; R 1 ← R 1 + M[B] ; R 2 ← M[C] ; R 2 ← R 2 + M[D] ; R 1 ← R 1 R 2 ; M[X] ← R 1

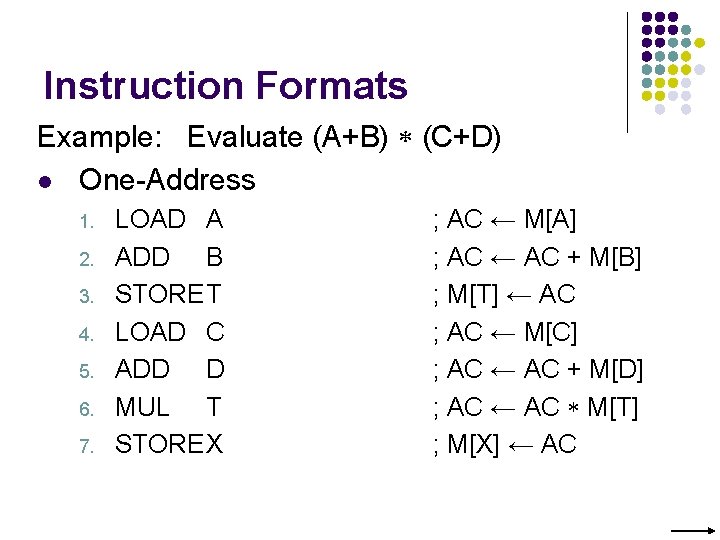

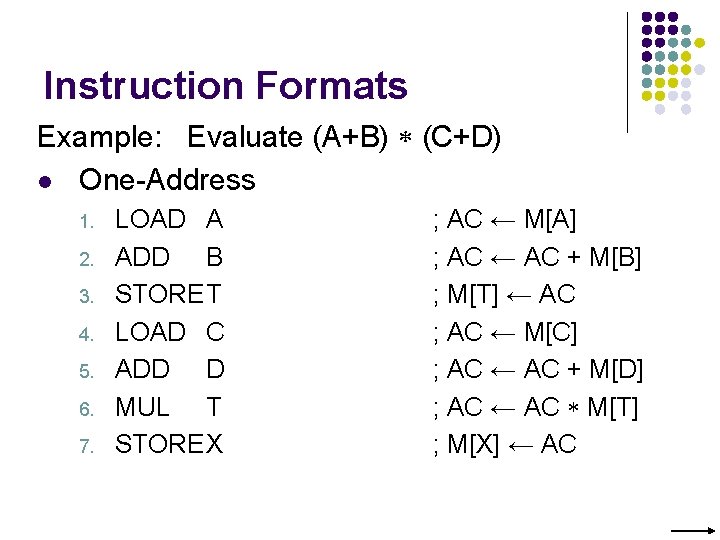

Instruction Formats Example: Evaluate (A+B) (C+D) l One-Address 1. 2. 3. 4. 5. 6. 7. LOAD A ADD B STORET LOAD C ADD D MUL T STOREX ; AC ← M[A] ; AC ← AC + M[B] ; M[T] ← AC ; AC ← M[C] ; AC ← AC + M[D] ; AC ← AC M[T] ; M[X] ← AC

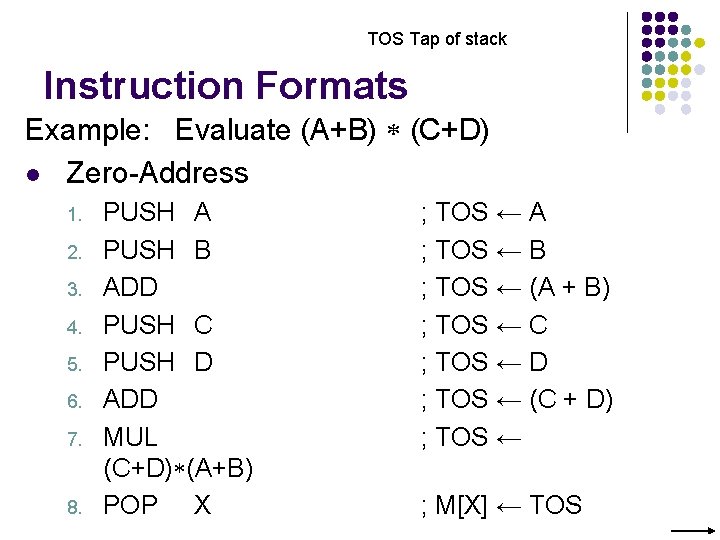

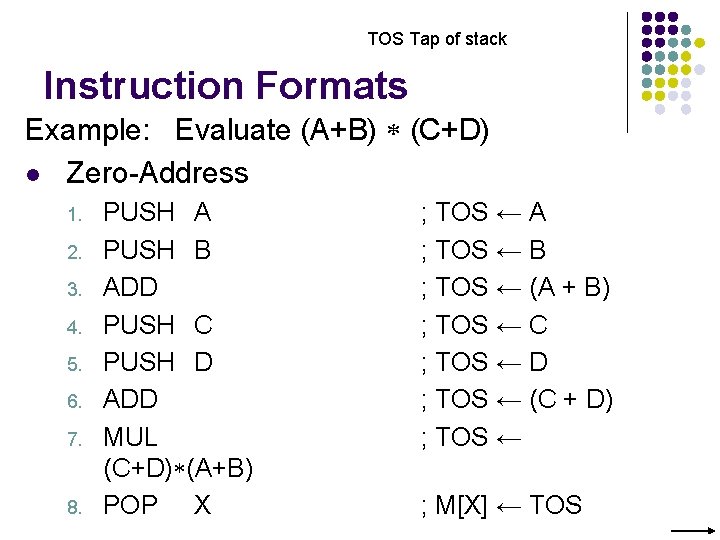

TOS Tap of stack Instruction Formats Example: Evaluate (A+B) (C+D) l Zero-Address 1. 2. 3. 4. 5. 6. 7. 8. PUSH A PUSH B ADD PUSH C PUSH D ADD MUL (C+D) (A+B) POP X ; TOS ← A ; TOS ← B ; TOS ← (A + B) ; TOS ← C ; TOS ← D ; TOS ← (C + D) ; TOS ← ; M[X] ← TOS

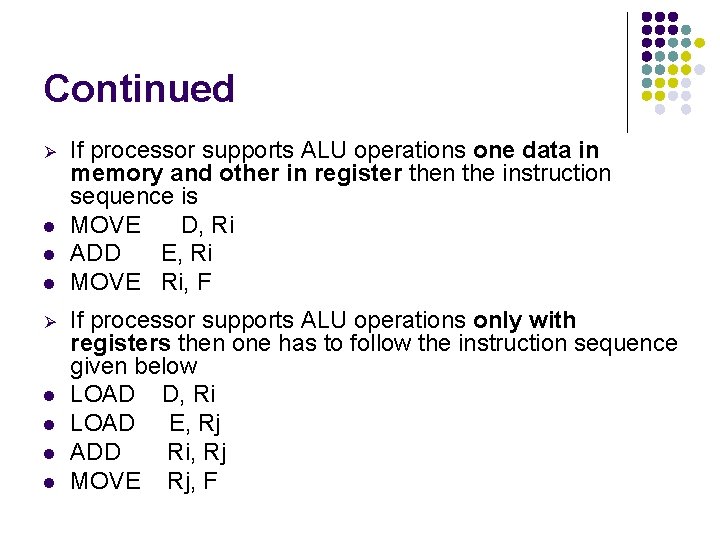

Continued Ø l l l l If processor supports ALU operations one data in memory and other in register then the instruction sequence is MOVE D, Ri ADD E, Ri MOVE Ri, F If processor supports ALU operations only with registers then one has to follow the instruction sequence given below LOAD D, Ri LOAD E, Rj ADD Ri, Rj MOVE Rj, F

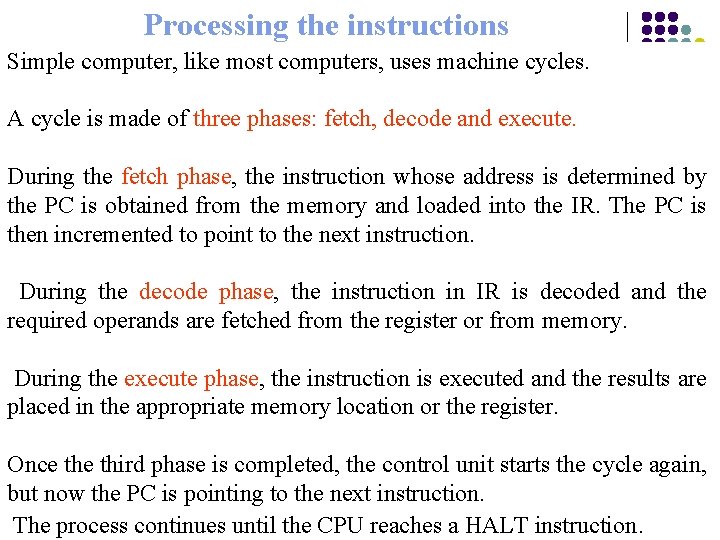

Processing the instructions Simple computer, like most computers, uses machine cycles. A cycle is made of three phases: fetch, decode and execute. During the fetch phase, the instruction whose address is determined by the PC is obtained from the memory and loaded into the IR. The PC is then incremented to point to the next instruction. During the decode phase, the instruction in IR is decoded and the required operands are fetched from the register or from memory. During the execute phase, the instruction is executed and the results are placed in the appropriate memory location or the register. Once third phase is completed, the control unit starts the cycle again, but now the PC is pointing to the next instruction. The process continues until the CPU reaches a HALT instruction.

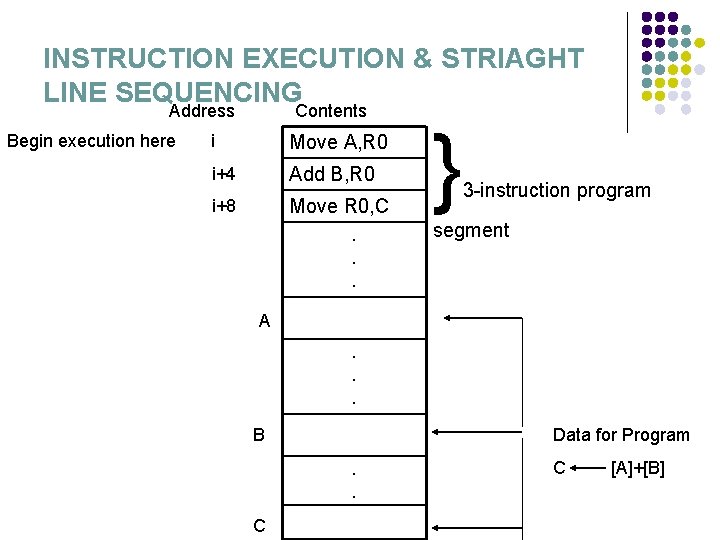

INSTRUCTION EXECUTION & STRIAGHT LINE SEQUENCING Address Begin execution here Contents i Move A, R 0 i+4 Add B, R 0 i+8 Move R 0, C. . . } 3 -instruction program segment A. . . B Data for Program. . C C [A]+[B]

l l l PC – Program counter: hold the address of the next instruction to be executed Straight line sequencing: If fetching and executing of instructions is carried out one by one from successive addresses of memory, it is called straight line sequencing. Major two phase of instruction execution Instruction fetch phase: Instruction is fetched form memory and is placed in instruction register IR Instruction execute phase: Contents of IR is decoded and processor carries out the operation either by reading data from memory or registers.

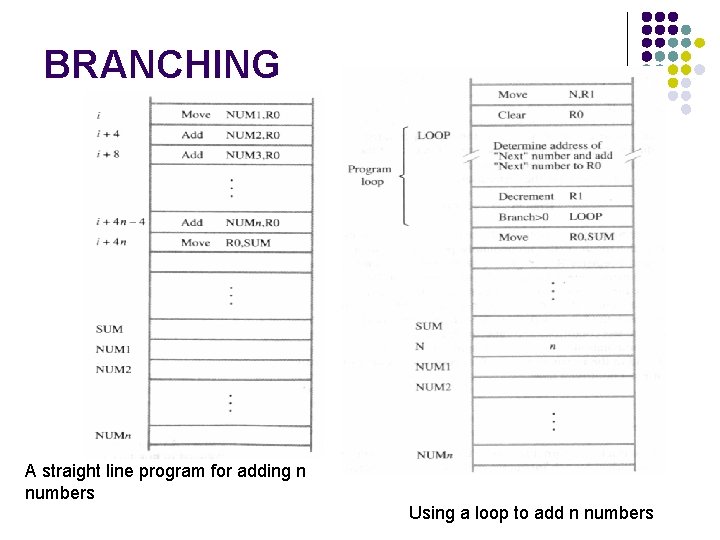

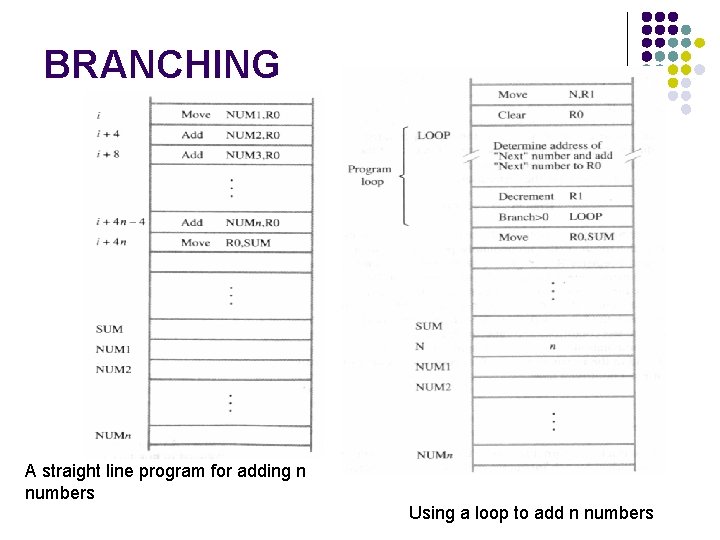

BRANCHING A straight line program for adding n numbers Using a loop to add n numbers

BRANCHING l l l Branch instruction are those which changes the normal sequence of execution. Sequence can be changed either conditionally or unconditionally. Accordingly we have conditional branch instructions and unconditional branch instruction. Conditional branch instruction changes the sequence only when certain conditions are met. Unconditional branch instruction changes the sequence of execution irrespective of condition of the results.