Register and Counter Design Registers in the Basic

Register and Counter Design

Registers in the Basic Computer • Registers are basic building blocks in digital systems. – store information – auxiliary circuits may modify stored information or “steer it” to and from register

Registers and Counters A register is a set of flip flops, often supplemented by additional circuits to control input and output. - can have parallel I/O or serial I/O or combination Usually, registers are used to store a set of related bits. -bits that collectively represent an integer value - bits of an ASCII character code -status bits for a device in a computer system (disk controller) Counters are registers that store numeric values alongwith circuits to increment/decrement the stored value.

counters - up-counters, down-counters, up-down counters - generalized counters - BCD counters, gray-code counters, . . .

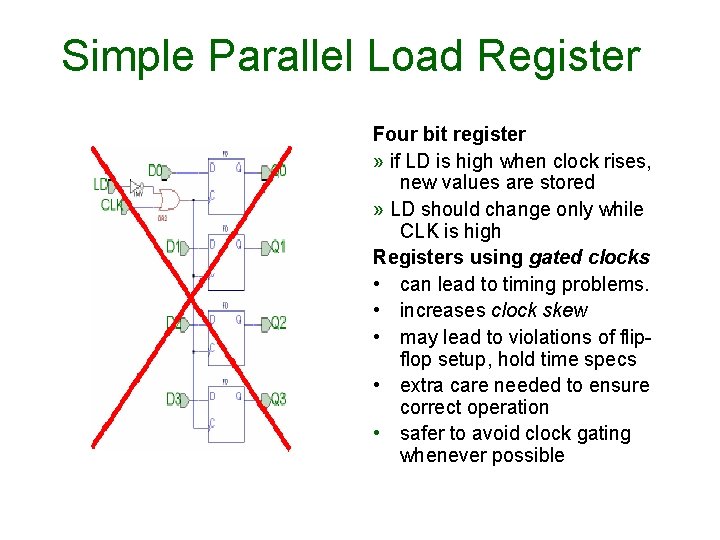

Simple Parallel Load Register Four bit register » if LD is high when clock rises, new values are stored » LD should change only while CLK is high Registers using gated clocks • can lead to timing problems. • increases clock skew • may lead to violations of flipflop setup, hold time specs • extra care needed to ensure correct operation • safer to avoid clock gating whenever possible

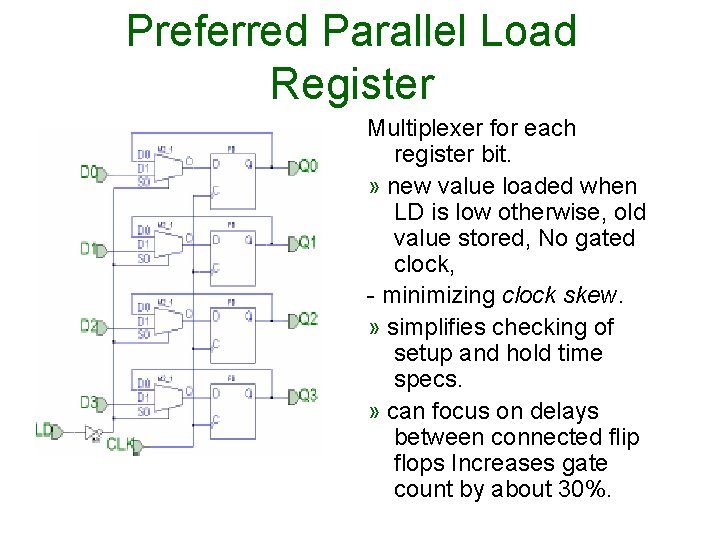

Preferred Parallel Load Register Multiplexer for each register bit. » new value loaded when LD is low otherwise, old value stored, No gated clock, - minimizing clock skew. » simplifies checking of setup and hold time specs. » can focus on delays between connected flip flops Increases gate count by about 30%.

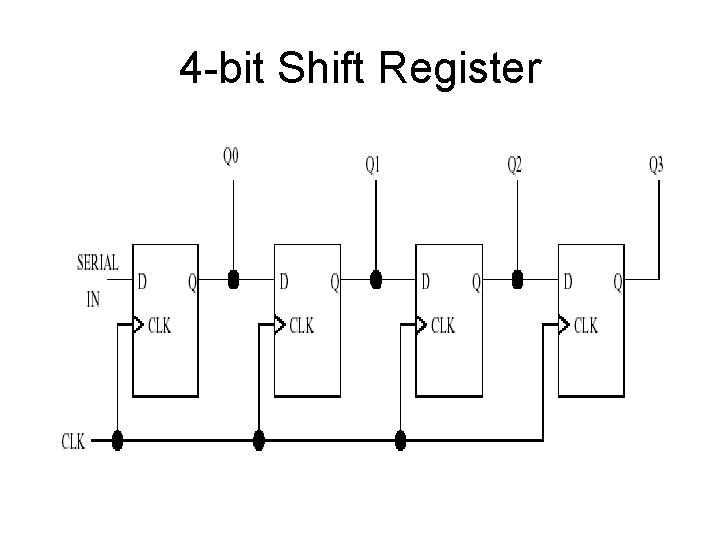

4 -bit Shift Register

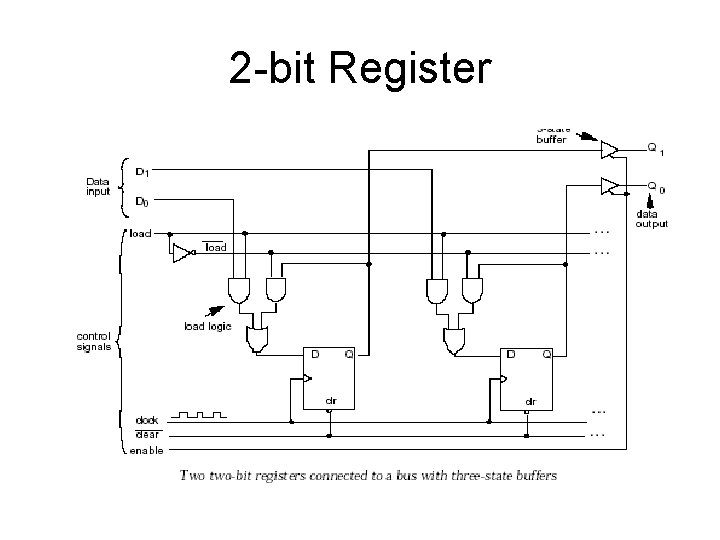

2 -bit Register

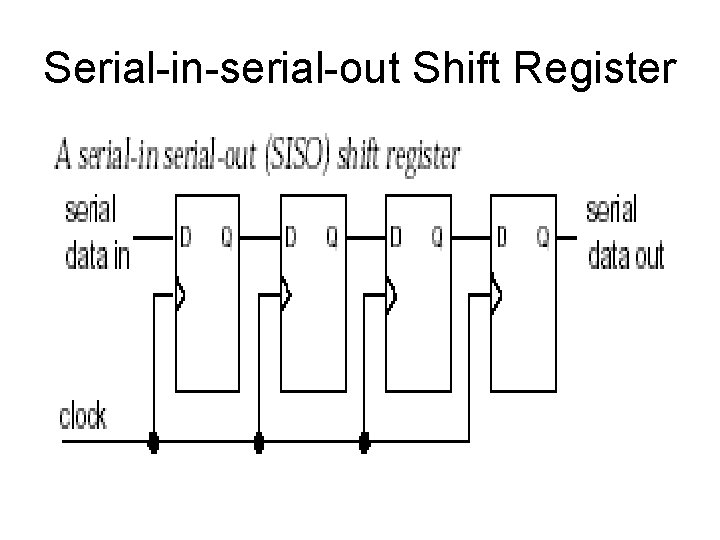

Serial-in-serial-out Shift Register

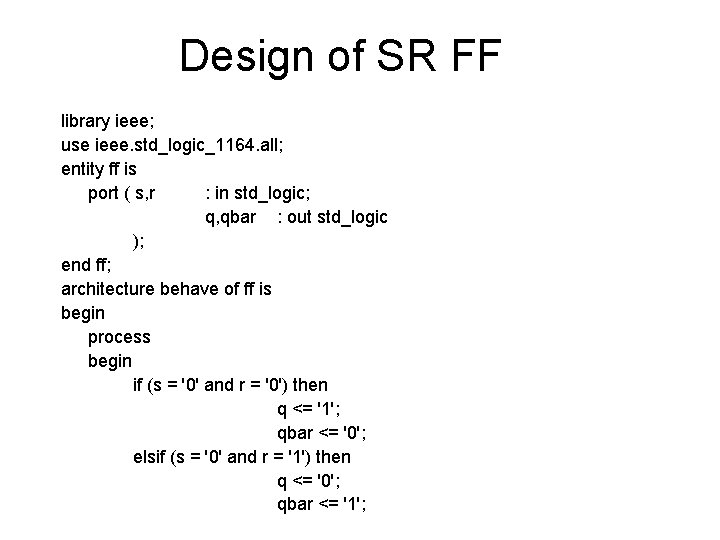

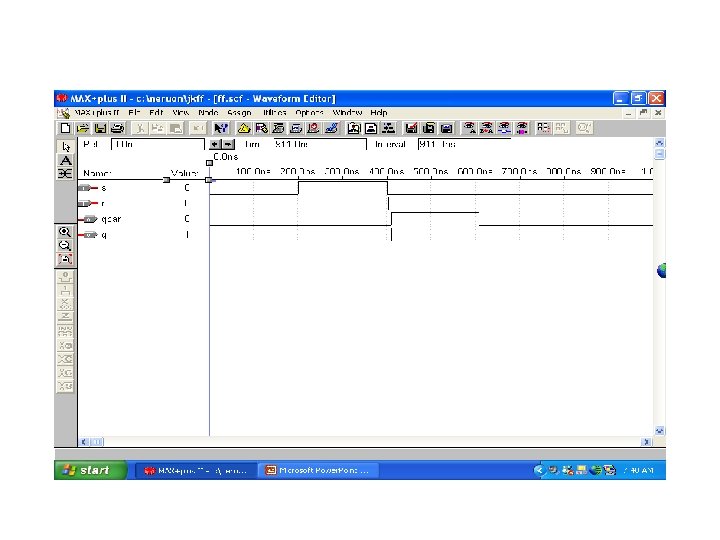

Design of SR FF library ieee; use ieee. std_logic_1164. all; entity ff is port ( s, r : in std_logic; q, qbar : out std_logic ); end ff; architecture behave of ff is begin process begin if (s = '0' and r = '0') then q <= '1'; qbar <= '0'; elsif (s = '0' and r = '1') then q <= '0'; qbar <= '1';

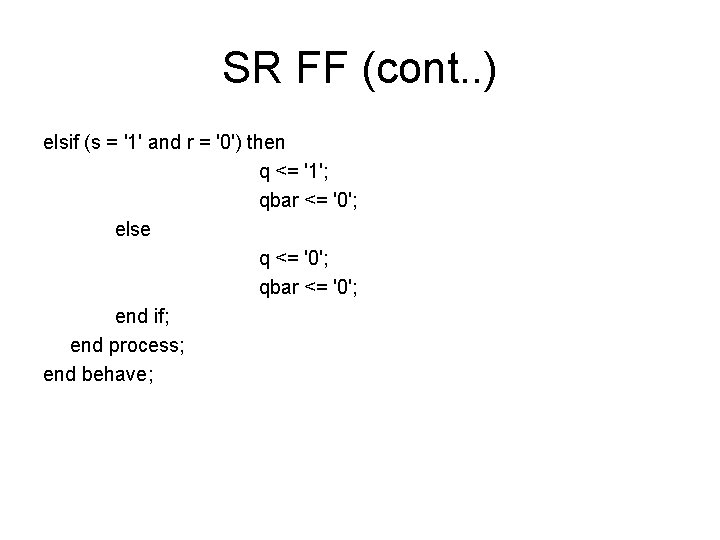

SR FF (cont. . ) elsif (s = '1' and r = '0') then q <= '1'; qbar <= '0'; else q <= '0'; qbar <= '0'; end if; end process; end behave;

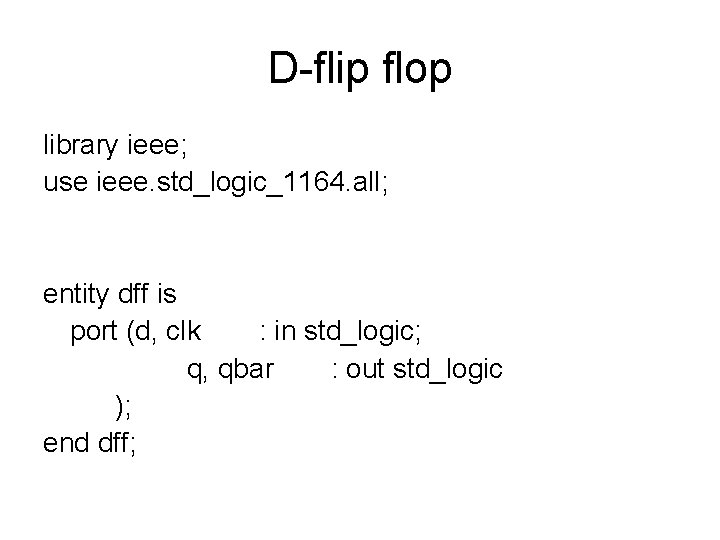

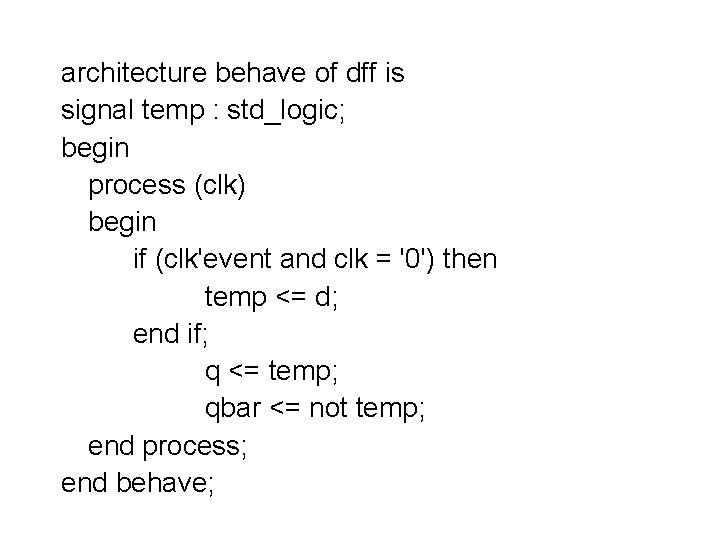

D-flip flop library ieee; use ieee. std_logic_1164. all; entity dff is port (d, clk : in std_logic; q, qbar : out std_logic ); end dff;

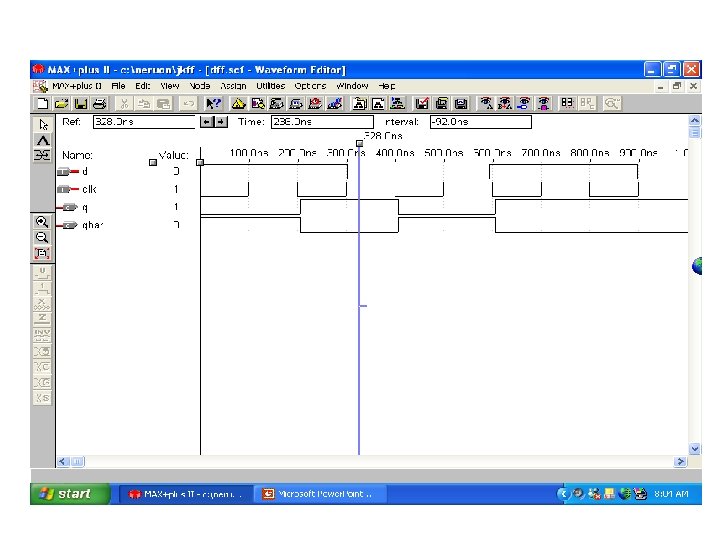

architecture behave of dff is signal temp : std_logic; begin process (clk) begin if (clk'event and clk = '0') then temp <= d; end if; q <= temp; qbar <= not temp; end process; end behave;

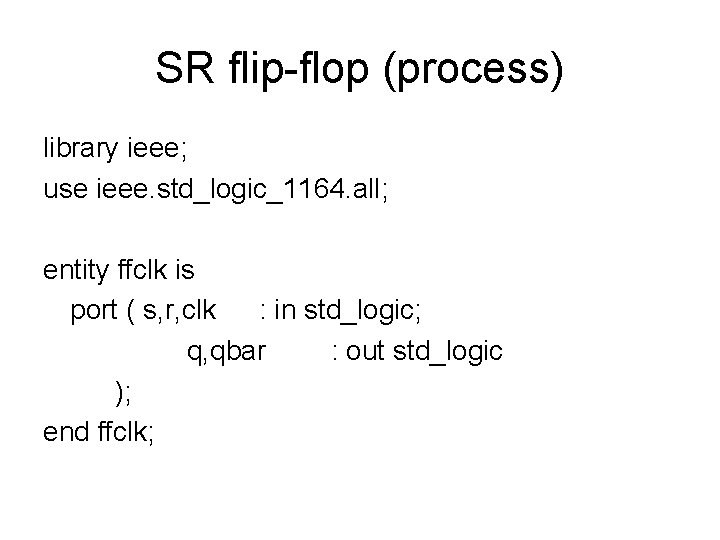

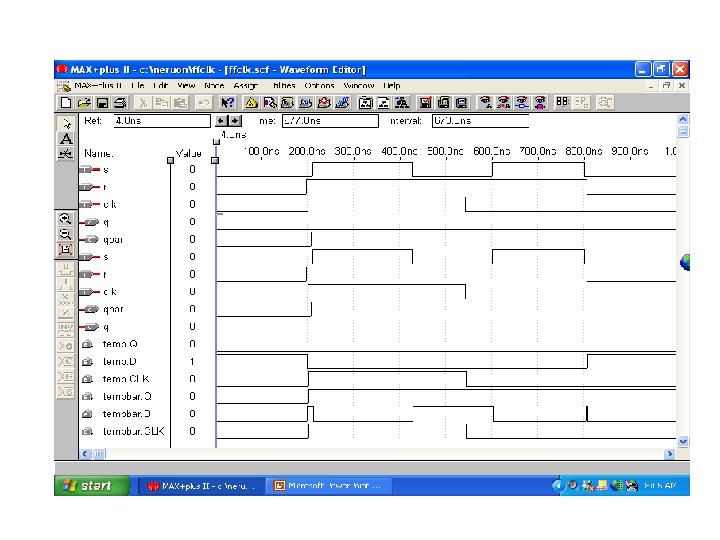

SR flip-flop (process) library ieee; use ieee. std_logic_1164. all; entity ffclk is port ( s, r, clk : in std_logic; q, qbar : out std_logic ); end ffclk;

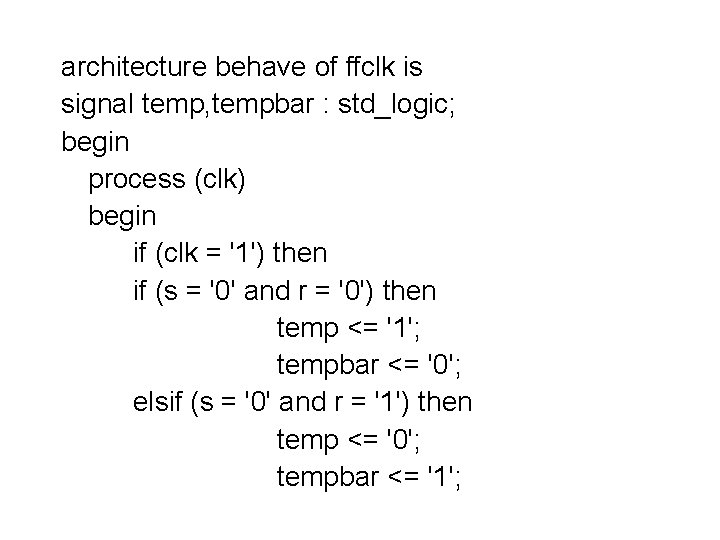

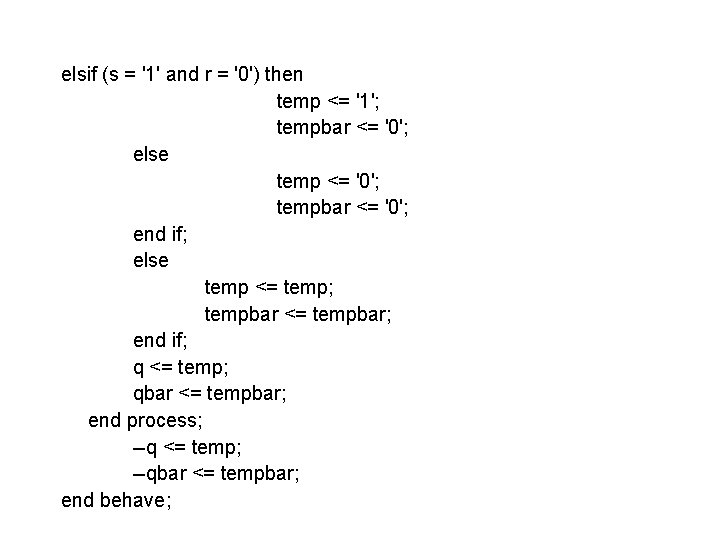

architecture behave of ffclk is signal temp, tempbar : std_logic; begin process (clk) begin if (clk = '1') then if (s = '0' and r = '0') then temp <= '1'; tempbar <= '0'; elsif (s = '0' and r = '1') then temp <= '0'; tempbar <= '1';

elsif (s = '1' and r = '0') then temp <= '1'; tempbar <= '0'; else temp <= '0'; tempbar <= '0'; end if; else temp <= temp; tempbar <= tempbar; end if; q <= temp; qbar <= tempbar; end process; --q <= temp; --qbar <= tempbar; end behave;

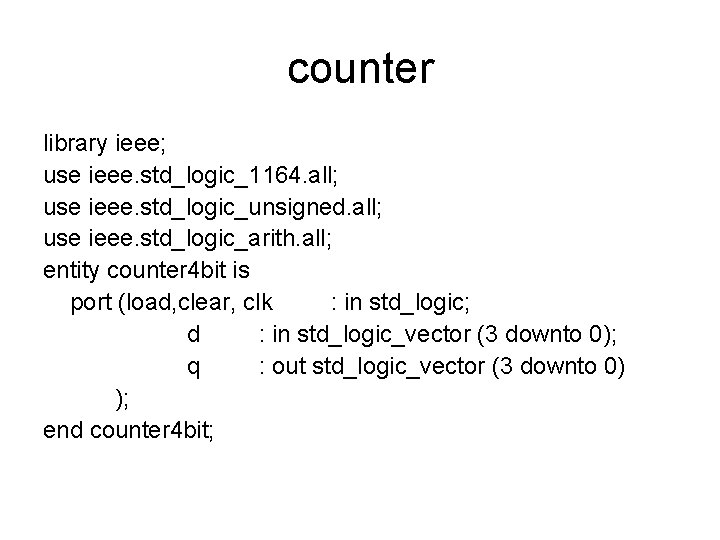

counter library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; use ieee. std_logic_arith. all; entity counter 4 bit is port (load, clear, clk : in std_logic; d : in std_logic_vector (3 downto 0); q : out std_logic_vector (3 downto 0) ); end counter 4 bit;

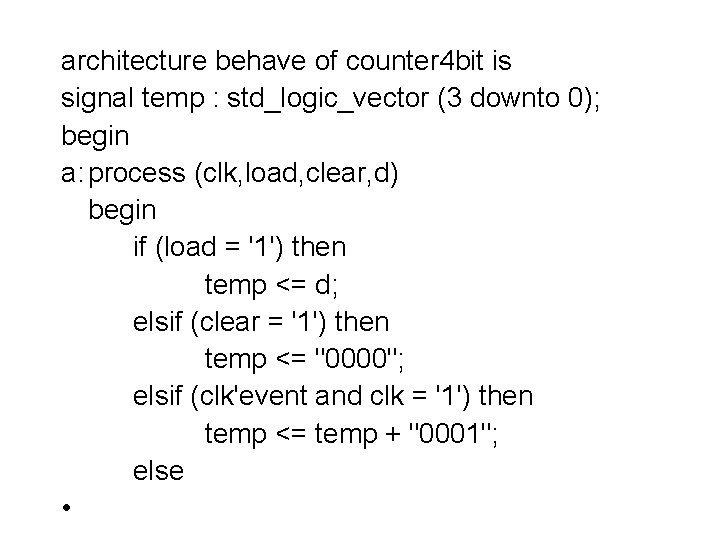

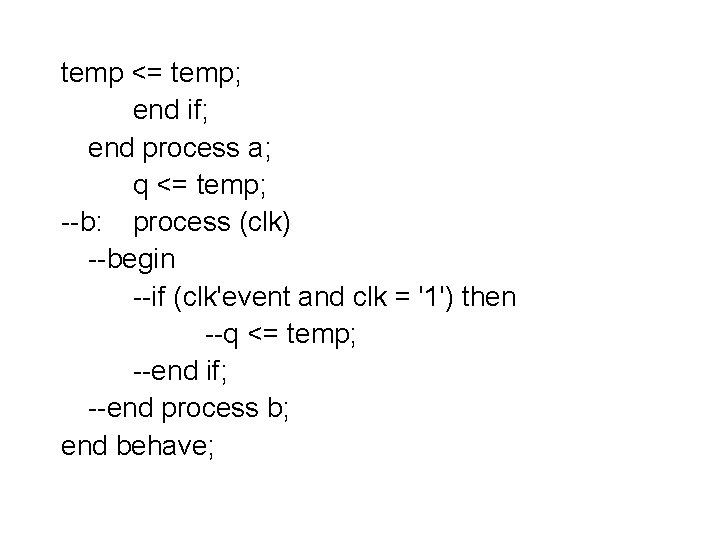

architecture behave of counter 4 bit is signal temp : std_logic_vector (3 downto 0); begin a: process (clk, load, clear, d) begin if (load = '1') then temp <= d; elsif (clear = '1') then temp <= "0000"; elsif (clk'event and clk = '1') then temp <= temp + "0001"; else •

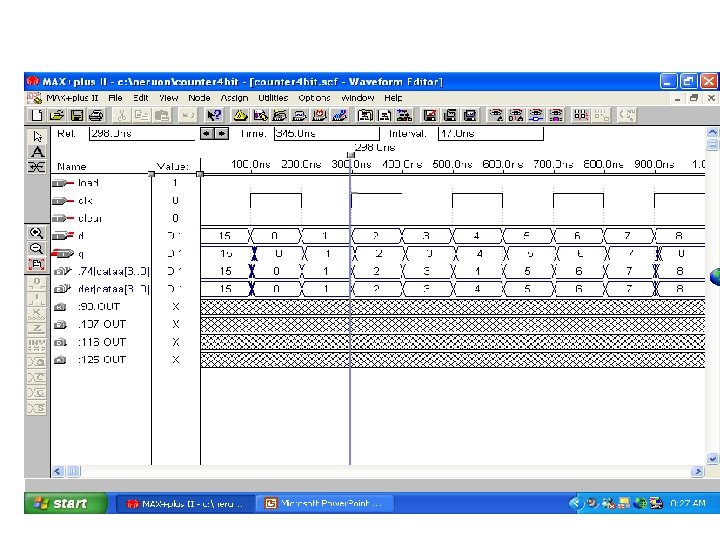

temp <= temp; end if; end process a; q <= temp; --b: process (clk) --begin --if (clk'event and clk = '1') then --q <= temp; --end if; --end process b; end behave;

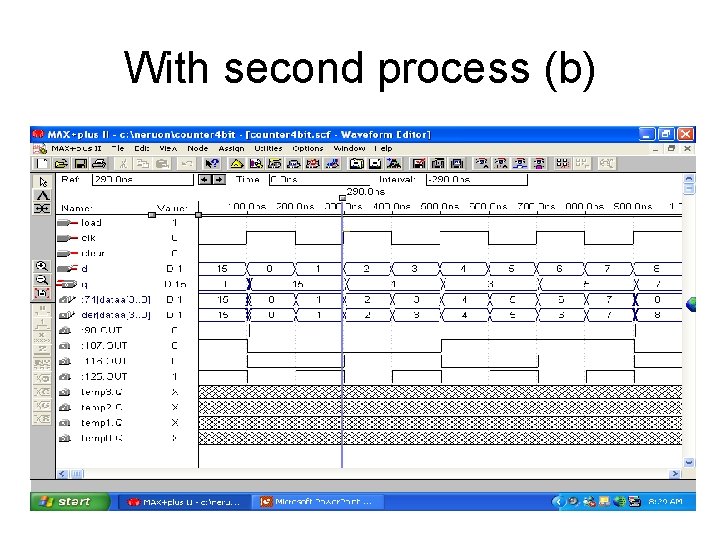

With second process (b)

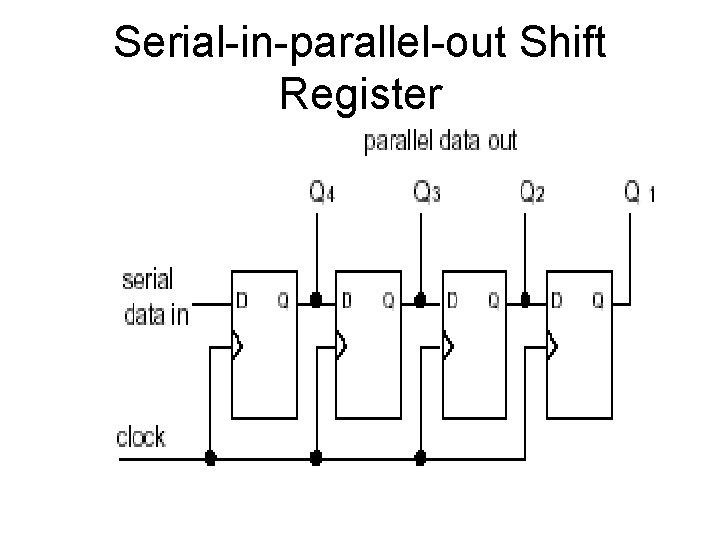

Serial-in-parallel-out Shift Register

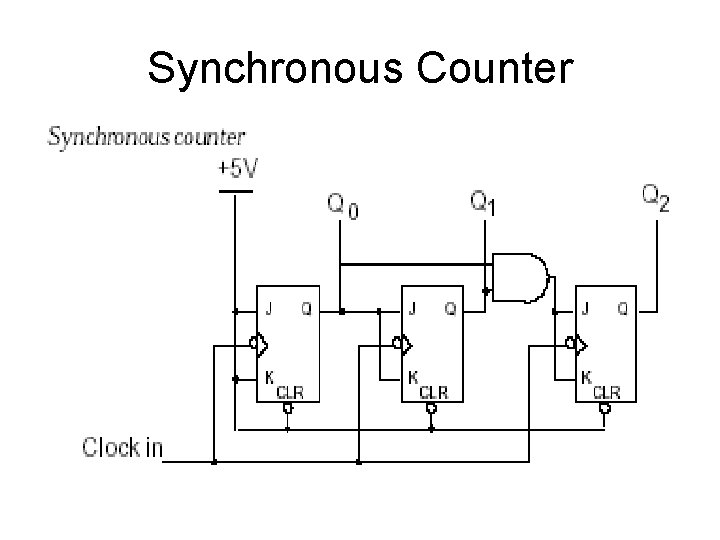

Synchronous Counter

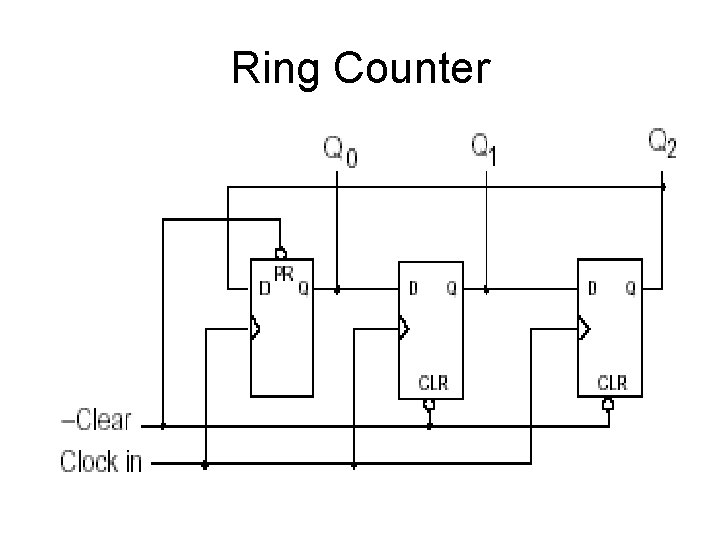

Ring Counter

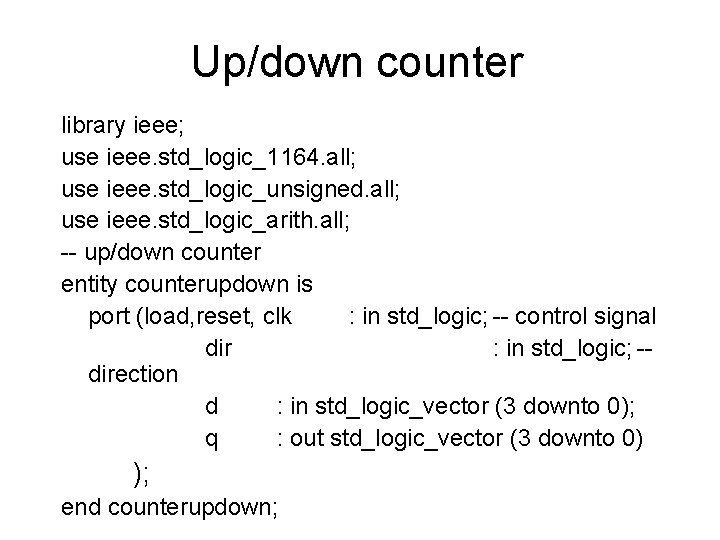

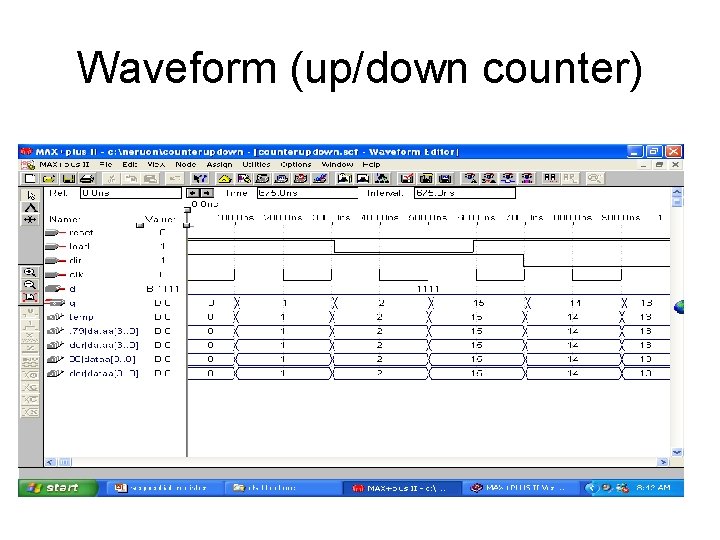

Up/down counter library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; use ieee. std_logic_arith. all; -- up/down counter entity counterupdown is port (load, reset, clk : in std_logic; -- control signal dir : in std_logic; -direction d : in std_logic_vector (3 downto 0); q : out std_logic_vector (3 downto 0) ); end counterupdown;

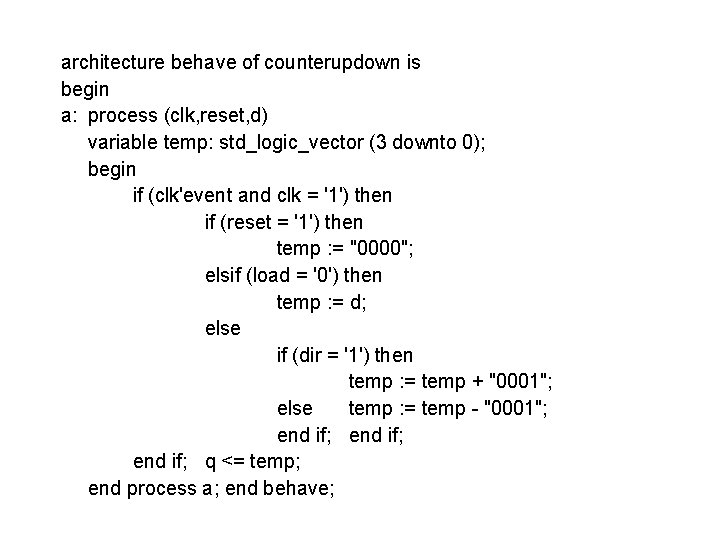

architecture behave of counterupdown is begin a: process (clk, reset, d) variable temp: std_logic_vector (3 downto 0); begin if (clk'event and clk = '1') then if (reset = '1') then temp : = "0000"; elsif (load = '0') then temp : = d; else if (dir = '1') then temp : = temp + "0001"; else temp : = temp - "0001"; end if; q <= temp; end process a; end behave;

Waveform (up/down counter)

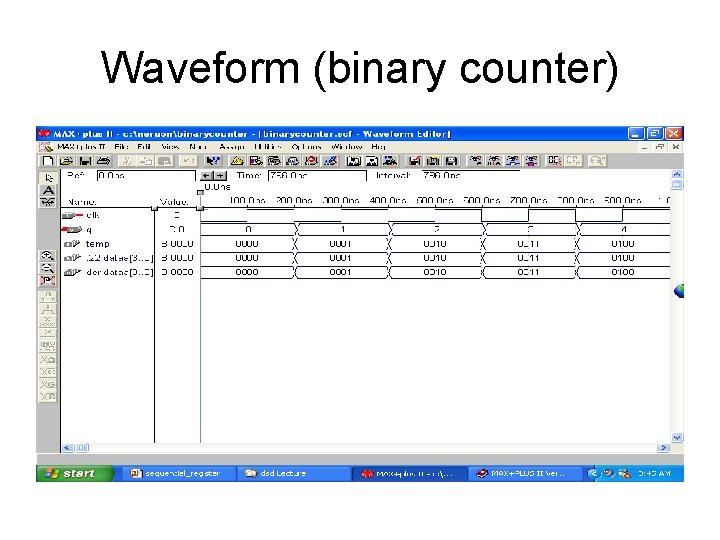

Binary counter library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; use ieee. std_logic_arith. all; entity binarycounter is port (clk : in std_logic; q : out std_logic_vector (3 downto 0) ); end binarycounter;

architecture behave of binarycounter is signal temp : std_logic_vector (3 downto 0); begin a: process (clk) begin if (clk'event and clk = '0') then temp <= temp + "0001"; end if; q <= temp; end process a; end behave;

Waveform (binary counter)

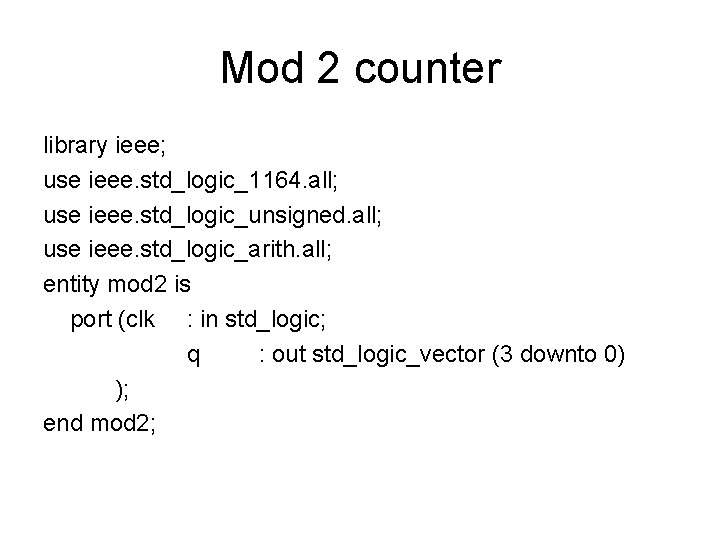

Mod 2 counter library ieee; use ieee. std_logic_1164. all; use ieee. std_logic_unsigned. all; use ieee. std_logic_arith. all; entity mod 2 is port (clk : in std_logic; q : out std_logic_vector (3 downto 0) ); end mod 2;

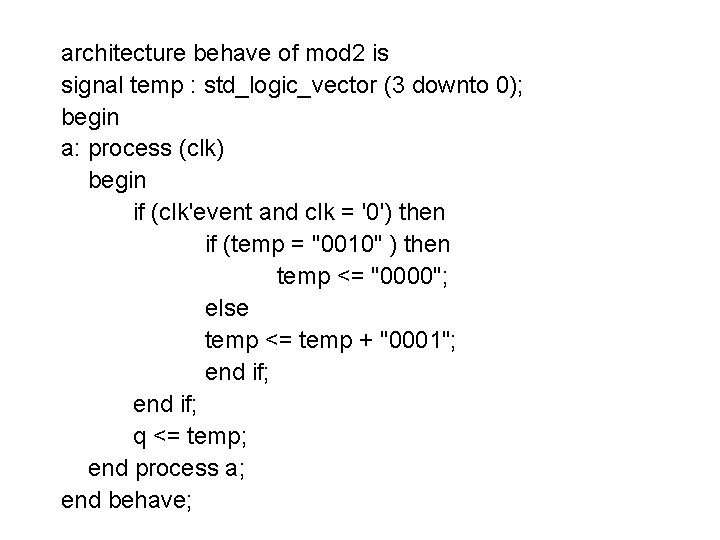

architecture behave of mod 2 is signal temp : std_logic_vector (3 downto 0); begin a: process (clk) begin if (clk'event and clk = '0') then if (temp = "0010" ) then temp <= "0000"; else temp <= temp + "0001"; end if; q <= temp; end process a; end behave;

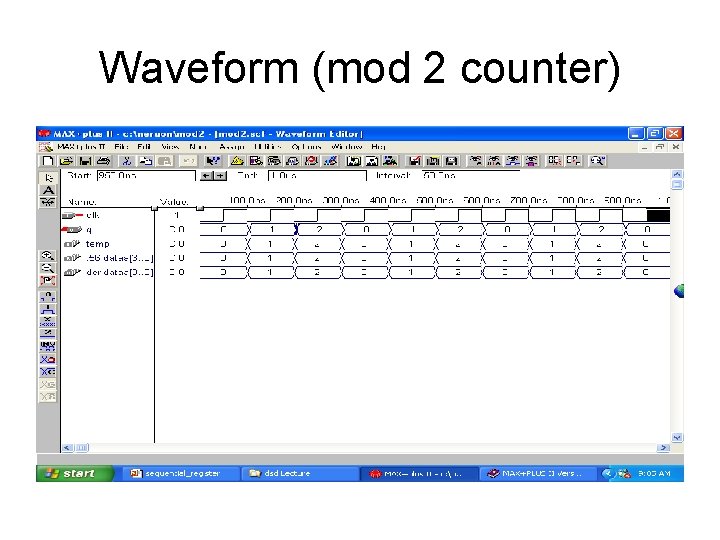

Waveform (mod 2 counter)

- Slides: 36