Reference Router on Net FPGA Course Presenter YiFang

![INTRODUCTION l Reference Router Features [3] • Forwards IPv 4 packets of length 64 INTRODUCTION l Reference Router Features [3] • Forwards IPv 4 packets of length 64](https://slidetodoc.com/presentation_image_h/1b14030f9b09a5c32d55d2eb2026bf43/image-3.jpg)

![REFERNCE l l [1]https: //github. com/Net. FPGA/netfpga/wiki/Releases [2]http: //netfpga. org/ [3]http: //www. cl. cam. REFERNCE l l [1]https: //github. com/Net. FPGA/netfpga/wiki/Releases [2]http: //netfpga. org/ [3]http: //www. cl. cam.](https://slidetodoc.com/presentation_image_h/1b14030f9b09a5c32d55d2eb2026bf43/image-24.jpg)

- Slides: 24

Reference Router on Net. FPGA Course: Presenter: Yi-Fang, Huang Date: 108/03/12 Department of Computer Science and Information Engineering, National Cheng Kung University, Tainan, Taiwan, R. O. C.

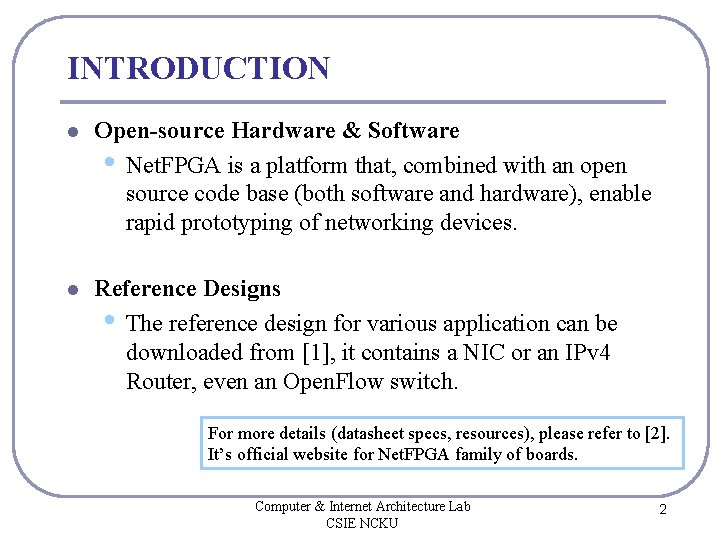

INTRODUCTION l Open-source Hardware & Software • Net. FPGA is a platform that, combined with an open source code base (both software and hardware), enable rapid prototyping of networking devices. l Reference Designs • The reference design for various application can be downloaded from [1], it contains a NIC or an IPv 4 Router, even an Open. Flow switch. For more details (datasheet specs, resources), please refer to [2]. It’s official website for Net. FPGA family of boards. Computer & Internet Architecture Lab CSIE NCKU 2

![INTRODUCTION l Reference Router Features 3 Forwards IPv 4 packets of length 64 INTRODUCTION l Reference Router Features [3] • Forwards IPv 4 packets of length 64](https://slidetodoc.com/presentation_image_h/1b14030f9b09a5c32d55d2eb2026bf43/image-3.jpg)

INTRODUCTION l Reference Router Features [3] • Forwards IPv 4 packets of length 64 -1500 bytes. • Performs Longest Prefix Matching on destination address. • Allows host receive packets by filter on destination address. • Drops packets with bad IP checksum. Computer & Internet Architecture Lab CSIE NCKU 3

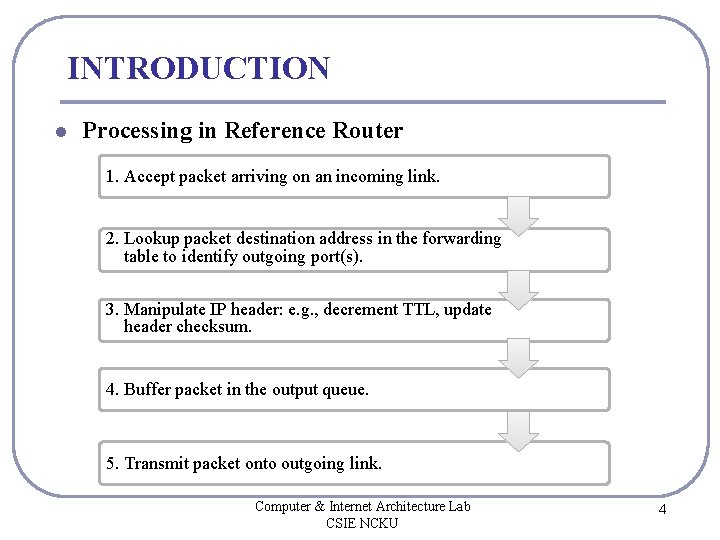

INTRODUCTION l Processing in Reference Router 1. Accept packet arriving on an incoming link. 2. Lookup packet destination address in the forwarding table to identify outgoing port(s). 3. Manipulate IP header: e. g. , decrement TTL, update header checksum. 4. Buffer packet in the output queue. 5. Transmit packet onto outgoing link. Computer & Internet Architecture Lab CSIE NCKU 4

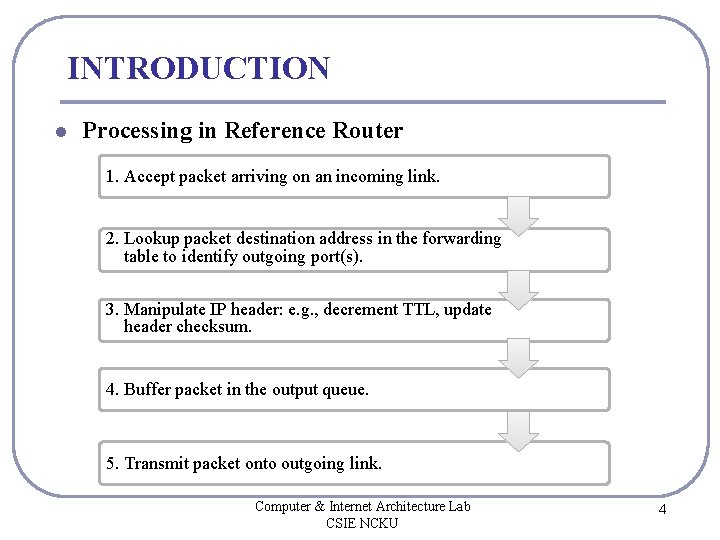

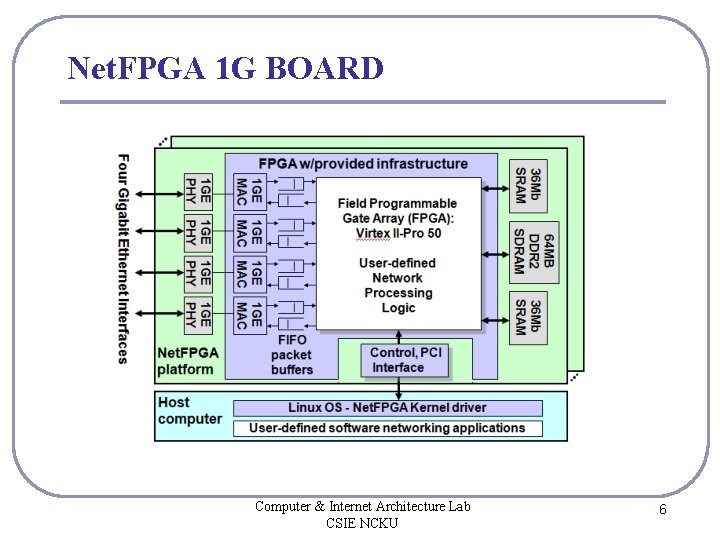

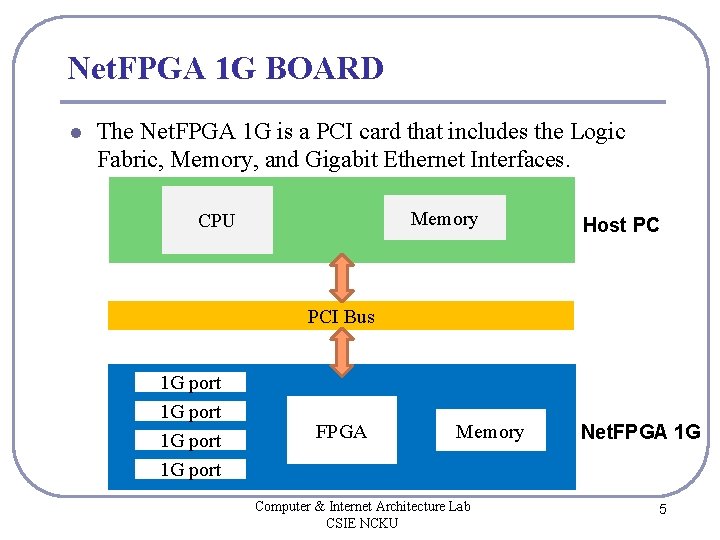

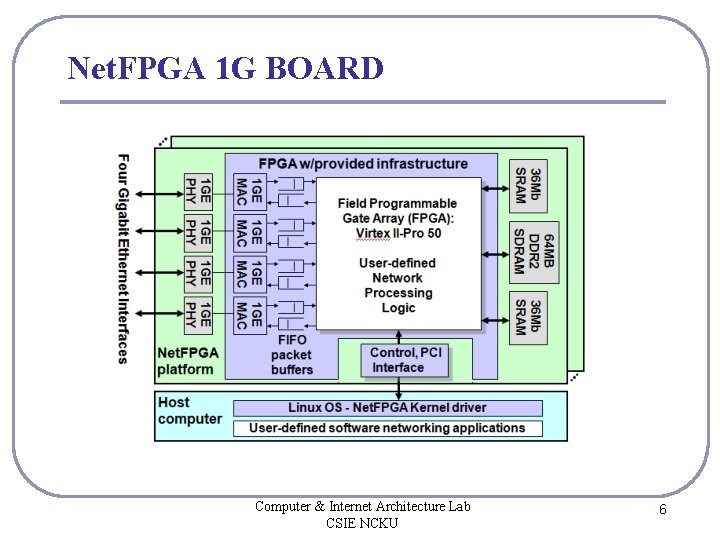

Net. FPGA 1 G BOARD l The Net. FPGA 1 G is a PCI card that includes the Logic Fabric, Memory, and Gigabit Ethernet Interfaces. Memory CPU Host PC PCI Bus 1 G port FPGA Memory Computer & Internet Architecture Lab CSIE NCKU Net. FPGA 1 G 5

Net. FPGA 1 G BOARD Computer & Internet Architecture Lab CSIE NCKU 6

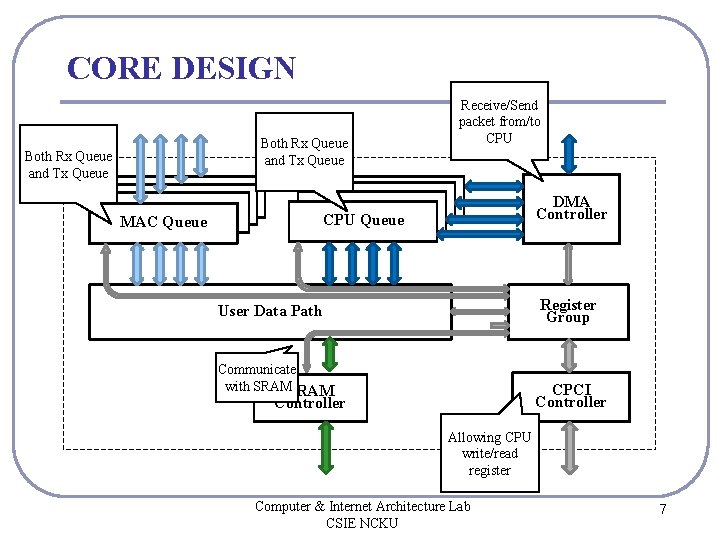

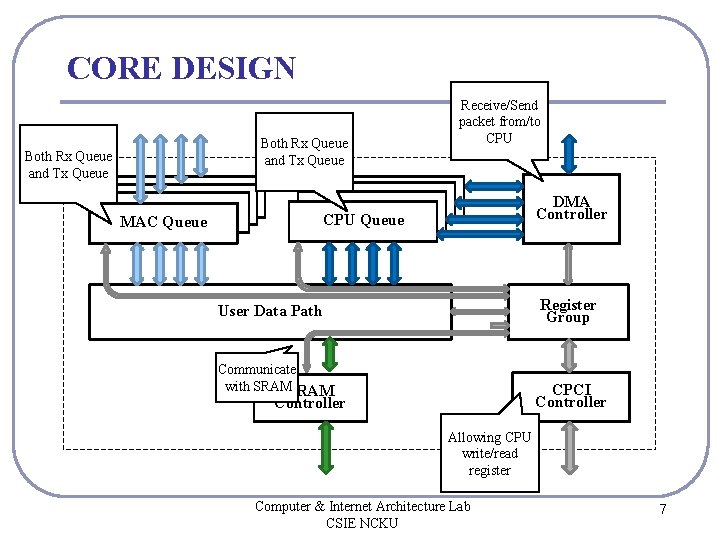

CORE DESIGN Both Rx Queue and Tx Queue Receive/Send packet from/to CPUQueues CPU Queue MACQueues MAC Queue DMA Controller Register Group User Data Path Communicate with SRAM CPCI Controller Allowing CPU write/read register Computer & Internet Architecture Lab CSIE NCKU 7

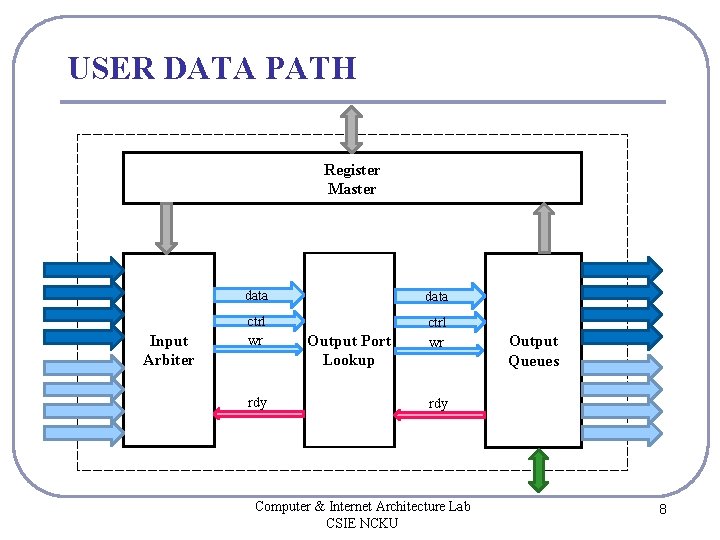

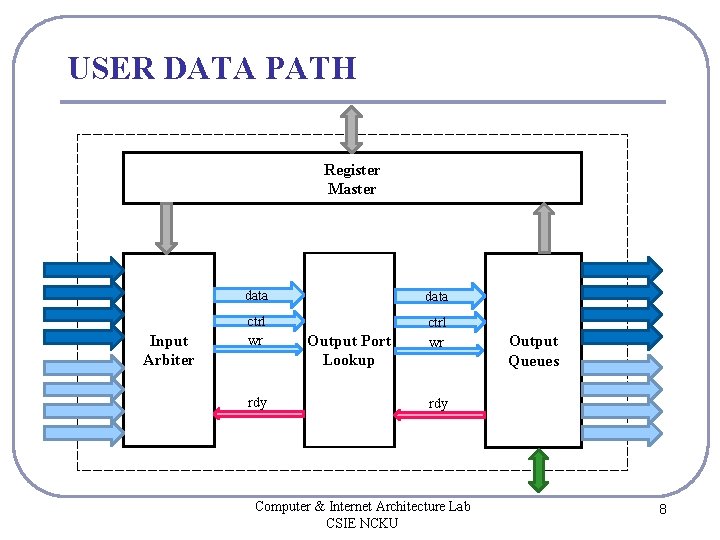

USER DATA PATH Register Master Input Arbiter data ctrl wr rdy Output Port Lookup Output Queues rdy Computer & Internet Architecture Lab CSIE NCKU 8

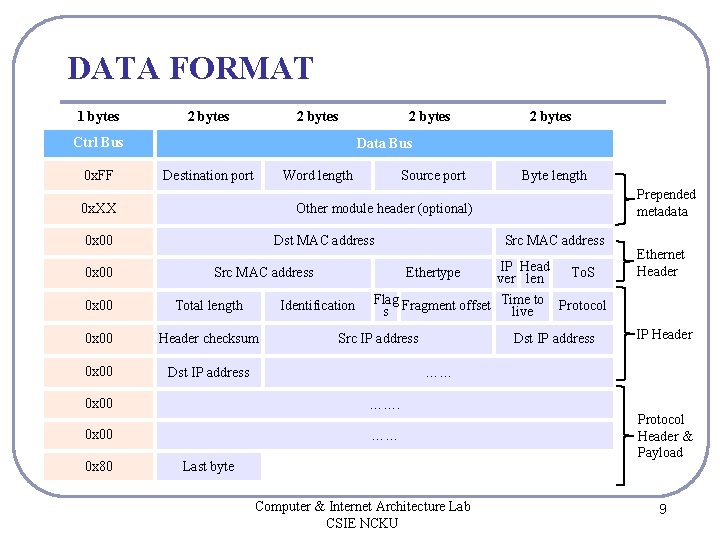

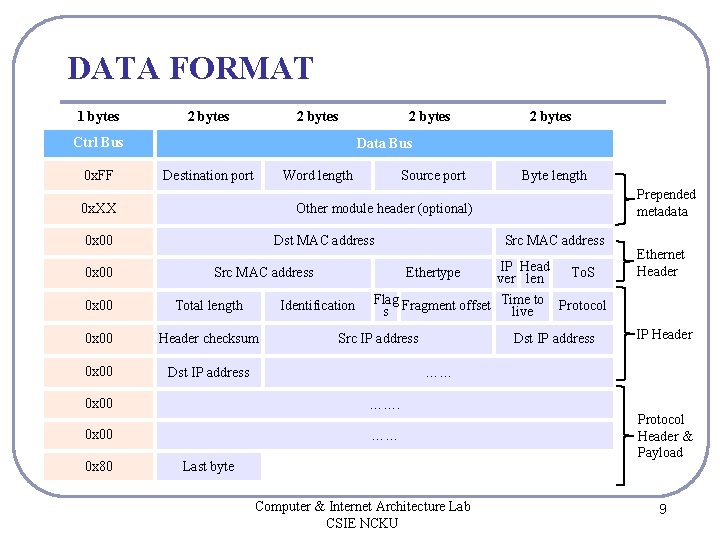

DATA FORMAT 1 bytes 2 bytes Ctrl Bus 0 x. FF Word length Destination port Source port Byte length Prepended metadata Other module header (optional) 0 x 00 Dst MAC address Src MAC address 0 x 00 Total length 0 x 00 Header checksum 0 x 00 Dst IP address Identification IP Head ver len To. S Ethernet Header Flag Fragment offset Time to Protocol s live Src IP address Dst IP address IP Header …… ……. 0 x 00 …… Last byte Src MAC address Ethertype 0 x 00 0 x 80 2 bytes Data Bus 0 x. XX 0 x 00 2 bytes Computer & Internet Architecture Lab CSIE NCKU Protocol Header & Payload 9

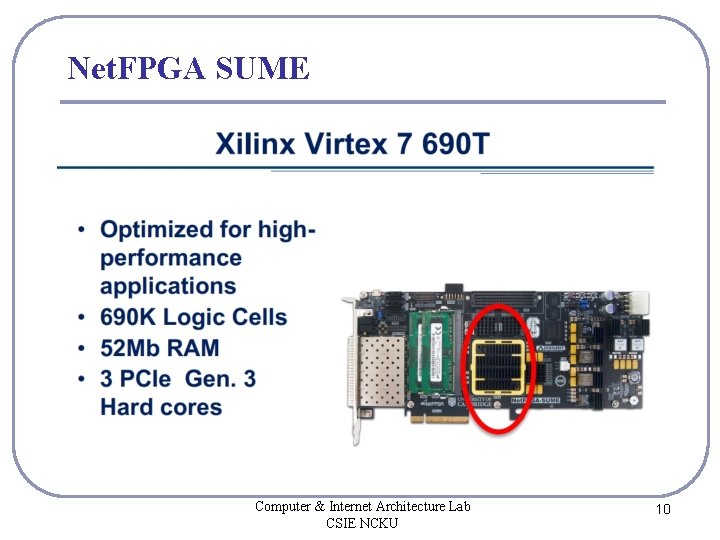

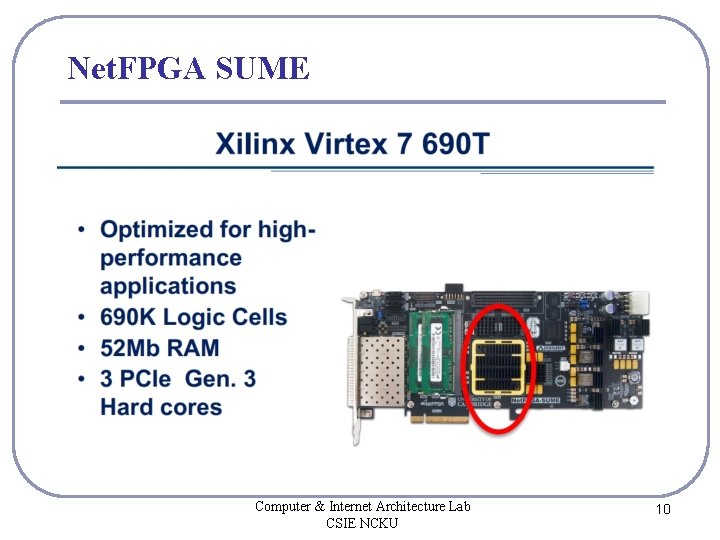

Net. FPGA SUME Computer & Internet Architecture Lab CSIE NCKU 10

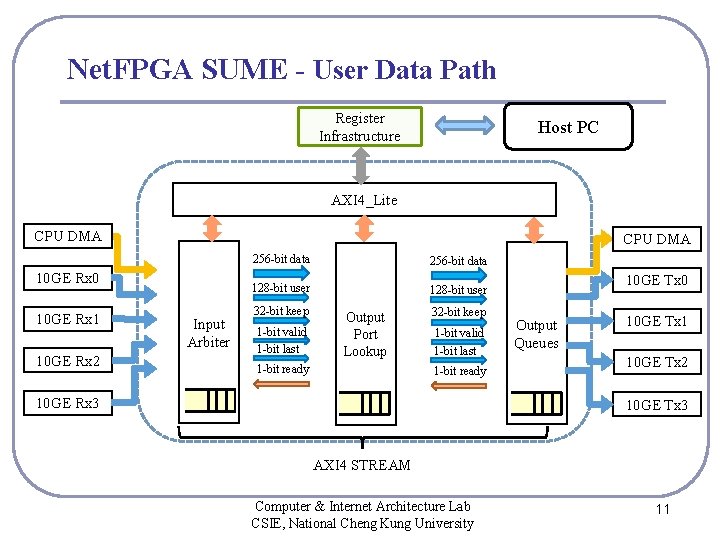

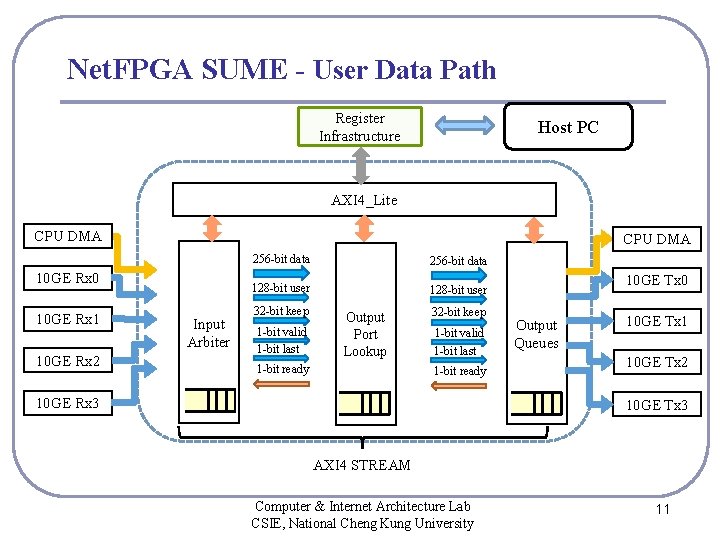

Net. FPGA SUME - User Data Path Register Infrastructure Host PC AXI 4_Lite CPU DMA 10 GE Rx 0 10 GE Rx 1 10 GE Rx 2 Input Arbiter 256 -bit data 128 -bit user 32 -bit keep 1 -bit valid 1 -bit last Output Port Lookup 1 -bit ready 32 -bit keep 1 -bit valid 1 -bit last 1 -bit ready 10 GE Rx 3 10 GE Tx 0 Output Queues 10 GE Tx 1 10 GE Tx 2 10 GE Tx 3 AXI 4 STREAM Computer & Internet Architecture Lab CSIE, National Cheng Kung University 11

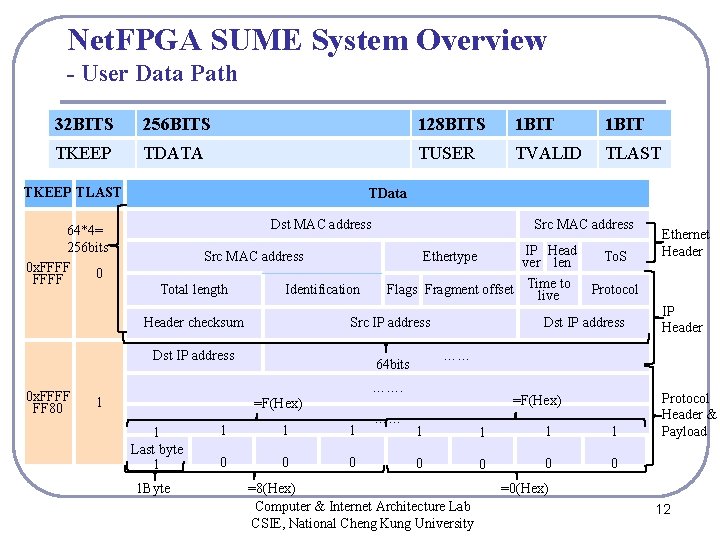

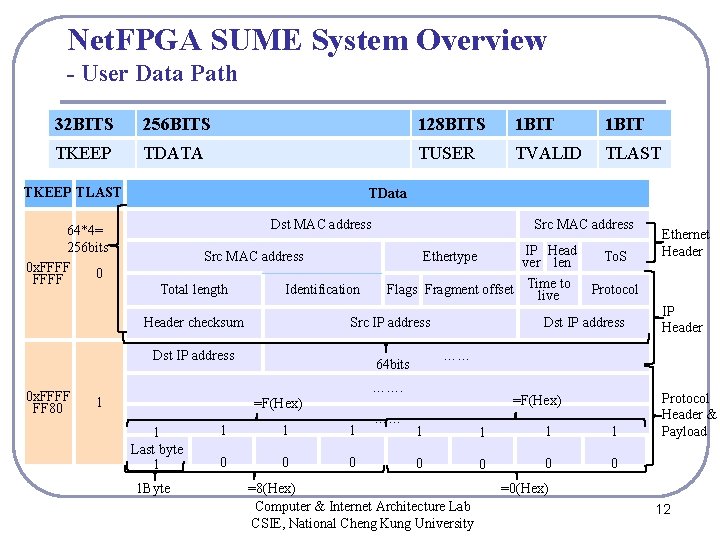

Net. FPGA SUME System Overview - User Data Path 32 BITS 256 BITS 128 BITS 1 BIT TKEEP TDATA TUSER TVALID TLAST TKEEP TLAST 64*4= 256 bits 0 x. FFFF 0 FFFF TData Dst MAC address Src MAC address Total length 1 Byte 1 1 0 0 0 …… To. S Protocol IP Header Dst IP address ……. 1 Ethernet Header …… 64 bits =F(Hex) 1 Last byte 1 Flags Fragment offset Time to live Src IP address Dst IP address 1 IP Head ver len Ethertype Identification Header checksum 0 x. FFFF FF 80 Src MAC address Protocol Header & Payload =F(Hex) 1 0 =8(Hex) Computer & Internet Architecture Lab CSIE, National Cheng Kung University 1 1 0 0 1 0 =0(Hex) 12

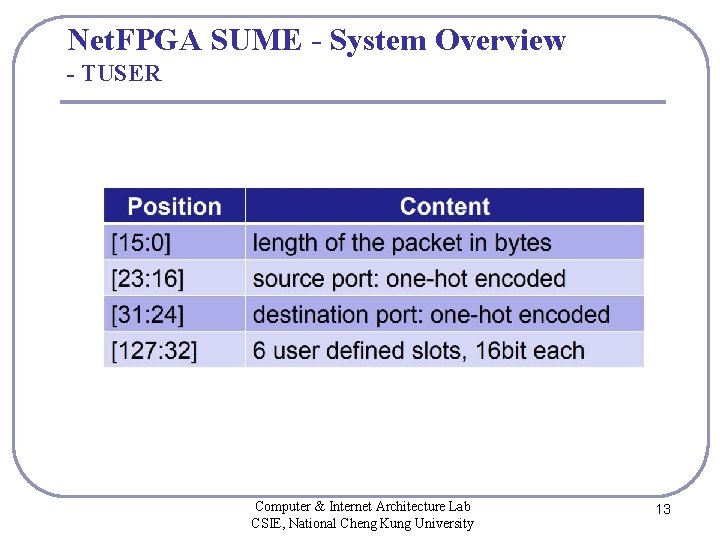

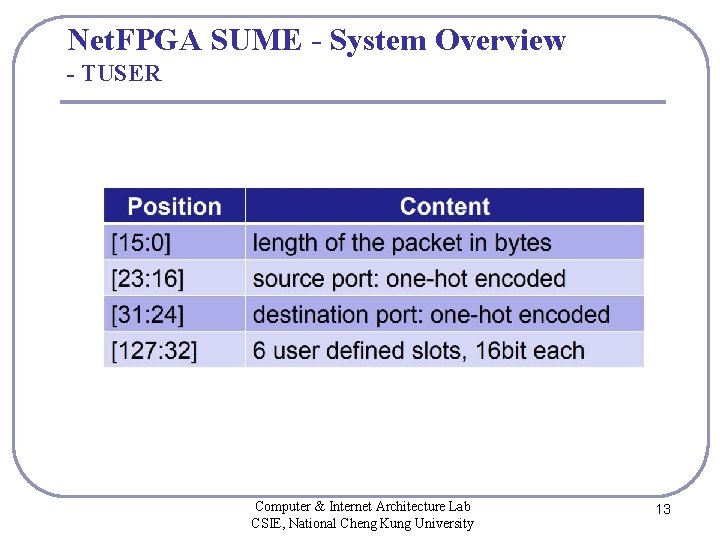

Net. FPGA SUME - System Overview - TUSER Computer & Internet Architecture Lab CSIE, National Cheng Kung University 13

OUTPUT PORT LOOKUP pre_process_ control ip_lpm ip_arp dest_ip_filter ip_checksum_ttl eth_parser op_lut_process_sm op_lut_hdr_parser router_op_lut_regs fallthrough_small_fifo Computer & Internet Architecture Lab CSIE NCKU 14

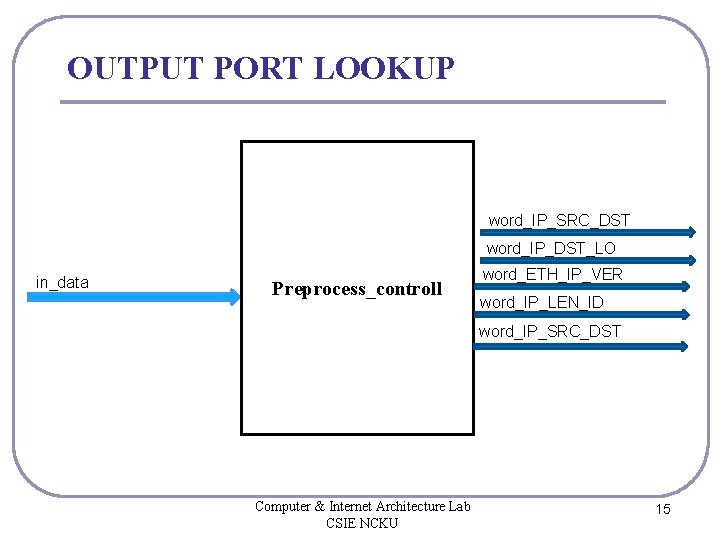

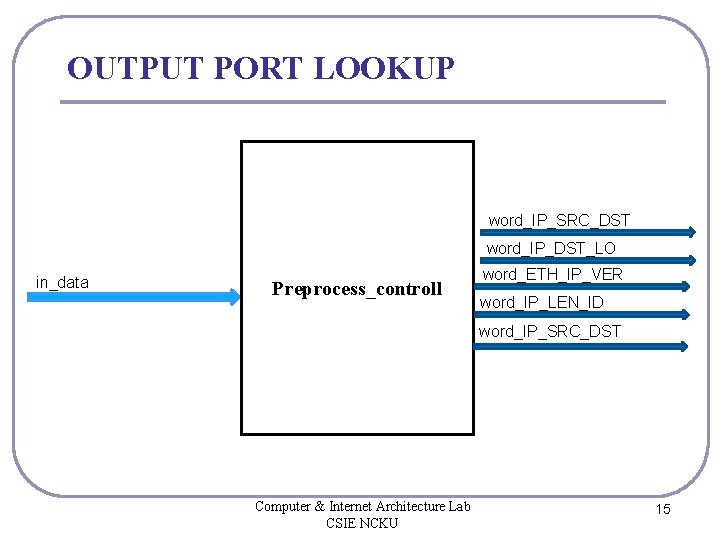

OUTPUT PORT LOOKUP word_IP_SRC_DST word_IP_DST_LO in_data Preprocess_controll word_ETH_IP_VER word_IP_LEN_ID word_IP_SRC_DST Computer & Internet Architecture Lab CSIE NCKU 15

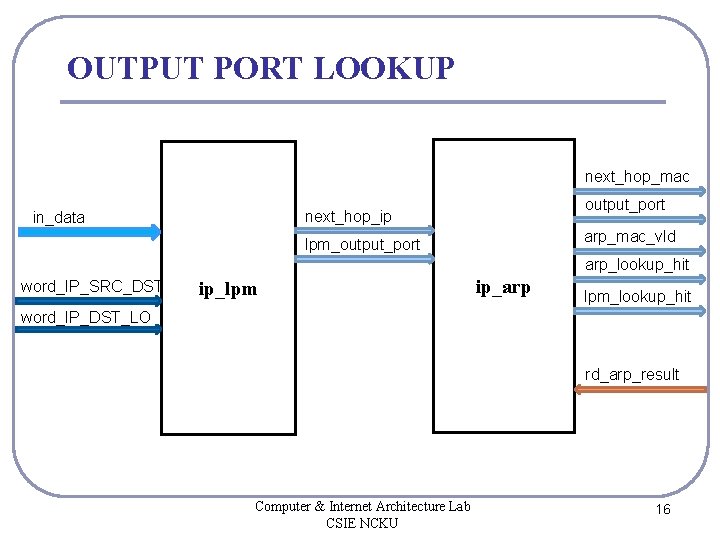

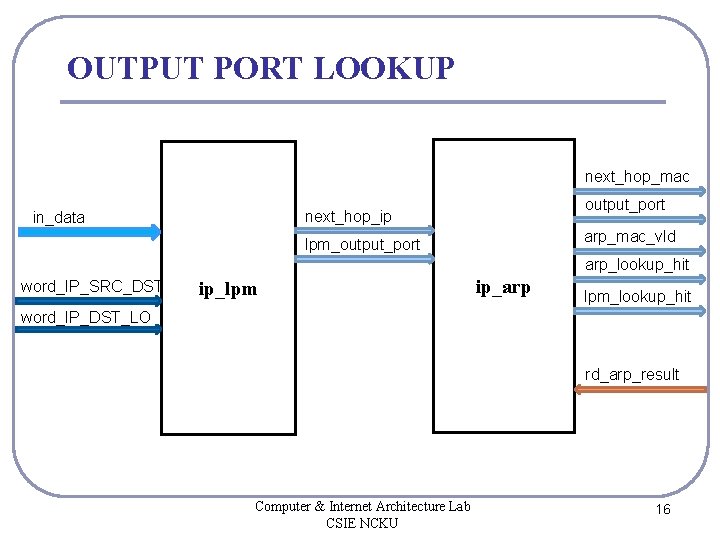

OUTPUT PORT LOOKUP next_hop_mac output_port next_hop_ip in_data arp_mac_vld lpm_output_port arp_lookup_hit word_IP_SRC_DST ip_lpm ip_arp lpm_lookup_hit word_IP_DST_LO rd_arp_result Computer & Internet Architecture Lab CSIE NCKU 16

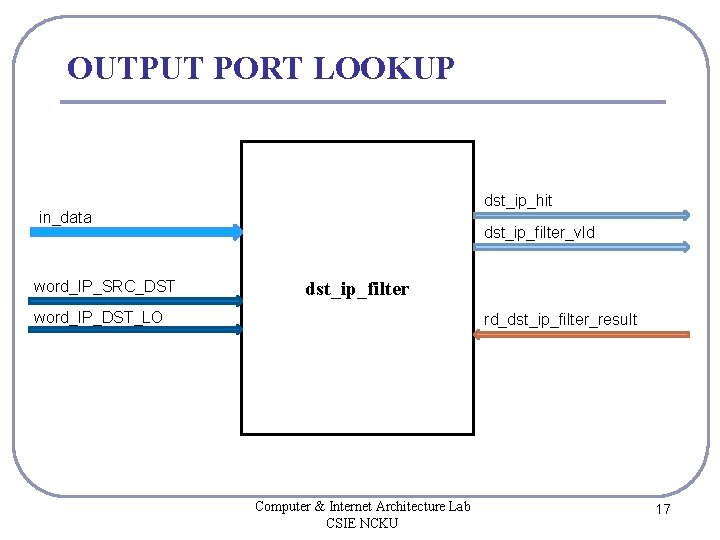

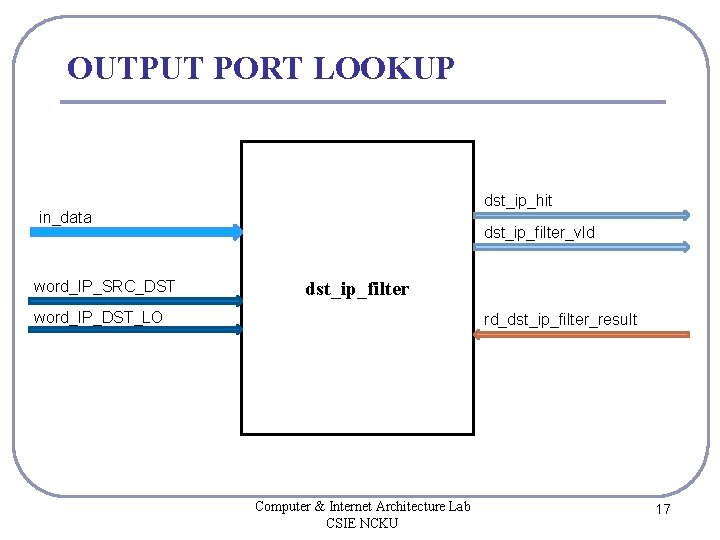

OUTPUT PORT LOOKUP dst_ip_hit in_data word_IP_SRC_DST dst_ip_filter_vld dst_ip_filter word_IP_DST_LO rd_dst_ip_filter_result Computer & Internet Architecture Lab CSIE NCKU 17

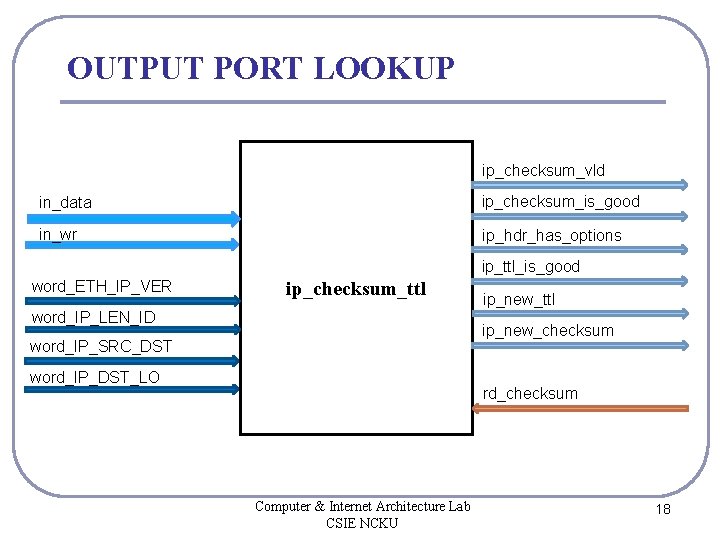

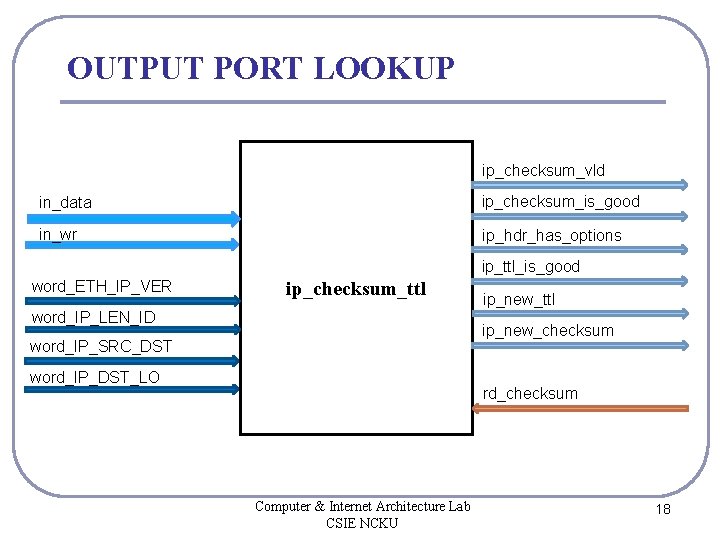

OUTPUT PORT LOOKUP ip_checksum_vld in_data ip_checksum_is_good in_wr ip_hdr_has_options ip_ttl_is_good word_ETH_IP_VER ip_checksum_ttl word_IP_LEN_ID ip_new_ttl ip_new_checksum word_IP_SRC_DST word_IP_DST_LO rd_checksum Computer & Internet Architecture Lab CSIE NCKU 18

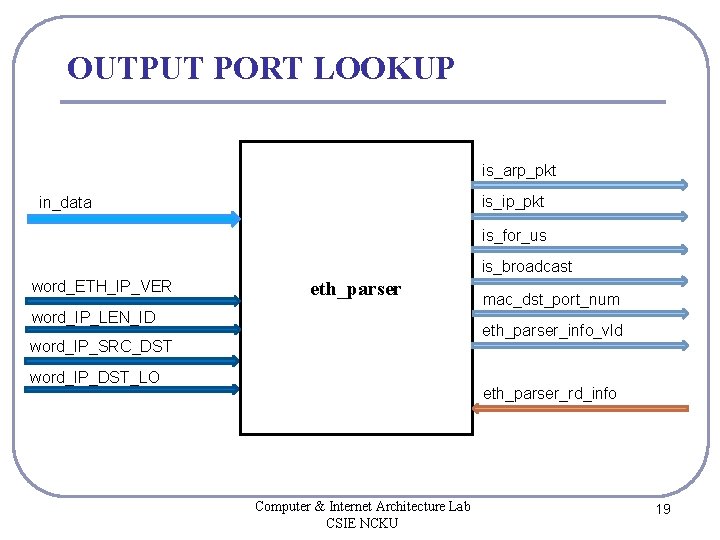

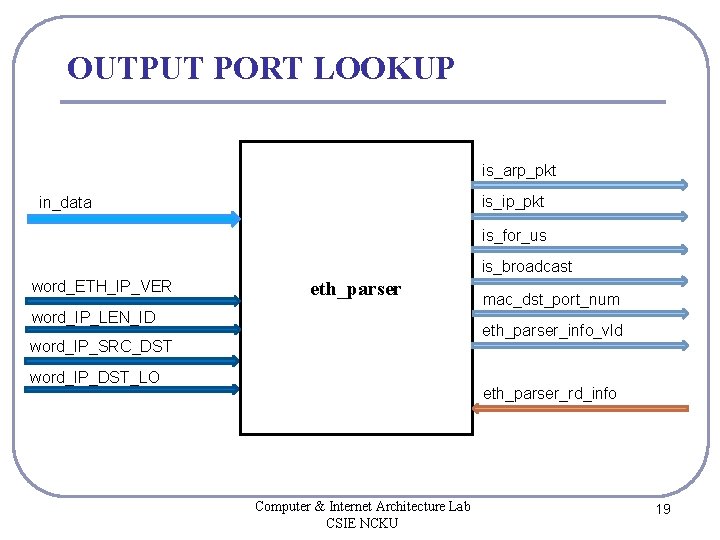

OUTPUT PORT LOOKUP is_arp_pkt is_ip_pkt in_data is_for_us is_broadcast word_ETH_IP_VER eth_parser word_IP_LEN_ID mac_dst_port_num eth_parser_info_vld word_IP_SRC_DST word_IP_DST_LO eth_parser_rd_info Computer & Internet Architecture Lab CSIE NCKU 19

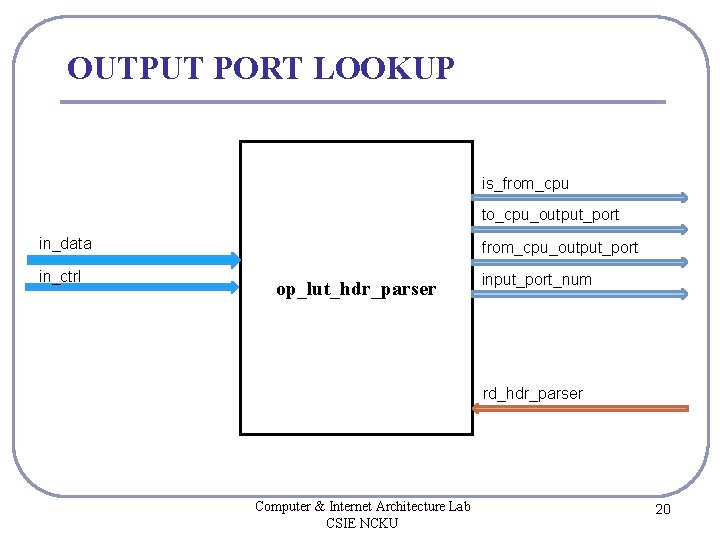

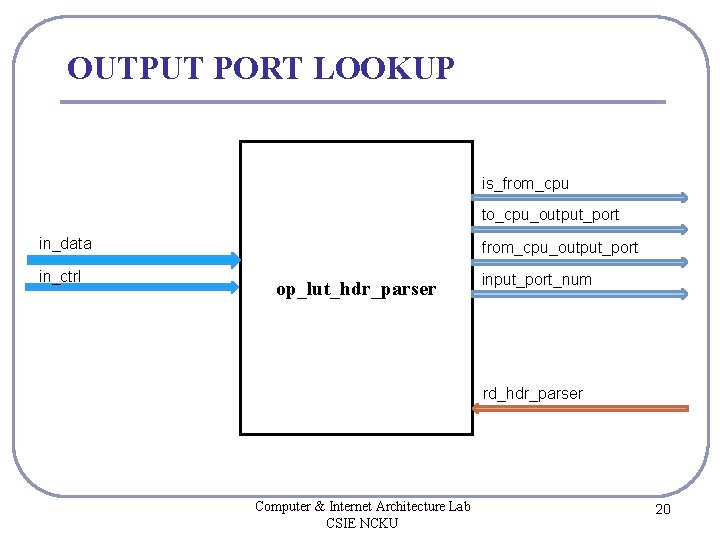

OUTPUT PORT LOOKUP is_from_cpu to_cpu_output_port in_data in_ctrl from_cpu_output_port op_lut_hdr_parser input_port_num rd_hdr_parser Computer & Internet Architecture Lab CSIE NCKU 20

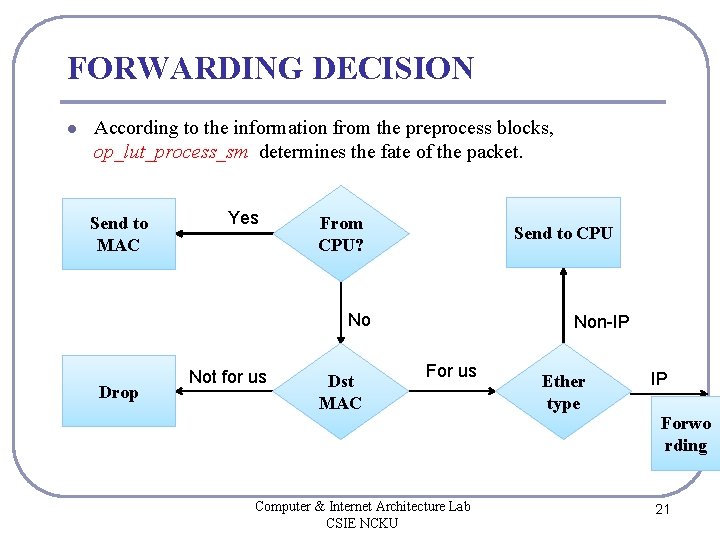

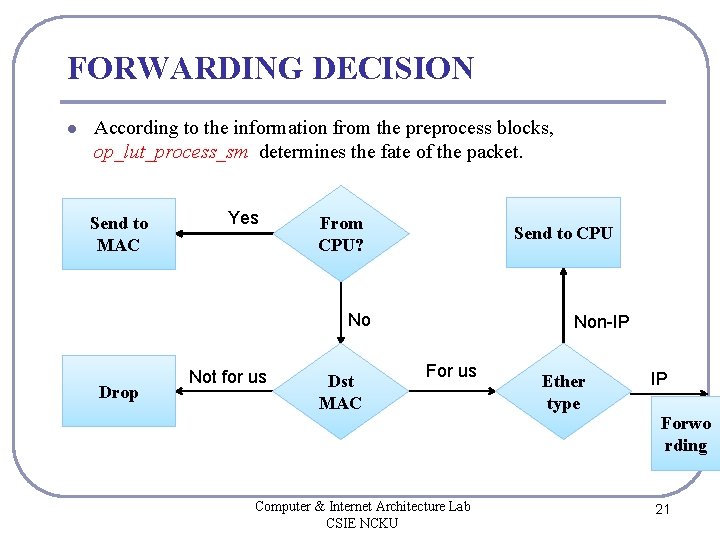

FORWARDING DECISION l According to the information from the preprocess blocks, op_lut_process_sm determines the fate of the packet. Send to MAC Yes From CPU? Send to CPU No Drop Not for us Dst MAC Non-IP For us Ether type IP Forwo rding Computer & Internet Architecture Lab CSIE NCKU 21

FORWARDING DECISION IP IP checksum correct? No Drop Send to MAC Yes Send to CPU Filter table hit? Yes No No Broadcast Drop Ver ==4? TTL > 1? Routing table hit? ARP table hit? Computer & Internet Architecture Lab CSIE NCKU Dec TTL Update IP checksum Set Dst MAC Set Src MAC Yes 22

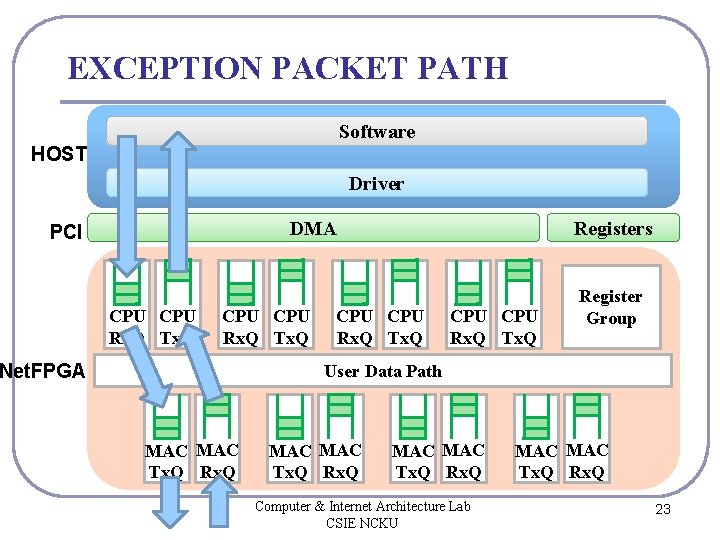

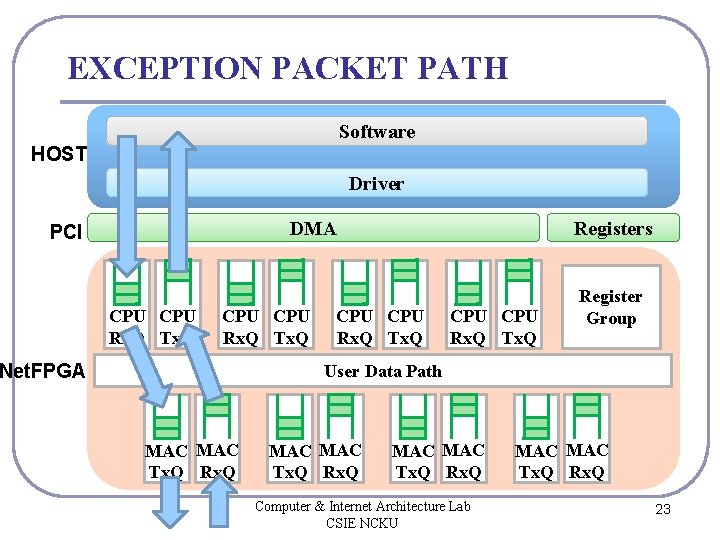

EXCEPTION PACKET PATH Software HOST Driver DMA PCI CPU CPU Rx. Q Tx. Q Net. FPGA Registers CPU CPU Rx. Q Tx. Q Register Group User Data Path MAC MAC Tx. Q Rx. Q Computer & Internet Architecture Lab CSIE NCKU MAC Tx. Q Rx. Q 23

![REFERNCE l l 1https github comNet FPGAnetfpgawikiReleases 2http netfpga org 3http www cl cam REFERNCE l l [1]https: //github. com/Net. FPGA/netfpga/wiki/Releases [2]http: //netfpga. org/ [3]http: //www. cl. cam.](https://slidetodoc.com/presentation_image_h/1b14030f9b09a5c32d55d2eb2026bf43/image-24.jpg)

REFERNCE l l [1]https: //github. com/Net. FPGA/netfpga/wiki/Releases [2]http: //netfpga. org/ [3]http: //www. cl. cam. ac. uk/research/srg/netos/projects/net fpga/workshop/cambridge-september 2011/2011_Net. FPGA_Day_tutorial_Cambridge. pdf [4]https: //www. cl. cam. ac. uk/research/srg/netos/projects/n etfpga/workshop/summer-school-2017/ Computer & Internet Architecture Lab CSIE NCKU 24