Reconfigurable Scalable Computing for Space Applications Dr Robert

Reconfigurable Scalable Computing for Space Applications Dr. Robert F. Hodson Chief Engineer Electronic Systems Branch NASA Langley Research Center Explore. Discover. Understand.

Agenda • • • What is RSC? RSC Team RSC Design Approach RSC Architecture Issues/Concerns, etc Questions Explore. Discover. Understand.

What is RSC? • A comprehensive Reconfigurable Scalable Computing (RSC) platform for space applications – Rad-Hard HW – System Software – Development tools Explore. Discover. Understand.

RSC Team • Core Team Members – NASA Langley Research Center (Lead) – NASA Goddard Space Flight Center – The University of Queensland – Sigma Space – Jefferson Lab (Do. E) – Starbridge Systems – Department of Defense • Affiliate Members – Air Force Research Laboratory – SEAKR Engineering – Imagination Engines Explore. Discover. Understand.

RSC Design Approach • Provide a comprehensive rad-hard RC solution • Leverage commercial hardware and software – Form factor (PCI-104/SPACE-104) – Operating System (u. CLinux) – Development Tools (gnu, Viva, MPI, XTMR, VHDL, etc) • Provide Fault-tolerant transparency to end-users • Provide a scalable architecture to support a broad application space • Provide and extensible solution the can transcend initial project goals and objectives Explore. Discover. Understand.

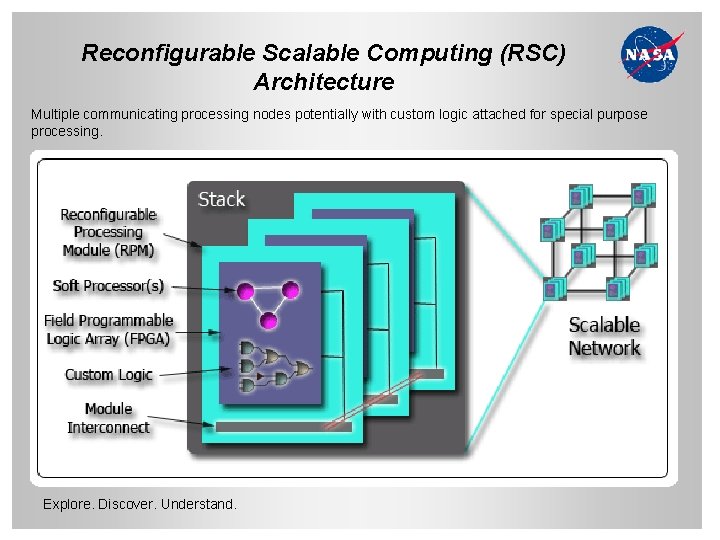

Reconfigurable Scalable Computing (RSC) Architecture Multiple communicating processing nodes potentially with custom logic attached for special purpose processing. Explore. Discover. Understand.

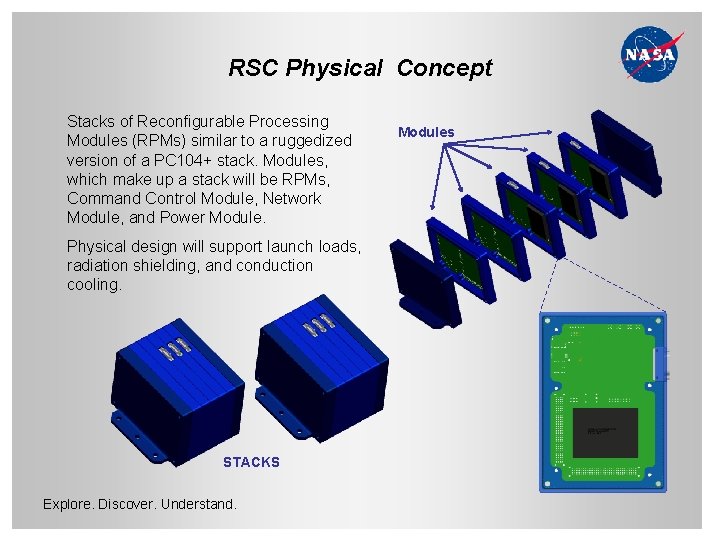

RSC Physical Concept Stacks of Reconfigurable Processing Modules (RPMs) similar to a ruggedized version of a PC 104+ stack. Modules, which make up a stack will be RPMs, Command Control Module, Network Module, and Power Module. Physical design will support launch loads, radiation shielding, and conduction cooling. STACKS Explore. Discover. Understand. Modules

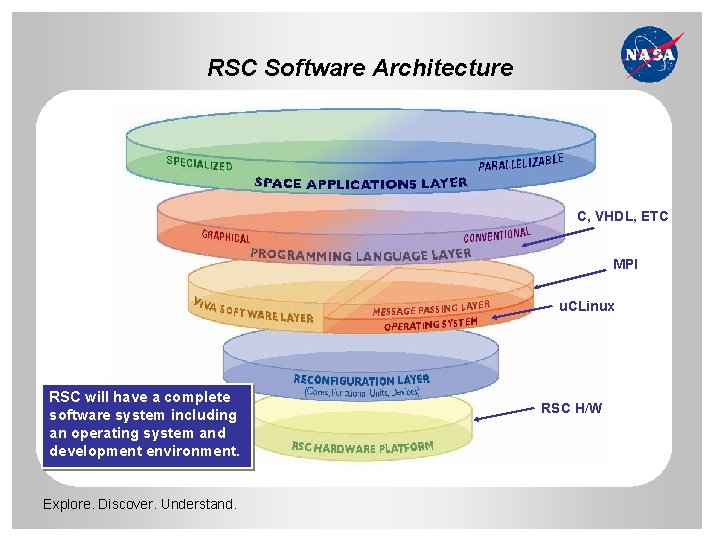

RSC Software Architecture C, VHDL, ETC MPI u. CLinux RSC will have a complete software system including an operating system and development environment. Explore. Discover. Understand. RSC H/W

Reconfigurable Processing Module TMR Logic Detect & Invalidate Application FPGA LMBs Data Cache INTC I-side Micro. Blaze Processor D-side Custom IP Core Other Devices OPB 2 W Bridge Bus A Arbiter Resource FPGA Wishbone Bus A Shielded, screened SDRAM NIC So. H Scrubber EDAC Wishbone Bus A Memory Interface NVMEM I/F S DRA M NV RA M Explore. Discover. Understand. EDAC or TMR HS I/F Onboard Peripheral Bus FSL TMR Timers Wishbone A-to-B Bridge DMA Engine CRAM or Other Configuration scrubbing Config Memory Config Manager Wishbone Bus B PCI Bridge SERDES Instr Cache RPP, Rad. Hard ASIC Bus B Arbiter Parameter LUT PCI Bus 33 MHz/32 or 64 bit Rad-Hard by design

RPM Prototype Board Explore. Discover. Understand.

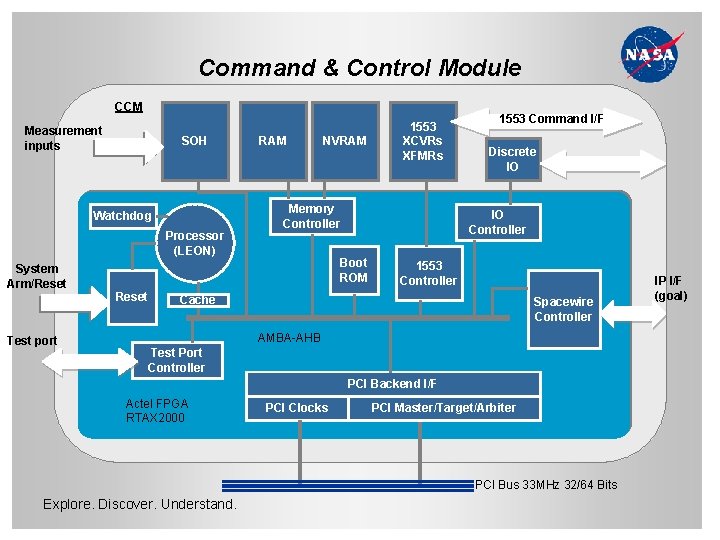

Command & Control Module CCM Measurement inputs SOH Watchdog Processor (LEON) RAM NVRAM Memory Controller Test port 1553 Command I/F Discrete IO IO Controller Boot ROM System Arm/Reset 1553 XCVRs XFMRs 1553 Controller Cache Spacewire Controller AMBA-AHB Test Port Controller PCI Backend I/F Actel FPGA RTAX 2000 PCI Clocks PCI Master/Target/Arbiter PCI Bus 33 MHz 32/64 Bits Explore. Discover. Understand. IP I/F (goal)

Network Module Design To/from other stacks SERDES Link I/F Routing Lookup Additional Link I/Fs Control From Link Interfaces To Other Link Interfaces From Link Interfaces Routing Lookup Actel AX 2000 PCI I/F Explore. Discover. Understand. Control DMA Network Module (NM) provides an interface to other RSC stacks. It buffers and routes IP packets based on routing information loaded during system initialization. Serialized links provide a high-bandwidth interconnect to other systems.

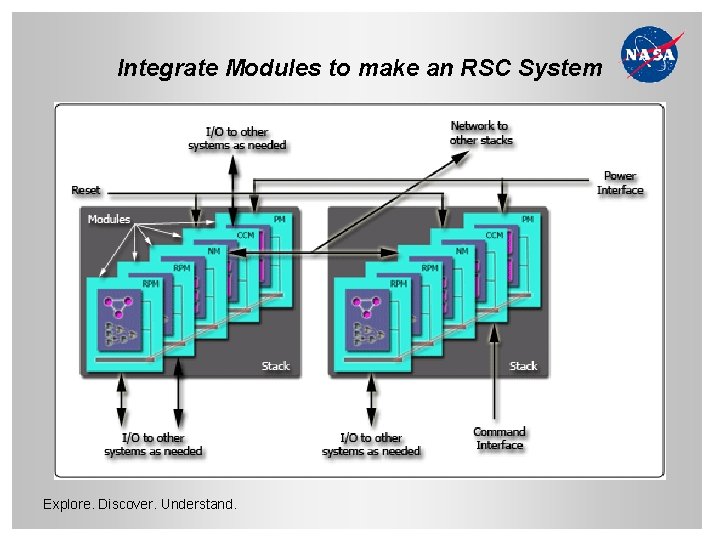

Integrate Modules to make an RSC System Explore. Discover. Understand.

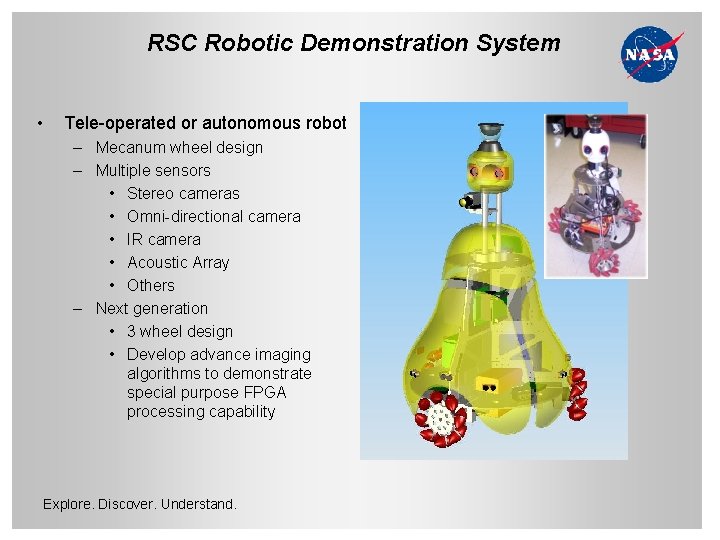

RSC Robotic Demonstration System • Tele-operated or autonomous robot – Mecanum wheel design – Multiple sensors • Stereo cameras • Omni-directional camera • IR camera • Acoustic Array • Others – Next generation • 3 wheel design • Develop advance imaging algorithms to demonstrate special purpose FPGA processing capability Explore. Discover. Understand.

Issues/Concerns/Questions/Desires • • • • Access to u. Blaze Cache code or hardened cache design XTMR version not in-synch with other tools (EDK, ISE) No Bi-Directional IO with using TMR Pin need to be tied at the board, can there be an internal package tie or other method? Has tri-state voting been qualified? Reliability? Design w/o clock enable control (all or nothing) Testing issue – need high scrub rates to prevent configuration MBUs while testing Soft DCMs, no automatic failure recovery Soft Rocket. IO Soft Power. PCs, can we at least have 3 with separate clock domains Single documented source of SEFI with some cross-section/error rate info (Reset, Select Map, JTAG, etc) Other rad-hard support devices (NVRAM, PROMs, POL Converters) The Holy Grail - Holistic well documented design tools and approach for applications Explore. Discover. Understand.

Backup Explore. Discover. Understand.

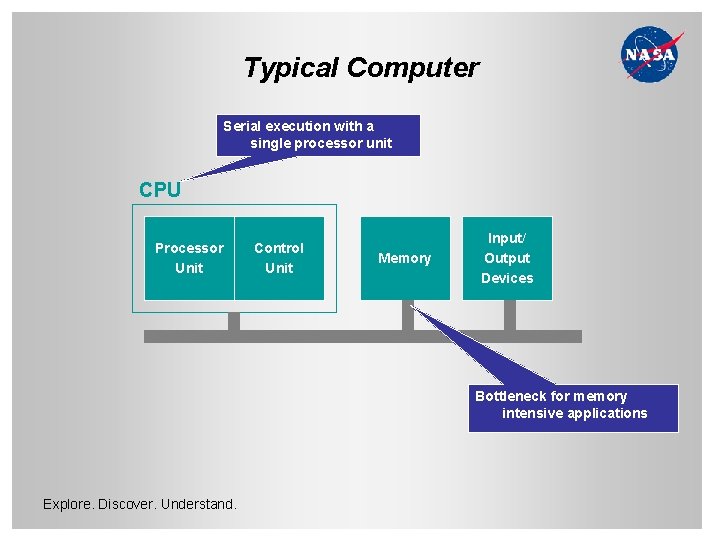

Typical Computer Serial execution with a single processor unit CPU Processor Unit Control Unit Memory Input/ Output Devices Bottleneck for memory intensive applications Explore. Discover. Understand.

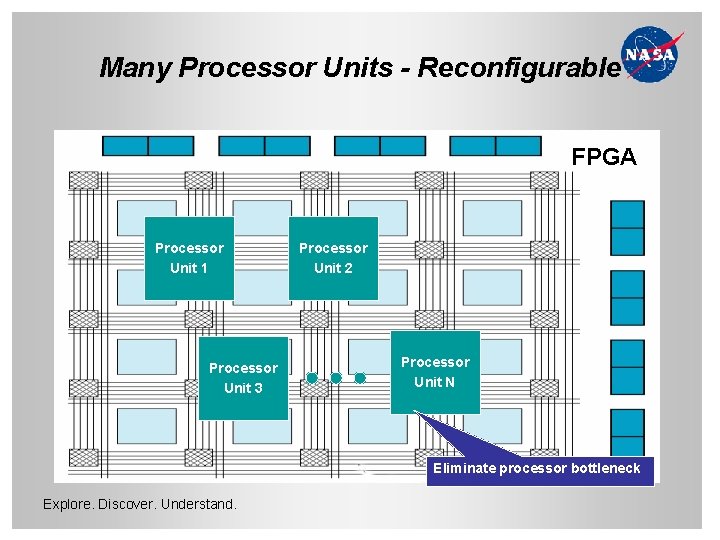

Many Processor Units - Reconfigurable FPGA Processor Unit 1 Processor Unit 3 Processor Unit 2 Processor Unit N Eliminate processor bottleneck Explore. Discover. Understand.

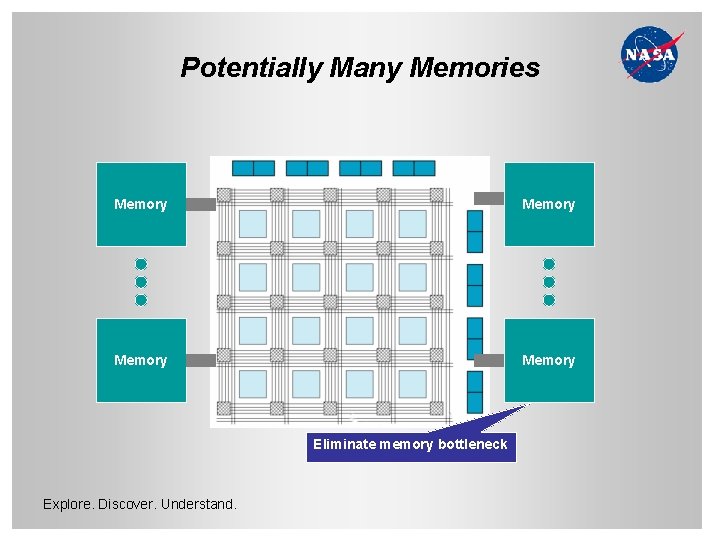

Potentially Many Memories Memory Eliminate memory bottleneck Explore. Discover. Understand.

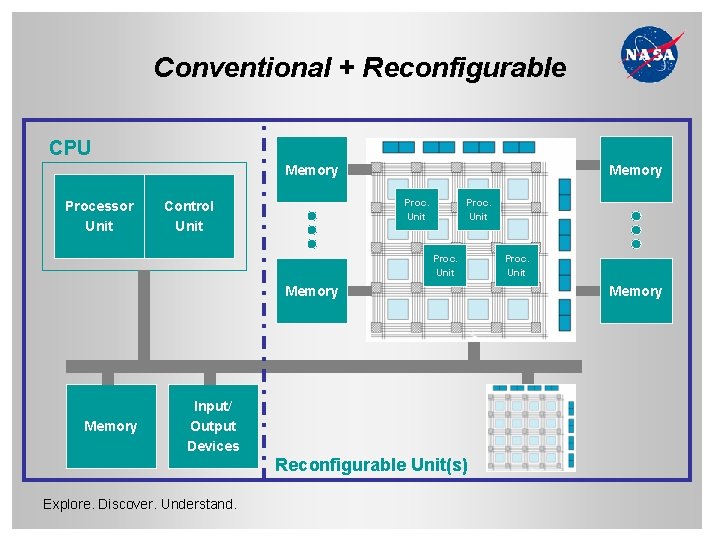

Conventional + Reconfigurable CPU Memory Processor Unit Memory Proc. Unit Control Unit Proc. Unit Memory Input/ Output Devices Reconfigurable Unit(s) Explore. Discover. Understand. Proc. Unit Memory

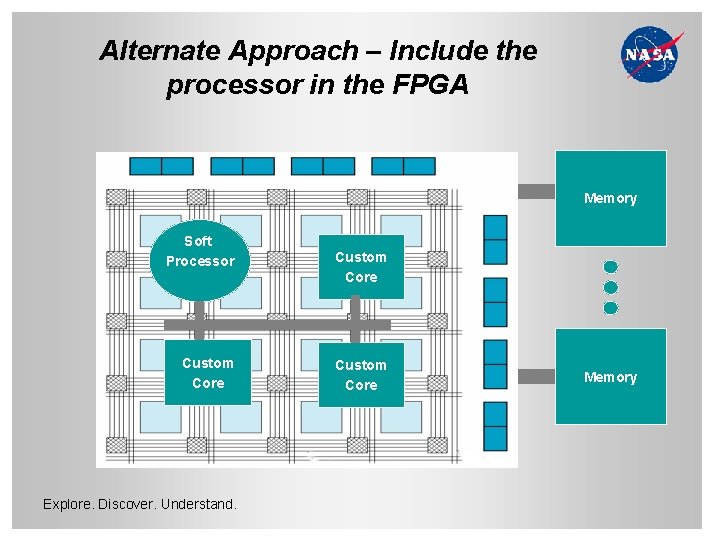

Alternate Approach – Include the processor in the FPGA Memory Soft Processor Custom Core Explore. Discover. Understand. Custom Core Memory

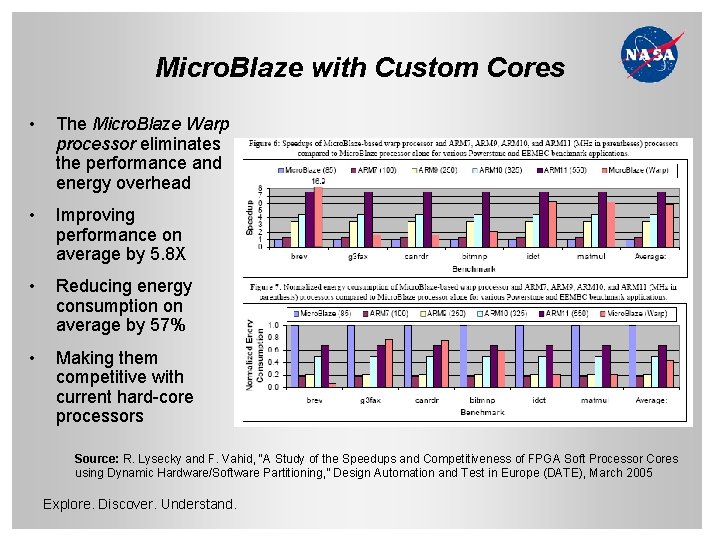

Micro. Blaze with Custom Cores • The Micro. Blaze Warp processor eliminates the performance and energy overhead • Improving performance on average by 5. 8 X • Reducing energy consumption on average by 57% • Making them competitive with current hard-core processors Source: R. Lysecky and F. Vahid, “A Study of the Speedups and Competitiveness of FPGA Soft Processor Cores using Dynamic Hardware/Software Partitioning, ” Design Automation and Test in Europe (DATE), March 2005 Explore. Discover. Understand.

Challenges for Space Avionics • Radiation Effects – SEE, TID • Launch Environment – Shock and Vibration • Thermal Environment – Surviving Extremes – Getting the Heat Out • Communications – Transmission Delay – Bandwidth • Mass • Power • Cost to Qualify for Space – It is a small marketplace Book by Simon Carter Explore. Discover. Understand.

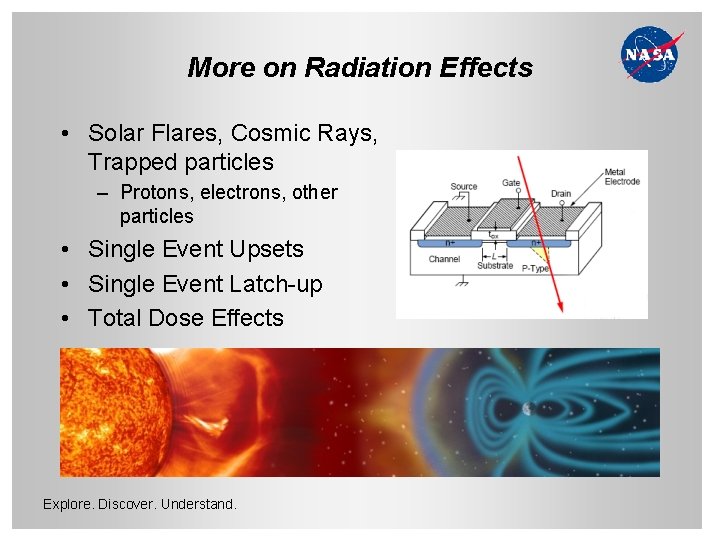

More on Radiation Effects • Solar Flares, Cosmic Rays, Trapped particles – Protons, electrons, other particles • Single Event Upsets • Single Event Latch-up • Total Dose Effects Explore. Discover. Understand.

Mitigation Strategies • • Microelectronic process enhancements Device/Cell level enhancements Error Detection and Correction Techniques Triple Modular Redundancy (@ various levels) Explore. Discover. Understand.

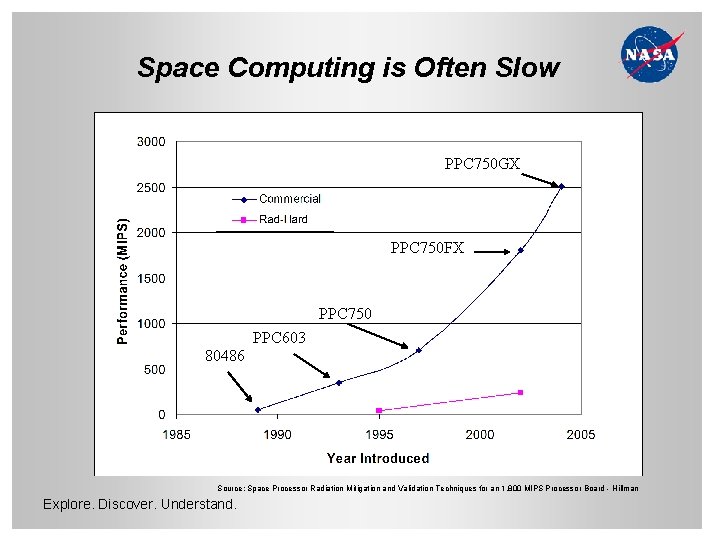

Space Computing is Often Slow PPC 750 GX PPC 750 FX PPC 750 PPC 603 80486 Source: Space Processor Radiation Mitigation and Validation Techniques for an 1, 800 MIPS Processor Board - Hillman Explore. Discover. Understand.

Other Approaches Leveraging COTS Power. PC 750 Functional Unit Power. PC 750 Requires Latchup/SEFI Mitigation Reset, Resync Voter Processors Compare Recompute if different No Latch-up (SOI) Approach by Maxwell Explore. Discover. Understand. Approach by Space Micro (TTMR™)

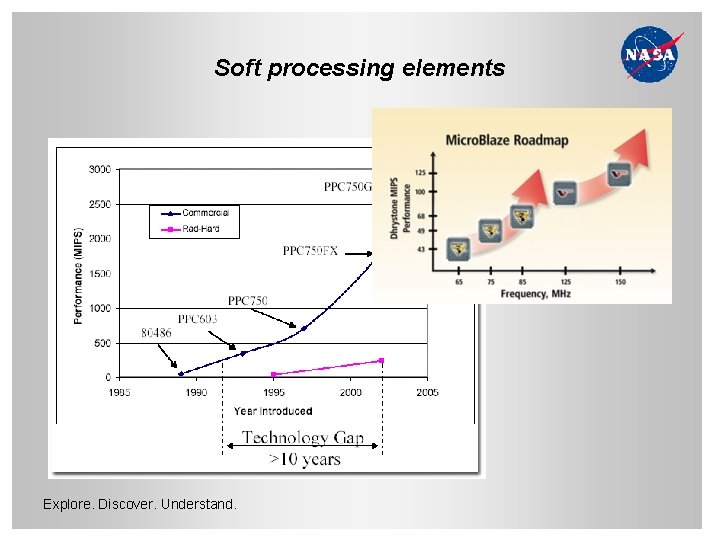

Soft processing elements Explore. Discover. Understand.

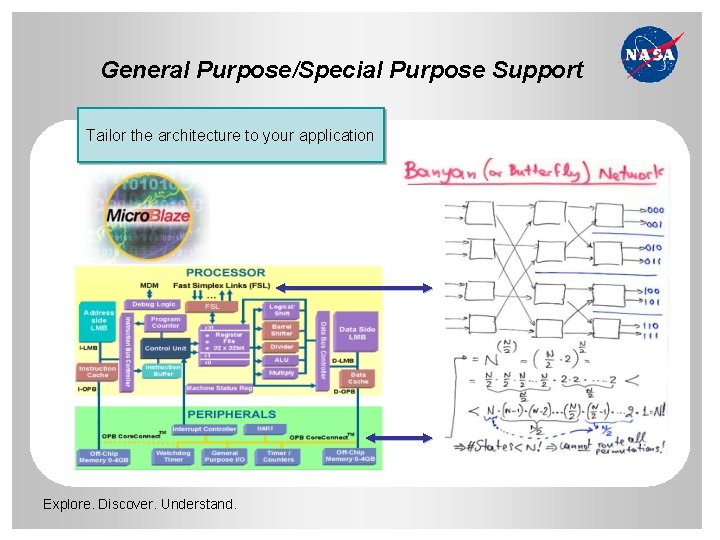

General Purpose/Special Purpose Support Tailor the architecture to your application Explore. Discover. Understand.

Application MPI Sockets message Transport UDP packet Network Internet Protocol datagrams Data Link and Physical Address and Size of Datagram and Sender Tag Communication Protocol INTR IP Sender Receiver Message PHdr Data NIC Send Request Buses Explore. Discover. Understand. IP DMA Engine Pull Address, Size, Tag Return ACK with Sender Tag PHdr Data NIC INTR

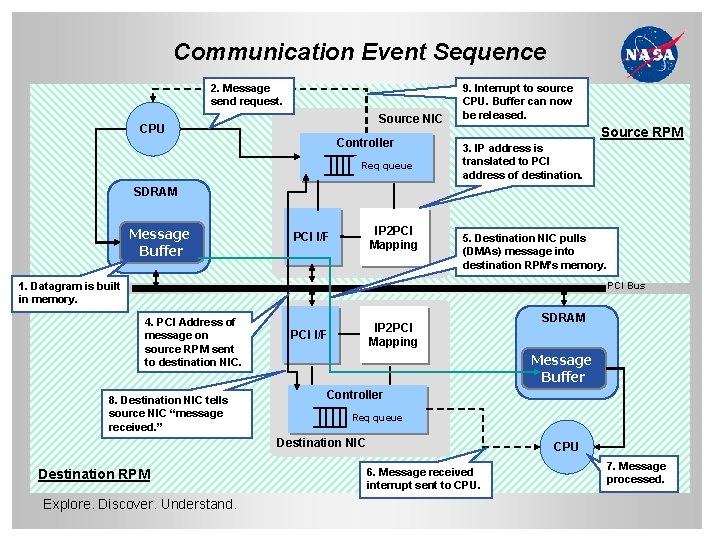

Communication Event Sequence 2. Message send request. Source NIC CPU Controller Req queue 9. Interrupt to source CPU. Buffer can now be released. Source RPM 3. IP address is translated to PCI address of destination. SDRAM Message Buffer IP 2 PCI Mapping PCI I/F 5. Destination NIC pulls (DMAs) message into destination RPM’s memory. PCI Bus 1. Datagram is built in memory. 4. PCI Address of message on source RPM sent to destination NIC. 8. Destination NIC tells source NIC “message received. ” IP 2 PCI Mapping PCI I/F Message Buffer Controller Req queue Destination NIC Destination RPM Explore. Discover. Understand. SDRAM CPU 6. Message received interrupt sent to CPU. 7. Message processed.

5/7/2006 SPACE-104 Small Form Factor Avionics Dr. Robert F. Hodson Electronic Systems Branch NASA Langley Research Center Robert. F. Hodson@NASA. gov [757] 864 -2326 Explore. Discover. Understand.

Introduction NASA Langley Research Center is developing for the Exploration Systems Mission Directorate, as part of the Reconfigurable Scalable Computing (RSC) project, a stackable form factor called SPACE-104. This form factor is designed for high performance and reduced mass/volume while meeting the harsh environmental requirements of space exploration. A project goal is to standardized SPACE-104. Therefore, the RSC project invites input from government agencies, industry, standards committees, and other organizations. Explore. Discover. Understand.

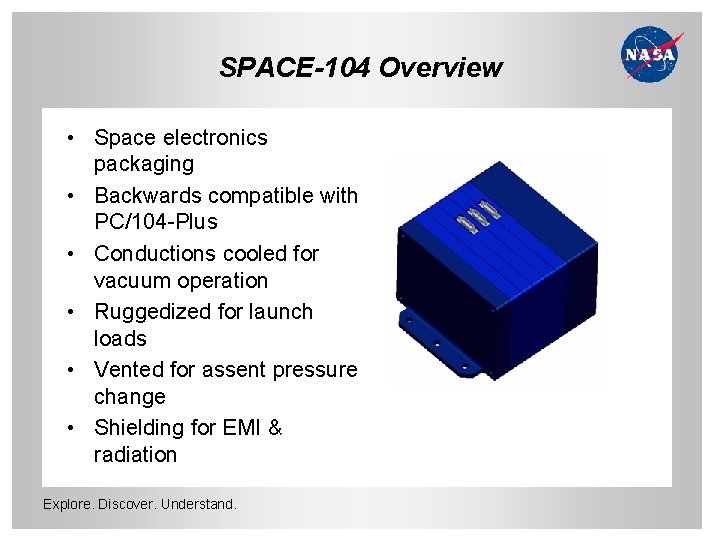

SPACE-104 Overview • Space electronics packaging • Backwards compatible with PC/104 -Plus • Conductions cooled for vacuum operation • Ruggedized for launch loads • Vented for assent pressure change • Shielding for EMI & radiation Explore. Discover. Understand.

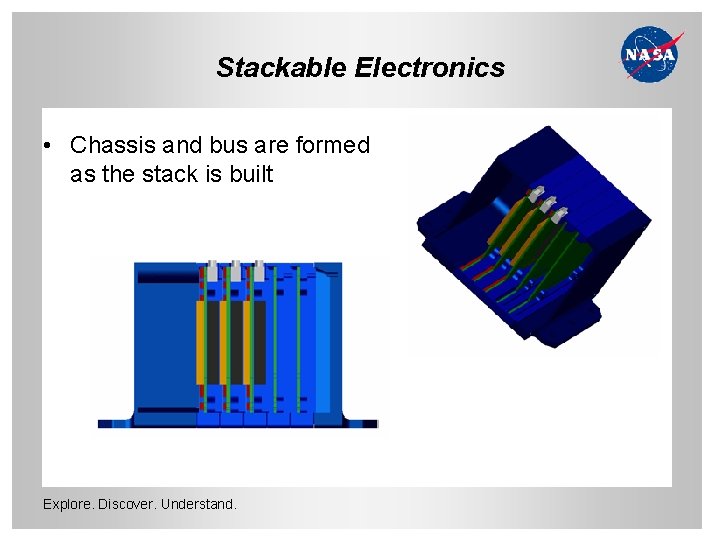

Stackable Electronics • Chassis and bus are formed as the stack is built Explore. Discover. Understand.

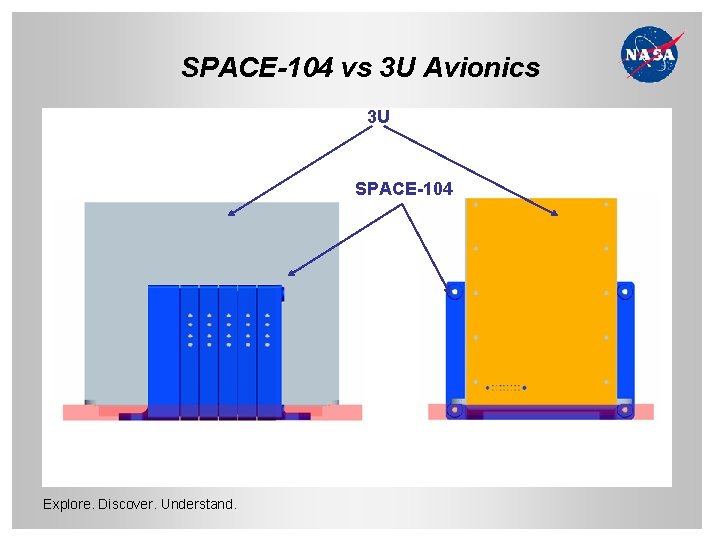

SPACE-104 vs 3 U Avionics 3 U SPACE-104 Explore. Discover. Understand.

Exploded View Circuit Modules Power Module Explore. Discover. Understand.

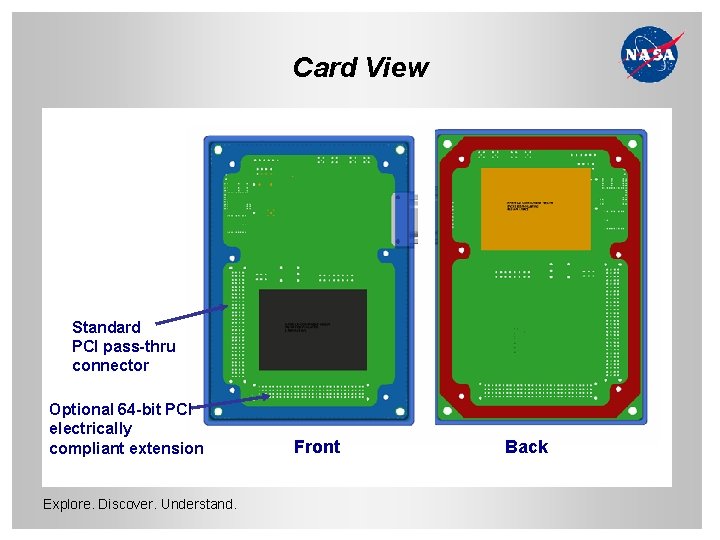

Card View Standard PCI pass-thru connector Optional 64 -bit PCI electrically compliant extension Explore. Discover. Understand. Front Back

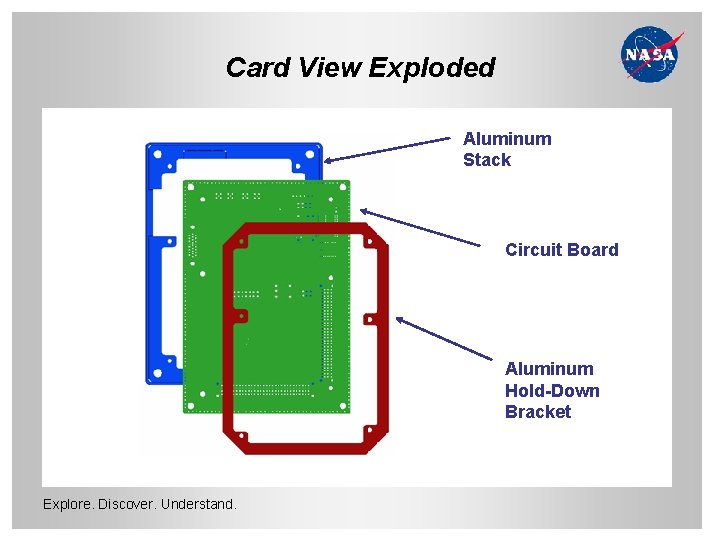

Card View Exploded Aluminum Stack Circuit Board Aluminum Hold-Down Bracket Explore. Discover. Understand.

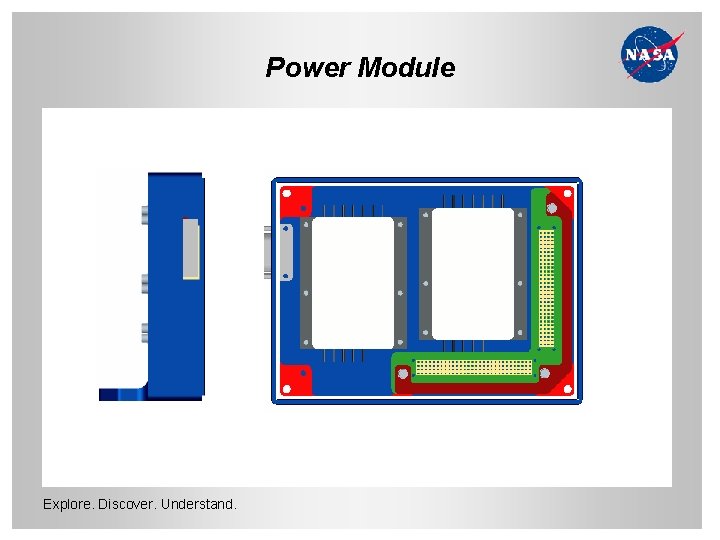

Power Module Explore. Discover. Understand.

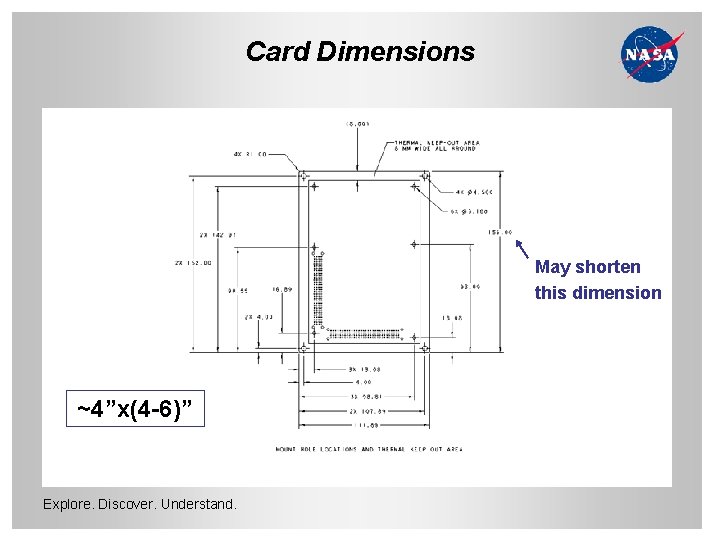

Card Dimensions May shorten this dimension ~4”x(4 -6)” Explore. Discover. Understand.

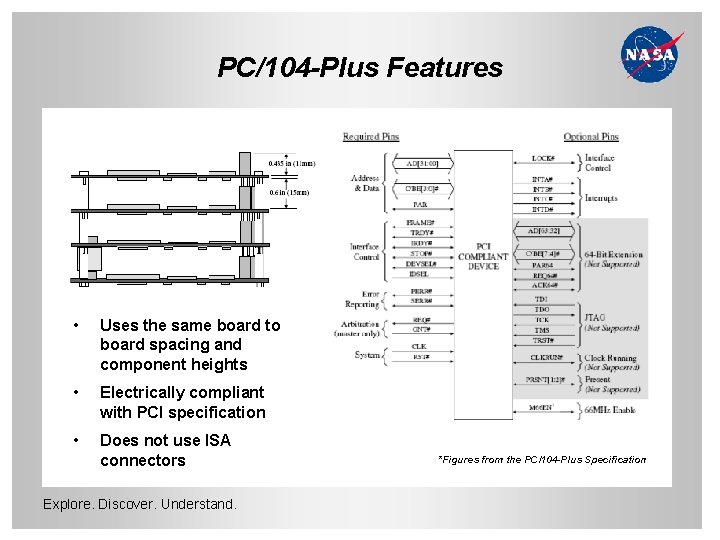

PC/104 -Plus Features • Uses the same board to board spacing and component heights • Electrically compliant with PCI specification • Does not use ISA connectors Explore. Discover. Understand. *Figures from the PC/104 -Plus Specification

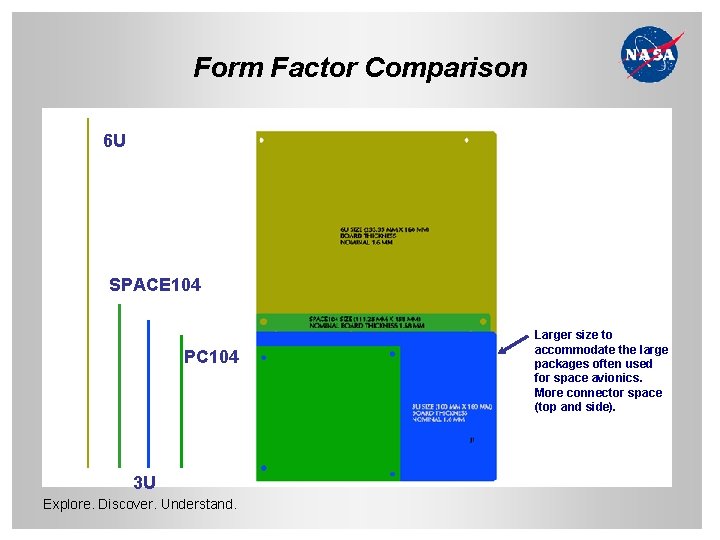

Usable Space Form Factor • • 6 U 3 U PC 104 SPACE 104 Size Board Area Usable 160 MM X 233. 35 MM 100 MM X 160 MM 90. 17 MM X 95. 89 MM 111. 25 MM X 155 MM 37, 336 mm² 16, 000 mm² 8, 646 mm² 17, 244 mm² 30, 430 mm² 11, 595 mm² 7, 686 mm² 12, 280 mm² Explore. Discover. Understand.

Form Factor Comparison 6 U SPACE 104 PC 104 3 U Explore. Discover. Understand. Larger size to accommodate the large packages often used for space avionics. More connector space (top and side).

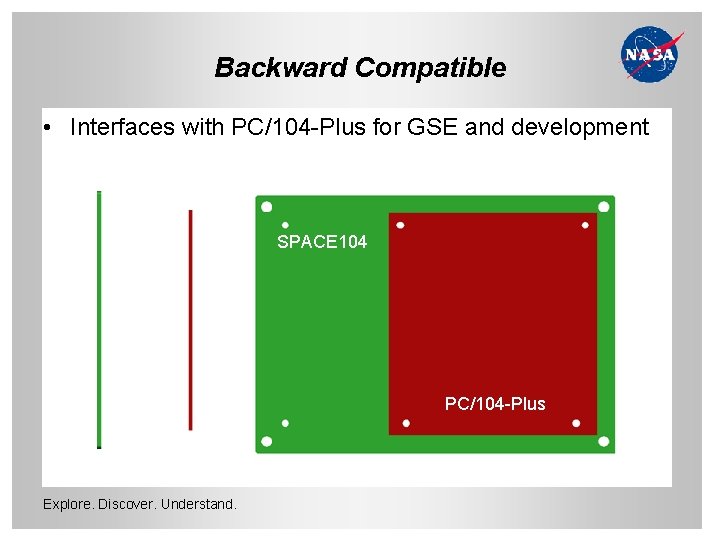

Backward Compatible • Interfaces with PC/104 -Plus for GSE and development SPACE 104 PC/104 -Plus Explore. Discover. Understand.

- Slides: 45