RECONFIGURABLE COMPUTING FOR SPACE Team Reconfigurable Systems Cameron

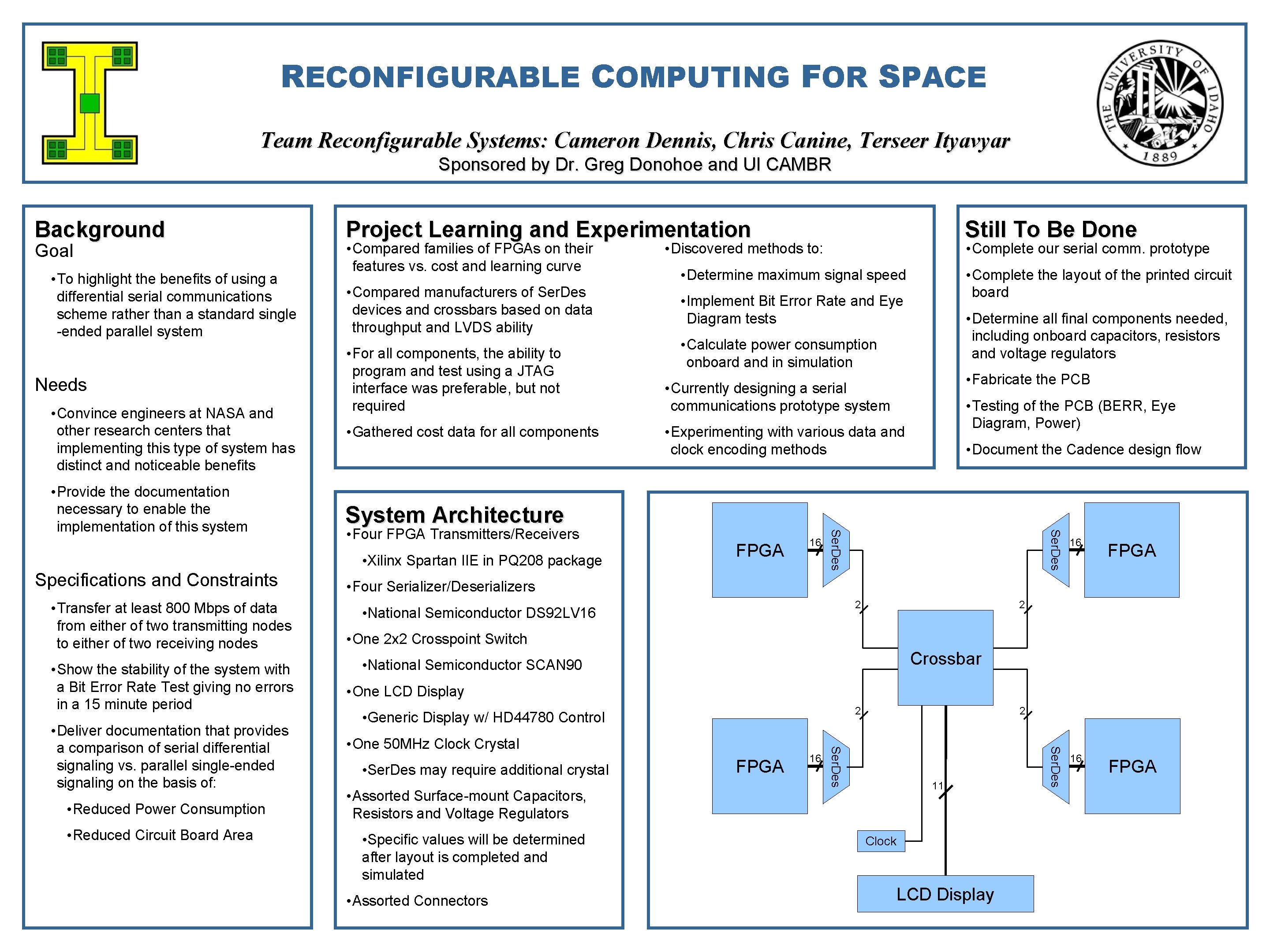

RECONFIGURABLE COMPUTING FOR SPACE Team Reconfigurable Systems: Cameron Dennis, Chris Canine, Terseer Ityavyar Sponsored by Dr. Greg Donohoe and UI CAMBR Background Goal • To highlight the benefits of using a differential serial communications scheme rather than a standard single -ended parallel system Needs • Convince engineers at NASA and other research centers that implementing this type of system has distinct and noticeable benefits • Compared families of FPGAs on their features vs. cost and learning curve • Compared manufacturers of Ser. Des devices and crossbars based on data throughput and LVDS ability • For all components, the ability to program and test using a JTAG interface was preferable, but not required • Gathered cost data for all components • Show the stability of the system with a Bit Error Rate Test giving no errors in a 15 minute period • Reduced Circuit Board Area • Complete the layout of the printed circuit board • Implement Bit Error Rate and Eye Diagram tests • Determine all final components needed, including onboard capacitors, resistors and voltage regulators • Calculate power consumption onboard and in simulation • Fabricate the PCB • Currently designing a serial communications prototype system • Testing of the PCB (BERR, Eye Diagram, Power) • Experimenting with various data and clock encoding methods • Document the Cadence design flow • Four FPGA Transmitters/Receivers FPGA 16 16 FPGA • Four Serializer/Deserializers 2 • National Semiconductor DS 92 LV 16 2 • One 2 x 2 Crosspoint Switch Crossbar • National Semiconductor SCAN 90 • One LCD Display 2 • Generic Display w/ HD 44780 Control • One 50 MHz Clock Crystal • Ser. Des may require additional crystal FPGA 16 2 11 • Assorted Surface-mount Capacitors, Resistors and Voltage Regulators • Specific values will be determined after layout is completed and simulated • Assorted Connectors Clock LCD Display Ser. Des • Reduced Power Consumption • Determine maximum signal speed Ser. Des • Deliver documentation that provides a comparison of serial differential signaling vs. parallel single-ended signaling on the basis of: • Complete our serial comm. prototype Ser. Des • Transfer at least 800 Mbps of data from either of two transmitting nodes to either of two receiving nodes • Discovered methods to: System Architecture • Xilinx Spartan IIE in PQ 208 package Specifications and Constraints Still To Be Done Ser. Des • Provide the documentation necessary to enable the implementation of this system Project Learning and Experimentation

- Slides: 1