Recap Lecture 1 What is asynchronous design Why

- Slides: 13

Recap: Lecture 1 ã What is asynchronous design? Why do we want study it? ã What is pipelining? How can it be used to design really fast hardware? to 1

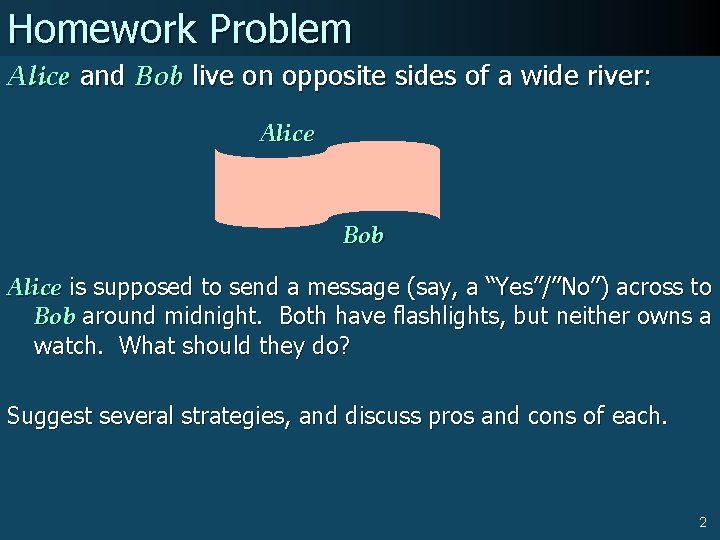

Homework Problem Alice and Bob live on opposite sides of a wide river: Alice Bob Alice is supposed to send a message (say, a “Yes”/”No”) across to Bob around midnight. Both have flashlights, but neither owns a watch. What should they do? Suggest several strategies, and discuss pros and cons of each. 2

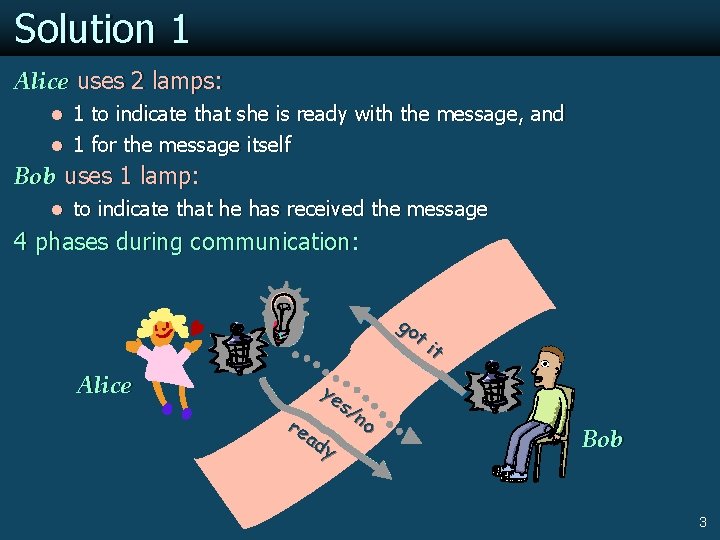

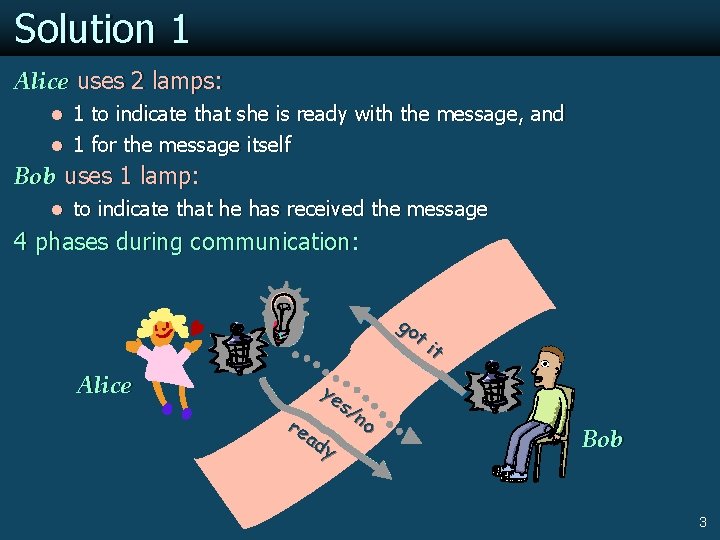

Solution 1 Alice uses 2 lamps: l 1 to indicate that she is ready with the message, and l 1 for the message itself Bob uses 1 lamp: l to indicate that he has received the message 4 phases during communication: go ti t Alice ye s/ no re ad y Bob 3

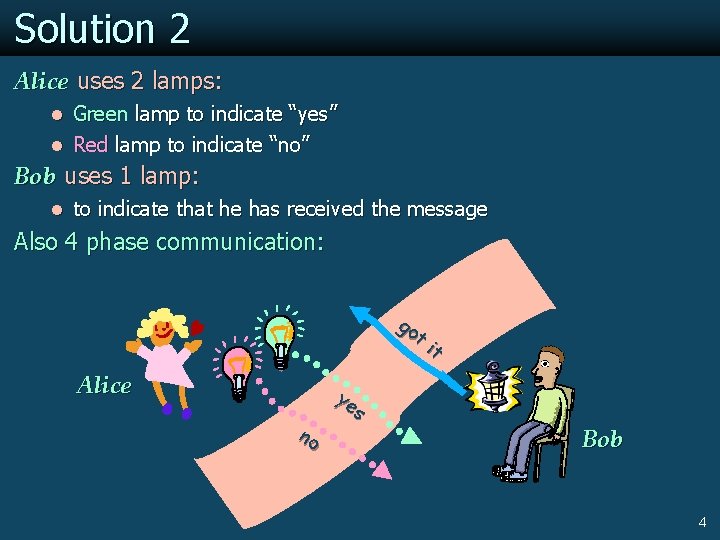

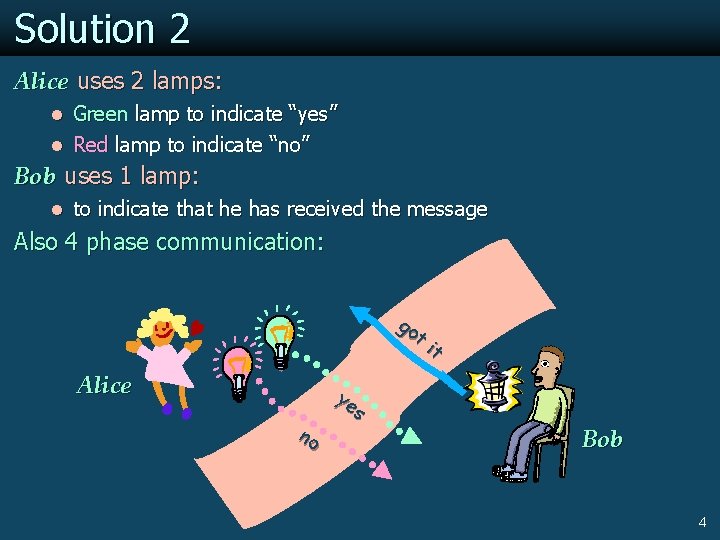

Solution 2 Alice uses 2 lamps: l Green lamp to indicate “yes” l Red lamp to indicate “no” Bob uses 1 lamp: l to indicate that he has received the message Also 4 phase communication: go ti t Alice no ye s Bob 4

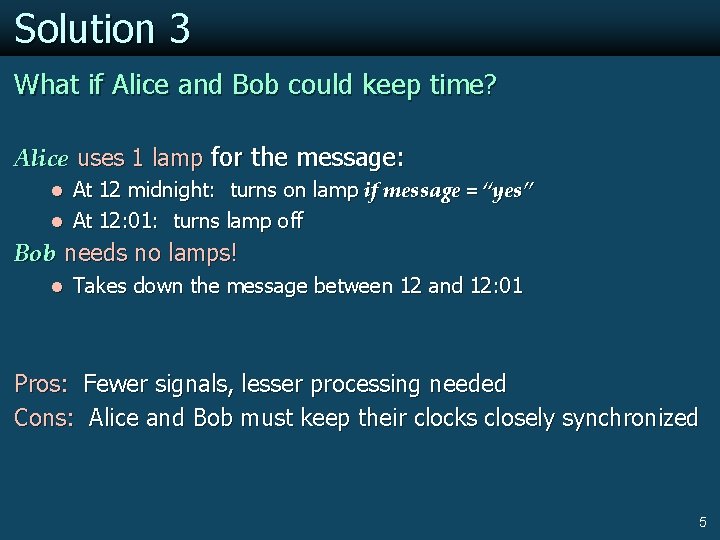

Solution 3 What if Alice and Bob could keep time? Alice uses 1 lamp for the message: l At 12 midnight: turns on lamp if message = “yes” l At 12: 01: turns lamp off Bob needs no lamps! l Takes down the message between 12 and 12: 01 Pros: Fewer signals, lesser processing needed Cons: Alice and Bob must keep their clocks closely synchronized 5

Lecture 2: Asynchronous Datapaths How is data represented in an asynchronous system? ã How is information exchanged? ã 6

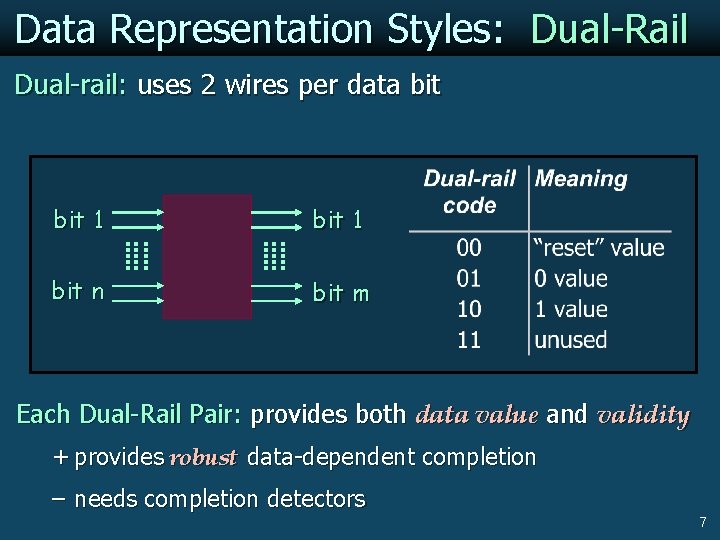

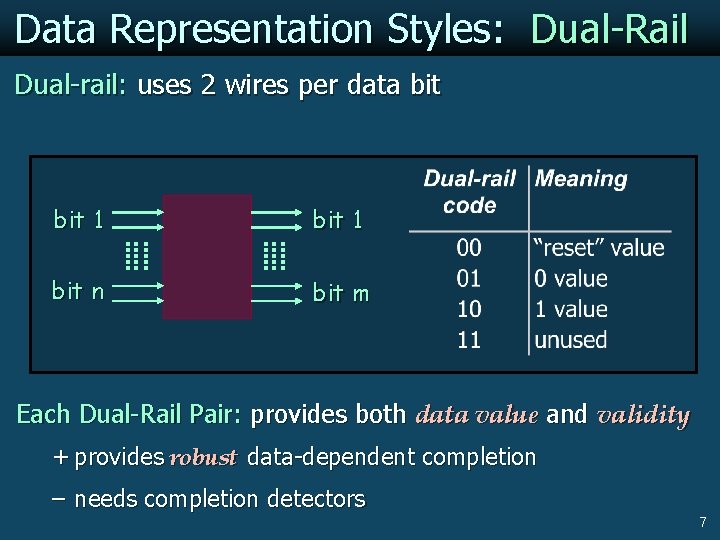

Data Representation Styles: Dual-Rail Dual-rail: uses 2 wires per data bit 1 bit n bit m Each Dual-Rail Pair: provides both data value and validity + provides robust data-dependent completion – needs completion detectors 7

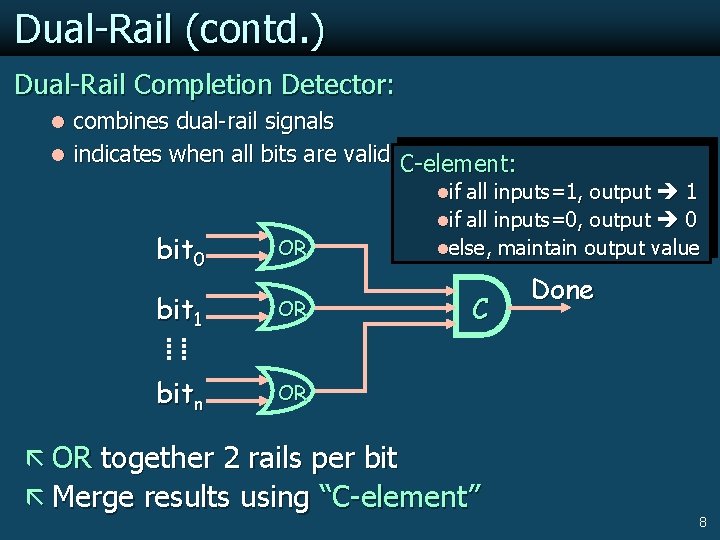

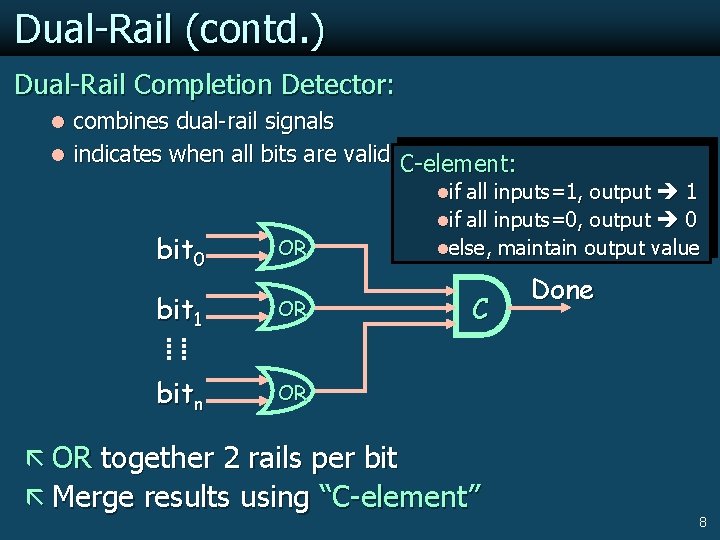

Dual-Rail (contd. ) Dual-Rail Completion Detector: l combines dual-rail signals l indicates when all bits are valid (or reset) C-element: lif all inputs=1, output 1 lif all inputs=0, output 0 lelse, maintain output value OR bit 0 0 bit 1 OR bitn OR C ã OR together 2 rails per bit ã Merge results using “C-element” Done 8

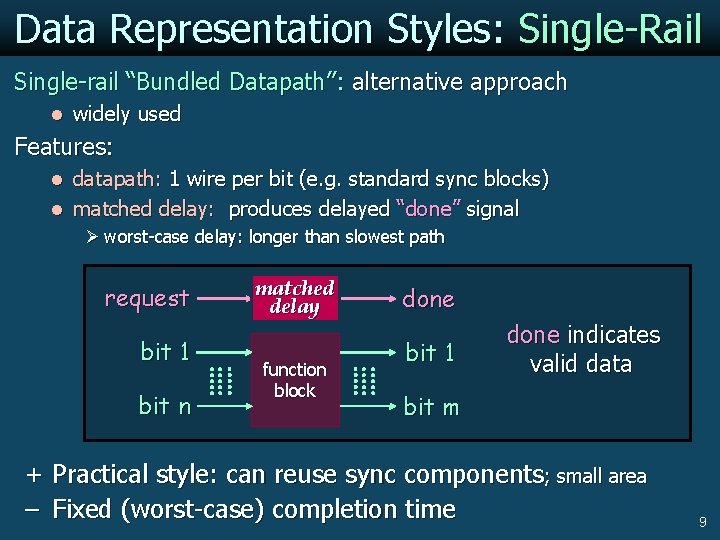

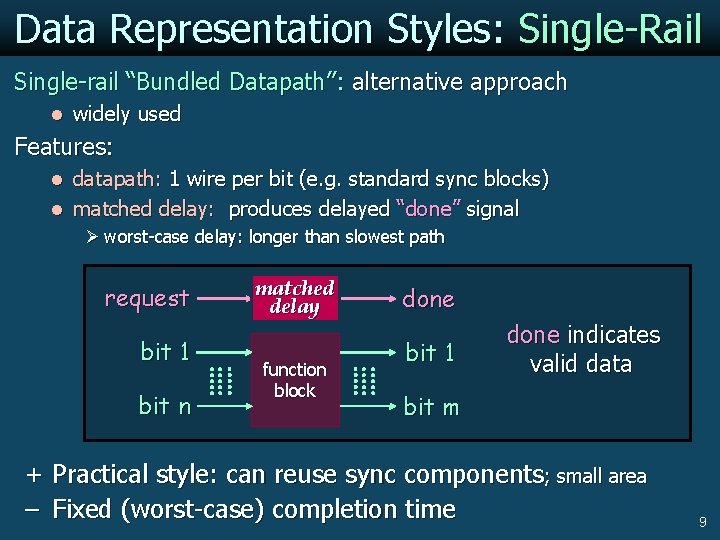

Data Representation Styles: Single-Rail Single-rail “Bundled Datapath”: alternative approach l widely used Features: l datapath: 1 wire per bit (e. g. standard sync blocks) l matched delay: produces delayed “done” signal Ø worst-case delay: longer than slowest path request bit 1 bit n matched delay function block done bit 1 done indicates valid data bit m + Practical style: can reuse sync components; small area – Fixed (worst-case) completion time 9

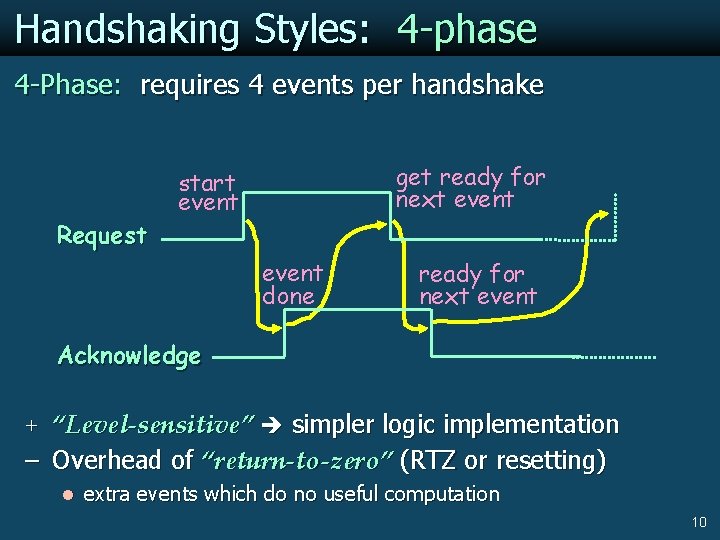

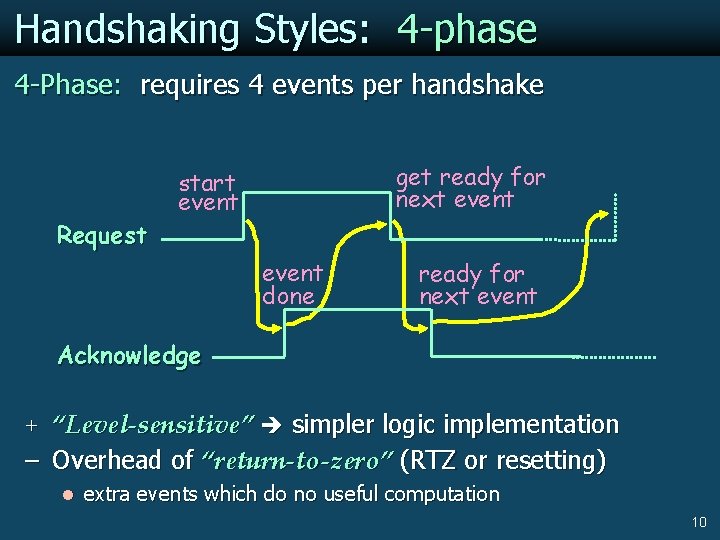

Handshaking Styles: 4 -phase 4 -Phase: requires 4 events per handshake Request get ready for next event start event done ready for next event Acknowledge + “Level-sensitive” simpler logic implementation – Overhead of “return-to-zero” (RTZ or resetting) l extra events which do no useful computation 10

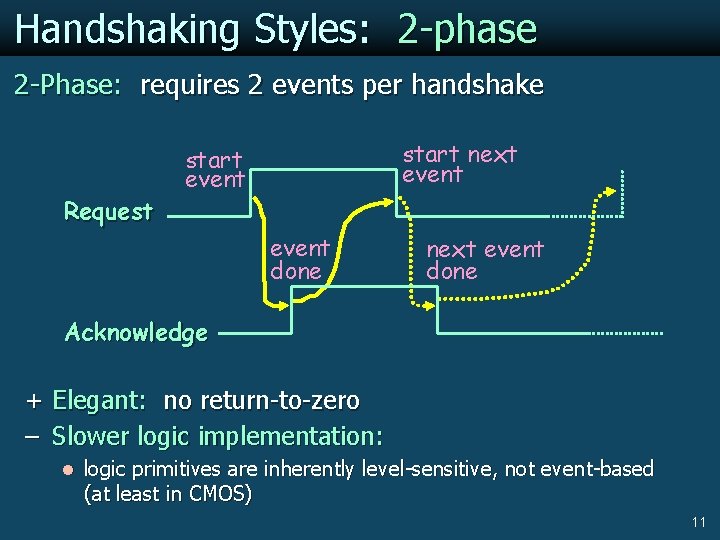

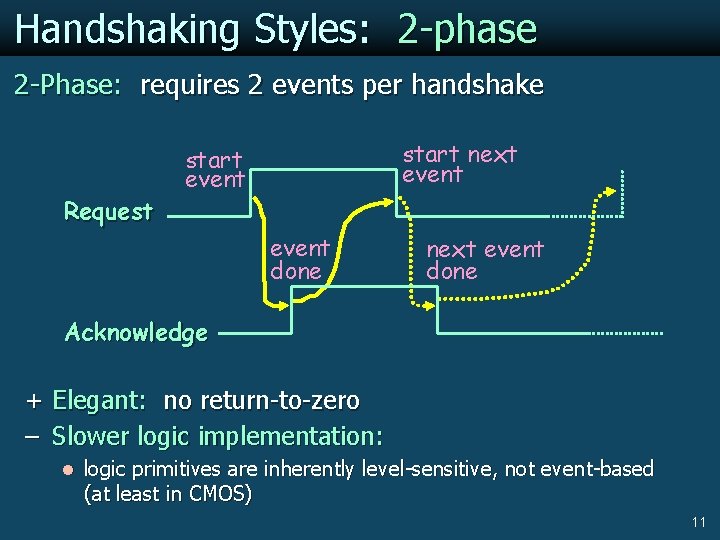

Handshaking Styles: 2 -phase 2 -Phase: requires 2 events per handshake Request start next event start event done next event done Acknowledge + Elegant: no return-to-zero – Slower logic implementation: l logic primitives are inherently level-sensitive, not event-based (at least in CMOS) 11

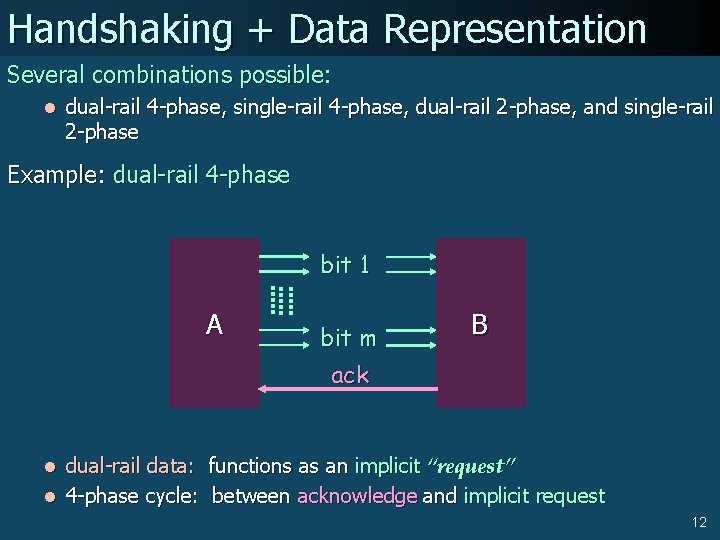

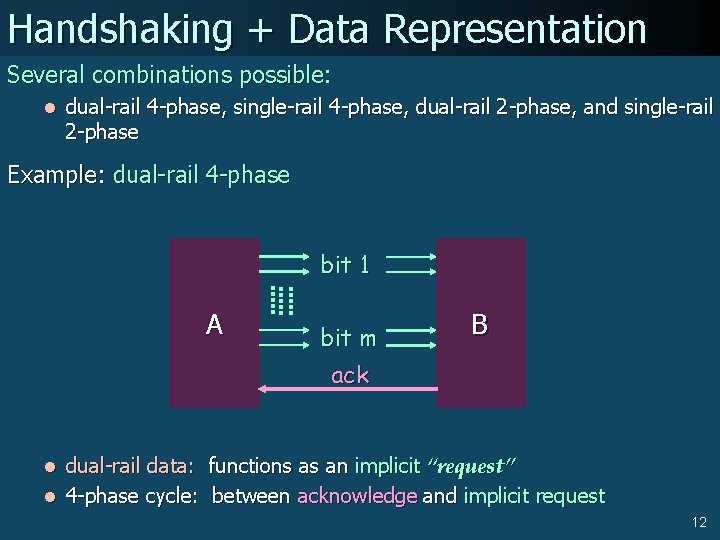

Handshaking + Data Representation Several combinations possible: l dual-rail 4 -phase, single-rail 4 -phase, dual-rail 2 -phase, and single-rail 2 -phase Example: dual-rail 4 -phase bit 1 A bit m B ack l dual-rail data: functions as an implicit “request” l 4 -phase cycle: between acknowledge and implicit request 12

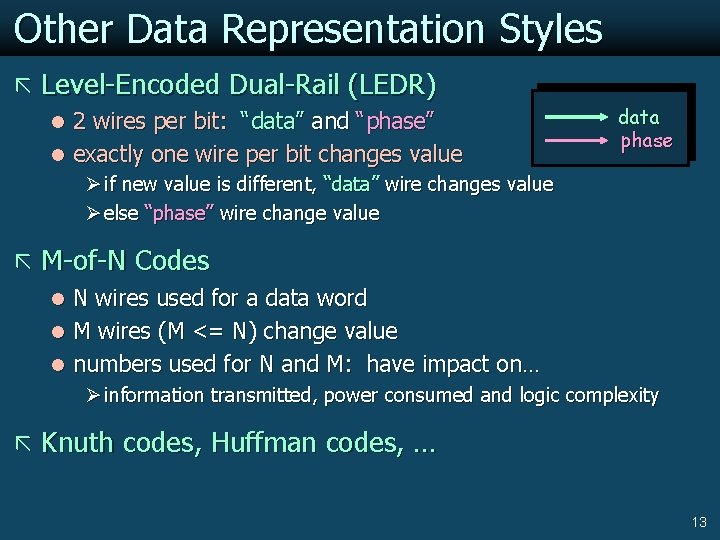

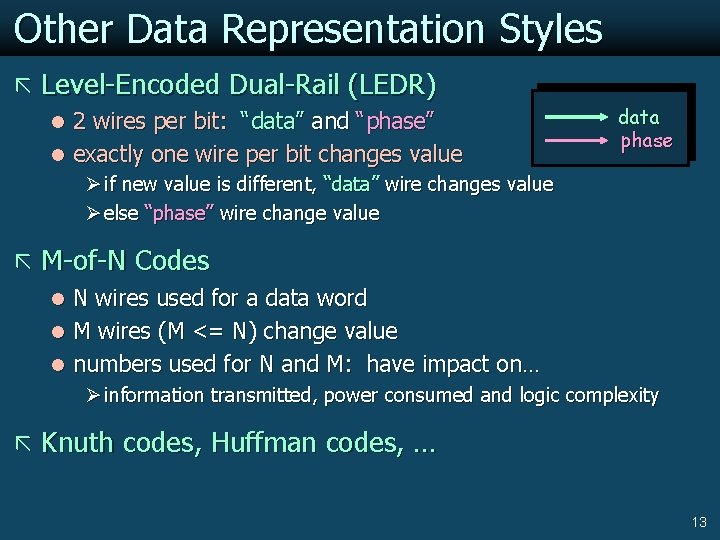

Other Data Representation Styles ã Level-Encoded Dual-Rail (LEDR) l 2 wires per bit: “data” and “phase” l exactly one wire per bit changes value Ø if new value is different, “data” wire changes value Ø else “phase” wire change value data phase ã M-of-N Codes l N wires used for a data word l M wires (M <= N) change value l numbers used for N and M: have impact on… Ø information transmitted, power consumed and logic complexity ã Knuth codes, Huffman codes, … 13