Recap Always block z Always waiting for a

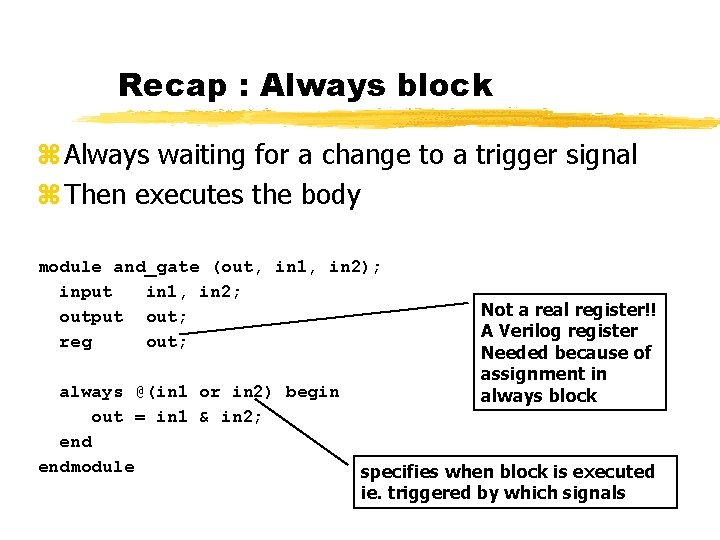

Recap : Always block z Always waiting for a change to a trigger signal z Then executes the body module and_gate (out, in 1, in 2); input in 1, in 2; output out; reg out; always @(in 1 or in 2) begin out = in 1 & in 2; endmodule Not a real register!! A Verilog register Needed because of assignment in always block specifies when block is executed ie. triggered by which signals

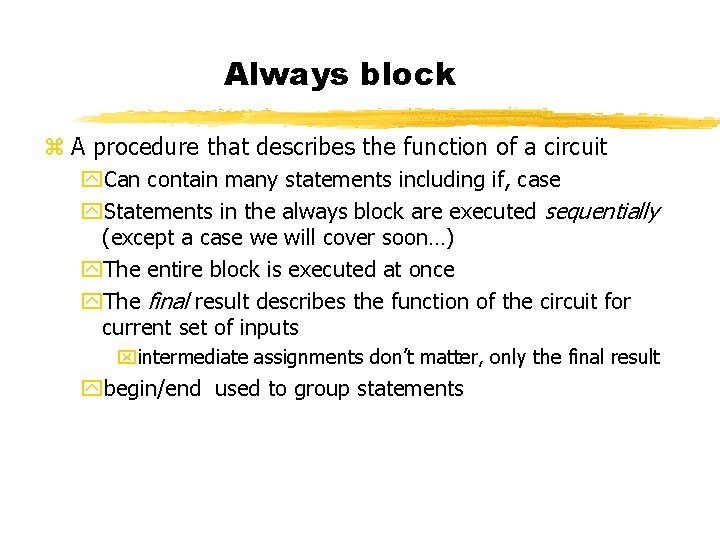

Always block z A procedure that describes the function of a circuit y. Can contain many statements including if, case y. Statements in the always block are executed sequentially (except a case we will cover soon…) y. The entire block is executed at once y. The final result describes the function of the circuit for current set of inputs xintermediate assignments don’t matter, only the final result ybegin/end used to group statements

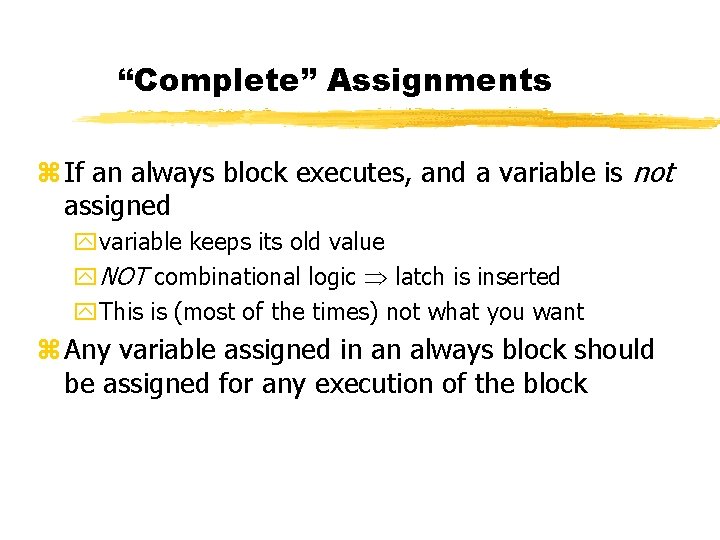

“Complete” Assignments z If an always block executes, and a variable is not assigned yvariable keeps its old value y. NOT combinational logic latch is inserted y. This is (most of the times) not what you want z Any variable assigned in an always block should be assigned for any execution of the block

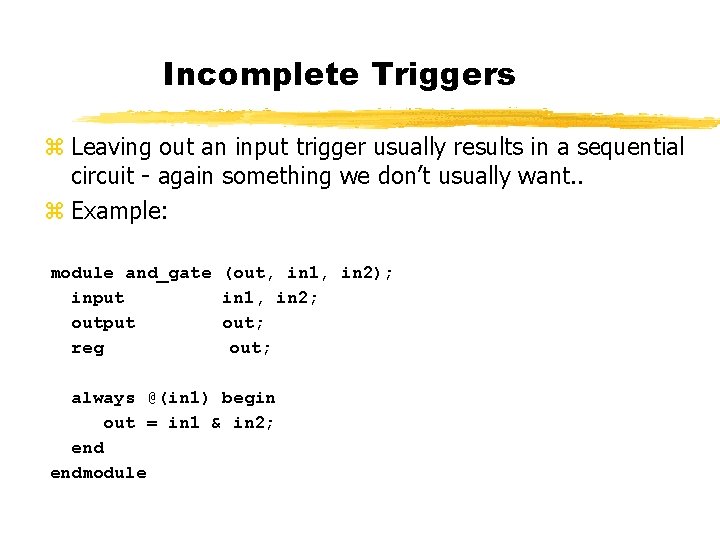

Incomplete Triggers z Leaving out an input trigger usually results in a sequential circuit - again something we don’t usually want. . z Example: module and_gate (out, in 1, in 2); input in 1, in 2; output out; reg out; always @(in 1) begin out = in 1 & in 2; endmodule

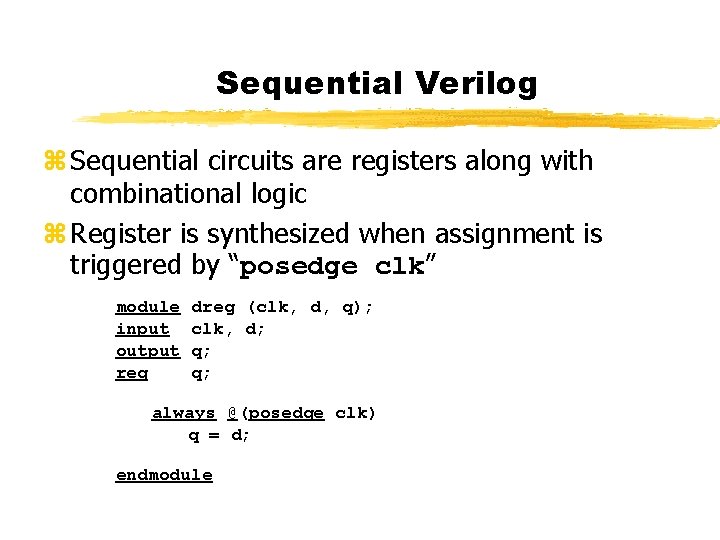

Sequential Verilog z Sequential circuits are registers along with combinational logic z Register is synthesized when assignment is triggered by “posedge clk” module input output reg dreg (clk, d, q); clk, d; q; q; always @(posedge clk) q = d; endmodule

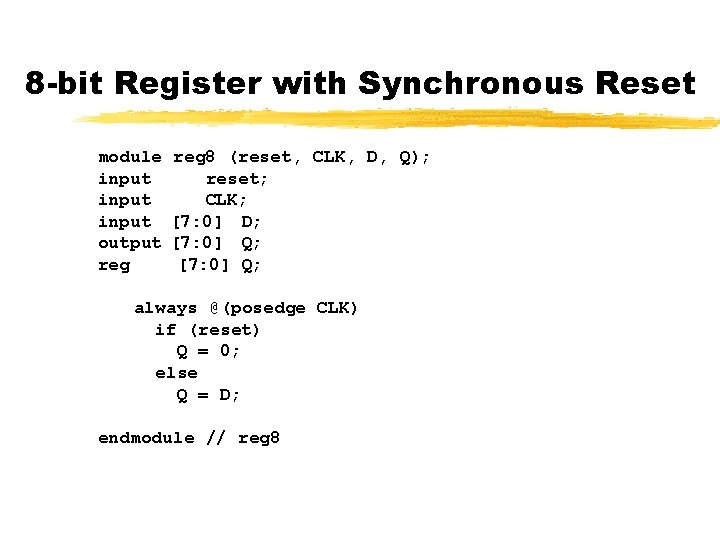

8 -bit Register with Synchronous Reset module input output reg 8 (reset, CLK, D, Q); reset; CLK; [7: 0] D; [7: 0] Q; always @(posedge CLK) if (reset) Q = 0; else Q = D; endmodule // reg 8

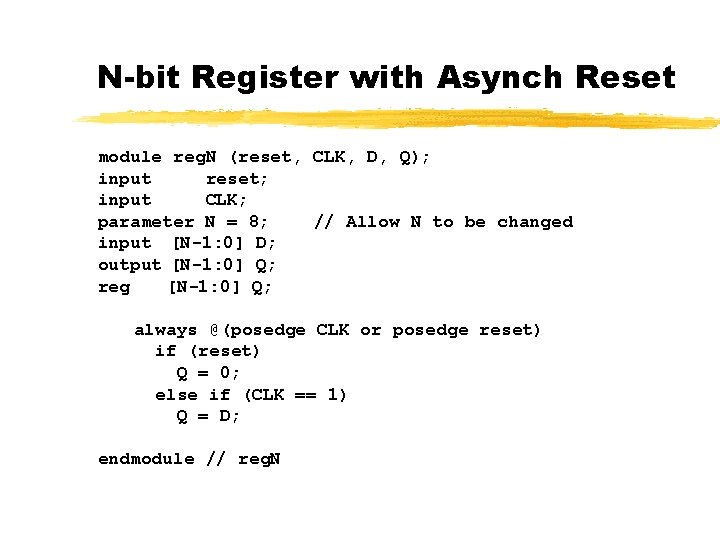

N-bit Register with Asynch Reset module reg. N (reset, CLK, D, Q); input reset; input CLK; parameter N = 8; // Allow N to be changed input [N-1: 0] D; output [N-1: 0] Q; reg [N-1: 0] Q; always @(posedge CLK or posedge reset) if (reset) Q = 0; else if (CLK == 1) Q = D; endmodule // reg. N

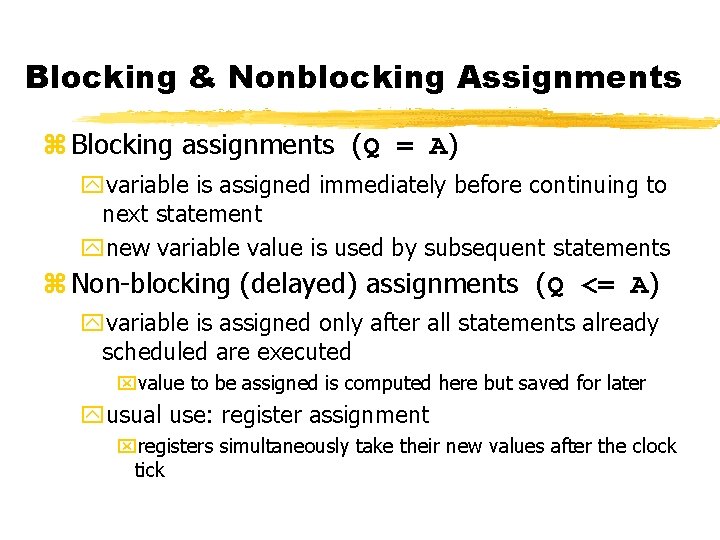

Blocking & Nonblocking Assignments z Blocking assignments (Q = A) yvariable is assigned immediately before continuing to next statement ynew variable value is used by subsequent statements z Non-blocking (delayed) assignments (Q <= A) yvariable is assigned only after all statements already scheduled are executed xvalue to be assigned is computed here but saved for later yusual use: register assignment xregisters simultaneously take their new values after the clock tick

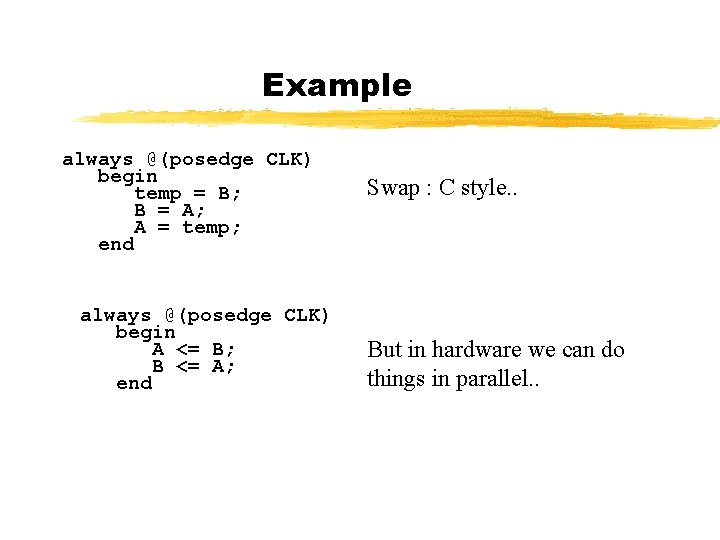

Example always @(posedge CLK) begin temp = B; B = A; A = temp; end always @(posedge CLK) begin A <= B; B <= A; end Swap : C style. . But in hardware we can do things in parallel. .

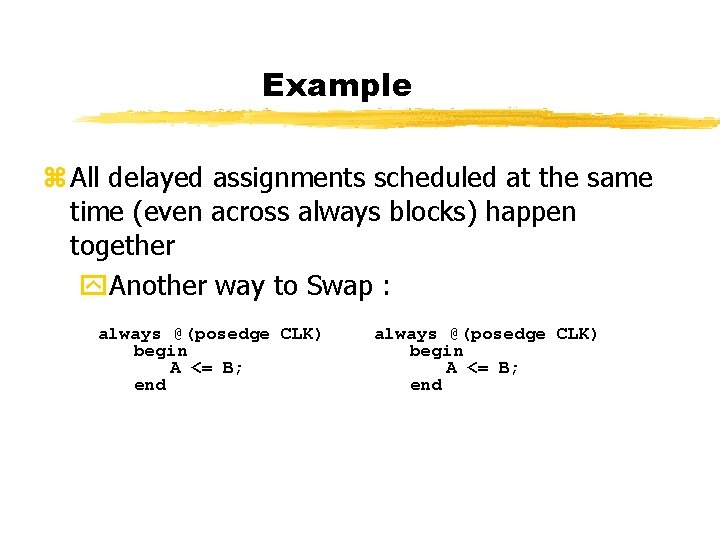

Example z All delayed assignments scheduled at the same time (even across always blocks) happen together y. Another way to Swap : always @(posedge CLK) begin A <= B; end

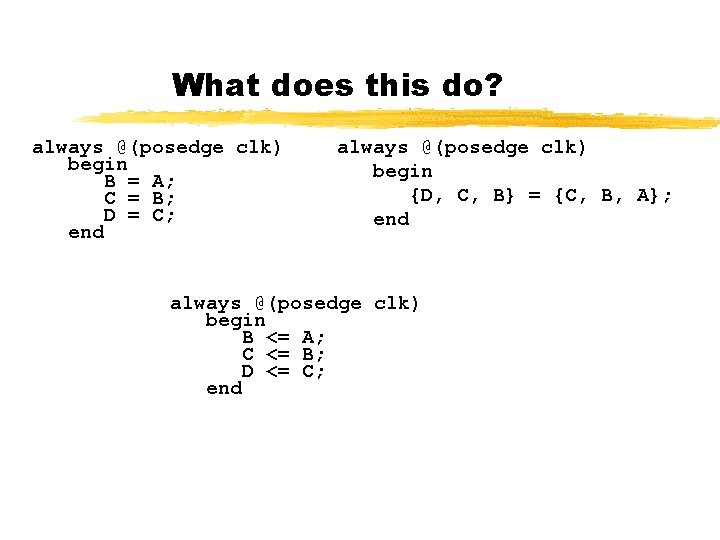

What does this do? always @(posedge clk) begin B = A; C = B; D = C; end always @(posedge clk) begin {D, C, B} = {C, B, A}; end always @(posedge clk) begin B <= A; C <= B; D <= C; end

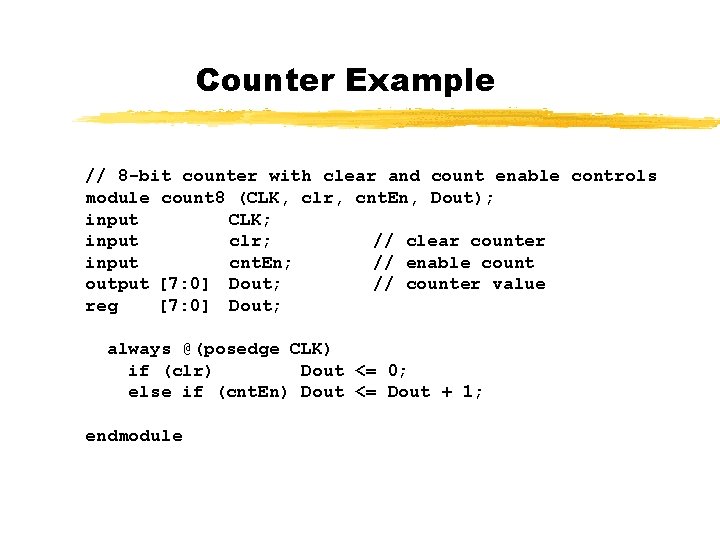

Counter Example // 8 -bit counter with clear and count enable controls module count 8 (CLK, clr, cnt. En, Dout); input CLK; input clr; // clear counter input cnt. En; // enable count output [7: 0] Dout; // counter value reg [7: 0] Dout; always @(posedge CLK) if (clr) Dout <= 0; else if (cnt. En) Dout <= Dout + 1; endmodule

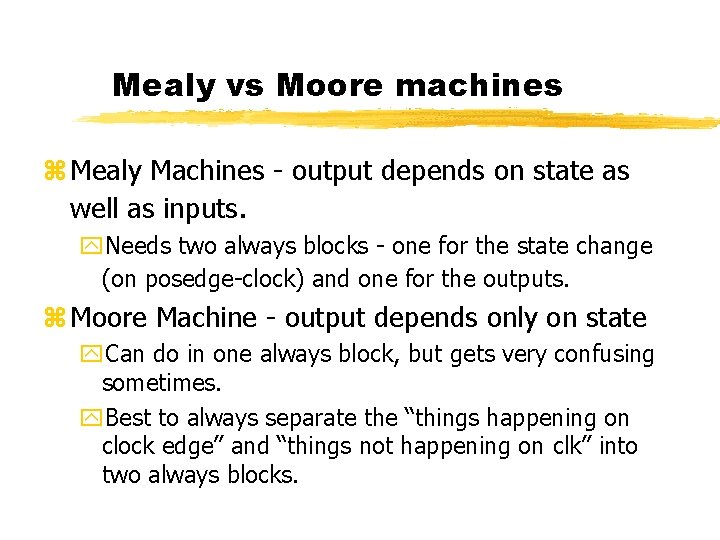

Mealy vs Moore machines z Mealy Machines - output depends on state as well as inputs. y. Needs two always blocks - one for the state change (on posedge-clock) and one for the outputs. z Moore Machine - output depends only on state y. Can do in one always block, but gets very confusing sometimes. y. Best to always separate the “things happening on clock edge” and “things not happening on clk” into two always blocks.

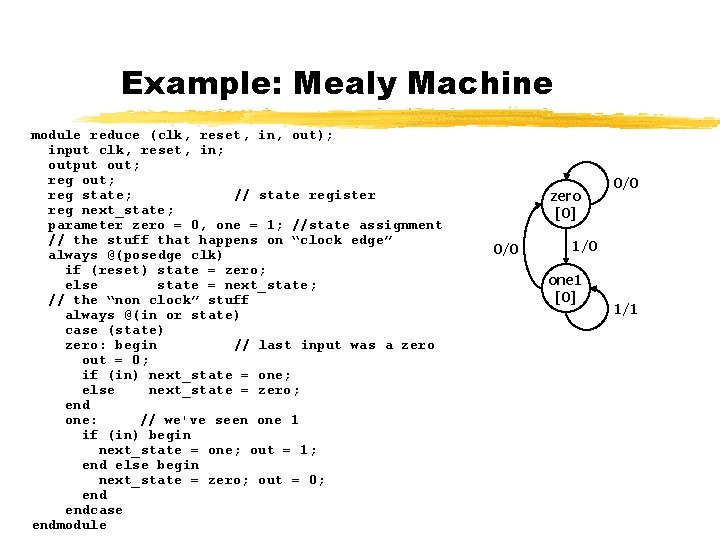

Example: Mealy Machine module reduce (clk, reset, in, out); input clk, reset, in; output out; reg state; // state register reg next_state; parameter zero = 0, one = 1; //state assignment // the stuff that happens on “clock edge” always @(posedge clk) if (reset) state = zero; else state = next_state; // the “non clock” stuff always @(in or state) case (state) zero: begin // last input was a zero out = 0; if (in) next_state = one; else next_state = zero; end one: // we've seen one 1 if (in) begin next_state = one; out = 1; end else begin next_state = zero; out = 0; endcase endmodule zero [0] 0/0 1/0 one 1 [0] 1/1

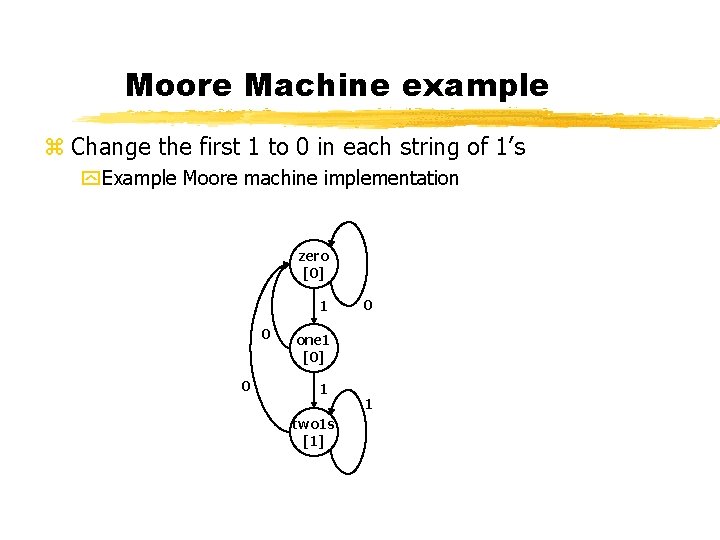

Moore Machine example z Change the first 1 to 0 in each string of 1’s y Example Moore machine implementation zero [0] 1 0 0 0 one 1 [0] 1 two 1 s [1] 1

Verilog code for Moore. . module reduce (clk, reset, in, out); input clk, reset, in; output out; reg [1: 0] state; // state register reg [1: 0] next_state; // State assignment parameter zero = 0, one 1 = 1, two 1 s = 2; // Implement the state register always @(posedge clk) if (reset) state = zero; else state = next_state;

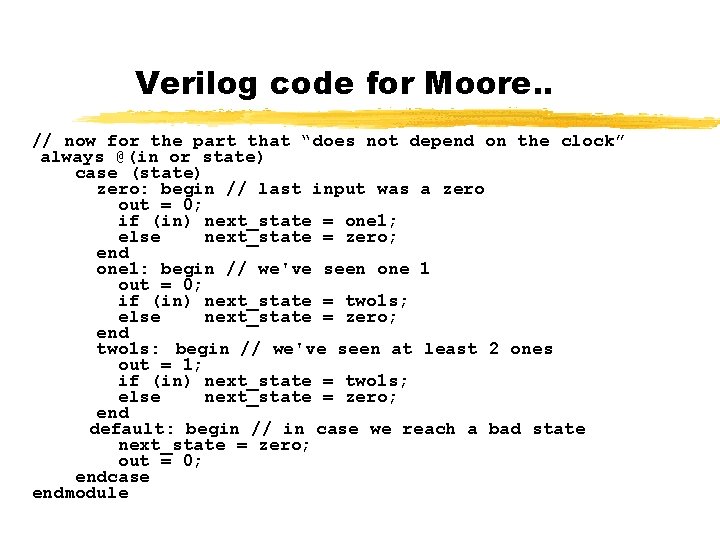

Verilog code for Moore. . // now for the part that “does not depend on the clock” always @(in or state) case (state) zero: begin // last input was a zero out = 0; if (in) next_state = one 1; else next_state = zero; end one 1: begin // we've seen one 1 out = 0; if (in) next_state = two 1 s; else next_state = zero; end two 1 s: begin // we've seen at least 2 ones out = 1; if (in) next_state = two 1 s; else next_state = zero; end default: begin // in case we reach a bad state next_state = zero; out = 0; endcase endmodule

- Slides: 17