Recap 1 Instruction Set Architecture ISA The ISA

- Slides: 21

Recap 1

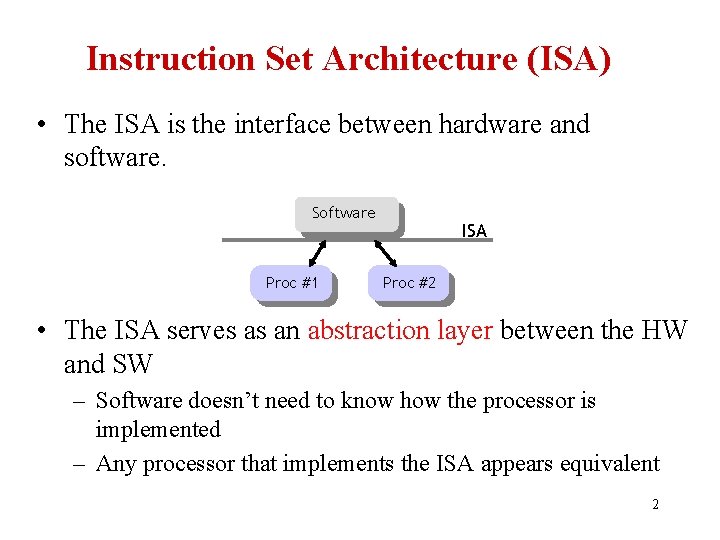

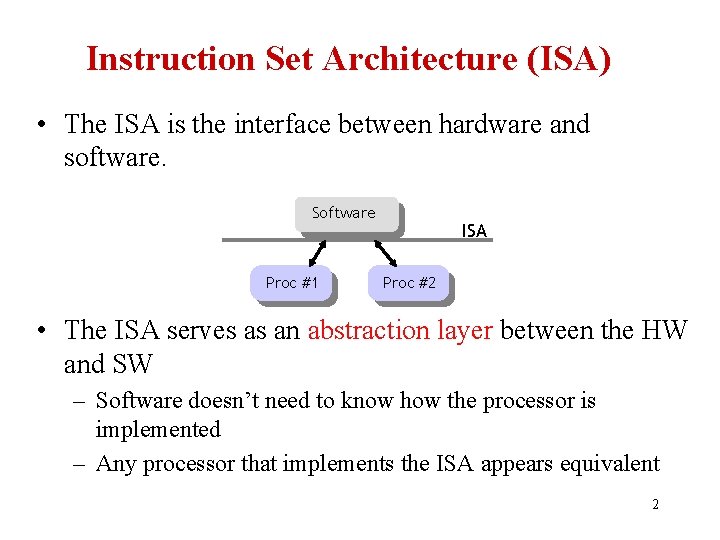

Instruction Set Architecture (ISA) • The ISA is the interface between hardware and software. Software Proc #1 ISA Proc #2 • The ISA serves as an abstraction layer between the HW and SW – Software doesn’t need to know how the processor is implemented – Any processor that implements the ISA appears equivalent 2

What is instruction set architecture (ISA)? • Instruction set of a computer: the portion of the computer visible to the assembly level programmer or to the compiler writer ISA – Defines registers – Defines data transfer modes (instructions) between registers, memory and I/O – There should be sufficient instructions to efficiently translate any program • Next, define instruction set format – binary representation used by the hardware – Variable-length vs. fixed-length instructions 3

Growth/Variations of Processors 4

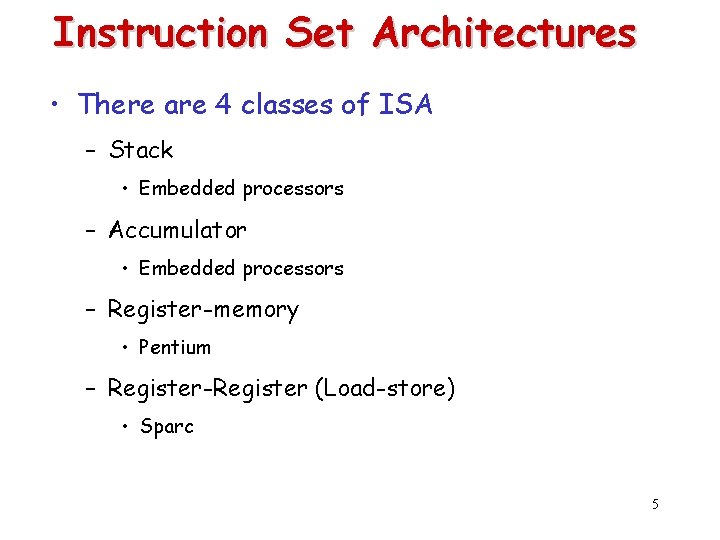

Instruction Set Architectures • There are 4 classes of ISA – Stack • Embedded processors – Accumulator • Embedded processors – Register-memory • Pentium – Register-Register (Load-store) • Sparc 5

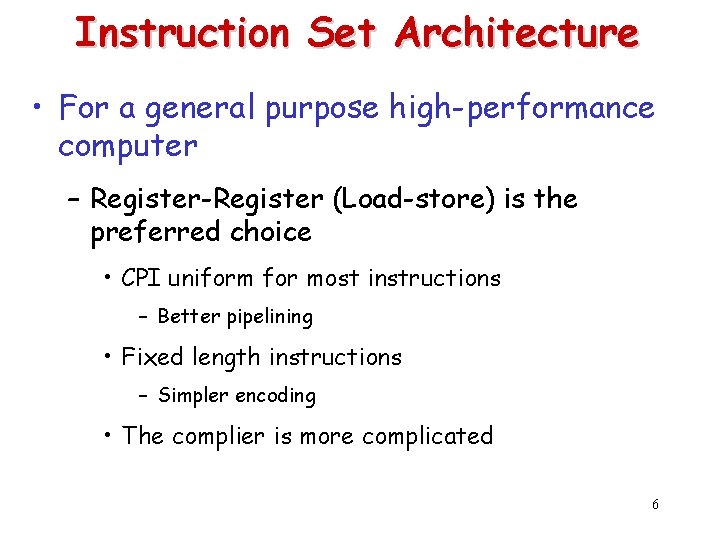

Instruction Set Architecture • For a general purpose high-performance computer – Register-Register (Load-store) is the preferred choice • CPI uniform for most instructions – Better pipelining • Fixed length instructions – Simpler encoding • The complier is more complicated 6

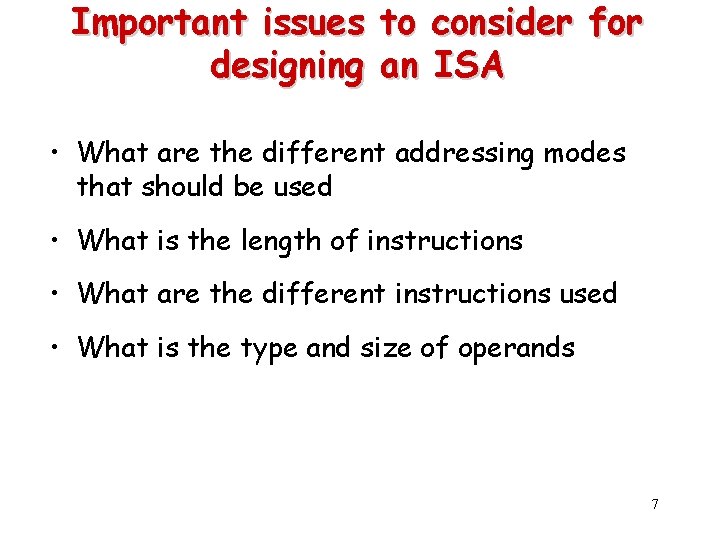

Important issues to consider for designing an ISA • What are the different addressing modes that should be used • What is the length of instructions • What are the different instructions used • What is the type and size of operands 7

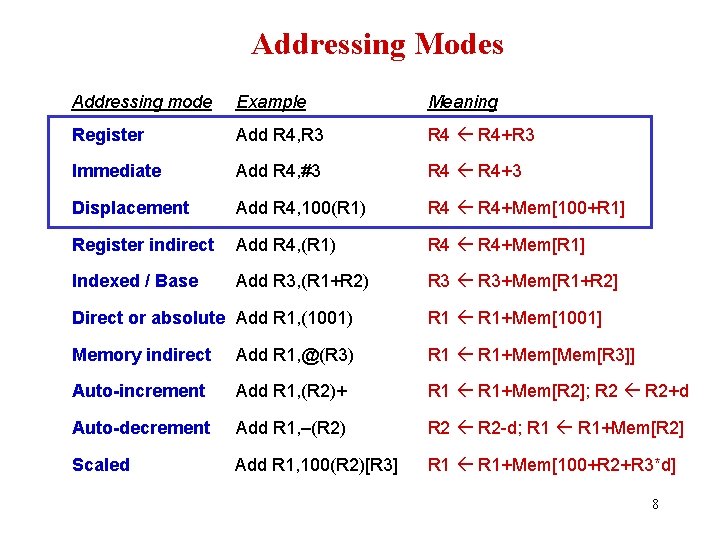

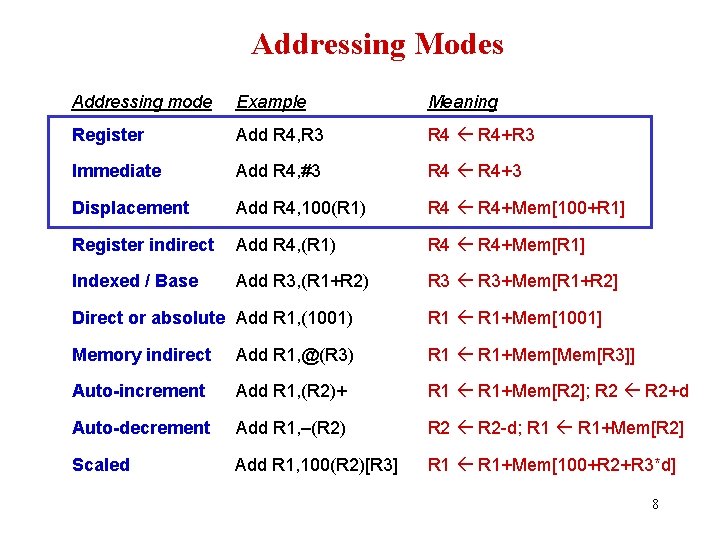

Addressing Modes Addressing mode Example Meaning Register Add R 4, R 3 R 4+R 3 Immediate Add R 4, #3 R 4+3 Displacement Add R 4, 100(R 1) R 4+Mem[100+R 1] Register indirect Add R 4, (R 1) R 4+Mem[R 1] Indexed / Base Add R 3, (R 1+R 2) R 3+Mem[R 1+R 2] Direct or absolute Add R 1, (1001) R 1+Mem[1001] Memory indirect Add R 1, @(R 3) R 1+Mem[R 3]] Auto-increment Add R 1, (R 2)+ R 1+Mem[R 2]; R 2+d Auto-decrement Add R 1, –(R 2) R 2 -d; R 1+Mem[R 2] Scaled Add R 1, 100(R 2)[R 3] R 1+Mem[100+R 2+R 3*d] 8

85% 75% 9

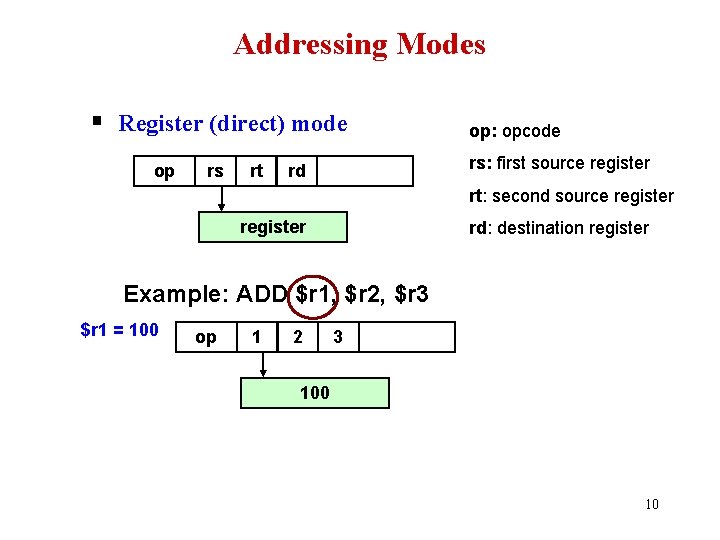

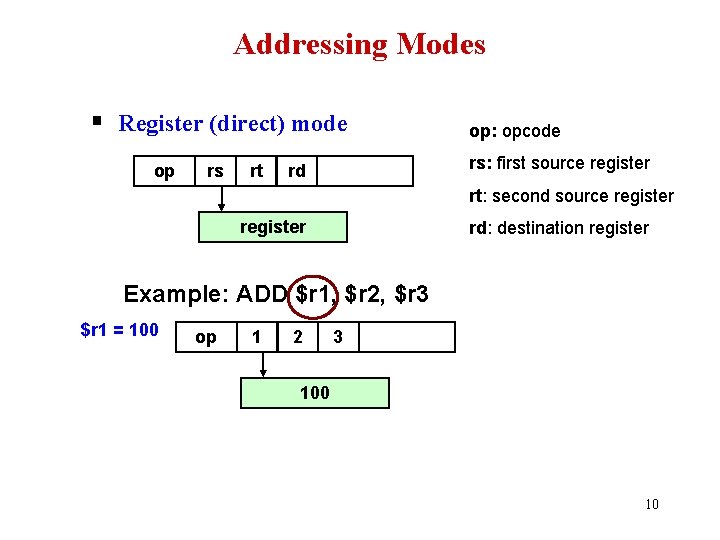

Addressing Modes § Register (direct) mode op rs rt op: opcode rs: first source register rd rt: second source register rd: destination register Example: ADD $r 1, $r 2, $r 3 $r 1 = 100 op 1 2 3 100 10

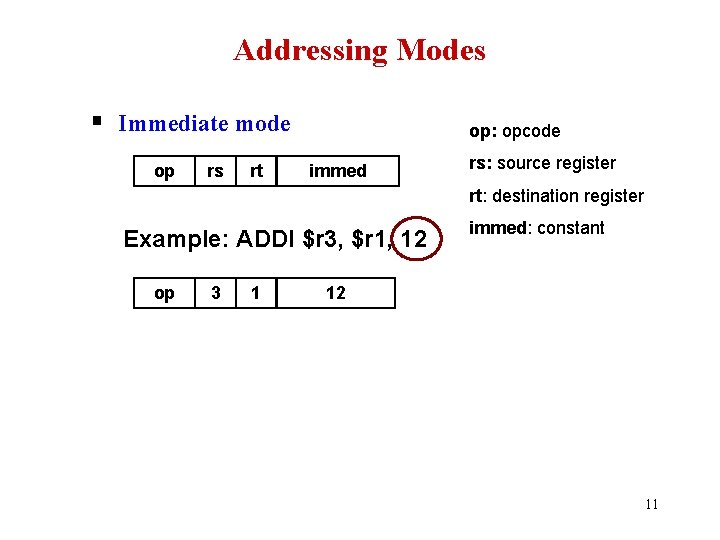

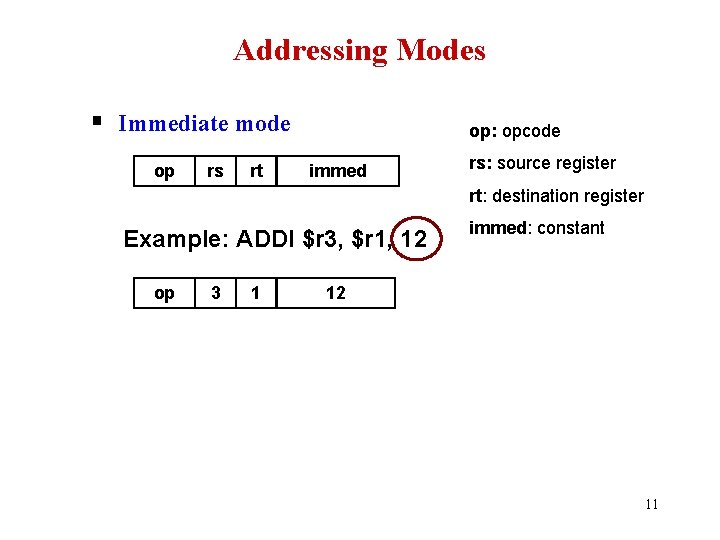

Addressing Modes § Immediate mode op rs rt op: opcode immed rs: source register rt: destination register Example: ADDI $r 3, $r 1, 12 op 3 1 immed: constant 12 11

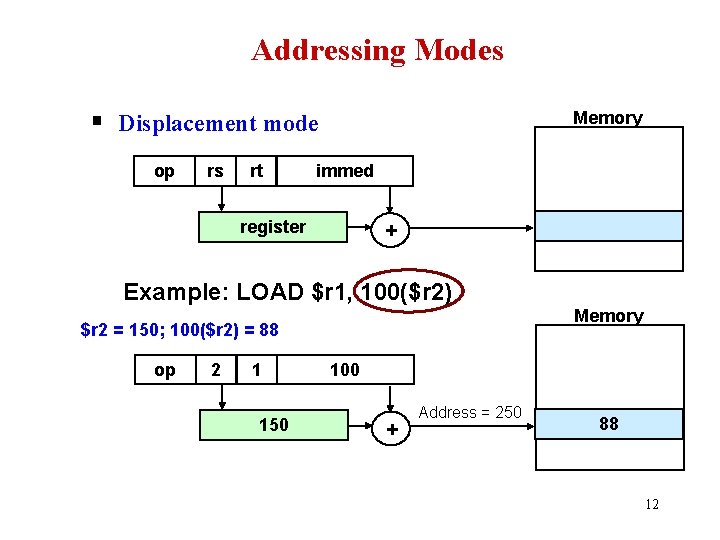

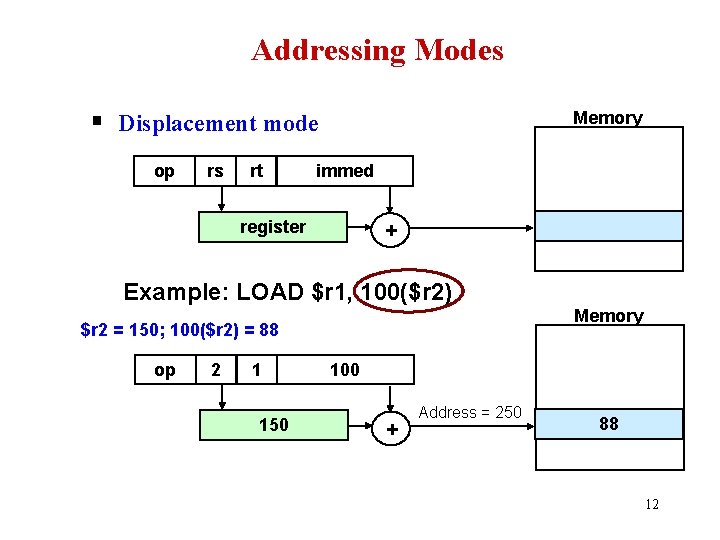

Addressing Modes § Displacement mode op rs rt Memory immed + register Example: LOAD $r 1, 100($r 2) Memory $r 2 = 150; 100($r 2) = 88 op 2 1 150 100 + Address = 250 88 12

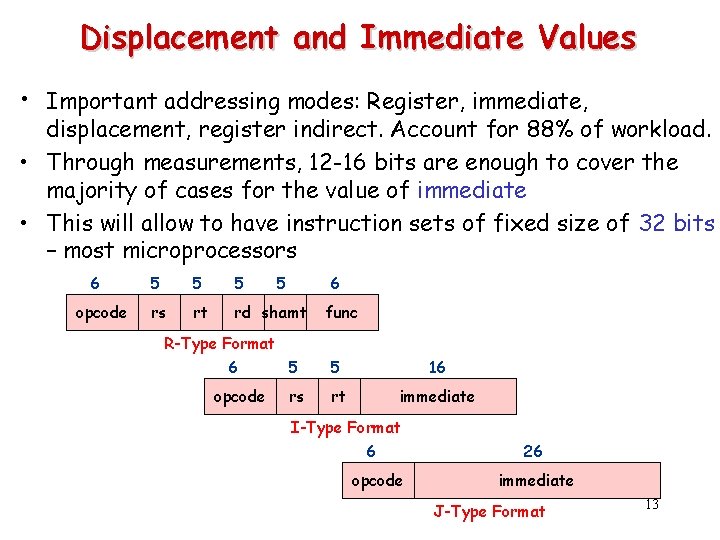

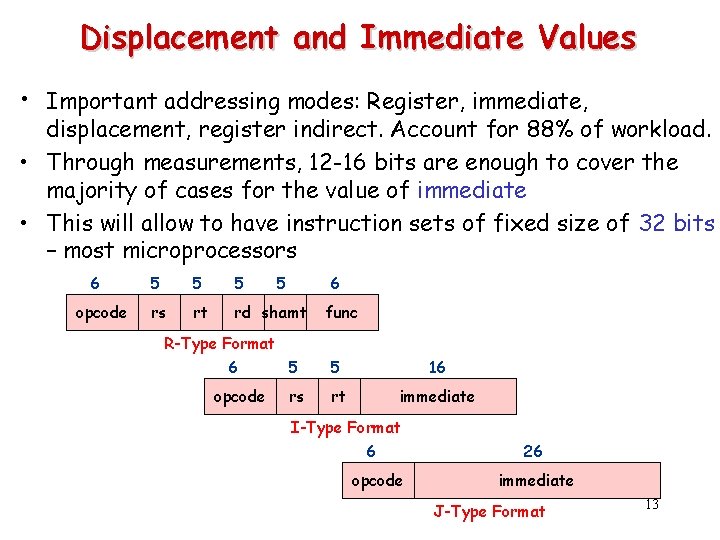

Displacement and Immediate Values • Important addressing modes: Register, immediate, displacement, register indirect. Account for 88% of workload. • Through measurements, 12 -16 bits are enough to cover the majority of cases for the value of immediate • This will allow to have instruction sets of fixed size of 32 bits – most microprocessors 6 opcode 5 5 6 rs rt rd shamt R-Type Format 6 5 opcode rs func 5 16 rt immediate I-Type Format 6 opcode 26 immediate J-Type Format 13

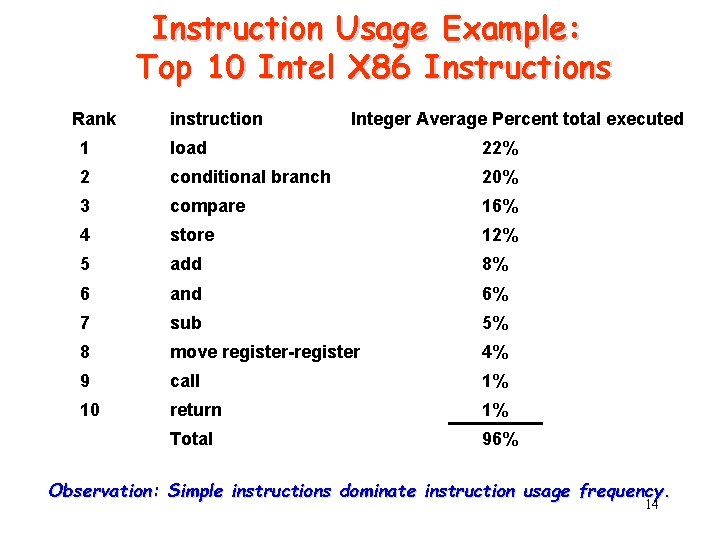

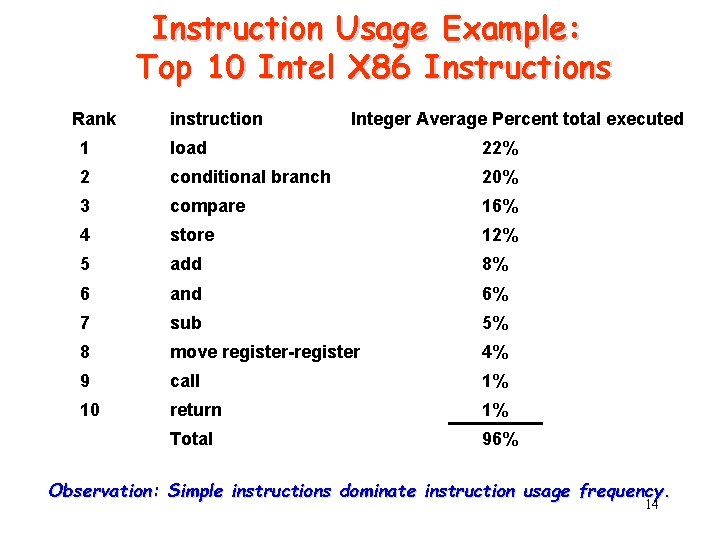

Instruction Usage Example: Top 10 Intel X 86 Instructions Rank instruction Integer Average Percent total executed 1 load 22% 2 conditional branch 20% 3 compare 16% 4 store 12% 5 add 8% 6 and 6% 7 sub 5% 8 move register-register 4% 9 call 1% 10 return 1% Total 96% Observation: Simple instructions dominate instruction usage frequency. 14

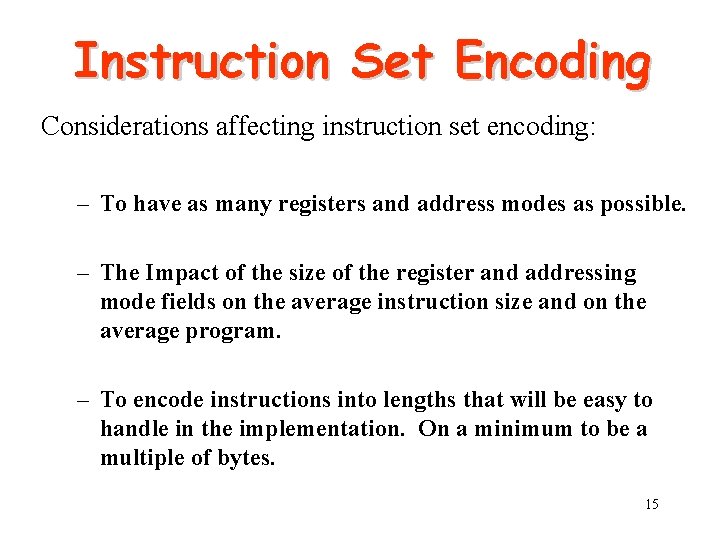

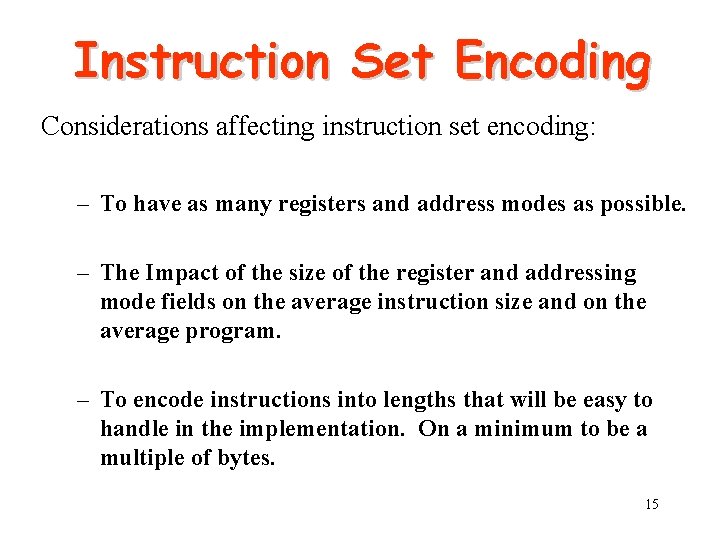

Instruction Set Encoding Considerations affecting instruction set encoding: – To have as many registers and address modes as possible. – The Impact of the size of the register and addressing mode fields on the average instruction size and on the average program. – To encode instructions into lengths that will be easy to handle in the implementation. On a minimum to be a multiple of bytes. 15

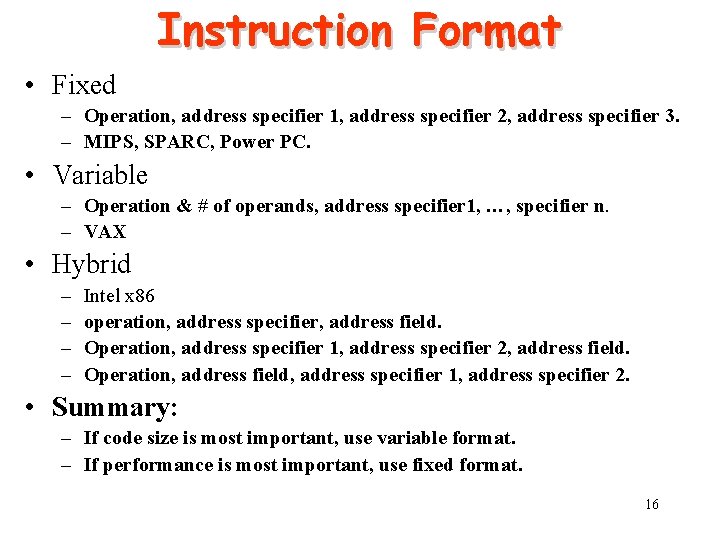

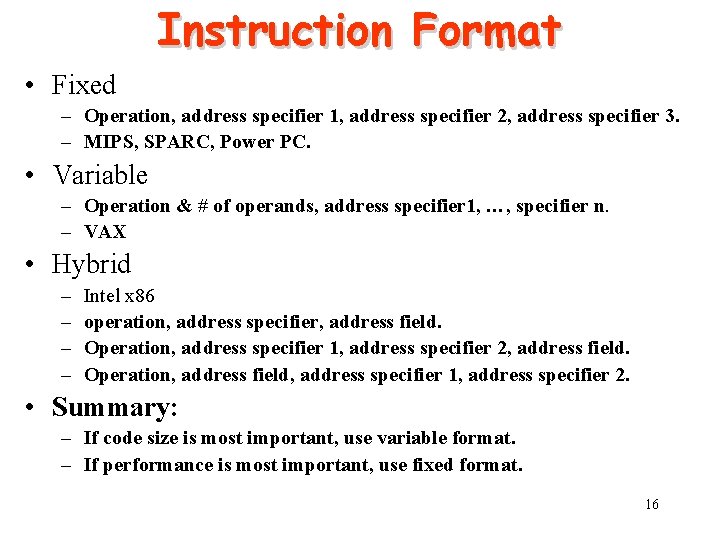

Instruction Format • Fixed – Operation, address specifier 1, address specifier 2, address specifier 3. – MIPS, SPARC, Power PC. • Variable – Operation & # of operands, address specifier 1, …, specifier n. – VAX • Hybrid – – Intel x 86 operation, address specifier, address field. Operation, address specifier 1, address specifier 2, address field. Operation, address field, address specifier 1, address specifier 2. • Summary: – If code size is most important, use variable format. – If performance is most important, use fixed format. 16

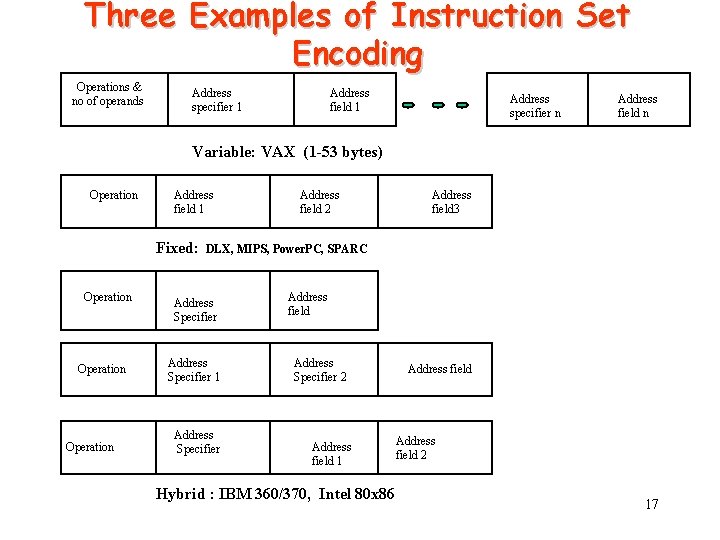

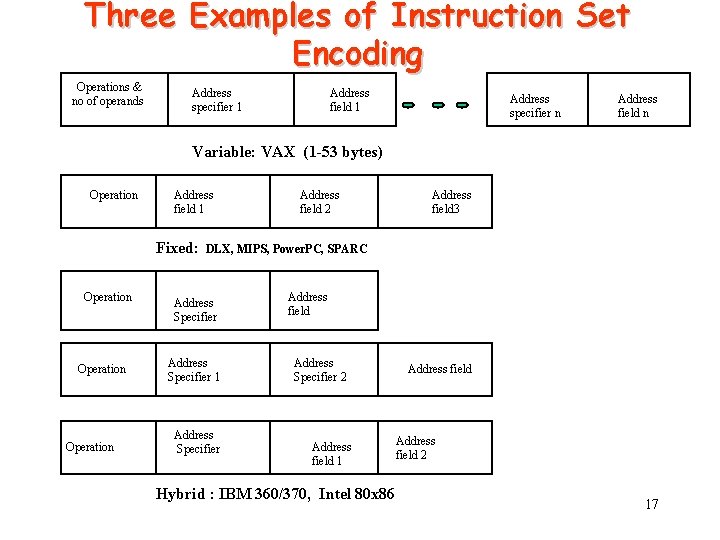

Three Examples of Instruction Set Encoding Operations & no of operands Address specifier 1 Address field 1 Address specifier n Address field n Variable: VAX (1 -53 bytes) Operation Address field 1 Fixed: Operation Address field 2 Address field 3 DLX, MIPS, Power. PC, SPARC Address Specifier 1 Address Specifier Address field Address Specifier 2 Address field 1 Hybrid : IBM 360/370, Intel 80 x 86 Address field 2 17

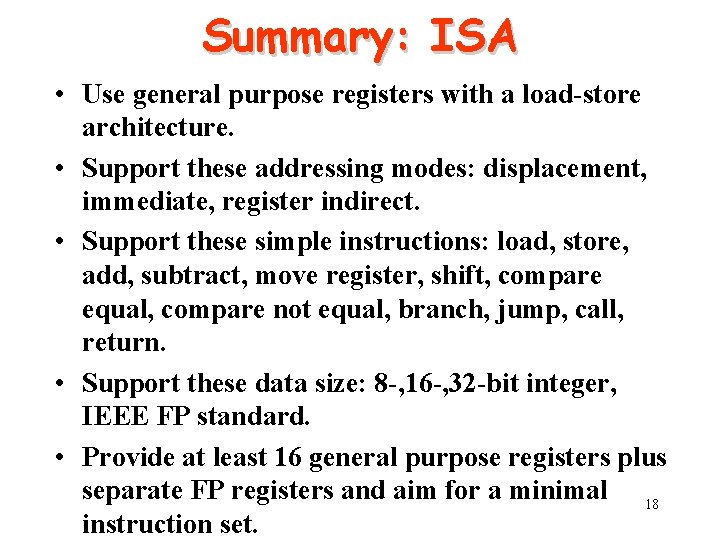

Summary: ISA • Use general purpose registers with a load-store architecture. • Support these addressing modes: displacement, immediate, register indirect. • Support these simple instructions: load, store, add, subtract, move register, shift, compare equal, compare not equal, branch, jump, call, return. • Support these data size: 8 -, 16 -, 32 -bit integer, IEEE FP standard. • Provide at least 16 general purpose registers plus separate FP registers and aim for a minimal 18 instruction set.

Alternative Architectures • Design alternative: – provide more powerful operations – goal is to reduce number of instructions executed – danger is a slower cycle time and/or a higher CPI –“The path toward operation complexity is thus fraught with peril. To avoid these problems, designers have moved toward simpler instructions” • Let’s look (briefly) at IA-32 19

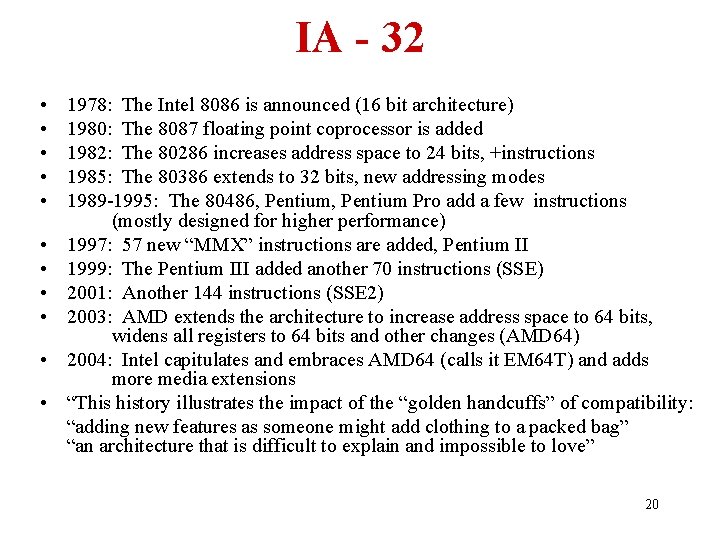

IA - 32 • • • 1978: The Intel 8086 is announced (16 bit architecture) 1980: The 8087 floating point coprocessor is added 1982: The 80286 increases address space to 24 bits, +instructions 1985: The 80386 extends to 32 bits, new addressing modes 1989 -1995: The 80486, Pentium Pro add a few instructions (mostly designed for higher performance) 1997: 57 new “MMX” instructions are added, Pentium II 1999: The Pentium III added another 70 instructions (SSE) 2001: Another 144 instructions (SSE 2) 2003: AMD extends the architecture to increase address space to 64 bits, widens all registers to 64 bits and other changes (AMD 64) 2004: Intel capitulates and embraces AMD 64 (calls it EM 64 T) and adds more media extensions “This history illustrates the impact of the “golden handcuffs” of compatibility: “adding new features as someone might add clothing to a packed bag” “an architecture that is difficult to explain and impossible to love” 20

IA-32 Overview • Complexity: – Instructions from 1 to 17 bytes long – one operand must act as both a source and destination – one operand can come from memory – complex addressing modes e. g. , “base or scaled index with 8 or 32 bit displacement” • Saving grace: – the most frequently used instructions are not too difficult to build – compilers avoid the portions of the architecture that are slow “what the 80 x 86 lacks in style is made up in quantity, making it beautiful from the right perspective” 21