RealTime Operating Systems ROS 01 Minor Embedded Systems

Real-Time Operating Systems ROS 01 Minor Embedded Systems versd@hr. nl brojz@hr. nl Week 2 Super loop construct with an ISR

Planning ROS 01 • • Week 1: Week 2: Week 3: Week 4: Week 5: Week 6: Week 7: Week 8: ROS 01 Week 2 Introduction – Hello World Super loop construct with an ISR Cooperative Scheduling Pre-emptive Scheduling Using TI-RTOS Schedulability Analyses, Priority Assignment Response Time Analyses Finalizing Final Assigment 2

Overview • The microcontroller – – – History Properties of the Cortex M 4 CPU Interrupt system Timers Direct Memory Access system • Superloop ‘scheduler’ ROS 01 Week 2 3

ARM History • Started in 1980 as a co-processor – ARM 1 architecture Difference to x 86? • Latest: – ARMv 8. 6 -A architecture (zie bijv. Cortex-A 77) ROS 01 Week 2 4

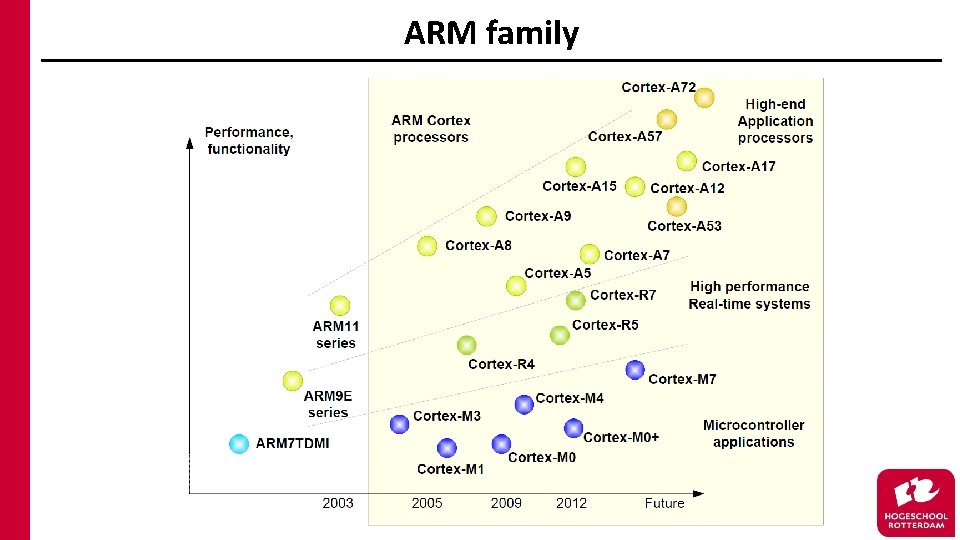

ARM family ROS 01 Week 2 5

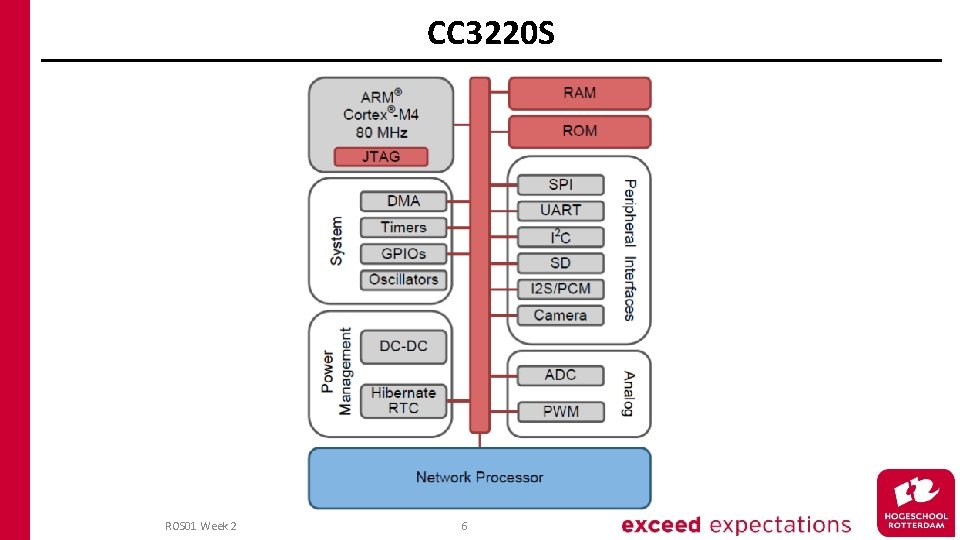

CC 3220 S ROS 01 Week 2 6

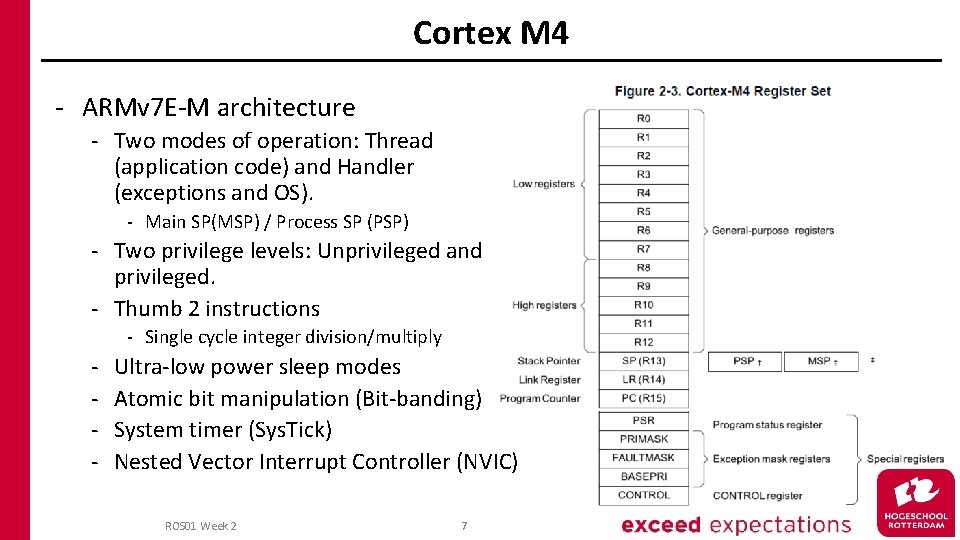

Cortex M 4 - ARMv 7 E-M architecture - Two modes of operation: Thread (application code) and Handler (exceptions and OS). - Main SP(MSP) / Process SP (PSP) - Two privilege levels: Unprivileged and privileged. - Thumb 2 instructions - Single cycle integer division/multiply - Ultra-low power sleep modes Atomic bit manipulation (Bit-banding) System timer (Sys. Tick) Nested Vector Interrupt Controller (NVIC) ROS 01 Week 2 7

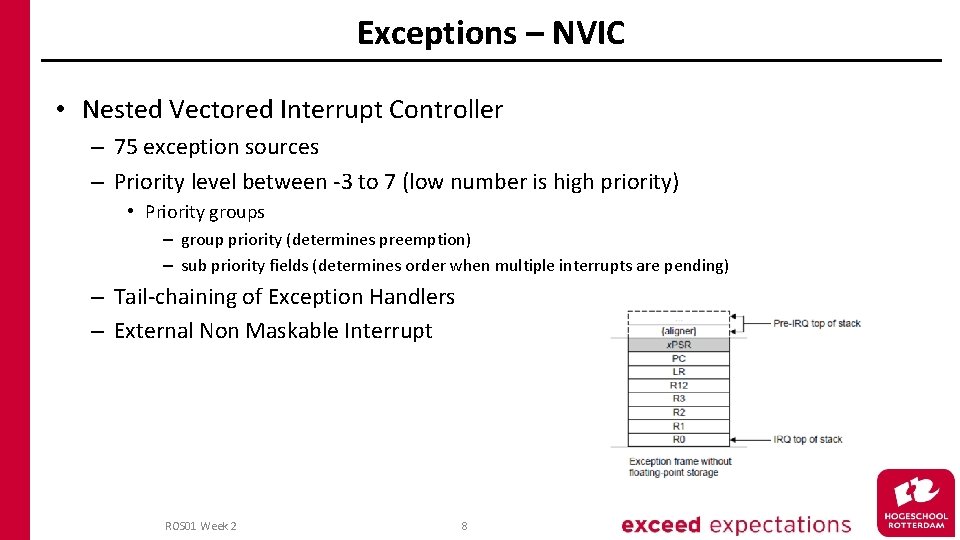

Exceptions – NVIC • Nested Vectored Interrupt Controller – 75 exception sources – Priority level between -3 to 7 (low number is high priority) • Priority groups – group priority (determines preemption) – sub priority fields (determines order when multiple interrupts are pending) – Tail-chaining of Exception Handlers – External Non Maskable Interrupt ROS 01 Week 2 8

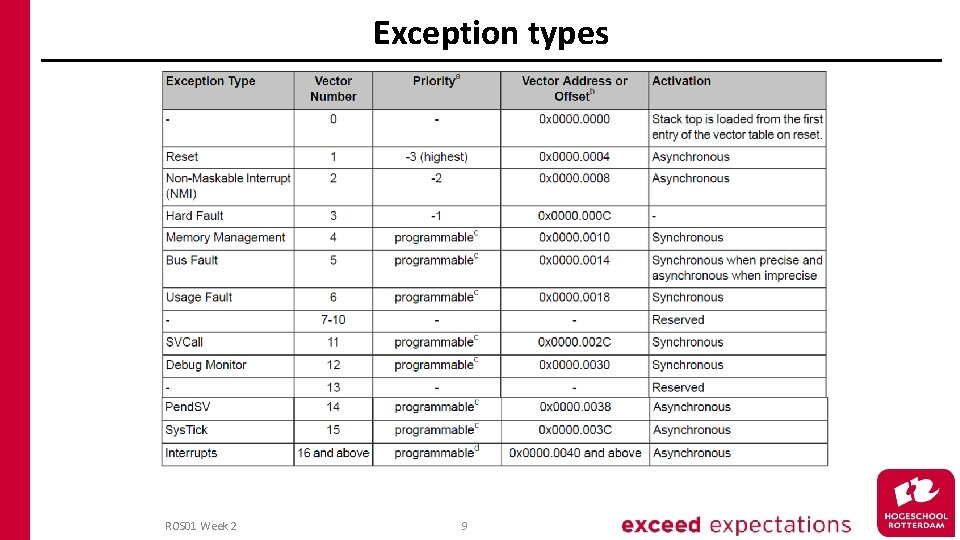

Exception types ROS 01 Week 2 9

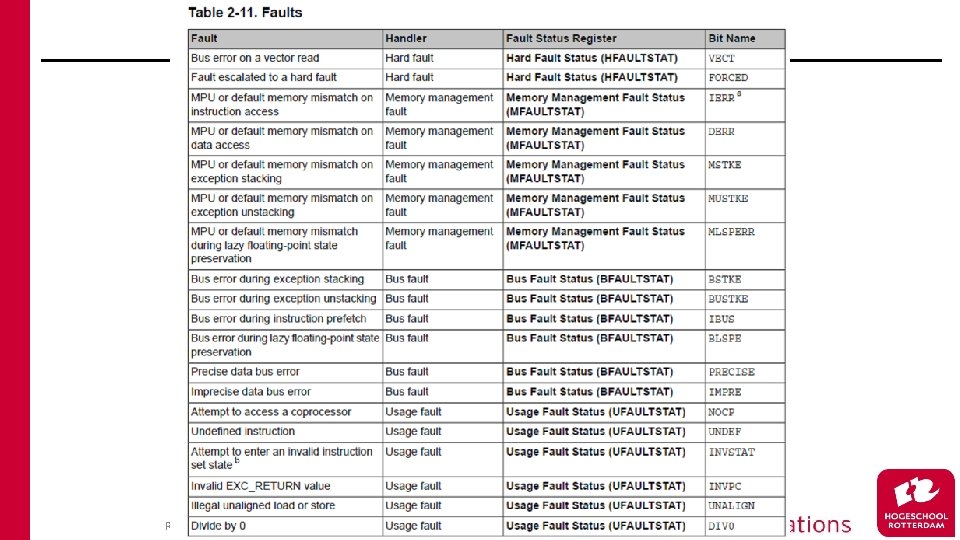

ROS 01 Week 2 10

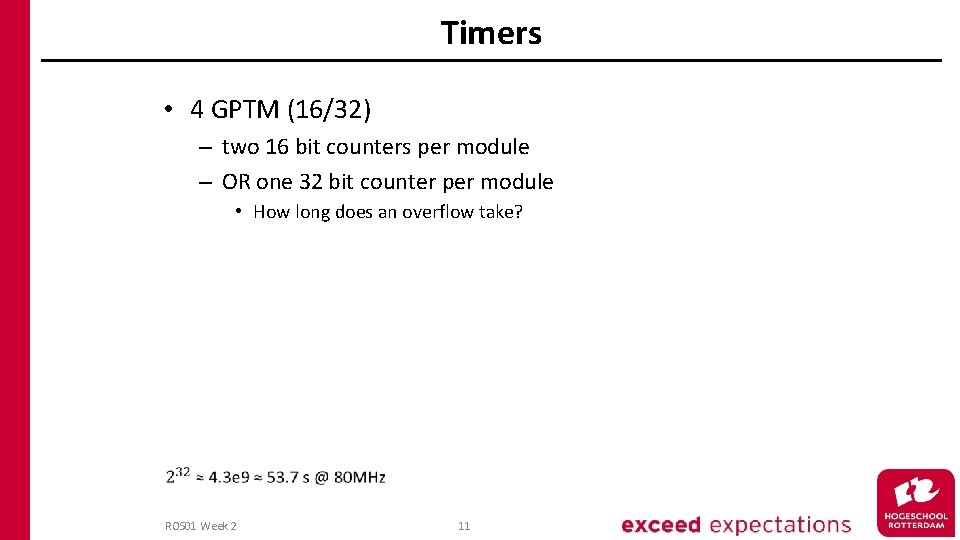

Timers • 4 GPTM (16/32) – two 16 bit counters per module – OR one 32 bit counter per module • How long does an overflow take? ROS 01 Week 2 11

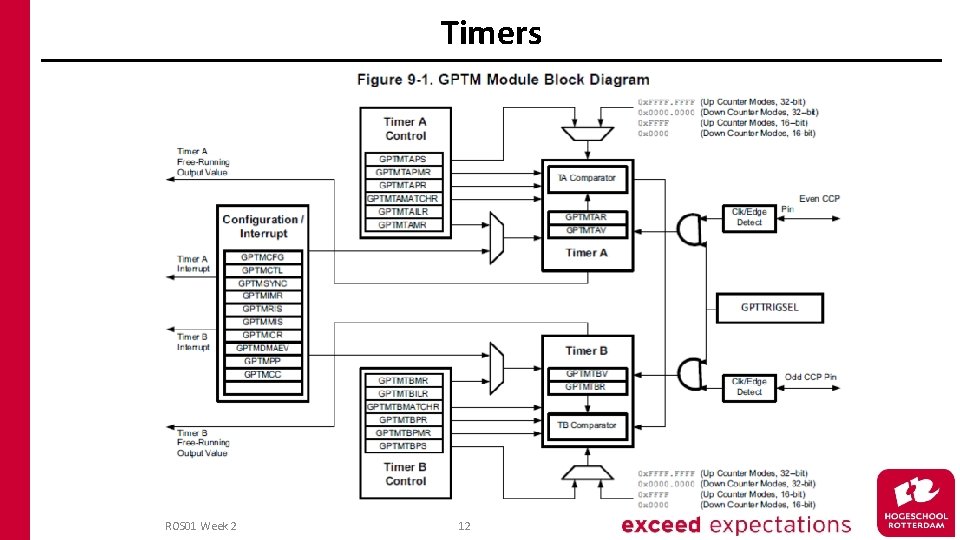

Timers ROS 01 Week 2 12

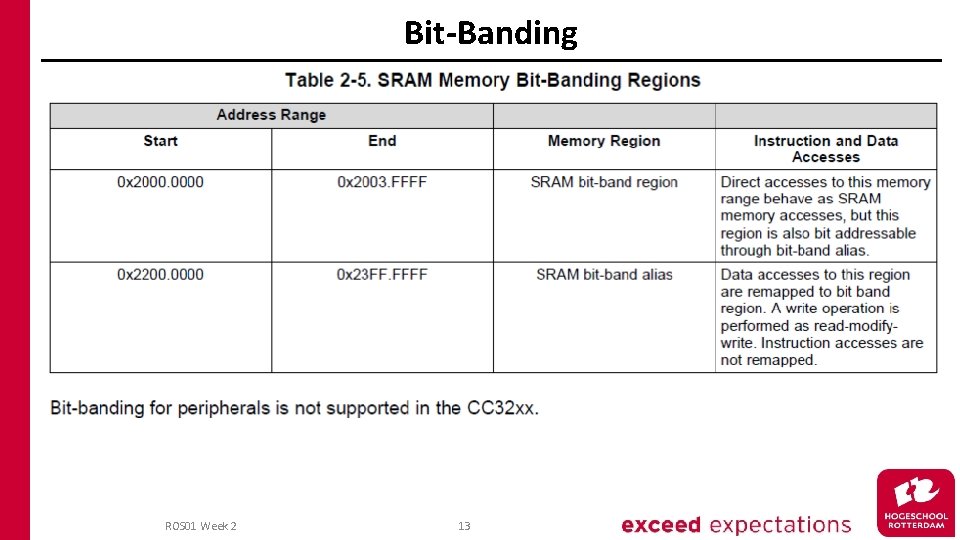

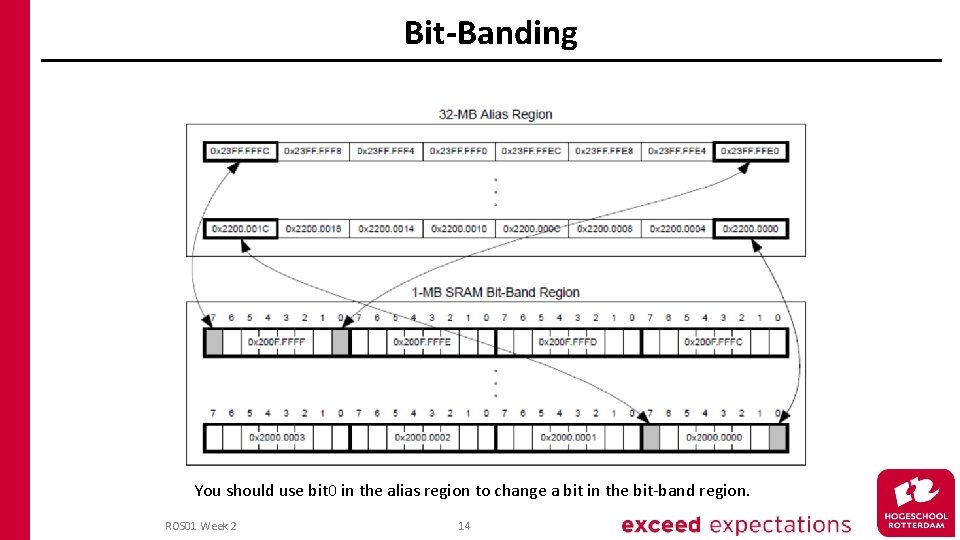

Bit-Banding ROS 01 Week 2 13

Bit-Banding You should use bit 0 in the alias region to change a bit in the bit-band region. ROS 01 Week 2 14

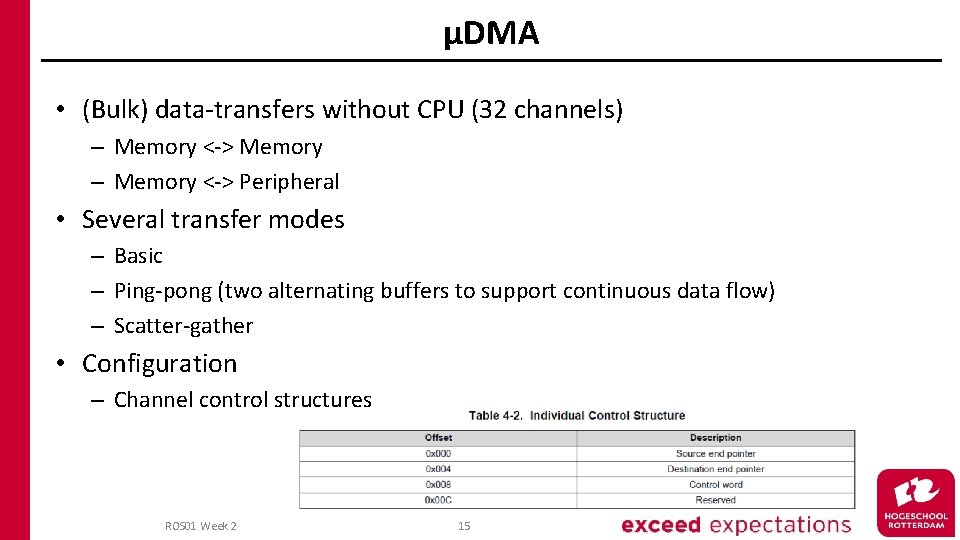

µDMA • (Bulk) data-transfers without CPU (32 channels) – Memory <-> Memory – Memory <-> Peripheral • Several transfer modes – Basic – Ping-pong (two alternating buffers to support continuous data flow) – Scatter-gather • Configuration – Channel control structures ROS 01 Week 2 15

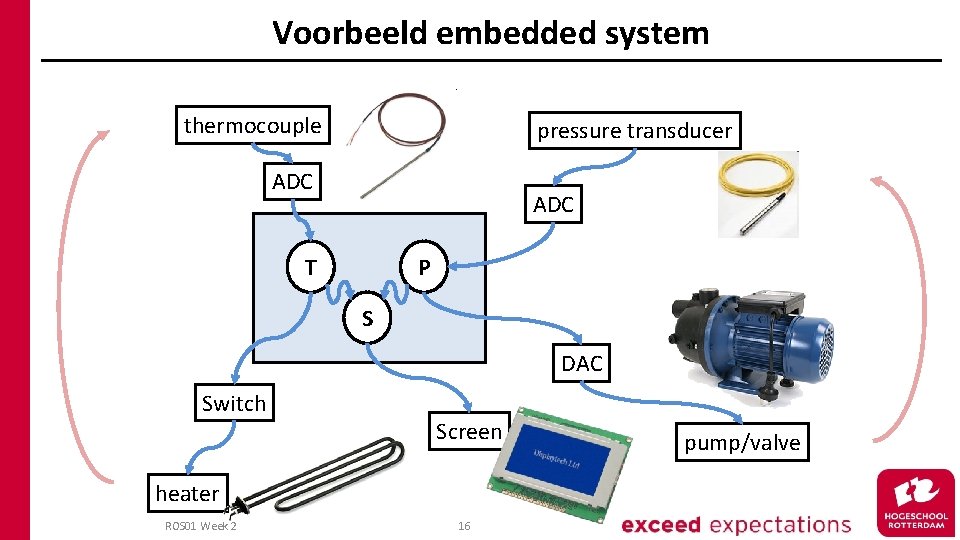

Voorbeeld embedded system thermocouple pressure transducer ADC T P S DAC Switch Screen heater ROS 01 Week 2 16 pump/valve

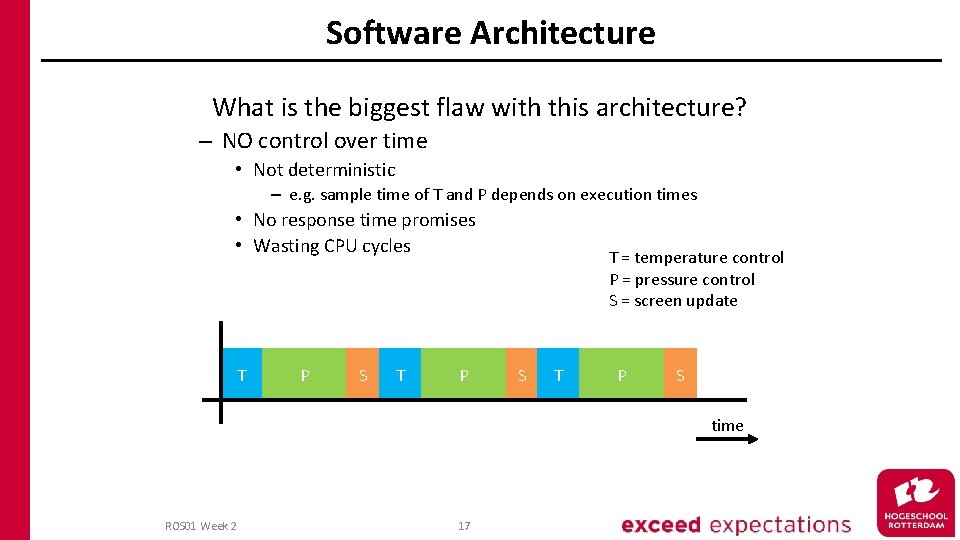

Software Architecture What is the biggest flaw with this architecture? – NO control over time • Not deterministic – e. g. sample time of T and P depends on execution times • No response time promises • Wasting CPU cycles T P S T P T = temperature control P = pressure control S = screen update S T P S time ROS 01 Week 2 17

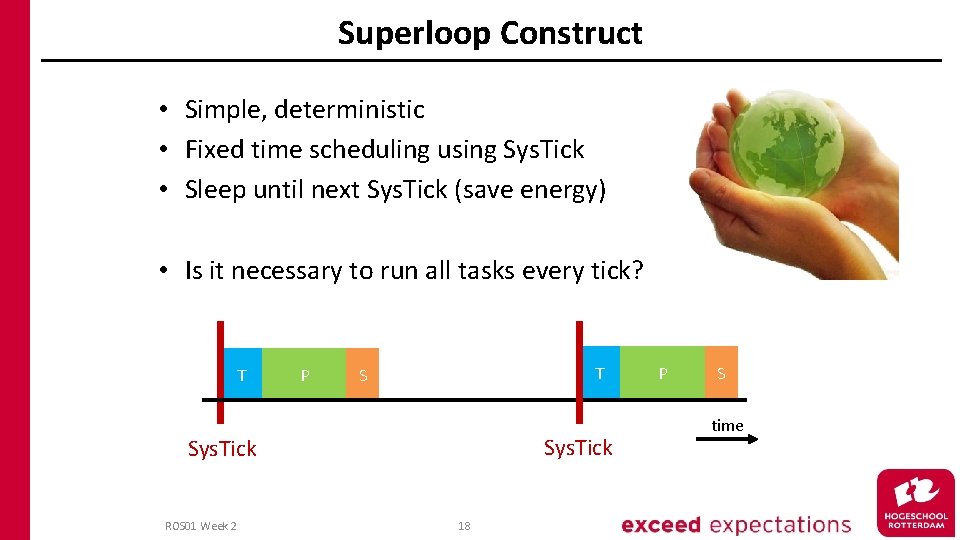

Superloop Construct • Simple, deterministic • Fixed time scheduling using Sys. Tick • Sleep until next Sys. Tick (save energy) • Is it necessary to run all tasks every tick? T P T S Sys. Tick ROS 01 Week 2 18 P S time

- Slides: 18