Readout Controller ROC Status Report October 20 Radu

Readout Controller (ROC) Status Report October 20 Radu Coliban

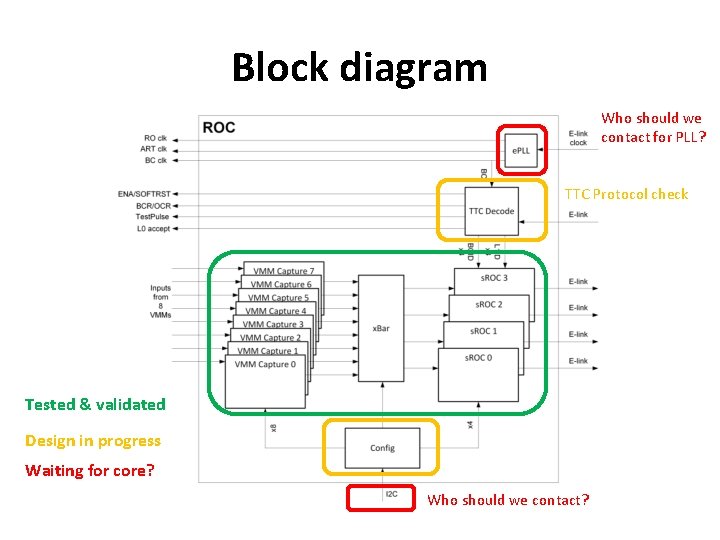

Block diagram Who should we contact for PLL? TTC Protocol check Tested & validated Design in progress Waiting for core? Who should we contact?

![Input/Output Name Elnk_BCclk Elnk_TTC Elnk_data[0: 3] ROC_I 2 C_SCL ROC_I 2 C_SDA reset TDS_BCclk[0: Input/Output Name Elnk_BCclk Elnk_TTC Elnk_data[0: 3] ROC_I 2 C_SCL ROC_I 2 C_SDA reset TDS_BCclk[0:](http://slidetodoc.com/presentation_image/22aaa56177ac0f61c67609b041fadbc8/image-3.jpg)

Input/Output Name Elnk_BCclk Elnk_TTC Elnk_data[0: 3] ROC_I 2 C_SCL ROC_I 2 C_SDA reset TDS_BCclk[0: 3] In, Out or I/O in in out in i/o in out 2 2 8 1 1 1 8 SLVS CMOS SLVS TDS_BCR[0: 3] VMM_d 0[0: 7] VMM_d 1[0: 7] VMM_ROclk[0: 7] out in in out 8 16 16 16 SLVS VMM_ARTclk[0: 7 out ] VMM_BCclk[0: 7] out 16 SLVS VMM_BCR[0: 7] VMM_L 0 A[0: 7] VMM_TP[0: 7] VMM_ENA[0: 7] SEU TEST_MODE SCAN_IN SCAN_OUT SCAN_EN 16 16 1 1 1 SLVS CMOS CMOS out out out in in Dim Type of Signal or Max/Min Description ROC clk, from GBT TTC, from GBT s. ROC[0. . . 3] L 1 data I 2 C clock I 2 C data from SCA DIO 40 MHz reference input to SER and BC clock Bunch Crossing Reset Serial data from VMM Data out and 6 -bit ADC clock, 160 MHz Address in Real Time (ART) clock Bunch Crossing clock , Advances 12 -bit Graycode BC counter Bunch Crossing Reset Level 0 Accept Test Pulse Clock Soft reset from TTC Single Event Upset

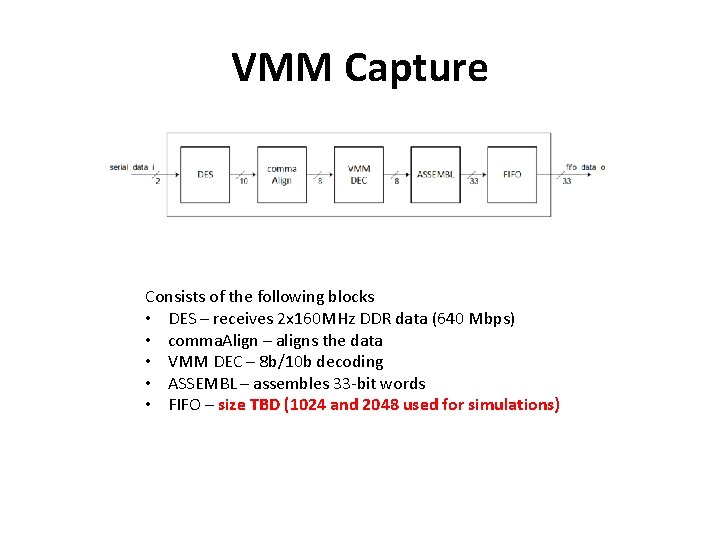

VMM Capture Consists of the following blocks • DES – receives 2 x 160 MHz DDR data (640 Mbps) • comma. Align – aligns the data • VMM DEC – 8 b/10 b decoding • ASSEMBL – assembles 33 -bit words • FIFO – size TBD (1024 and 2048 used for simulations)

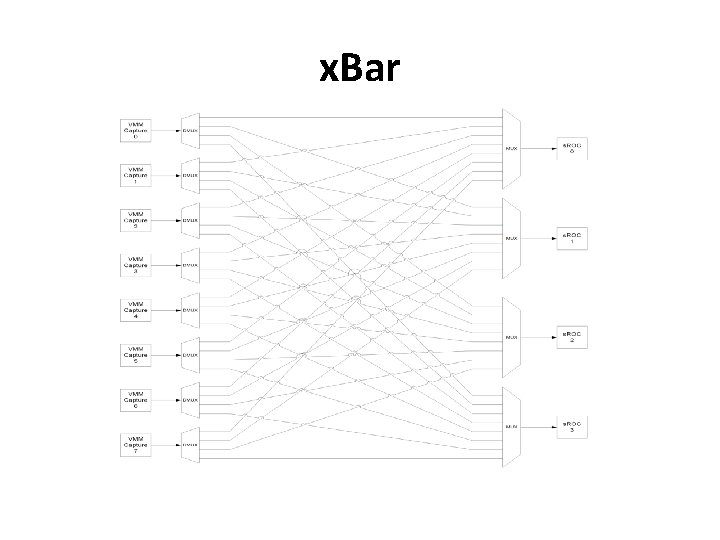

x. Bar

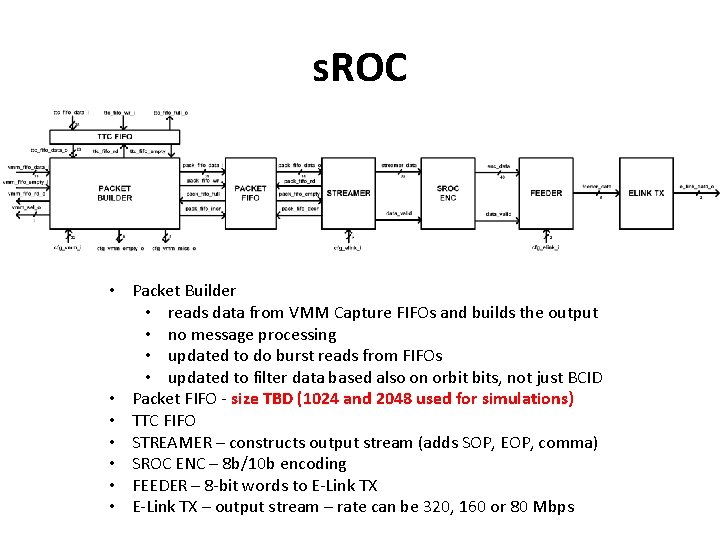

s. ROC • Packet Builder • reads data from VMM Capture FIFOs and builds the output • no message processing • updated to do burst reads from FIFOs • updated to filter data based also on orbit bits, not just BCID • Packet FIFO - size TBD (1024 and 2048 used for simulations) • TTC FIFO • STREAMER – constructs output stream (adds SOP, EOP, comma) • SROC ENC – 8 b/10 b encoding • FEEDER – 8 -bit words to E-Link TX • E-Link TX – output stream – rate can be 320, 160 or 80 Mbps

Simulation • Simulation of individual sub-blocks • Simulation of the entire design for validation – Emulation of TTC decode and Config blocks • Test scenarios in order to determine the sizes of the FIFOs

Simulation • Worst case scenario – Phase 2 - Input packet rate: 1 MHz Mean packet length: 20 hits Trigger rate: 400 k. Hz Trigger latency: 60 us X-Bar connections: 2 x VMM Capture -> 1 x s. ROC E-Link output rate: 320 Mbps (effectively 256 Mbps)

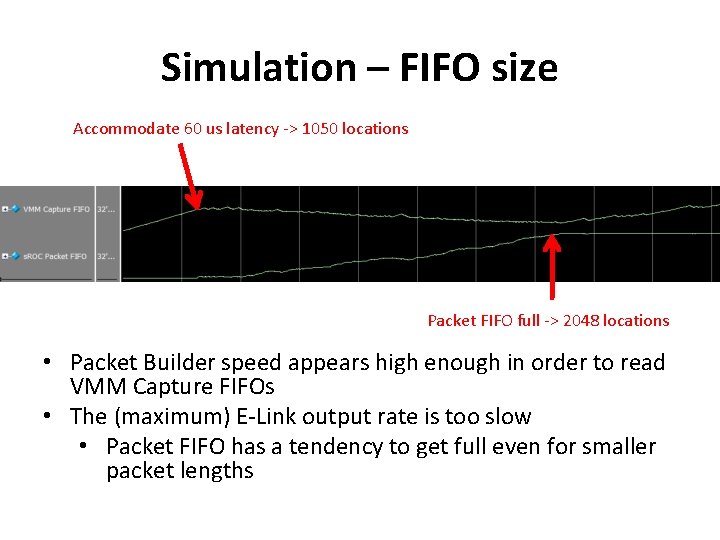

Simulation – FIFO size Accommodate 60 us latency -> 1050 locations Packet FIFO full -> 2048 locations • Packet Builder speed appears high enough in order to read VMM Capture FIFOs • The (maximum) E-Link output rate is too slow • Packet FIFO has a tendency to get full even for smaller packet lengths

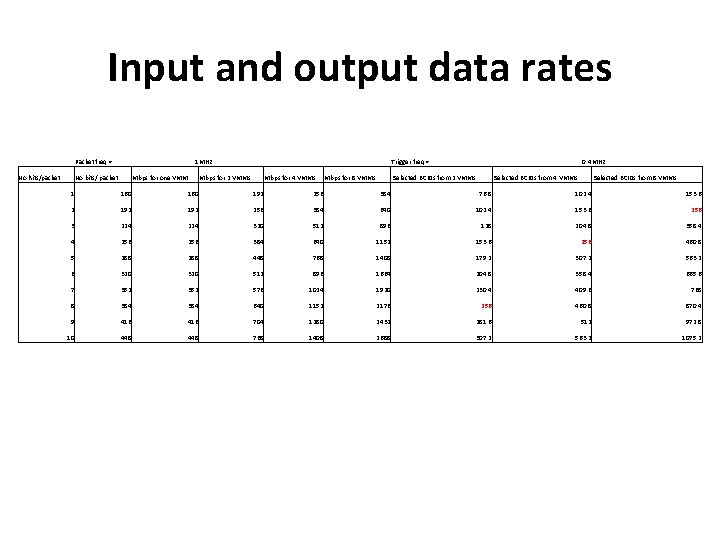

Input and output data rates Packet freq = No hits/packet 1 MHz No bits/ packet Mbps for one VMM Trigger freq = Mbps for 2 VMMs Mbps for 4 VMMs Mbps for 8 VMMs 0. 4 MHz Selected BCIDs from 2 VMMs Selected BCIDs from 4 VMMs Selected BCIDs from 8 VMMs 1 160 192 256 384 76. 8 102. 4 153. 6 2 192 256 384 640 102. 4 153. 6 256 3 224 320 512 896 128 204. 8 358. 4 4 256 384 640 1152 153. 6 256 460. 8 5 288 448 768 1408 179. 2 307. 2 563. 2 6 320 512 896 1664 204. 8 358. 4 665. 6 7 352 576 1024 1920 230. 4 409. 6 768 8 384 640 1152 2176 256 460. 8 870. 4 9 416 704 1280 2432 281. 6 512 972. 8 10 448 768 1408 2688 307. 2 563. 2 1075. 2

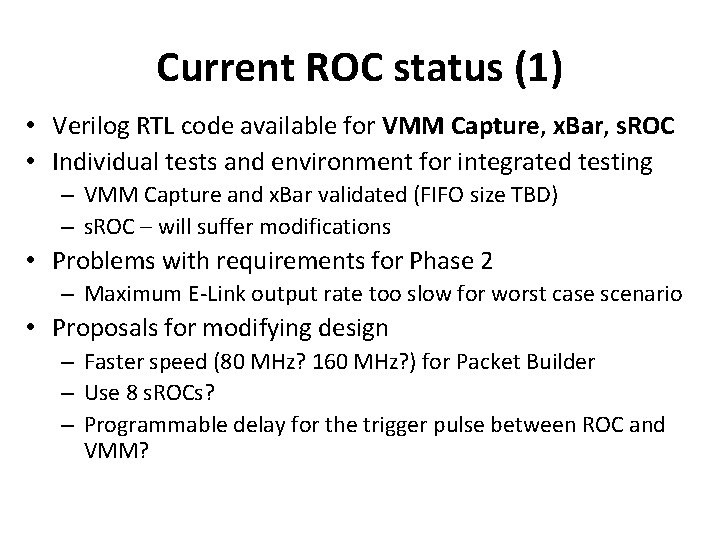

Current ROC status (1) • Verilog RTL code available for VMM Capture, x. Bar, s. ROC • Individual tests and environment for integrated testing – VMM Capture and x. Bar validated (FIFO size TBD) – s. ROC – will suffer modifications • Problems with requirements for Phase 2 – Maximum E-Link output rate too slow for worst case scenario • Proposals for modifying design – Faster speed (80 MHz? 160 MHz? ) for Packet Builder – Use 8 s. ROCs? – Programmable delay for the trigger pulse between ROC and VMM?

Current ROC status (2) • Design in progress for TTC Decode and Config -> early November • e. PLL & I 2 C blocks to be received and integrated • Undergoing preliminary synthesis – Check timing violations – Estimating size & floor plan -> end of October / early November • Memory generation from the guys at CERN? Who should we contact?

- Slides: 12