Read Only Read Write Program counter PC ALU

![JUMP- הוספת הטיפול ב Instruction [25– 0] 26 Shift left 2 Jump address [31– JUMP- הוספת הטיפול ב Instruction [25– 0] 26 Shift left 2 Jump address [31–](https://slidetodoc.com/presentation_image_h2/88fb7642e02d4f3dc8c776dbb64669e9/image-24.jpg)

![? מתי מגיע השעון Instruction [25– 0] 26 Shift left 2 Jump address [31– ? מתי מגיע השעון Instruction [25– 0] 26 Shift left 2 Jump address [31–](https://slidetodoc.com/presentation_image_h2/88fb7642e02d4f3dc8c776dbb64669e9/image-26.jpg)

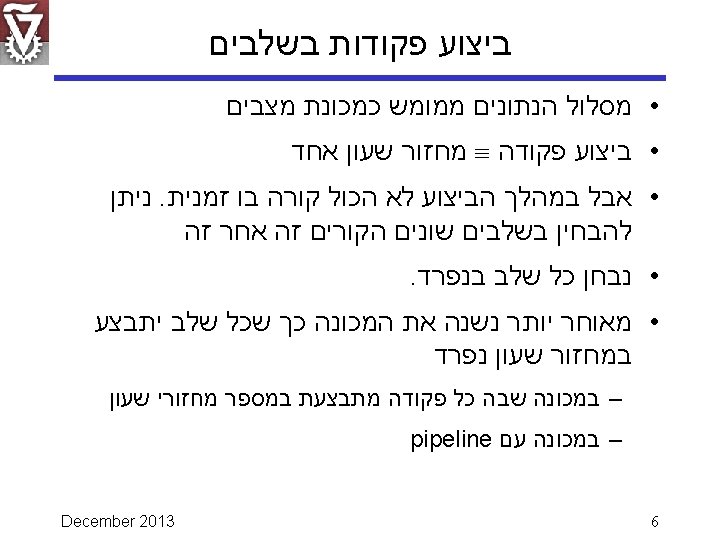

- Slides: 30

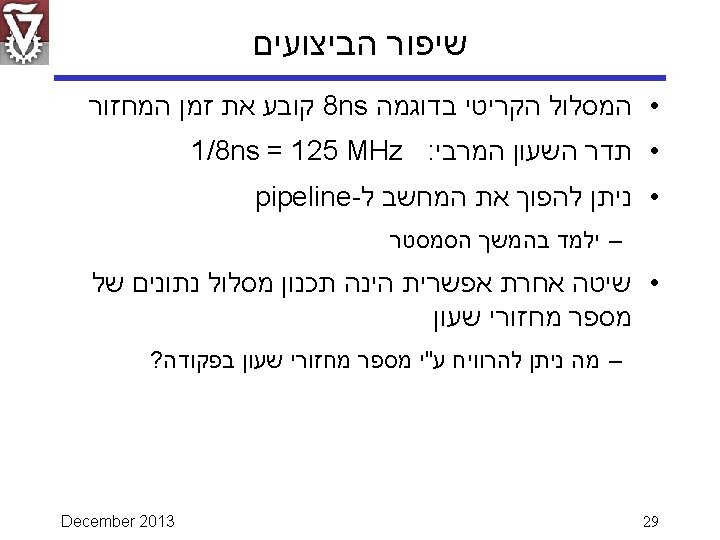

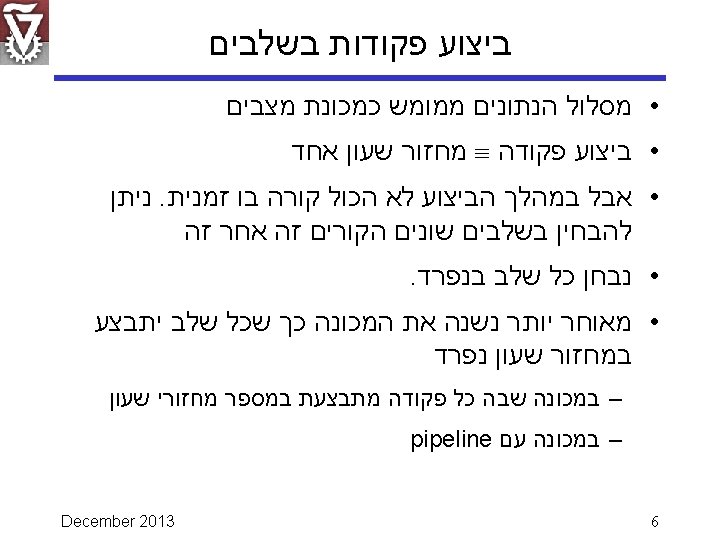

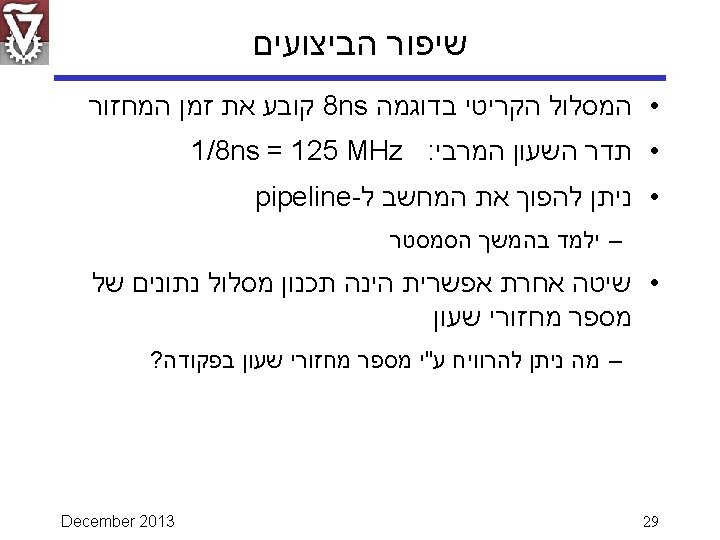

מרכיבי מסלול הנתונים ( חוץ מזמן טעינת תכנית חדשה , Read Only) • זיכרון פקודות (Read / Write) • זיכרון נתונים • רגיסטרים Program counter (PC) • ALU • Data PC Address Instruction memory Register # Registers Register # ALU Address Data memory Register # Data December 2013 1

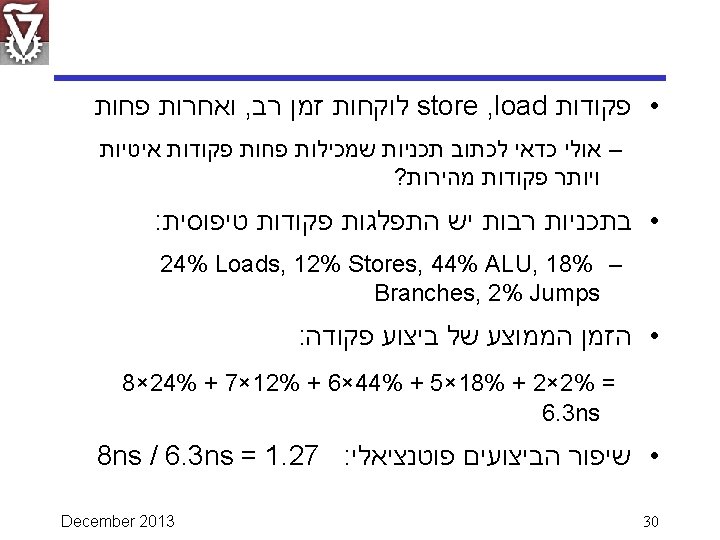

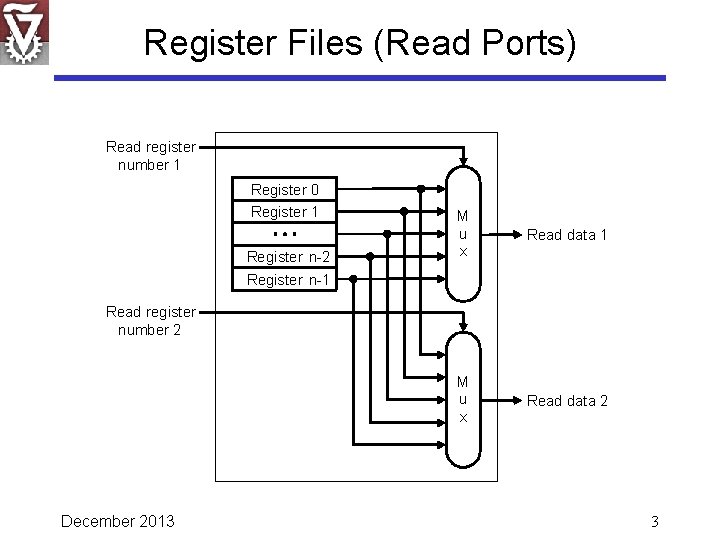

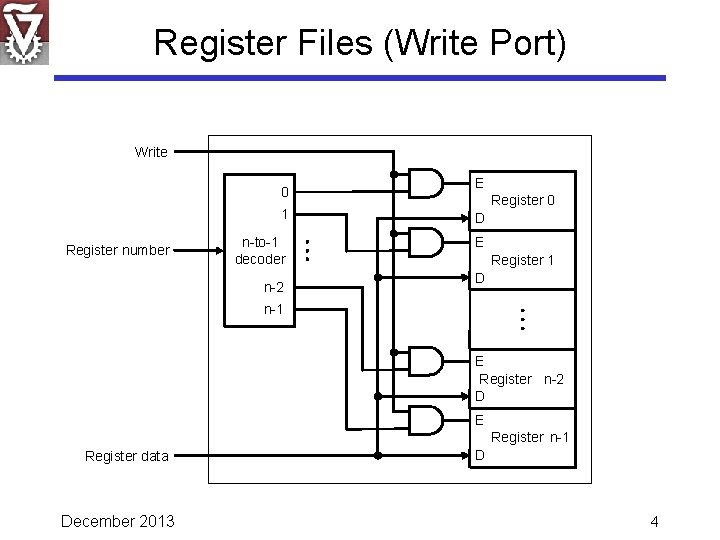

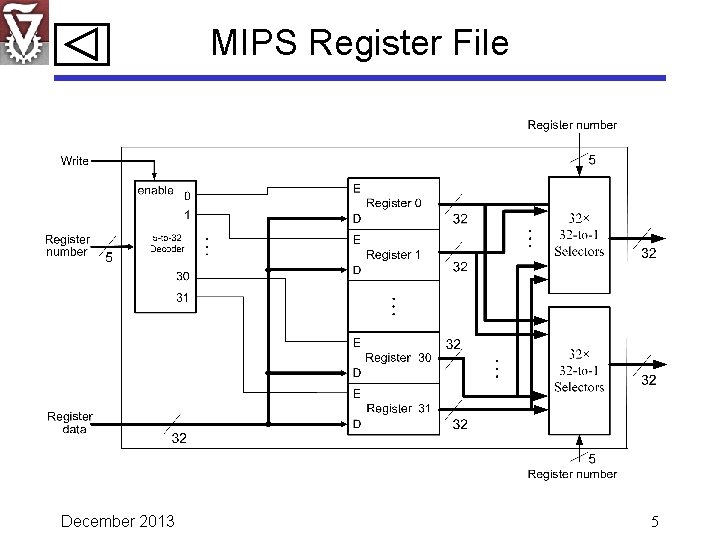

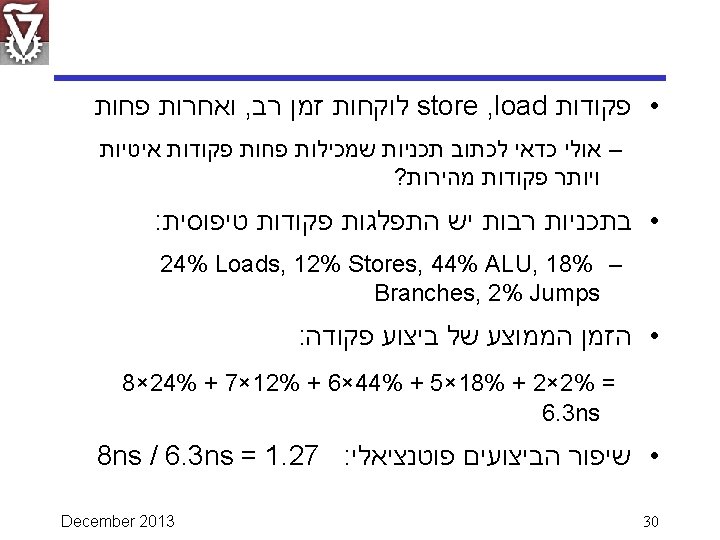

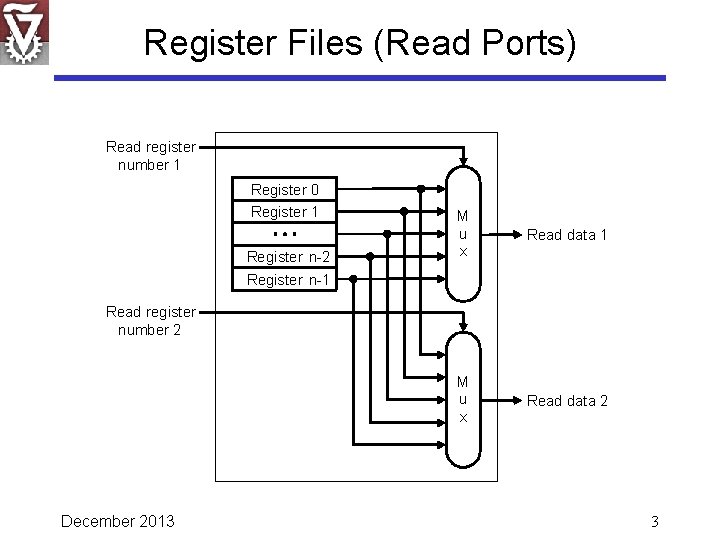

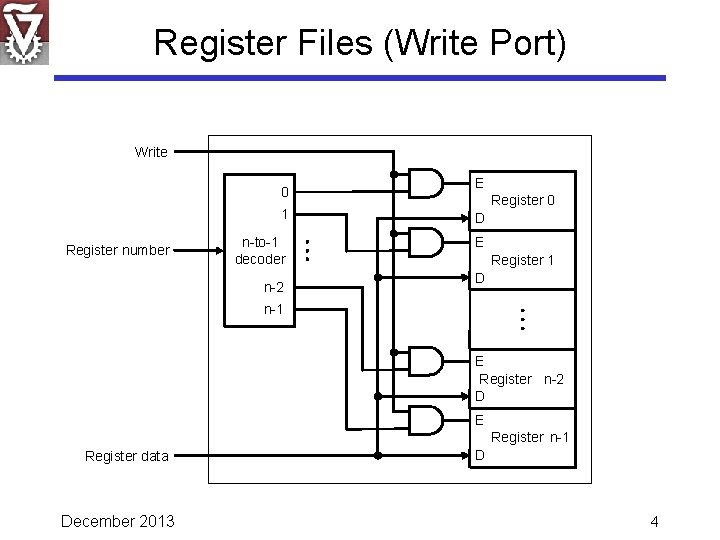

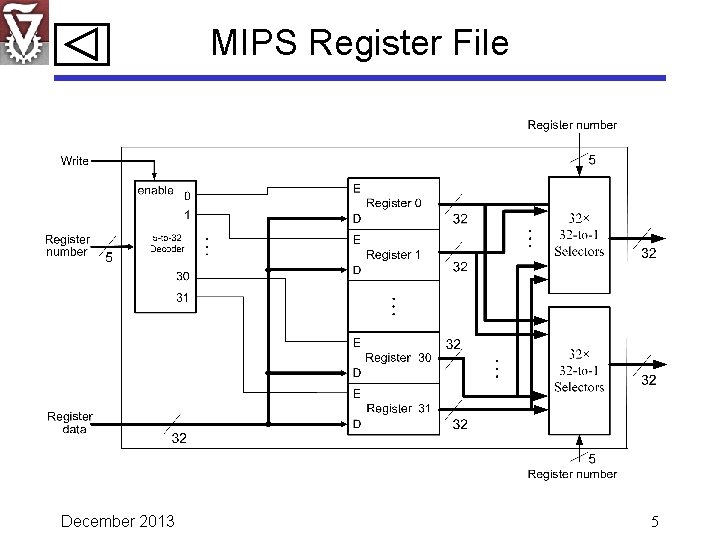

A General Register File כתובת רגיסטר לקריאה כתובת רגיסטר לכתיבה Register number Write Register number enable 0 E 1 D log n to-n decoder n– 2 Register 0 E Register 1 n-to-1 selector D תוכן נקרא n– 1 E Register n – 2 D Register data תוכן לכתיבה n-to-1 selector E Register n – 1 D Register number כתובת רגיסטר לקריאה December 2013 2

Register Files (Read Ports) Read register number 1 Register 0 Register 1 Register n-2 Register n-1 M u x Read data 2 Read register number 2 December 2013 3

Register Files (Write Port) Write 0 Register number E Register 0 1 D n-to-1 decoder E n-2 Register 1 D n-1 E Register n-2 D E Register n-1 Register data December 2013 D 4

MIPS Register File December 2013 5

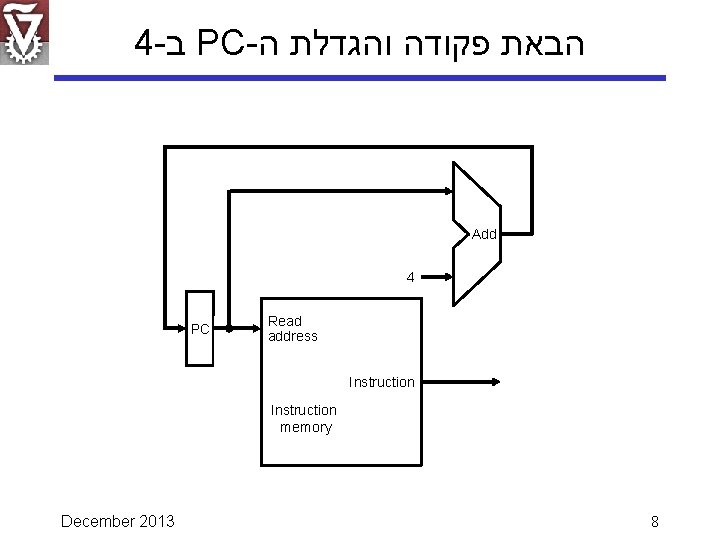

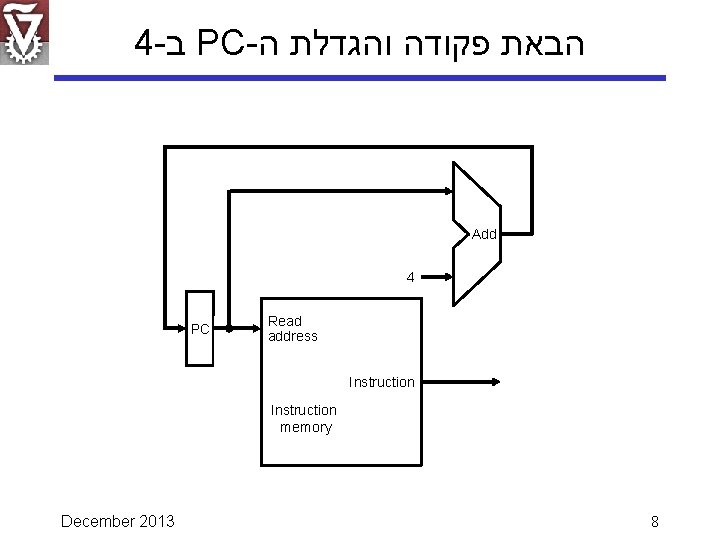

4 - ב PC- הבאת פקודה והגדלת ה Add 4 PC Read address Instruction memory December 2013 8

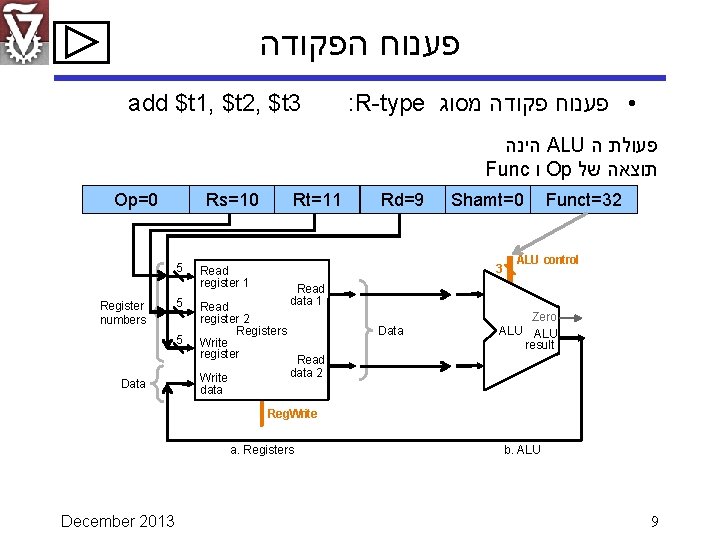

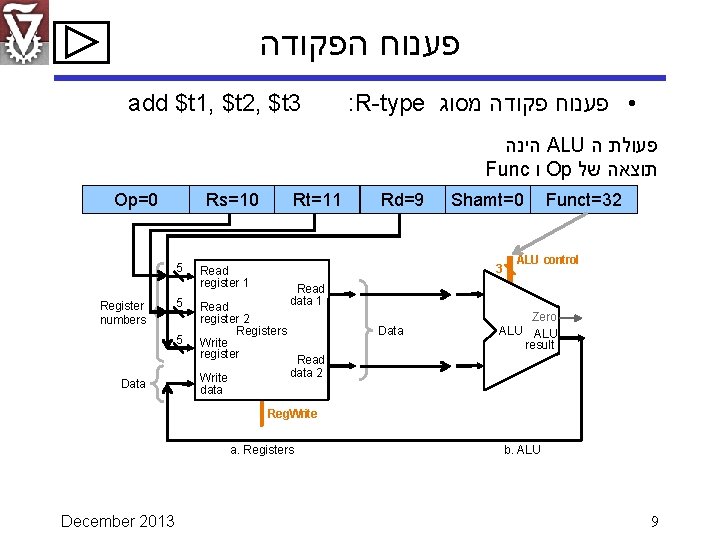

פענוח הפקודה add $t 1, $t 2, $t 3 : R-type • פענוח פקודה מסוג הינה ALU פעולת ה Func ו Op תוצאה של Op=0 Rs=10 5 Register numbers 5 5 Data Rt=11 Shamt=0 3 Read register 1 Read register 2 Registers Write register Write data Rd=9 Funct=32 ALU control Read data 1 Data Zero ALU result Read data 2 Reg. Write a. Registers December 2013 b. ALU 9

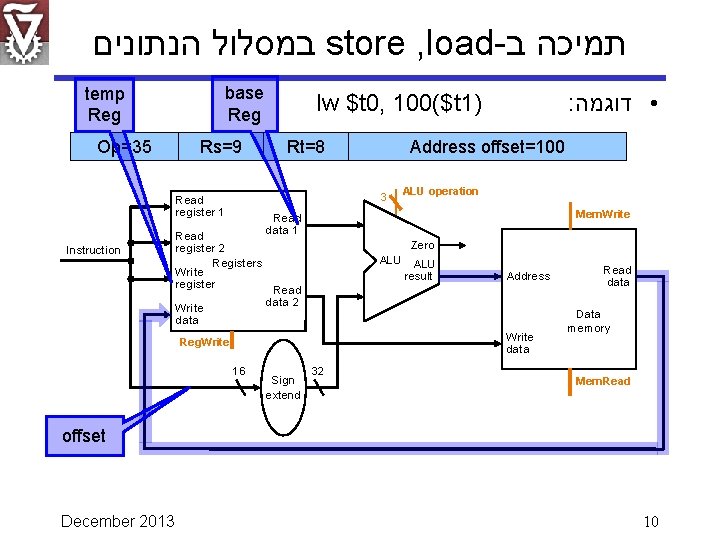

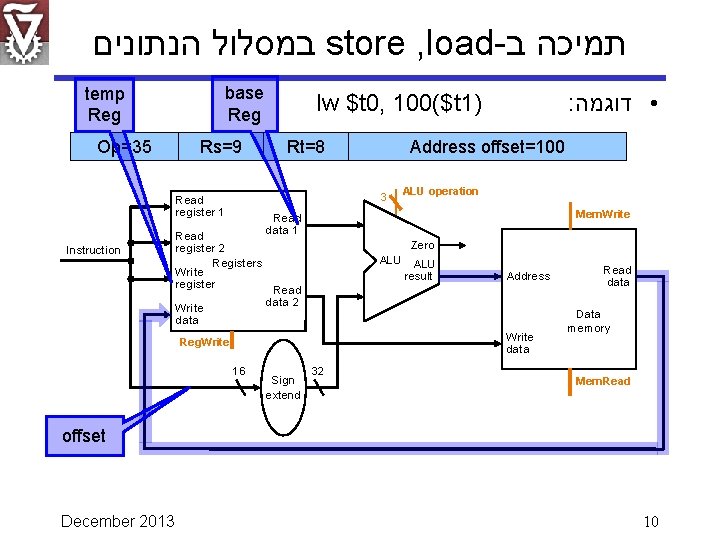

במסלול הנתונים store , load- תמיכה ב base Reg temp Reg Op=35 Rs=9 Instruction Rt=8 Address offset=100 3 Read register 1 Read register 2 Registers Write register Write data : • דוגמה lw $t 0, 100($t 1) ALU operation Mem. W rite Read data 1 Zero ALU result Address Read data 2 Write data Reg. Write 16 Sign extend 32 Read data Data memory Mem. Read offset December 2013 10

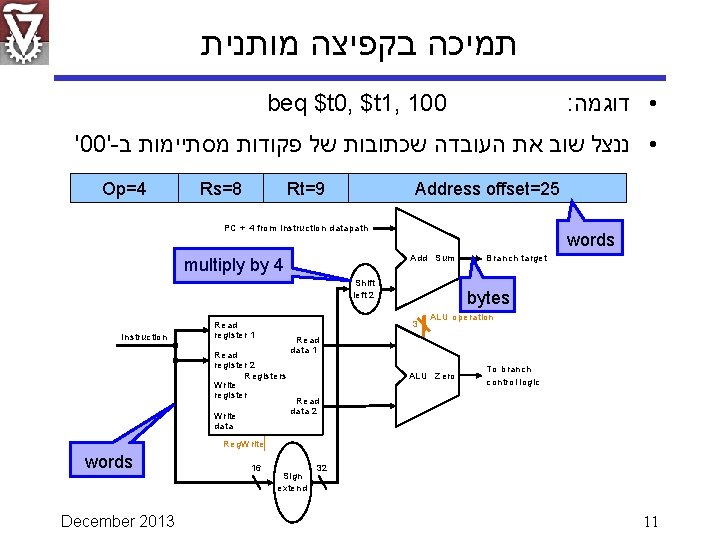

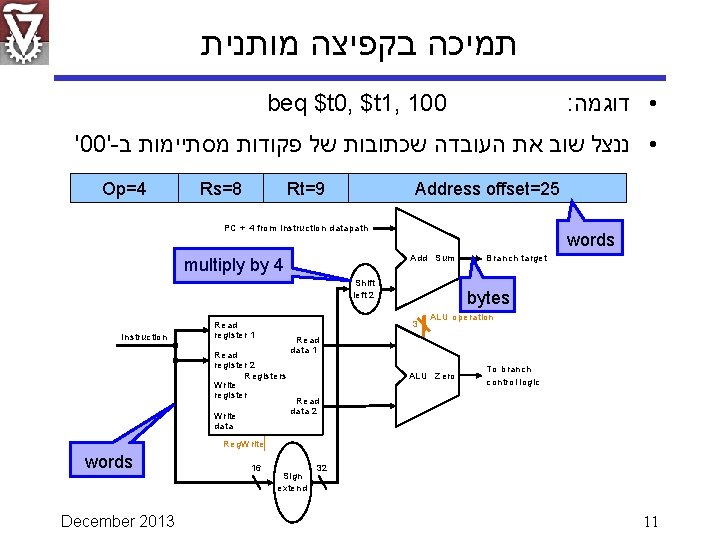

תמיכה בקפיצה מותנית : • דוגמה beq $t 0, $t 1, 100 '00'- • ננצל שוב את העובדה שכתובות של פקודות מסתיימות ב Op=4 Rs=8 Rt=9 Address offset=25 PC + 4 from instruction datapath words Add Sum multiply by 4 Shift left 2 Instruction Read register 2 Registers W rite register W rite data bytes 3 Read register 1 Branch target ALU operation Read data 1 ALU Zero To branch control logic Read data 2 Reg. W rite words December 2013 16 S ign extend 32 11

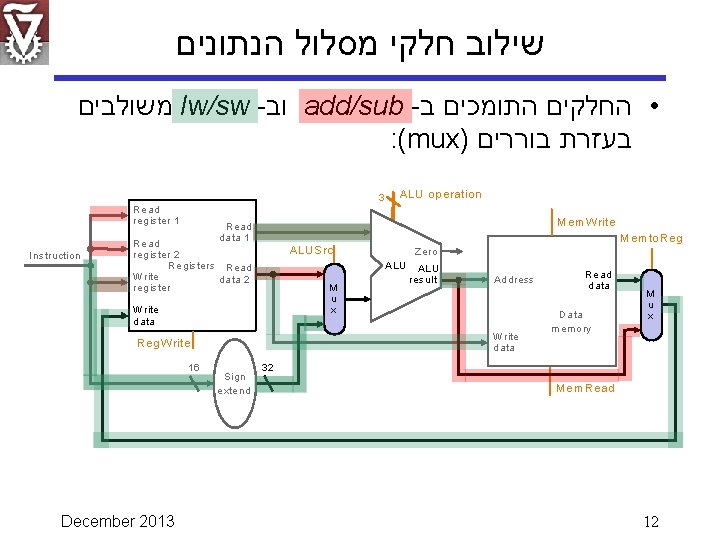

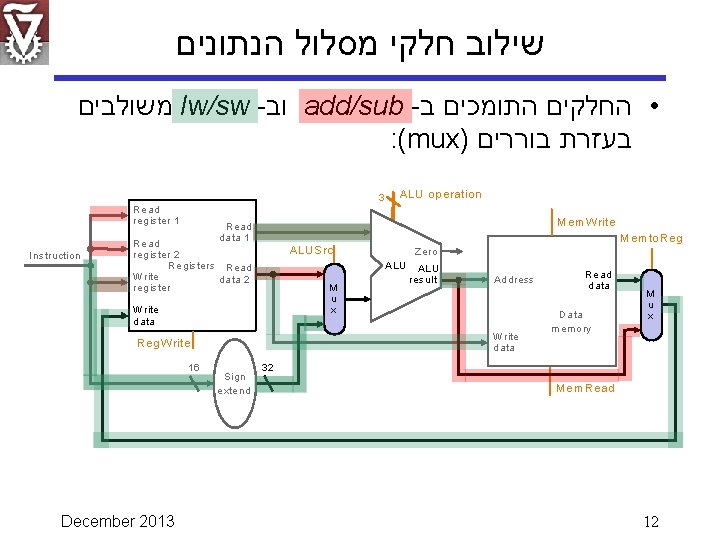

שילוב חלקי מסלול הנתונים משולבים lw/sw - וב add/sub - • החלקים התומכים ב : (mux) בעזרת בוררים 3 R e ad reg ister 1 Instruction M e m W rite Read da ta 1 R e ad reg ister 2 R egisters Read W rite da ta 2 reg ister Ze ro ALU M u x ALU result A ddress W rite d ata R eg W rite 16 M em to R eg A LU S rc W rite d ata December 2013 A L U op e ration Sign e xte nd Read d ata Data m em ory M u x 32 M e m R ea d 12

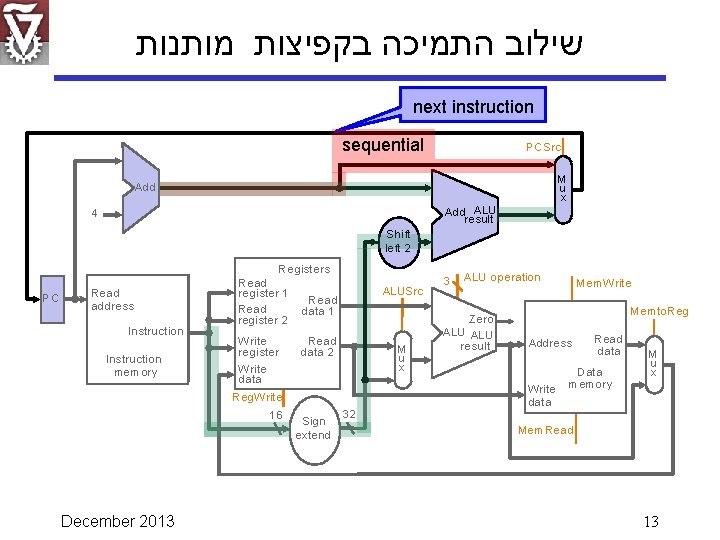

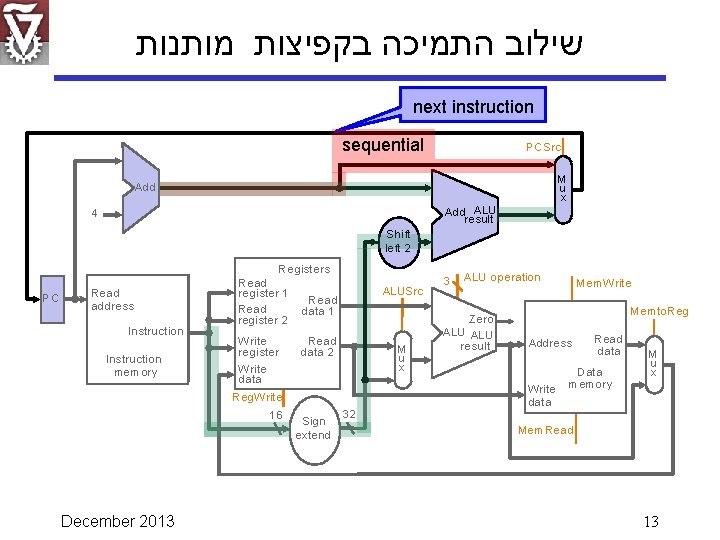

שילוב התמיכה בקפיצות מותנות next instruction sequential PCSrc M u x Add A LU result 4 Shift left 2 PC Read address Instruction memory Registers Read register 1 Read data 1 register 2 W rite register ALUSrc Read data 2 M u x W rite data December 2013 A LU operation Zero A LU ALU result Sign extend Mem. Write Memto. Reg Address Write data Reg. W rite 16 3 Read data D ata memory M u x 32 Mem. Read 13

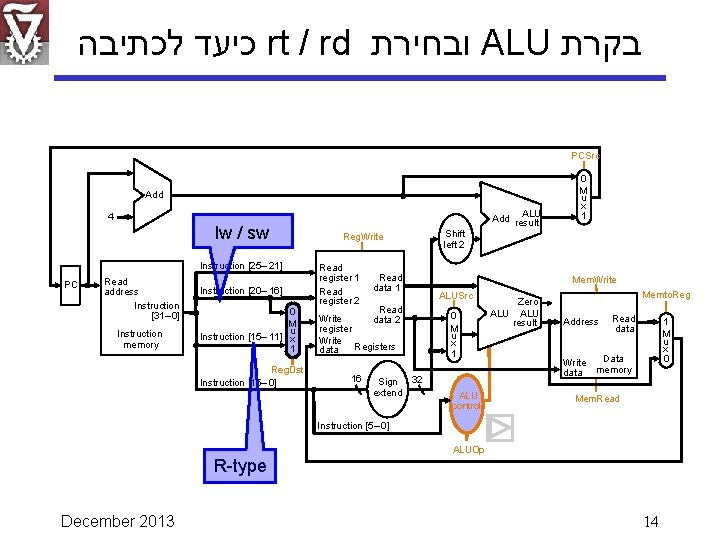

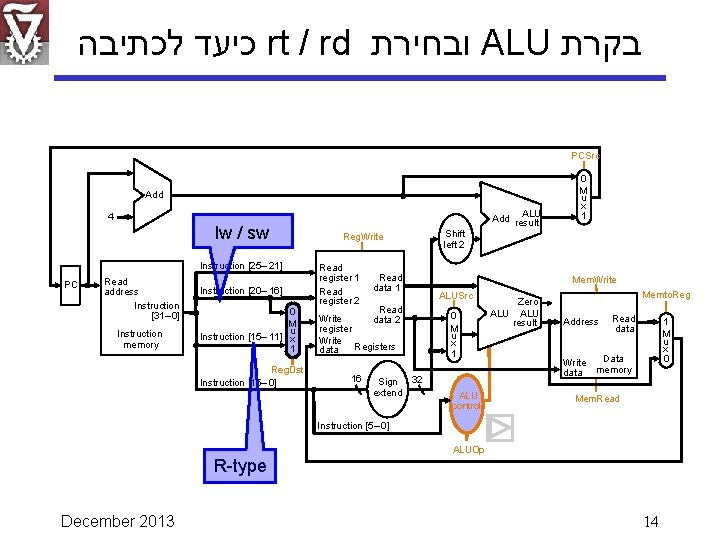

כיעד לכתיבה rt / rd ובחירת ALU בקרת PCSrc Add 4 lw / sw Instruction [25– 21] PC Read address Instruction [31– 0] Instruction memory Instruction [20– 16] 0 M u Instruction [15– 11] x 1 Reg. Dst Instruction [15– 0] Reg. Write Read register 1 Read register 2 Read data 1 Read Write data 2 register Write Registers data 16 Sign 32 extend Shift left 2 ALU Add result 0 M u x 1 Mem. Write ALUSrc 0 M u x 1 ALU control Zero ALU result Memto. Reg Address Write data Read data 1 M u x 0 Data memory Mem. Read Instruction [5– 0] ALUOp R-type December 2013 14

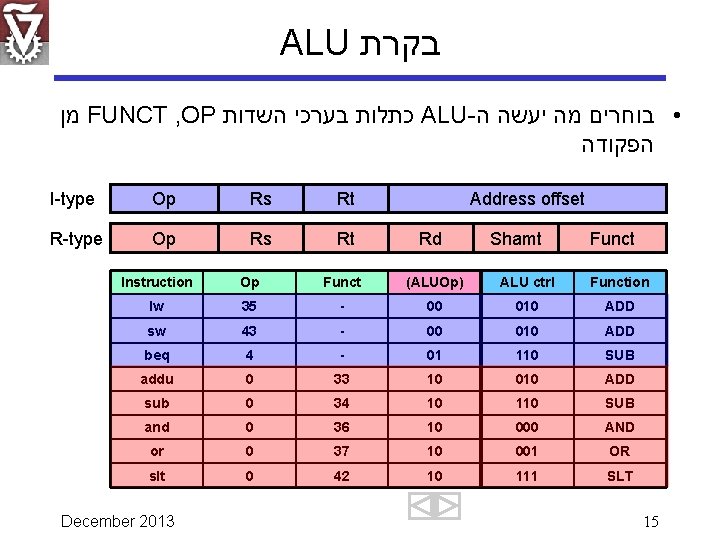

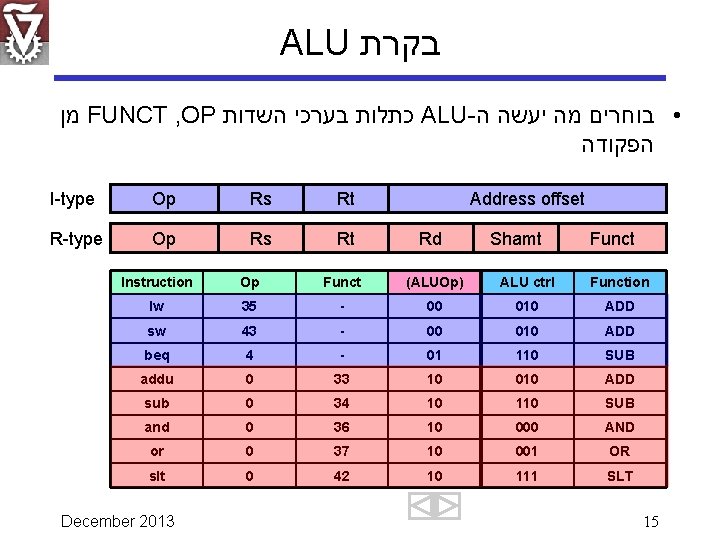

ALU בקרת מן FUNCT , OP כתלות בערכי השדות ALU- • בוחרים מה יעשה ה הפקודה I-type Op Rs Rt Address offset R-type Op Rs Rt Rd Shamt Funct Instruction Op Funct (ALUOp) ALU ctrl Function lw 35 - 00 010 ADD sw 43 - 00 010 ADD beq 4 - 01 110 SUB addu 0 33 10 010 ADD sub 0 34 10 110 SUB and 0 36 10 000 AND or 0 37 10 001 OR slt 0 42 10 111 SLT December 2013 15

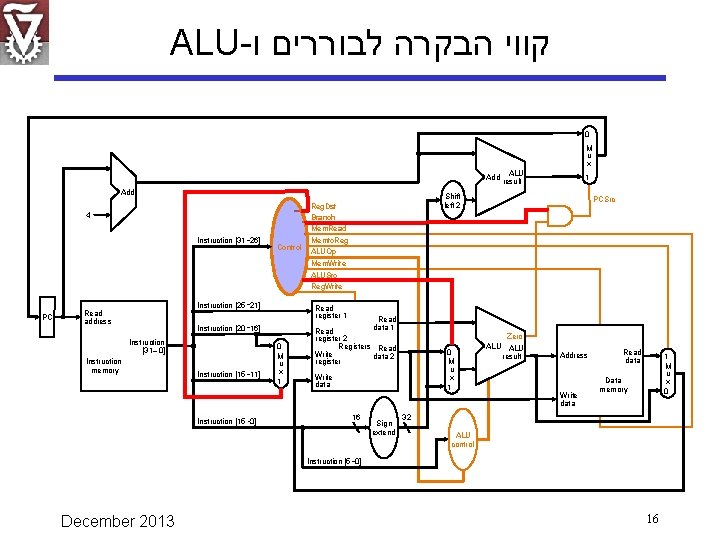

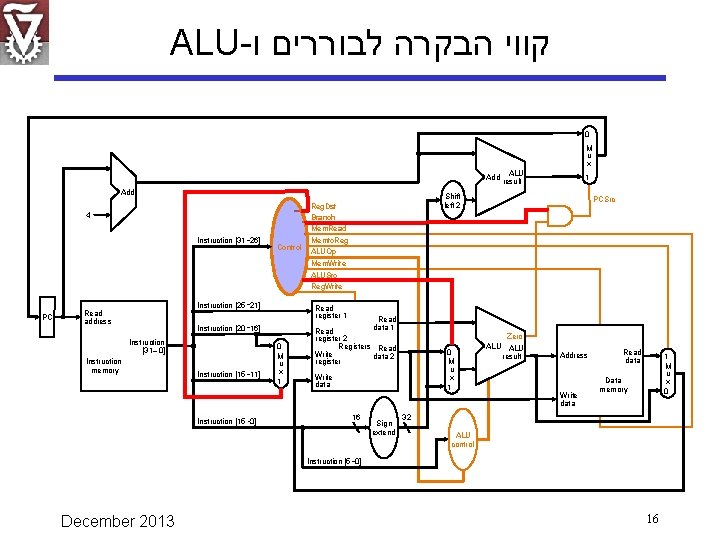

ALU- קווי הבקרה לבוררים ו 0 M u x ALU Add result Add 4 Instruction [31 26] PC Control Instruction [25 21] Read address Instruction memory Instruction [15 11] Instruction [15 0] Shift left 2 Reg. Dst Branch Mem. Read Memto. Reg ALUOp Mem. Write ALUSrc Reg. Write PCSrc Read register 1 Instruction [20 16] Instruction [31– 0] 1 0 M u x 1 Read data 1 Read register 2 Registers Read Write data 2 register 0 M u x 1 Write data 16 Sign extend Zero ALU result Address Write data Read data 1 M u x 0 Data memory 32 ALU control Instruction [5 0] December 2013 16

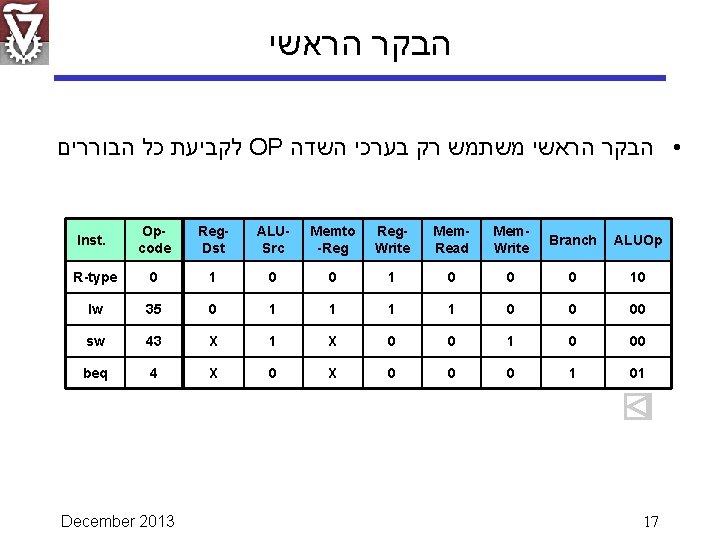

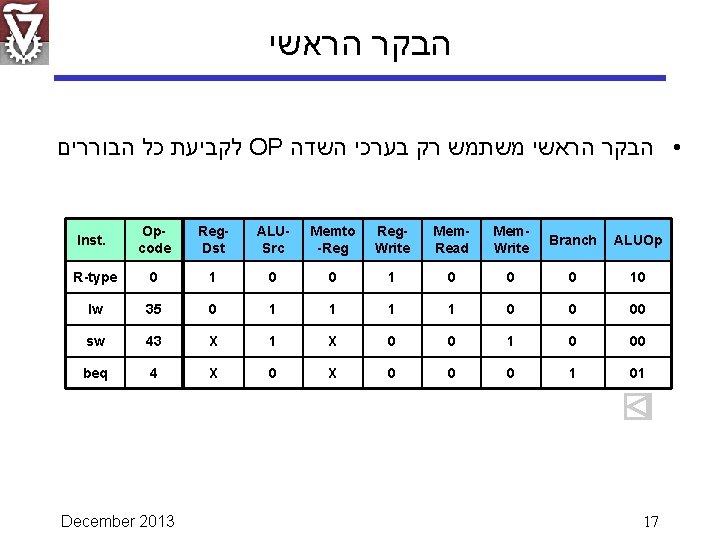

הבקר הראשי לקביעת כל הבוררים OP • הבקר הראשי משתמש רק בערכי השדה Inst. Opcode Reg. Dst ALUSrc Memto -Reg Reg. Write Mem. Read Mem. Write Branch ALUOp R-type 0 1 0 0 0 10 lw 35 0 1 1 0 0 00 sw 43 X 1 X 0 0 1 0 00 beq 4 X 0 0 0 1 01 December 2013 17

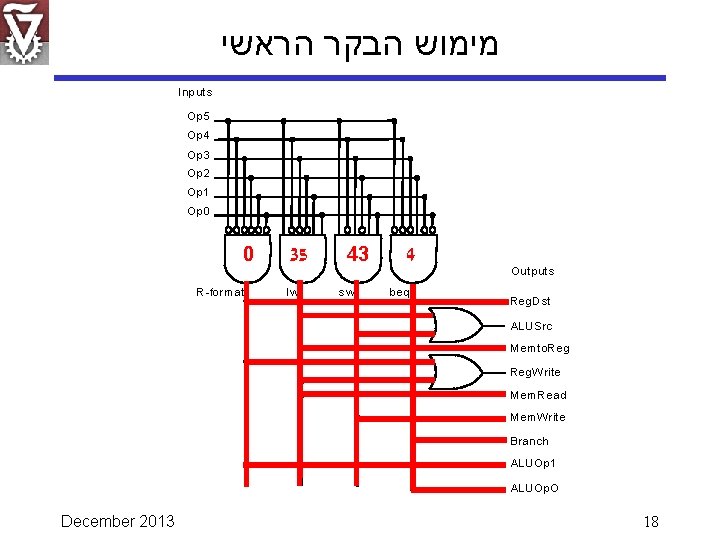

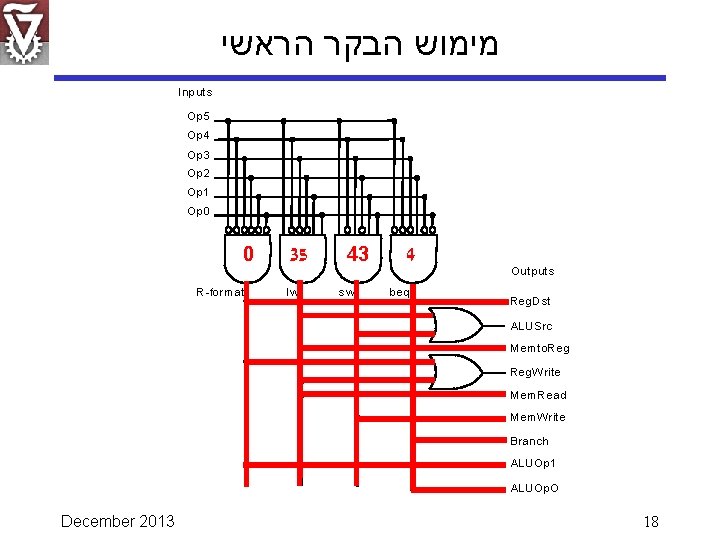

מימוש הבקר הראשי Inputs Op 5 Op 4 Op 3 Op 2 Op 1 Op 0 0 R -for mat 35 Iw 43 sw 4 beq O utputs Reg. D st ALUSrc M emto. Reg. Write M em. Read M em. Write Branch ALUOp 1 ALUOp. O December 2013 18

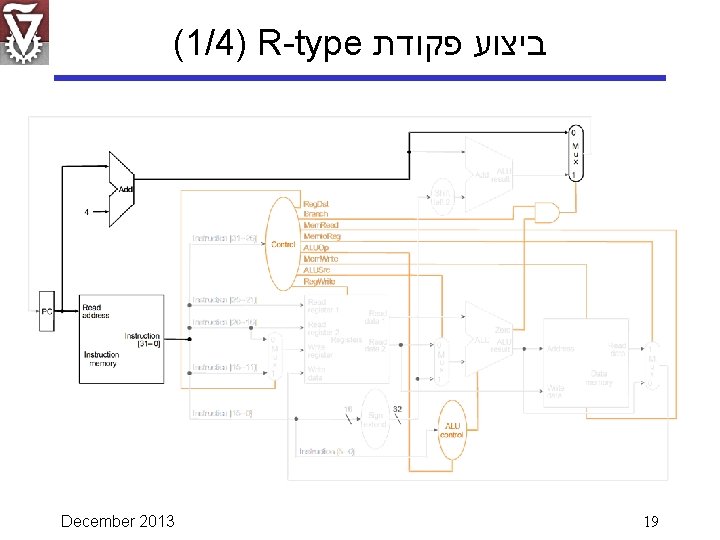

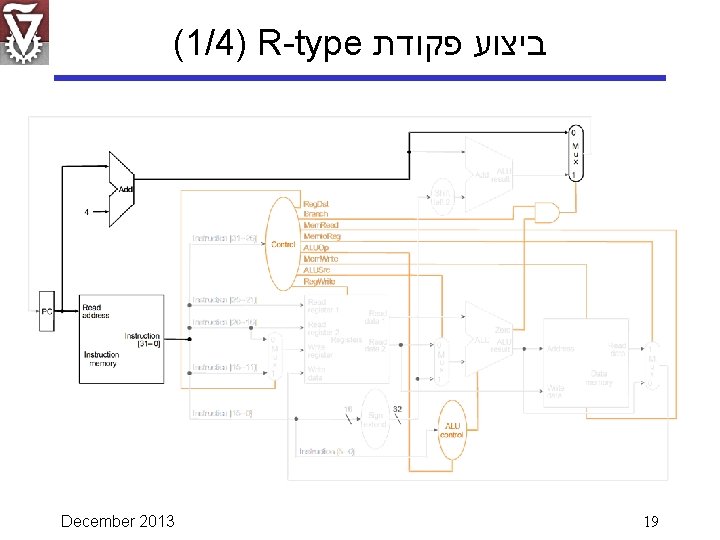

(1/4) R-type ביצוע פקודת December 2013 19

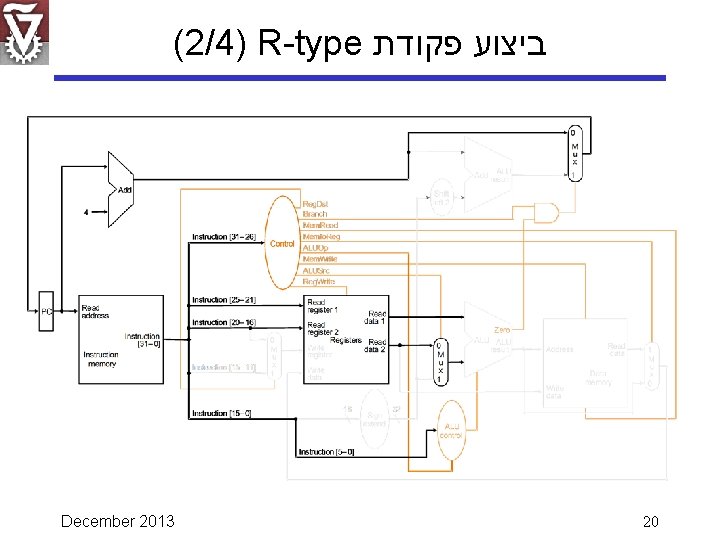

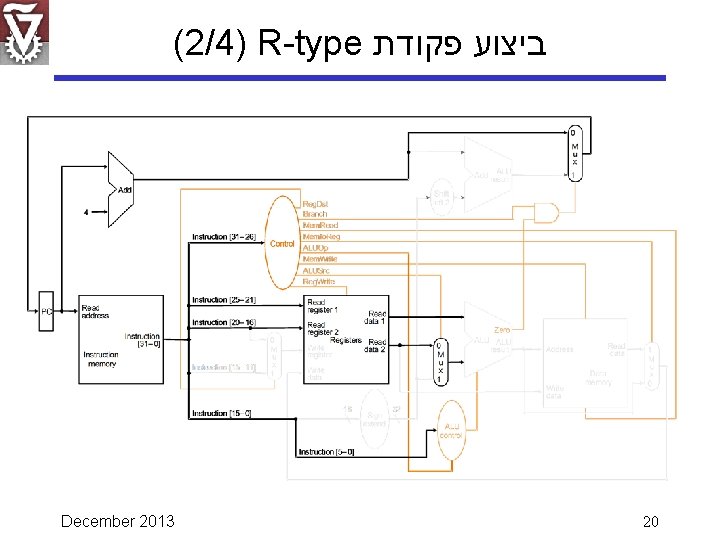

(2/4) R-type ביצוע פקודת December 2013 20

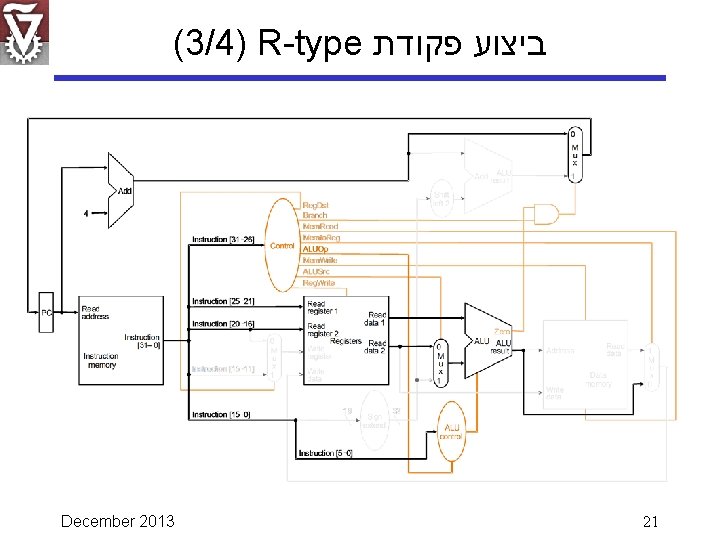

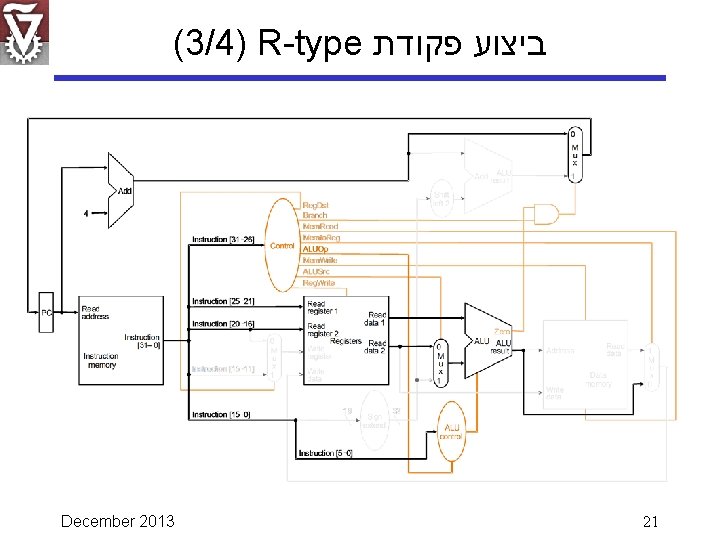

(3/4) R-type ביצוע פקודת December 2013 21

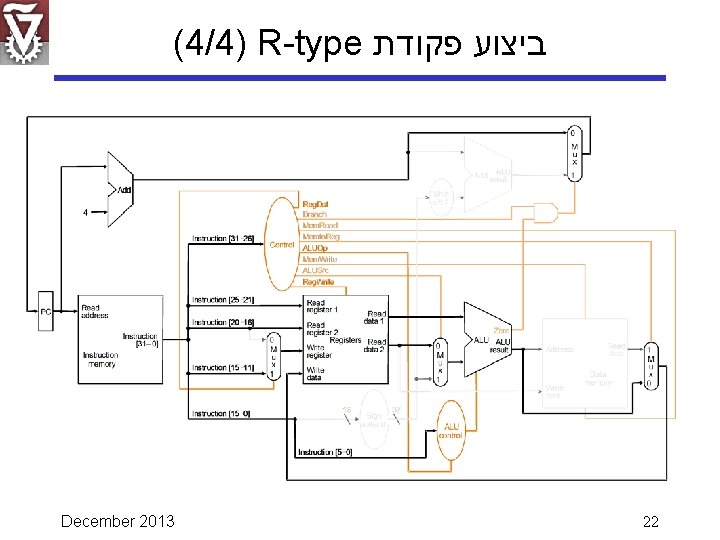

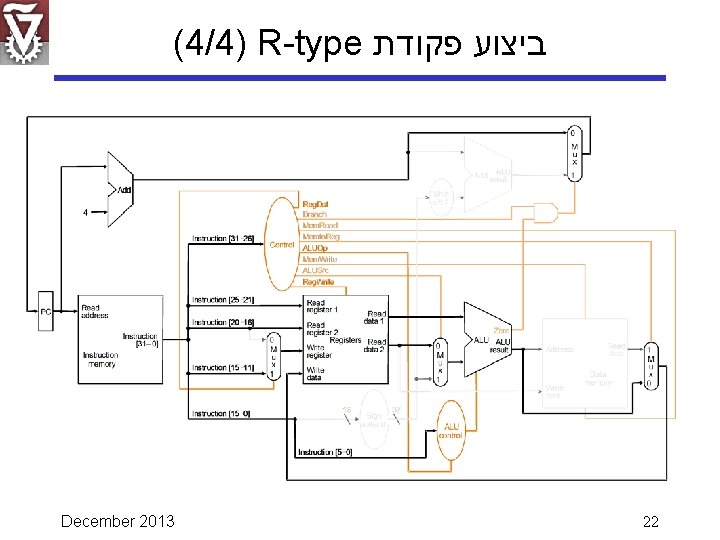

(4/4) R-type ביצוע פקודת December 2013 22

![JUMP הוספת הטיפול ב Instruction 25 0 26 Shift left 2 Jump address 31 JUMP- הוספת הטיפול ב Instruction [25– 0] 26 Shift left 2 Jump address [31–](https://slidetodoc.com/presentation_image_h2/88fb7642e02d4f3dc8c776dbb64669e9/image-24.jpg)

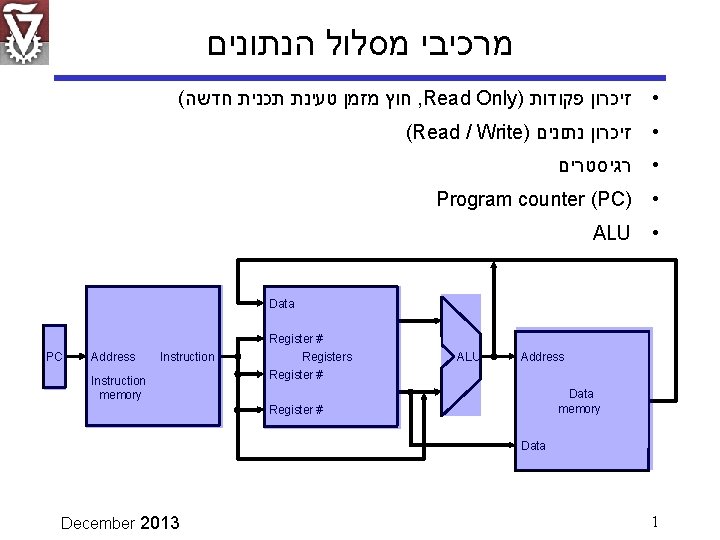

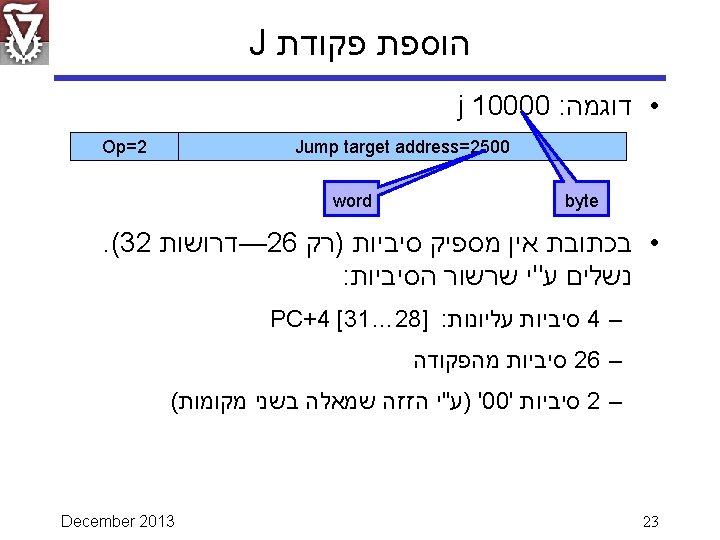

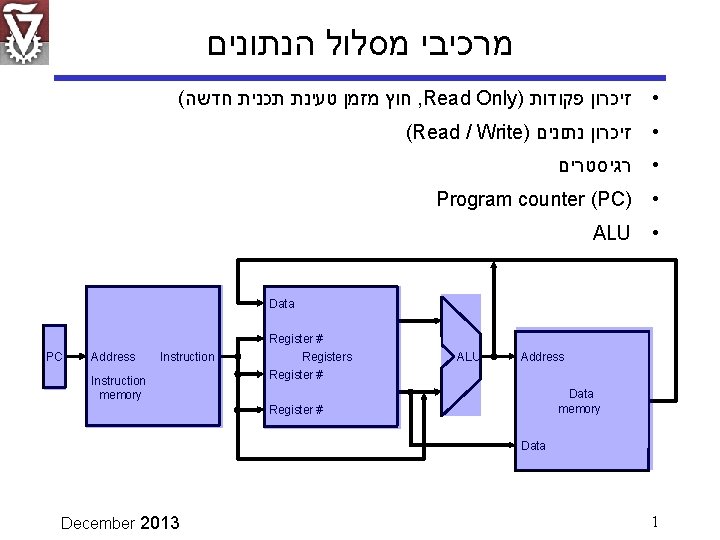

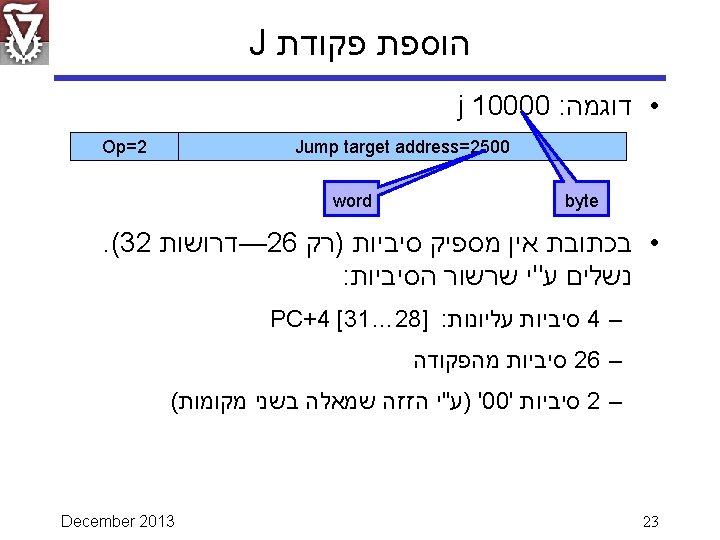

JUMP- הוספת הטיפול ב Instruction [25– 0] 26 Shift left 2 Jump address [31– 0] 28 PC+4 [31– 28] Add 1 M u x 1 0 Shift left 2 Reg. Dst Jump 4 ALU result 0 Branch Instruction [31– 26] Mem. Read Control Memto. Reg ALUOp Mem. Write ALUSrc Reg. Write Instruction [25– 21] PC Read address Read register 1 Instruction [20– 16] Instruction [31– 0] Instruction memory Instruction [15– 11] 0 M u x 1 Read data 1 Read register 2 Registers Read Write data 2 register 0 M u x 1 Write data Zero ALU result Address Write data Instruction [15– 0] 16 Sign extend Read data Data memory 1 M u x 0 32 ALU control Instruction [5– 0] December 2013 24

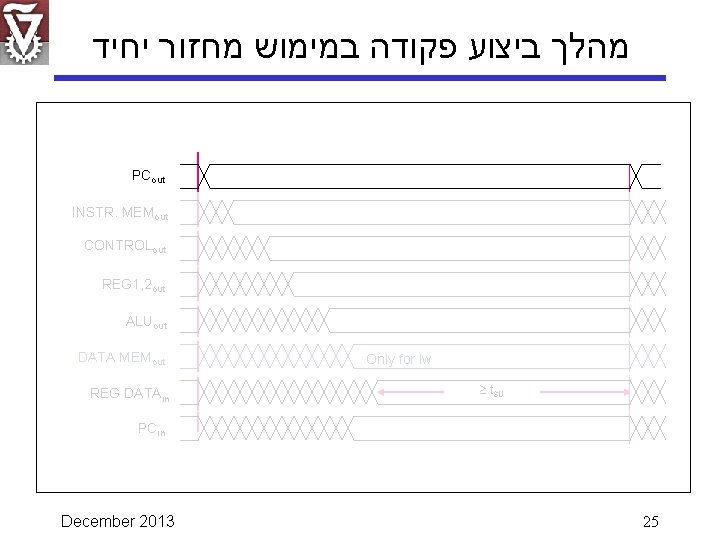

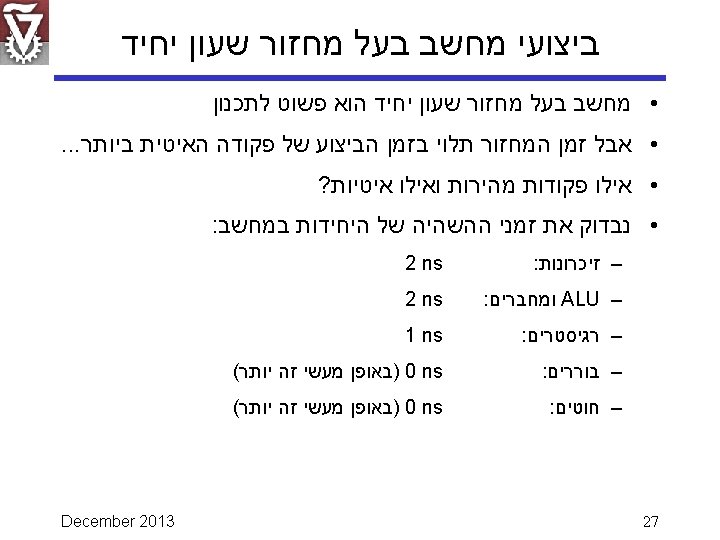

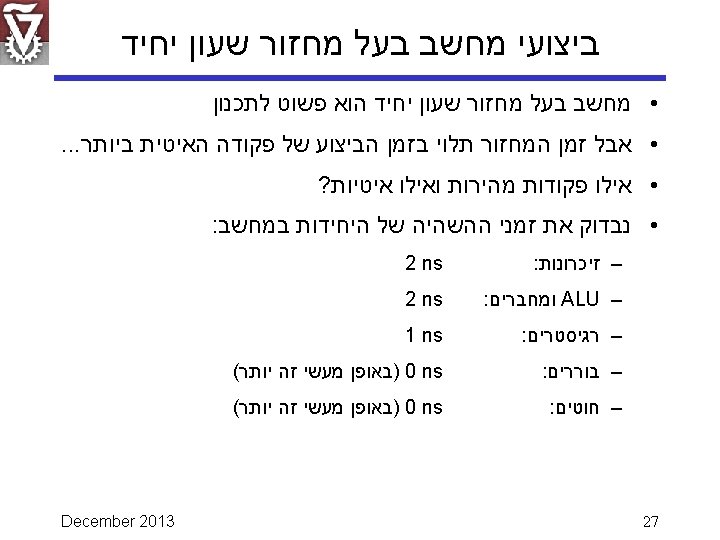

מהלך ביצוע פקודה במימוש מחזור יחיד PCout INSTR. MEMout CONTROLout REG 1, 2 out ALUout DATA MEMout REG DATAin Only for lw t. SU PCin December 2013 25

![מתי מגיע השעון Instruction 25 0 26 Shift left 2 Jump address 31 ? מתי מגיע השעון Instruction [25– 0] 26 Shift left 2 Jump address [31–](https://slidetodoc.com/presentation_image_h2/88fb7642e02d4f3dc8c776dbb64669e9/image-26.jpg)

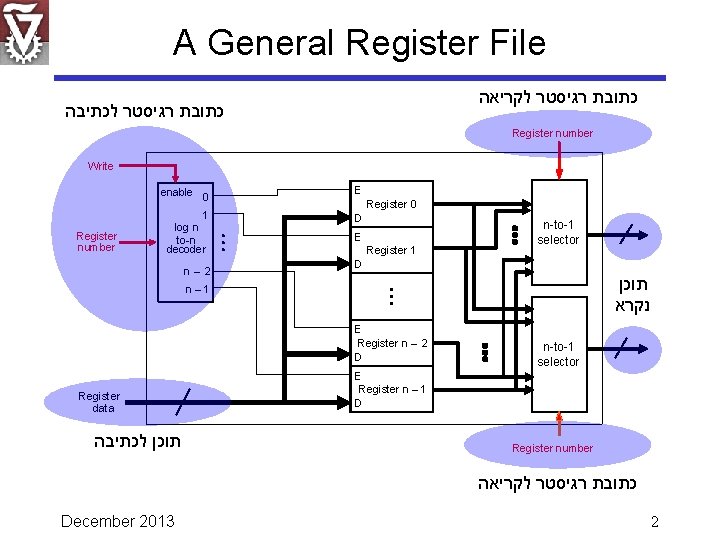

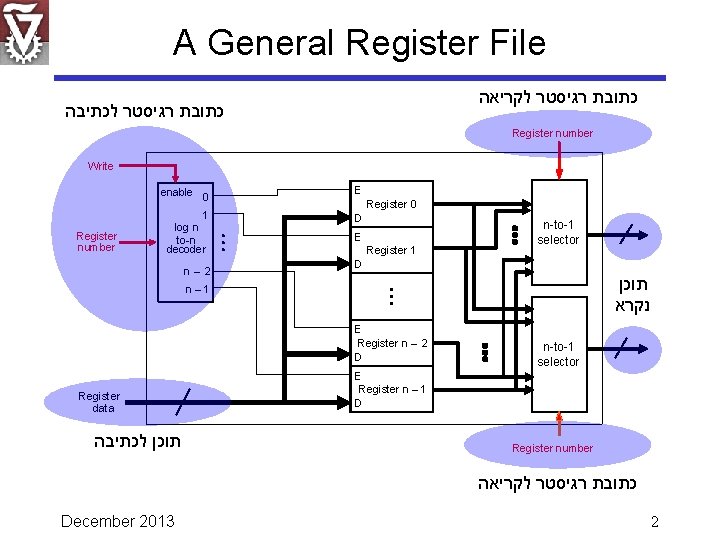

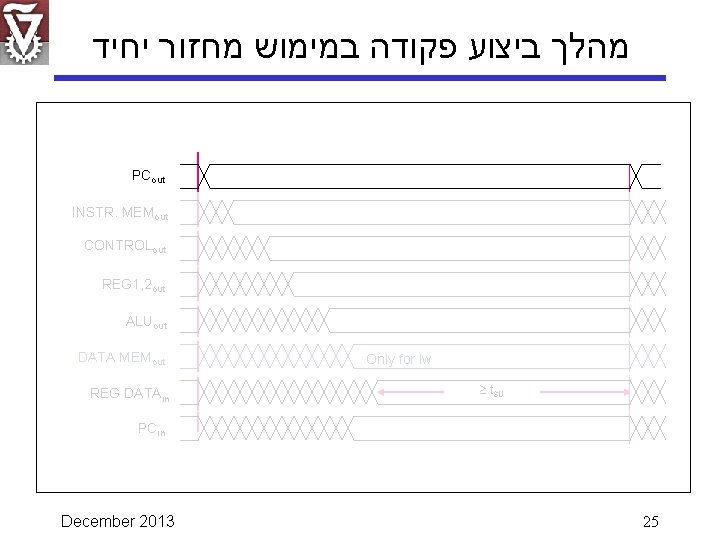

? מתי מגיע השעון Instruction [25– 0] 26 Shift left 2 Jump address [31– 0] 28 PC+4 [31– 28] Add 1 M u x 1 0 Shift left 2 Reg. Dst Jump 4 ALU result 0 Branch Instruction [31– 26] Mem. Read Control Memto. Reg ALUOp Mem. Write ALUSrc Reg. Write Instruction [25– 21] PC Read address Instruction [20– 16] Instruction [31– 0] t Read register 1 Instruction memory Instruction [15– 11] 0 M u x 1 Read data 1 Read register 2 Registers Read Write data 2 register Write data 16 Sign extend t+1 Instruction [5– 0] Read data Address Write data Instruction [15– 0] December 2013 0 M u x 1 Zero ALU result Data memory 1 M u x 0 32 ALU control t+1 26

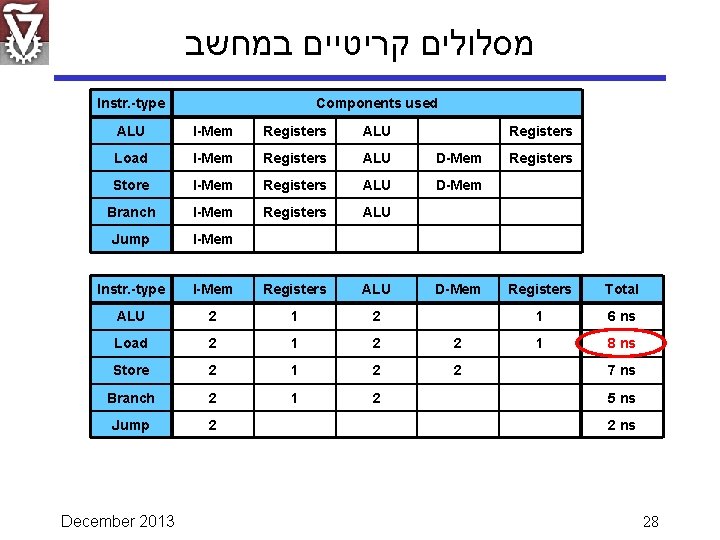

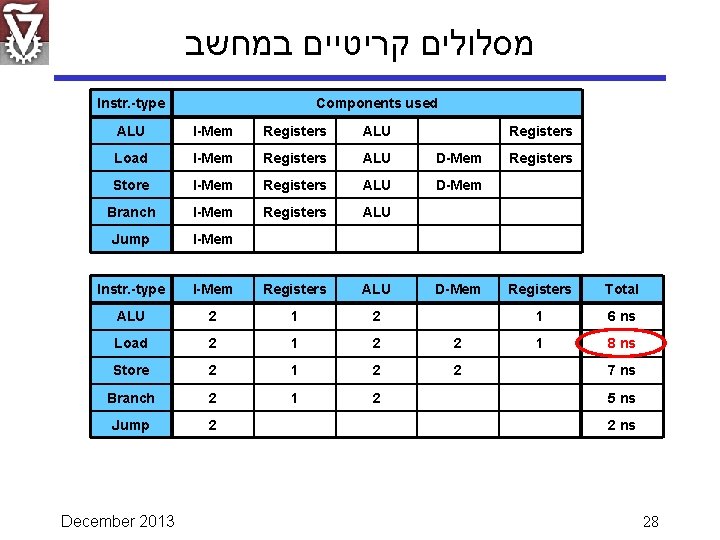

מסלולים קריטיים במחשב Instr. -type Components used ALU I-Mem Registers ALU Load I-Mem Registers ALU D-Mem Store I-Mem Registers ALU D-Mem Branch I-Mem Registers ALU Jump I-Mem Instr. -type I-Mem Registers ALU 2 1 2 Load 2 1 2 2 Store 2 1 2 2 Branch 2 1 2 Jump 2 December 2013 Registers D-Mem Registers Total 1 6 ns 1 8 ns 7 ns 5 ns 28