RCC typedef struct IO uint 32t CR IO

- Slides: 11

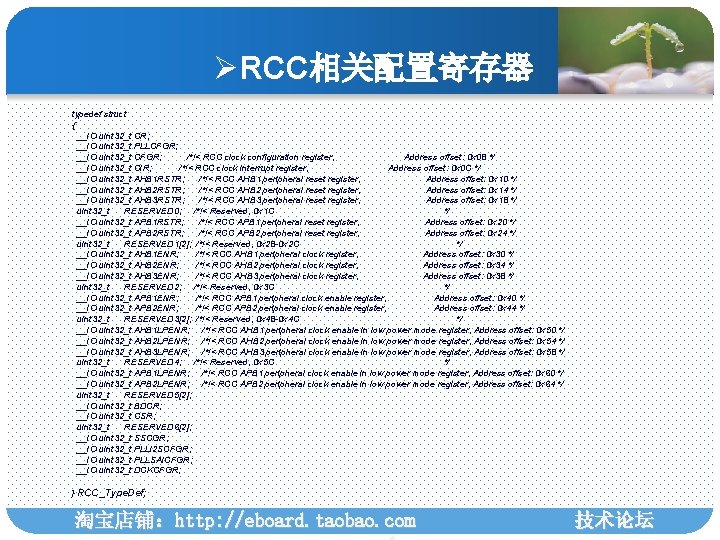

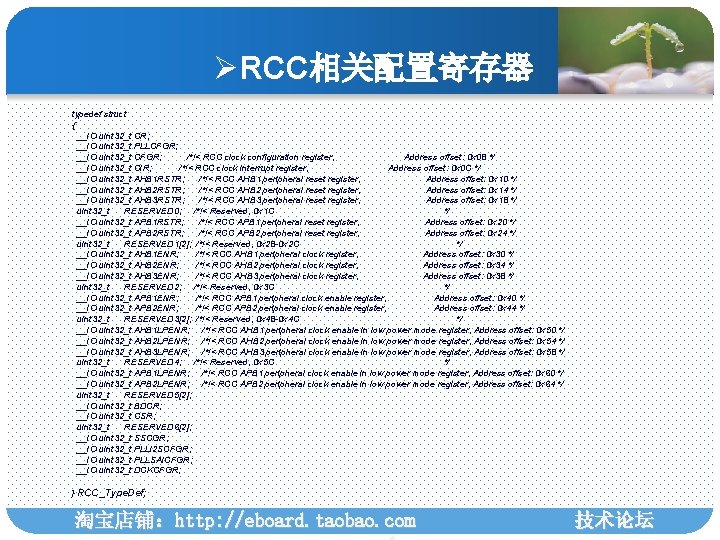

ØRCC相关配置寄存器 typedef struct { __IO uint 32_t CR; __IO uint 32_t PLLCFGR; __IO uint 32_t CFGR; /*!< RCC clock configuration register, Address offset: 0 x 08 */ __IO uint 32_t CIR; /*!< RCC clock interrupt register, Address offset: 0 x 0 C */ __IO uint 32_t AHB 1 RSTR; /*!< RCC AHB 1 peripheral reset register, Address offset: 0 x 10 */ __IO uint 32_t AHB 2 RSTR; /*!< RCC AHB 2 peripheral reset register, Address offset: 0 x 14 */ __IO uint 32_t AHB 3 RSTR; /*!< RCC AHB 3 peripheral reset register, Address offset: 0 x 18 */ uint 32_t RESERVED 0; /*!< Reserved, 0 x 1 C */ __IO uint 32_t APB 1 RSTR; /*!< RCC APB 1 peripheral reset register, Address offset: 0 x 20 */ __IO uint 32_t APB 2 RSTR; /*!< RCC APB 2 peripheral reset register, Address offset: 0 x 24 */ uint 32_t RESERVED 1[2]; /*!< Reserved, 0 x 28 -0 x 2 C */ __IO uint 32_t AHB 1 ENR; /*!< RCC AHB 1 peripheral clock register, Address offset: 0 x 30 */ __IO uint 32_t AHB 2 ENR; /*!< RCC AHB 2 peripheral clock register, Address offset: 0 x 34 */ __IO uint 32_t AHB 3 ENR; /*!< RCC AHB 3 peripheral clock register, Address offset: 0 x 38 */ uint 32_t RESERVED 2; /*!< Reserved, 0 x 3 C */ __IO uint 32_t APB 1 ENR; /*!< RCC APB 1 peripheral clock enable register, Address offset: 0 x 40 */ __IO uint 32_t APB 2 ENR; /*!< RCC APB 2 peripheral clock enable register, Address offset: 0 x 44 */ uint 32_t RESERVED 3[2]; /*!< Reserved, 0 x 48 -0 x 4 C */ __IO uint 32_t AHB 1 LPENR; /*!< RCC AHB 1 peripheral clock enable in low power mode register, Address offset: 0 x 50 */ __IO uint 32_t AHB 2 LPENR; /*!< RCC AHB 2 peripheral clock enable in low power mode register, Address offset: 0 x 54 */ __IO uint 32_t AHB 3 LPENR; /*!< RCC AHB 3 peripheral clock enable in low power mode register, Address offset: 0 x 58 */ uint 32_t RESERVED 4; /*!< Reserved, 0 x 5 C */ __IO uint 32_t APB 1 LPENR; /*!< RCC APB 1 peripheral clock enable in low power mode register, Address offset: 0 x 60 */ __IO uint 32_t APB 2 LPENR; /*!< RCC APB 2 peripheral clock enable in low power mode register, Address offset: 0 x 64 */ uint 32_t RESERVED 5[2]; __IO uint 32_t BDCR; __IO uint 32_t CSR; uint 32_t RESERVED 6[2]; __IO uint 32_t SSCGR; __IO uint 32_t PLLI 2 SCFGR; __IO uint 32_t PLLSAICFGR; __IO uint 32_t DCKCFGR; } RCC_Type. Def; 淘宝店铺:http: //eboard. taobao. com 技术论坛

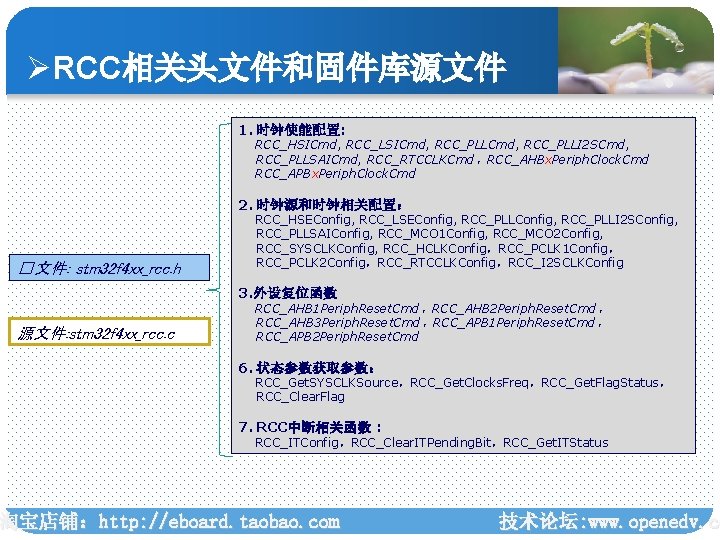

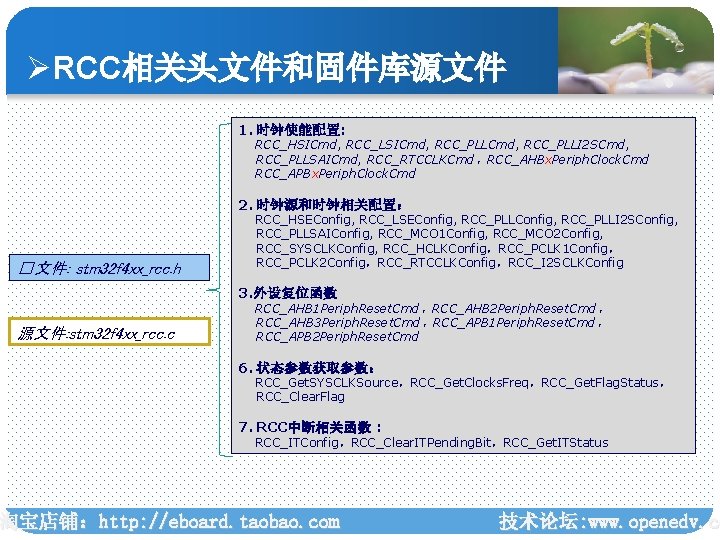

ØRCC相关头文件和固件库源文件 1. 时钟使能配置: RCC_HSICmd, RCC_LSICmd, RCC_PLLI 2 SCmd, RCC_PLLSAICmd, RCC_RTCCLKCmd,RCC_AHBx. Periph. Clock. Cmd RCC_APBx. Periph. Clock. Cmd 2. 时钟源和时钟相关配置: �文件: stm 32 f 4 xx_rcc. h RCC_HSEConfig, RCC_LSEConfig, RCC_PLLI 2 SConfig, RCC_PLLSAIConfig, RCC_MCO 1 Config, RCC_MCO 2 Config, RCC_SYSCLKConfig, RCC_HCLKConfig,RCC_PCLK 1 Config, RCC_PCLK 2 Config,RCC_RTCCLKConfig,RCC_I 2 SCLKConfig 3. 外设复位函数 源文件: stm 32 f 4 xx_rcc. c RCC_AHB 1 Periph. Reset. Cmd,RCC_AHB 2 Periph. Reset. Cmd, RCC_AHB 3 Periph. Reset. Cmd,RCC_APB 1 Periph. Reset. Cmd, RCC_APB 2 Periph. Reset. Cmd 6. 状态参数获取参数: RCC_Get. SYSCLKSource,RCC_Get. Clocks. Freq,RCC_Get. Flag. Status, RCC_Clear. Flag 7. RCC中断相关函数 : RCC_ITConfig,RCC_Clear. ITPending. Bit,RCC_Get. ITStatus 淘宝店铺:http: //eboard. taobao. com 技术论坛: www. openedv. co